Académique Documents

Professionnel Documents

Culture Documents

3094 Dell Latitude d630 Compalm08 (Dis) Briscoe La-3302

Transféré par

Pedro PericoDescription originale:

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

3094 Dell Latitude d630 Compalm08 (Dis) Briscoe La-3302

Transféré par

Pedro PericoDroits d'auteur :

Formats disponibles

A

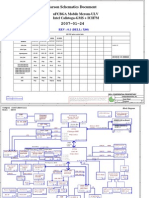

COMPAL CONFIDENTIAL

1

MODEL NAME : IBQ00

PCB NO : LA-3302P ( DAA00000K0L)

BOM P/N : 45144731L01

M08 (DIS) Briscoe

uFCPGA Mobile Merom

Intel Crestline + ICH8M

2007-03-07

REV : 0.4 (X03)

3

@ : Nopop Component

1@ : Populate for G72MV

2@ : Populate for G86MV

45144731L01 pop for G86MV

45144XXXXX pop for G72MV

4

MB PCB

Part Number

DELL CONFIDENTIAL/PROPRIETARY

Description

DAA00000K0L

PCB ZGX LA-3302P

REV0 M/B DIS

Compal Electronics, Inc.

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

Title

Cover Sheet

Size

Document Number

Date:

Wednesday, March 07, 2007

Rev

0.4

LA-3302P

Sheet

E

of

66

Block Diagram

Compal confidential

Model : IBQ01

FAN

1

Pentium-M

Merom -4MB (Socket P)

uFCPGA CPU

Thermal

GUARDIAN III

EMC4001

+FAN1_VOUT

page 18

+3.3V_SUS

+VCC_CORE

CRT CONN

+5V_RUN

CPU ITP Port

+1.05V_VCCP

page 18

H_A#(3..35)

page 20

+1.05V_VCCP page 7

page 7,8,9

478pin

System Bus

Clock Generator

CK505

+3.3V_M

page6

H_D#(0..63)

FSB 800 MHz

RGB

+LCDVDD page 19

DVI

INTEL

Crestline

NV G86

LVDS CONN

+INV_PWR_SRC

PCI-E 16X

+1.25V_GFX_PCIE

+1.25V_RUN

+GPU_CORE(1.1V)

+1.5V_RUN

page 51,52,53,54,55,56,57

+1.8V_SUS

Memory BUS

(DDR2) +1.8V_SUS

DDRII-DIMM X2

BANK 0, 1, 2, 3, 4 ,5 ,6 ,7 ,8

533 / 667MHz

page 16,17

+0.9V_DDR_VTT

1299pin BGA

+1.8V_SUS

+1.05V_VCCP

+3.3V_RUN

TV

PCI BUS

PCI_PIRQA#

REQ#0

GNT#0

DOCKING

BUFFER

DOCKING

PORT

page 36

DOCK LPC BUS

+5V_RUN page 35

(+3VRUN 33MHz)

+5V_RUN

USB[2,3]

page 30

Mini Card2

WLAN

+3.3V_WLAN

+1.5V_RUN page 34

Mini Card 1

WWAN

+3.3V_RUN

+1.5V_RUN page 34

+RTC_CELL

+3.3V_RUN

IEEE1394

+3.3V_SUS

page 30

USB[6]

USB[8]

+1.25V_RUN

+1.5V_RUN

(+1.5V_RUN 100MHz)

SIDE

page 32

USB Ports X2

USB0 : side pair top,

USB1 : side pair bottom

Azalia I/F

PATA

page 21,22,23,24

+3VRUN

33MHz

USB[0,1]

USB2 : Rear Left as viewed from the back,

USB3 Rear Right as viewed from the back

+5V_SUS IO/Board

+1.05V_VCCP

GIGA Enthernet

BCM5755M

SATA

SPI

SC_USB

M DC

LPC BUS

+3.3V_SUS

page 33

+3.3V_LAN

+2.5V_LAN

+1.2V_LAN

page 28,29

USB[9]

INTEL

ICH8-M

676pin BGA

SLOT

page 31

USB Ports X2

+5V_SUS

48MHz

CardBus

OZ711 LQFP

+3.3V_RUN

REAR

+1.5V_RUN

100MHz

IDSEL:AD17

(PIRQD#,GNT#1,REQ#1)

PCI Express BUS

page 10,11,12,13,14,15

DMI

Smart Card

OZ77CR6

USB[4]

+1.8V_RUN

DOCK LPC BUS

RJ45

+3.3V_ALW page 38

IO/B

Cable

SMSC SIO

ECE5028

S-HDD

D Moudle

+5V_HDD

page 25

+5V_MOD

page 25

Azalia Codec

STAC9205

+3.3V_RUN

+VDDA

page 26

RJ11

IO/B

COM

+3.3V_SUS

page 37

1.8V / 0.9V/1.25V

PWR Sequence

page 42

MEC5025

ECE1077

1.5V / 1.05V

ME & LED

SPI

page 46

page 43

+3.3V_ALW

page 37

page 47

+RTC_CELL

+3.3V_ALW page 39

AMP & INT.

Speaker

INT MIC

+VDDA

page 27

+5V_RUN page 27

DC IN

Vccore

page 44

Int.KBD &

Stick page

page 48

HeadPhone

& MIC Jack

+3.3V_RUN page 27

ST M25P16

+3.3V_SUS page 39

40

Charger

Battery IN

page 44

3V / 5V /15V

Bluetooth

page 49

Touch Pad

+5V_RUN

USB[7]

Battery Select

page 45

Stick

+3.3V_RUN page 40

page 40

Biometric

+3.3V_RUN page 40

USB[5]

DELL CONFIDENTIAL/PROPRIETARY

Compal Electronics, Inc.

Title

Block Diagram

Trough Cable

Size

page 50

Document Number

Rev

0.4

LA-3302P

Date:

A

Monday, February 26, 2007

Sheet

E

of

66

POWER STATES

Signal

State

S0 (Full ON) / M0

SLP

S3#

SLP

S4#

SLP

S5#

S4

STATE#

SLP

M#

ALWAYS

PLANE

HIGH

HIGH

HIGH

HIGH

HIGH

ON

M

PLANE

SUS

PLANE

RUN

PLANE

ON

ON

ON

CLOCKS

USB PORT#

DESTINATION

Side Top

Side Bottom

Rear Left

Rear Right

Smart Card

Biometric

Card Bus

Bluetooth

Docking

WWAN

None

None

None

None

ON

S3 (Suspend to RAM) / M1

LOW

HIGH

HIGH

HIGH

HIGH

ON

ON

ON

OFF

ON

S4 (Suspend to DISK) / M1

LOW

HIGH

HIGH

LOW

HIGH

ON

ON

ON

OFF

ON

S5 (SOFT OFF) / M1

LOW

HIGH

LOW

LOW

HIGH

ON

ON

ON

OFF

ON

S3 (Suspend to RAM) / M-OFF

LOW

HIGH

HIGH

HIGH

LOW

ON

OFF

ON

OFF

OFF

S4 (Suspend to DISK) / M-OFF

LOW

LOW

HIGH

LOW

LOW

ON

OFF

OFF

OFF

OFF

S5 (SOFT OFF) / M-OFF

LOW

LOW

LOW

LOW

LOW

ON

OFF

OFF

OFF

OFF

ICH8-M

PM TABLE

+15V_ALW

power

plane

+5V_SUS

+5V_RUN

+3.3V_M

+1.25V_M

+5V_ALW

+3.3V_SUS

+3.3V_RUN

+1.25V_M +3.3V_M

+3.3V_ALW

+1.8V_SUS

+2.5V_RUN

+1.05V_M +1.05V_M

(M-OFF)

+1.8V_RUN

+3.3V_RTC_LDO

+1.5V_RUN

ECE 5028

+VCC_+1P2V_GPU_CORE

+0.9V_DDR_VTT

+GPU_CORE

State

+VCC_CORE

+1.05V_VCCP

S0

ON

ON

ON

ON

ON

S3

ON

ON

OFF

ON

OFF

S5 S4/AC

ON

OFF

OFF

ON

OFF

S5 S4/AC don't exist

OFF

OFF

OFF

OFF

OFF

PCI EXPRESS

DESTINATION

Lane 1

MINI CARD-1 WWAN

Lane 2

MINI CARD-2 WLAN

Lane 3

None

Lane 4

None

Lane 5

None

Lane 6

GIGA LAN

PCI TABLE

PCI DEVICE

IDSEL

REQ#/GNT#

PIRQ

OZ711

AD17

REQ#1 / GNT#1

PIRQD

Docking

AD24

REQ#0 / GNT#0

PIRQA

DELL CONFIDENTIAL/PROPRIETARY

Compal Electronics, Inc.

Title

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

Index and Config.

Size

Rev

0.4

LA-3302P

Date:

Document Number

Monday, February 26, 2007

Sheet

1

of

66

RUN_ON

FDS4435

(Q24)

+INV_PWR_SRC

RUN_ON

M_ON

ADAPTER

MAX1510E

(PU26)

+1.25V_RUN

+1.25V_M

D

ISL6236

(PU25)

MAX1510E

(PU26)

+1.05V_M

GFX_CORE_ON

+GPU_CORE

+PWR_SRC

BATTERY

+15V_ALW

ALWON

+5V_ALW

CHARGER

ISL6260

(PU11)

ISL88550A

(PU6)

ISL6236

(PU21)

ISL6236

(PU20)

RUN_ON

SI4810DY

(Q52)

ALWON

+1.05V_VCCP

+1.5V_RUN

M_ON

1.5V_RUN_ON

1.05V_RUN_ON

+0.9V_DDR_VTT

SI3456BDV

(Q44)

SI4810DY

(Q58)

+3.3V_LAN

+3.3V_RUN

SI4800BDY

(Q67)

MAX9789A

(U37)

SI3456BDV

(Q54)

BCP69

(Q45)

+5V_HDD

+5V_MOD

+3.3V_M

CTRL_10

SI3456

(Q48)

CTRL_18

SI3456BDV

(Q56)

MODC_EN#

HDDC_EN#

AUDIO_AVDD_ON

RUN_ON

+3.3V_SUS

RUN_ON

+1.8V_SUS

ENAB_3VLAN

+VCC_CORE

+5V_SUS

DDR_ON

SUS_ON

ISlL88550_AVDD

RUNPWROK

+3.3V_ALW

+5V_RUN

BCP69

(Q46)

+VDDA

+1.8VRUN

+1.8V_LAN

+1.0V_LAN

DELL CONFIDENTIAL/PROPRIETARY

Compal Electronics, Inc.

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

Title

Power Rail

Size

Rev

0.4

LA-3302P

Date:

Document Number

Monday, February 26, 2007

Sheet

1

of

66

2.2K

2.2K

+3.3V_SUS

2.2K

ICH8-M

AJ26

ICH_SMBCLK

AD19

ICH_SMBDATA

2.2K

2N7002

+3.3V_RUN

MEM_SCLK

197

MEM_SDATA

195

DIMMA

SMBUS Address [TBD]

DIMMB

SMBUS Address [TBD]

2N7002

32

30

C7

C8

32

30

197

WWAN

2.2K

Intel LAN

195

2.2K

SMBUS Address [TBD]

SMBUS Address [TBD]

WLAN_SMBCLK

2N7002

+3.3V_WLAN

WLAN_SMBDATA

WLAN

@ 0

CLK_SCLK

@ 0

CLK_SDATA

2N7002

SMBUS Address [TBD]

8.2K

+3.3V_ALW

8.2K

8

LCD_SMBCLK

LCD_SMDATA

INVERTER

(JLVDS)

4.7K

SMBUS Address [TBD]

C

10

+3.3V_ALW

4.7K

100

THRM_SMBCLK

99

THRM_SMBDAT

Charger

SMBUS Address [TBD]

EMC4001

SMBUS Address [TBD]

2'nd

BATTERY

SMBUS Address [TBD]

BATTERY

CONN

SMBUS Address [TBD]

12

11

2.2K

+3.3V_ALW

2.2K

SIO

10

SBAT_SMBCLK

100 ohm

SBAT_SMBDAT

100 ohm

2.2K

+3.3V_ALW

2.2K

111

PBAT_SMBCLK

112

PBAT_SMBDAT

100 ohm

100 ohm

9

10 CHARGER

SMBUS Address [TBD]

8.2K

+5V_ALW

8.2K

MEC 5025

DOCK_SMB_CLK

DOCK_SMB_DAT

6

5

DOCKING

SMBUS Address [TBD]

2.2K

2.2K

12

CKG_SMBDAT

13

CKG_SMBCLK

2N7002

2N7002

+3.3V_RUN

CLK_SDATA

17

CLK_SCLK

16 CLK GEN

SMBUS Address [TBD]

Compal Electronics, Inc.

Title

SMBUS TOPOLOGY

Size

Document Number

Rev

0.4

LA-3302P

Date:

5

Monday, February 26, 2007

Sheet

1

of

66

+3.3V_RUN

2

G

CLKSEL2

CLKSEL1

CLKSEL0

CPU

MHz

SRC

MHz

PCI

MHz

266

100

33.3

133

100

33.3

200

100

33.3

333

100

33.3

100

100

33.3

400

100

33.3

200

100

33.3

C483

X1

27P_0402_50V8J~D 14.31818MHz_20P_1BX14318CC1A~D

2

1

Place crystal within

500 mils of CK410

CLK_ICH_48M

CLK_SMC_48M

CLK_PCI_TPM

CLK_PCI_DOCK

28 CLK_PCI_TPM

36 CLK_PCI_DOCK

0

30 CLK_PCI_PCM

39 CLK_PCI_5025

166

38 CLK_PCI_5018

23 CLK_ICH_14M

38 CLK_SIO_14M

1

2

1@ R697

84.5_0402_1%~D

R290

10K_0402_5%~D

52 CLK_NVSS_27M

21 CLK_PCI_ICH

23 CLK_PWRGD

PCI_PCM

VTT_PWRGD#/PD

CKPWRGD/PD#

@ R391

10K_0402_5%~D

VDD_REF

40

VDD_48

25

H_STP_PCI#

CPU_STP#

24

H_STP_CPU#

CPU_1

11

MCH_BCLK

CPU_1#

10

MCH_BCLK#

CPU_0

14

CPU_BCLK

CPU_0#

13

CPU_BCLK#

XTAL_IN

19

XTAL_OUT

41

USB_48MHz/FSLA

45

FSL_B/TEST_MODE

R314 1

2 8.2K_0402_5%~D

FSC

23

REF_0/FSL_C/TEST_SEL

R277 2

R596 2

1 33_0402_5%~D

1 33_0402_5%~D

PCI_LOM

34

PCICLK4/FCT_SEL

PCI_DOCK

33

PCICLK3

PCI_PCM

32

PCICLK2/TME

PCI_SIO

27

PCICLK1

CLKREF

22

1 33_0402_5%~D

1 15_0402_5%~D

CLK_PCI_5018

R333 1

2 15_0402_5%~D

CLK_ICH_14M

CLK_SIO_14M

R284 1

R285 1

2 15_0402_5%~D

2 15_0402_5%~D

CLK_NVSS_27M

2@ R286 1

1@ R833 1

R287 1

CLK_PCI_ICH

R291 2

2 33_0402_5%~D

2 147_0402_1%~D

2 33_0402_5%~D

1 33_0402_5%~D

DOT96

CPU_ITP/SRC_10

CPU_ITP

CPU_ITP#/SRC_10#

CPU_ITP#

SRC_9

PCIE_MINI1

PCIE_MINI1#

DOT_96/27M

CLK_NVSS

44

DOT_96#/27M_SS

PCI_ICH

37

CLK_PWRGD

@

+3.3V_RUN

R295

10K_0402_5%~D

1

2

@ R298

1

2

10K_0402_5%~D

39

34 CLK_SDATA

PGMODE

CLK_SCLK

16

CLK_SDATA

17

CLKREQ_9#

72

SRC_8

70

PCIE_MINI2

SRC_8#

69

PCIE_MINI2#

71

SRC_7

66

PCIE_ICH

PCIE_ICH#

SRC_7#

67

CLKREQ_7#

38

63

PCIE_LOM

64

PCIE_LOM#

CLKREQ_6#

62

SRC_5

60

PCIE_VGA

PCIE_VGA#

SRC_5#

61

CLKREQ_5#

29

SRC_4

58

SRC_4#

59

PGMODE

SMBCLK

57

MCH_3GPLL

56

MCH_3GPLL#

SRC_3#

CLKREQ_3#

28

VSS_REF

SRC_2

52

Pin 5/6 as SRC_10

31

VSS_PCI

SRC_2#

53

Pin 5/6 as CPU_ITP

35

VSS_PCI

CLKREQ_2#

26

42

VSS_48

68

VSS_SRC

73

74

75

76

THRM_PAD

THRM_PAD

THRM_PAD

THRM_PAD

Normal Operation

Trusted Mode Enabled

FCTSEL1

PIN43

PIN44

PIN47

PIN48

0=UMA

DOT96T

DOT96C

96/100M_T

96/100M_C

1=DIS

27M_out

27M SSout

SRCT0

SRCC0

1

R267

1

R268

CLK_MCH_BCLK

2

33_0402_5%~D

CLK_MCH_BCLK#

2

33_0402_5%~D

1

R269

1

R270

CLK_CPU_BCLK

2

33_0402_5%~D

CLK_CPU_BCLK#

2

33_0402_5%~D

1

R272

1

R274

CLK_CPU_ITP

2

33_0402_5%~D

CLK_CPU_ITP#

2

33_0402_5%~D

1

R311

1

R313

CLK_PCIE_MINI1

2

33_0402_5%~D

CLK_PCIE_MINI1#

2

33_0402_5%~D

1

R306

1

R307

CLK_PCIE_MINI2

2

33_0402_5%~D

CLK_PCIE_MINI2#

2

33_0402_5%~D

1

R288

1

R289

CLK_PCIE_ICH

2

33_0402_5%~D

CLK_PCIE_ICH#

2

33_0402_5%~D

0=UMA

1=Disc. GRFX down

1

R302

1

R303

CLK_PCIE_LOM

2

33_0402_5%~D

CLK_PCIE_LOM#

2

33_0402_5%~D

1

R299

1

R168

CLK_PCIE_VGA

2

33_0402_5%~D

CLK_PCIE_VGA#

2

33_0402_5%~D

SRC_1/SATA

50

PCIE_SATA

SRC_1#/SATA#

51

PCIE_SATA#

CLKREQ_1#

46

LCD_CLK/SRC_0

47

LCD_CLK#/SRC_0#

48

1

R293

1

R294

1

R419

CLK_MCH_3GPLL

2

33_0402_5%~D

CLK_MCH_3GPLL#

2

33_0402_5%~D

2

475_0402_1%~D

1

R279

1

R281

CLK_PCIE_SATA

2

33_0402_5%~D

CLK_PCIE_SATA#

2

33_0402_5%~D

CLK_PCI_TPM

CLK_MCH_BCLK# 10

1

CLK_CPU_BCLK 7

CLK_CPU_BCLK# 7

C777

3.3P_0402_50V8C~D

@

CLK_PCI_DOCK

CLK_CPU_ITP 7

1

CLK_CPU_ITP# 7

CLK_PCIE_MINI1 34

C778

3.3P_0402_50V8C~D

@

CLK_PCIE_MINI1# 34

CLK_PCI_PCM

1

CLK_PCIE_MINI2 34

CLK_PCIE_MINI2# 34

C779

3.3P_0402_50V8C~D

@

CLK_PCI_5025

CLK_PCIE_ICH 23

CLK_PCIE_ICH# 23

C780

3.3P_0402_50V8C~D

@

CLK_PCIE_LOM 28

CLK_PCI_5018

CLK_PCIE_LOM# 28

1

CLK_PCIE_VGA 52

C781

3.3P_0402_50V8C~D

@

CLK_PCIE_VGA# 52

CLK_PCI_ICH

C785

3.3P_0402_50V8C~D

@

CLK_MCH_3GPLL 10

CLK_MCH_3GPLL# 10

CLK_3GPLLREQ# 10

CLK_PCIE_SATA 22

CLK_PCIE_SATA# 22

SATA_CLKREQ# 23

A

DELL CONFIDENTIAL/PROPRIETARY

SLG8LP550_QFN72~D

Compal Electronics, Inc.

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

Title

Clock Generator

Size

Document Number

Rev

0.4

LA-3302P

Date:

C776

3.3P_0402_50V8C~D

@

CLK_MCH_BCLK 10

55

VSS_SRC

SRC_3

4

23

H_STP_CPU# 23

LOM_CLKREQ# 28

CLKREQ_4#

SMBDAT

H_STP_PCI#

SRC_6

VSS_CPU

PIN 32

C775

3.3P_0402_50V8C~D

@

MINI2CLK_REQ# 34

SRC_6#

PCICLK_F0/ITP_EN

CKPWRGD/PD#

CLK_ICH_14M

1

MINI1CLK_REQ# 34

CLKREQ_8#

REF_1

43

CLK_SIO_14M

PCI_STP#

21

C477

0.1U_0402_16V4Z~D

C475

0.1U_0402_16V4Z~D

C476

0.1U_0402_16V4Z~D

8

15

18

VSS_A

@ R319

10K_0402_5%~D

2

FSA

VDD_CPU

VDD_A

PIN 37

TME

@ R329

10K_0402_5%~D

12

20

PCI_LOM

R318

10K_0402_5%~D

A

+3.3V_RUN

VDD_PCI

VDD_PCI

FSA

PIN 9

ITP_EN

+3.3V_RUN

30

36

SLG8LP550

CLK_XTAL_OUT

1

2

PGMODE

PCI_ICH

VDD_SRC

VDD_SRC

VDD_SRC

VDD_SRC

1 15_0402_5%~D

2 15_0402_5%~D

2 2.2K_0402_5%~D

34 CLK_SCLK

R304

10K_0402_5%~D

R273 2

R275 1

R309 1

R280 2

R282 2

Populate R697,R833 for G72MV

Populate R286 for G86MV.

R833,R286 place overlap

+3.3V_RUN

R271

0_0402_5%~D

1

2

CLK_PCI_PCM

CLK_PCI_5025

CLK_NV_27M

52 CLK_NV_27M

+3.3V_RUN

SRC_9#

CPU_BSEL2(FSC) CPU_BSEL1(FSB)

0

2 +CK_VDD_REF

1_0603_5%~D

2 +CK_VDD_48

2.2_0603_5%~D

CLK_XTAL_IN

8,10 CPU_MCH_BSEL2

133

R760

1

R758

C484

33P_0402_50V8J~D

2

1

23 CLK_ICH_48M

31 CLK_SMC_48M

8,10 CPU_MCH_BSEL0

8,10 CPU_MCH_BSEL1

Table : ICS954305AK

CPU_BSEL

1

49

54

65

33.3

100

166

2

10K_0402_5%~D

2

10K_0402_5%~D

2

10K_0402_5%~D

2

10K_0402_5%~D

2

10K_0402_5%~D

+CK_VDD_A

2.2_0603_5%~D

1

R315

1

R310

CLK_3GPLLREQ# 1

R297

SATA_CLKREQ#

1

R283

LOM_CLKREQ#

1

R301

MINI2CLK_REQ#

CLK_SMC_48M

MINI1CLK_REQ#

R759

1

C774

3.3P_0402_50V8C~D

C708

3.3P_0402_50V8C~D

U28

CLK_ICH_48M

C479

0.047U_0402_16V4Z~D

FSA

C478

4.7U_0603_6.3V4Z~D

FSB

C189

0.047U_0402_16V4Z~D

1

2

@ R440

0_0402_5%~D

C799

0.047U_0402_16V4Z~D

FSC

+CK_VDD_REF

CLK_SCLK

+CK_VDD_48

C99

4.7U_0603_6.3V4Z~D

2

G

1

39 CKG_SMBCLK

Q35

2N7002W-7-F_SOT323-3~D

3

C474

0.1U_0402_16V4Z~D

1

2

L87

BLM21PG600SN1D_0805~D

+3.3V_RUN

+3.3V_RUN

1

C482

0.1U_0402_16V4Z~D

+CK_VDD_MAIN2

C473

0.1U_0402_16V4Z~D

C481

0.1U_0402_16V4Z~D

CLK_SDATA

3

Q34

2N7002W-7-F_SOT323-3~D

+CK_VDD_MAIN

1

2

L28

BLM21PG600SN1D_0805~D

C472

10U_0805_10V4Z~D

C471

0.1U_0402_16V4Z~D

39 CKG_SMBDAT

R266

2.2K_0402_5%~D

2

1

@ R435

1

2

0_0402_5%~D

R265

2.2K_0402_5%~D

2

1

+3.3V_RUN

+CK_VDD_MAIN

C480

10U_0805_10V4Z~D

Thursday, March 01, 2007

Sheet

1

of

66

JCPUA

H_ADSTB#1

M4

N5

T2

V3

B2

C3

D2

D22

D3

F6

RSVD[01]

RSVD[02]

RSVD[03]

RSVD[04]

RSVD[05]

RSVD[06]

RSVD[07]

RSVD[08]

RSVD[09]

RSVD[10]

H_LOCK#

RESET#

RS[0]#

RS[1]#

RS[2]#

TRDY#

C1

F3

F4

G3

G2

H_RESET#

H_RS#0

H_RS#1

H_RS#2

H_TRDY#

HIT#

HITM#

G6

E4

H_HIT#

H_HITM#

BPM[0]#

BPM[1]#

BPM[2]#

BPM[3]#

PRDY#

PREQ#

TCK

TDI

TDO

TMS

TRST#

DBR#

ITP_BPM#0

AD4

ITP_BPM#1

AD3

ITP_BPM#2

AD1

ITP_BPM#3

AC4

ITP_BPM#4

AC2

ITP_BPM#5

AC1

ITP_TCK

AC5

ITP_TDI

AA6

ITP_TDO

AB3

ITP_TMS

AB5

ITP_TRST#

AB6

C20 ITP_DBRESET#

CONTROL

H_LOCK#

10

H_RESET#

H_RS#0

H_RS#1

H_RS#2

H_TRDY#

10

10

10

10

10

T47

T48

T49

T50

T51

T52

PAD~D

PAD~D

PAD~D

PAD~D

PAD~D

PAD~D

THERMTRIP#

ITP_DBRESET# 23,38

H_THERMTRIP#

H CLK

BCLK[0]

BCLK[1]

CLK_CPU_BCLK

CLK_CPU_BCLK#

A22

A21

6

6

CLK_CPU_ITP

CLK_CPU_ITP#

CLK_CPU_ITP

CLK_CPU_ITP#

+1.05V_VCCP

29

@ MOLEX_52435-2891_28P~D

H_THERMDA 18

H_THERMDC

R321

22.6_0402_1%~D

1

2

EC_CPU_PROCHOT# 39

H_THERMDA

C7

H_RESET#

R323

56_0402_5%~D

EC_CPU_PROCHOT#

D21

A24

B25

+1.05V_VCCP

H_HIT# 10

H_HITM# 10

THERMAL

PROCHOT#

THERMDA

THERMDC

56_0402_5%~D

GND7

STPCLK#

LINT0

LINT1

SMI#

H4

R320

2

22

30

D5

C6

B4

A3

LOCK#

H_BR0# 10

H_INIT#

H_STPCLK#

H_INTR

H_NMI

H_SMI#

H_IERR#

H_INIT#

JCPUD

A4

A8

A11

A14

A16

A19

A23

AF2

B6

B8

B11

B13

B16

B19

B21

B24

C5

C8

C11

C14

C16

C19

C2

C22

C25

D1

D4

D8

D11

D13

D16

D19

D23

D26

E3

E6

E8

E11

E14

E16

E19

E21

E24

F5

F8

F11

F13

F16

F19

F2

F22

F25

G4

G1

G23

G26

H3

H6

H21

H24

J2

J5

J22

J25

K1

K4

K23

K26

L3

L6

L21

L24

M2

M5

M22

M25

N1

N4

N23

N26

P3

A20M#

FERR#

IGNNE#

A[17]#

A[18]#

A[19]#

A[20]#

A[21]#

A[22]#

A[23]#

A[24]#

A[25]#

A[26]#

A[27]#

A[28]#

A[29]#

A[30]#

A[31]#

A[32]#

A[33]#

A[34]#

A[35]#

ADSTB[1]#

XDP/ITP SIGNALS

A6

A5

C4

D20

B3

BR0#

+1.05V_VCCP

C417

2200P_0402_50V7K~D

H_THERMDC 18

H_THERMTRIP# 18

CLK_CPU_BCLK 6

CLK_CPU_BCLK# 6

H_THERMDA, H_THERMDC routing together,

Trace width / Spacing = 10 / 10 mil

1

C486

H_A20M#

H_FERR#

H_IGNNE#

IERR#

INIT#

VTT1

VTT0

VTAP

DBR#

DBA#

BPM0#

GND5

BPM1#

GND4

BPM2#

GND3

BPM3#

GND2

BPM4#

GND1

BPM5#

RESET#

FBO

GND0

BCLKP

BCLKN

TDO

NC2

TCK

NC1

TRST#

TMS

TDI

0.1U_0402_16V4Z~D

Y2

U5

R3

W6

U4

Y5

U1

R4

T5

T3

W2

W5

Y4

U2

V4

W3

AA4

AB2

AA3

V1

H_BR0#

28

27

26

25

24

23

22

21

20

19

18

17

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

H_DEFER# 10

H_DRDY# 10

H_DBSY# 10

C485

H_STPCLK#

H_INTR

H_NMI

H_SMI#

H_A#17

H_A#18

H_A#19

H_A#20

H_A#21

H_A#22

H_A#23

H_A#24

H_A#25

H_A#26

H_A#27

H_A#28

H_A#29

H_A#30

H_A#31

H_A#32

H_A#33

H_A#34

H_A#35

H_ADSTB#1

F1

DEFER#

DRDY#

DBSY#

0.1U_0402_16V4Z~D

22

22

22

22

REQ[0]#

REQ[1]#

REQ[2]#

REQ[3]#

REQ[4]#

H5

F21

E1

H_DEFER#

H_DRD Y#

H_DBSY#

H_ADS# 10

H_BNR# 10

H_BPRI# 10

ITP_DBRESET#

ICH

22 H_A20M#

22 H_FERR#

22 H_IGNNE#

K3

H2

K2

J3

L1

H_ADS#

H_BNR#

H_BPRI#

Place near JITP

RESERVED

10

H_REQ#0

H_REQ#1

H_REQ#2

H_REQ#3

H_REQ#4

H1

E2

G5

ADS#

BNR#

BPRI#

ADDR GROUP 1

A[3]#

A[4]#

A[5]#

A[6]#

A[7]#

A[8]#

A[9]#

A[10]#

A[11]#

A[12]#

A[13]#

A[14]#

A[15]#

A[16]#

ADSTB[0]#

H_REQ#0

H_REQ#1

H_REQ#2

H_REQ#3

H_REQ#4

J4

L5

L4

K5

M3

N2

J1

N3

P5

P2

L2

P4

P1

R1

M1

ADDR GROUP 0

10

10

10

10

10

H_ADSTB#0

H_A#3

H_A#4

H_A#5

H_A#6

H_A#7

H_A#8

H_A#9

H_A#10

H_A#11

H_A#12

H_A#13

H_A#14

H_A#15

H_A#16

H_ADSTB#0

GND6

JITP

10

+1.05V_VCCP

H_A#[3..35]

10

+3.3V_SUS

R324

150_0402_5%~D

ITP_DBRESET#

1

2

TYCO_1-1674770-2_Merom~D

+1.05V_VCCP

R325

51_0402_5%~D

B

ITP_TDO

R326

51_0402_1%~D

+1.05V_VCCP

R327

56_0402_5%~D

1

2 H_THERMTRIP#

H_RESET#

R328

39_0402_1%~D

ITP_TMS

R330

150_0402_5%~D

ITP_TDI

This shall place near CPU

R331

649_0402_1%~D

1

2

ITP_TRST#

VSS[001]

VSS[002]

VSS[003]

VSS[004]

VSS[005]

VSS[006]

VSS[007]

VSS[008]

VSS[009]

VSS[010]

VSS[011]

VSS[012]

VSS[013]

VSS[014]

VSS[015]

VSS[016]

VSS[017]

VSS[018]

VSS[019]

VSS[020]

VSS[021]

VSS[022]

VSS[023]

VSS[024]

VSS[025]

VSS[026]

VSS[027]

VSS[028]

VSS[029]

VSS[030]

VSS[031]

VSS[032]

VSS[033]

VSS[034]

VSS[035]

VSS[036]

VSS[037]

VSS[038]

VSS[039]

VSS[040]

VSS[041]

VSS[042]

VSS[043]

VSS[044]

VSS[045]

VSS[046]

VSS[047]

VSS[048]

VSS[049]

VSS[050]

VSS[051]

VSS[052]

VSS[053]

VSS[054]

VSS[055]

VSS[056]

VSS[057]

VSS[058]

VSS[059]

VSS[060]

VSS[061]

VSS[062]

VSS[063]

VSS[064]

VSS[065]

VSS[066]

VSS[067]

VSS[068]

VSS[069]

VSS[070]

VSS[071]

VSS[072]

VSS[073]

VSS[074]

VSS[075]

VSS[076]

VSS[077]

VSS[078]

VSS[079]

VSS[080]

VSS[081]

VSS[082]

VSS[083]

VSS[084]

VSS[085]

VSS[086]

VSS[087]

VSS[088]

VSS[089]

VSS[090]

VSS[091]

VSS[092]

VSS[093]

VSS[094]

VSS[095]

VSS[096]

VSS[097]

VSS[098]

VSS[099]

VSS[100]

VSS[101]

VSS[102]

VSS[103]

VSS[104]

VSS[105]

VSS[106]

VSS[107]

VSS[108]

VSS[109]

VSS[110]

VSS[111]

VSS[112]

VSS[113]

VSS[114]

VSS[115]

VSS[116]

VSS[117]

VSS[118]

VSS[119]

VSS[120]

VSS[121]

VSS[122]

VSS[123]

VSS[124]

VSS[125]

VSS[126]

VSS[127]

VSS[128]

VSS[129]

VSS[130]

VSS[131]

VSS[132]

VSS[133]

VSS[134]

VSS[135]

VSS[136]

VSS[137]

VSS[138]

VSS[139]

VSS[140]

VSS[141]

VSS[142]

VSS[143]

VSS[144]

VSS[145]

VSS[146]

VSS[147]

VSS[148]

VSS[149]

VSS[150]

VSS[151]

VSS[152]

VSS[153]

VSS[154]

VSS[155]

VSS[156]

VSS[157]

VSS[158]

VSS[159]

VSS[160]

VSS[161]

VSS[162]

VSS[163]

P6

P21

P24

R2

R5

R22

R25

T1

T4

T23

T26

U3

U6

U21

U24

V2

V5

V22

V25

W1

W4

W23

W26

Y3

Y6

Y21

Y24

AA2

AA5

AA8

AA11

AA14

AA16

AA19

AA22

AA25

AB1

AB4

AB8

AB11

AB13

AB16

AB19

AB23

AB26

AC3

AC6

AC8

AC11

AC14

AC16

AC19

AC21

AC24

AD2

AD5

AD8

AD11

AD13

AD16

AD19

AD22

AD25

AE1

AE4

AE8

AE11

AE14

AE16

AE19

AE23

AE26

A2

AF6

AF8

AF11

AF13

AF16

AF19

AF21

A25

AF25

TYCO_1-1674770-2_Merom~D

R332

27_0402_1%~D

ITP_TCK

DELL CONFIDENTIAL/PROPRIETARY

Compal Electronics, Inc.

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

5

Title

Merom Processor(1/2)

Size

Document Number

Date:

Thursday, March 01, 2007

Rev

0.4

LA-3302P

Sheet

1

of

66

+VCC_CORE

+VCC_CORE

JCPUC

10

H_D#[0..63]

1

2

1

2

10,22,48

22

10

22

10

48

BSEL[0]

BSEL[1]

BSEL[2]

H_DPRSTP#

H_DPSLP#

H_DPWR#

H_PWRGOOD

H_CPUSLP#

H_PSI#

H_DPRSTP#

H_DPSLP#

H_DPWR#

H_PW RGOOD

H_CPUSLP#

H_PSI#

G21

V6

J6

K6

M6

J21

K21

M21

N21

N6

R21

R6

T21

T6

V21

W21

VCCA[1]

VCCA[2]

B26

C26

VID[0]

VID[1]

VID[2]

VID[3]

VID[4]

VID[5]

VID[6]

AD6

AF5

AE5

AF4

AE3

AF3

AE2

VID0

VID1

VID2

VID3

VID4

VID5

VID6

VCCSENSE

AF7

VCCSENSE

VSSSENSE

AE7

VSSSENSE

+1.05V_VCCP

1

+

2

CRB was 270uF

VID0

VID1

VID2

VID3

VID4

VID5

VID6

48

48

48

48

48

48

48

VCCSENSE

48

VSSSENSE

48

+1.5V_RUN

C489

E5

B5

D24

D6

D7

AE6

VCCP[01]

VCCP[02]

VCCP[03]

VCCP[04]

VCCP[05]

VCCP[06]

VCCP[07]

VCCP[08]

VCCP[09]

VCCP[10]

VCCP[11]

VCCP[12]

VCCP[13]

VCCP[14]

VCCP[15]

VCCP[16]

10U_0805_10V4Z~D

C488

DPRSTP#

DPSLP#

DPWR#

PWRGOOD

SLP#

PSI#

R340

COMP0

COMP1

COMP2

COMP3

27.4_0402_1%~D

R26

U26

AA1

Y1

54.9_0402_1%~D

COMP[0]

COMP[1]

COMP[2]

COMP[3]

MISC

R339

CPU_MCH_BSEL0 B22

CPU_MCH_BSEL1 B23

CPU_MCH_BSEL2 C21

H_DSTBN#3 10

H_DSTBP#3 10

H_DINV#3 10

27.4_0402_1%~D

6,10 CPU_MCH_BSEL0

6,10 CPU_MCH_BSEL1

6,10 CPU_MCH_BSEL2

H_D#48

H_D#49

H_D#50

H_D#51

H_D#52

H_D#53

H_D#54

H_D#55

H_D#56

H_D#57

H_D#58

H_D#59

H_D#60

H_D#61

H_D#62

H_D#63

H_DSTBN#3

H_DSTBP#3

H_DINV#3

R338

TSET1

TEST2

TEST3

TEST4

TEST5

TEST6

AE24

AD24

AA21

AB22

AB21

AC26

AD20

AE22

AF23

AC25

AE21

AD21

AC22

AD23

AF22

AC23

AE25

AF24

AC20

R337

GTLREF

C23

D25

C24

AF26

AF1

A26

D[48]#

D[49]#

D[50]#

D[51]#

D[52]#

D[53]#

D[54]#

D[55]#

D[56]#

D[57]#

D[58]#

D[59]#

D[60]#

D[61]#

D[62]#

D[63]#

DSTBN[3]#

DSTBP[3]#

DINV[3]#

H_DSTBN#2 10

H_DSTBP#2 10

H_DINV#2 10

54.9_0402_1%~D

AD26

TEST1

TEST2

TEST3

TEST4

TEST5

TEST6

H_D#32

H_D#33

H_D#34

H_D#35

H_D#36

H_D#37

H_D#38

H_D#39

H_D#40

H_D#41

H_D#42

H_D#43

H_D#44

H_D#45

H_D#46

H_D#47

H_DSTBN#2

H_DSTBP#2

H_DINV#2

AB20

AB7

AC7

AC9

AC12

AC13

AC15

AC17

AC18

AD7

AD9

AD10

AD12

AD14

AD15

AD17

AD18

AE9

AE10

AE12

AE13

AE15

AE17

AE18

AE20

AF9

AF10

AF12

AF14

AF15

AF17

AF18

AF20

0.01U_0402_16V7K~D

V_CPU_GTLREF

Y22

AB24

V24

V26

V23

T22

U25

U23

Y25

W22

Y23

W24

W25

AA23

AA24

AB25

Y26

AA26

U22

VCC[068]

VCC[069]

VCC[070]

VCC[071]

VCC[072]

VCC[073]

VCC[074]

VCC[075]

VCC[076]

VCC[077]

VCC[078]

VCC[079]

VCC[080]

VCC[081]

VCC[082]

VCC[083]

VCC[084]

VCC[085]

VCC[086]

VCC[087]

VCC[088]

VCC[089]

VCC[090]

VCC[091]

VCC[092]

VCC[093]

VCC[094]

VCC[095]

VCC[096]

VCC[097]

VCC[098]

VCC[099]

VCC[100]

C487

H_DSTBN#1

H_DSTBP#1

H_DINV#1

D[16]#

D[17]#

D[18]#

D[19]#

D[20]#

D[21]#

D[22]#

D[23]#

D[24]#

D[25]#

D[26]#

D[27]#

D[28]#

D[29]#

D[30]#

D[31]#

DSTBN[1]#

DSTBP[1]#

DINV[1]#

D[32]#

D[33]#

D[34]#

D[35]#

D[36]#

D[37]#

D[38]#

D[39]#

D[40]#

D[41]#

D[42]#

D[43]#

D[44]#

D[45]#

D[46]#

D[47]#

DSTBN[2]#

DSTBP[2]#

DINV[2]#

VCC[001]

VCC[002]

VCC[003]

VCC[004]

VCC[005]

VCC[006]

VCC[007]

VCC[008]

VCC[009]

VCC[010]

VCC[011]

VCC[012]

VCC[013]

VCC[014]

VCC[015]

VCC[016]

VCC[017]

VCC[018]

VCC[019]

VCC[020]

VCC[021]

VCC[022]

VCC[023]

VCC[024]

VCC[025]

VCC[026]

VCC[027]

VCC[028]

VCC[029]

VCC[030]

VCC[031]

VCC[032]

VCC[033]

VCC[034]

VCC[035]

VCC[036]

VCC[037]

VCC[038]

VCC[039]

VCC[040]

VCC[041]

VCC[042]

VCC[043]

VCC[044]

VCC[045]

VCC[046]

VCC[047]

VCC[048]

VCC[049]

VCC[050]

VCC[051]

VCC[052]

VCC[053]

VCC[054]

VCC[055]

VCC[056]

VCC[057]

VCC[058]

VCC[059]

VCC[060]

VCC[061]

VCC[062]

VCC[063]

VCC[064]

VCC[065]

VCC[066]

VCC[067]

220U_D2_4VY_R15M~D

10

10

10

N22

K25

P26

R23

L23

M24

L22

M23

P25

P23

P22

T24

R24

L25

T25

N25

L26

M26

N24

DATA GRP 1

H_D#16

H_D#17

H_D#18

H_D#19

H_D#20

H_D#21

H_D#22

H_D#23

H_D#24

H_D#25

H_D#26

H_D#27

H_D#28

H_D#29

H_D#30

H_D#31

H_DSTBN#1

H_DSTBP#1

H_DINV#1

DATA GRP 3

H_DSTBN#0

H_DSTBP#0

H_DINV#0

D[0]#

D[1]#

D[2]#

D[3]#

D[4]#

D[5]#

D[6]#

D[7]#

D[8]#

D[9]#

D[10]#

D[11]#

D[12]#

D[13]#

D[14]#

D[15]#

DSTBN[0]#

DSTBP[0]#

DINV[0]#

DATA GRP 0

10

10

10

E22

F24

E26

G22

F23

G25

E25

E23

K24

G24

J24

J23

H22

F26

K22

H23

J26

H26

H25

DATA GRP 2

JCPUB

H_D#0

H_D#1

H_D#2

H_D#3

H_D#4

H_D#5

H_D#6

H_D#7

H_D#8

H_D#9

H_D#10

H_D#11

H_D#12

H_D#13

H_D#14

H_D#15

H_DSTBN#0

H_DSTBP#0

H_DINV#0

A7

A9

A10

A12

A13

A15

A17

A18

A20

B7

B9

B10

B12

B14

B15

B17

B18

B20

C9

C10

C12

C13

C15

C17

C18

D9

D10

D12

D14

D15

D17

D18

E7

E9

E10

E12

E13

E15

E17

E18

E20

F7

F9

F10

F12

F14

F15

F17

F18

F20

AA7

AA9

AA10

AA12

AA13

AA15

AA17

AA18

AA20

AB9

AC10

AB10

AB12

AB14

AB15

AB17

AB18

TYCO_1-1674770-2_Merom~D

TYCO_1-1674770-2_Merom~D

Resistor placed within 0.5" of

CPU pin.Trace should be at least

25 mils away from any other

toggling signal. COMP0, COMP2

trace should be 27.4 ohm.

COMP1, COMP3 should be 55

ohm.

R394

0_0402_5%~D

1

2

C490

0.1U_0402_16V4Z~D

@R336

1K_0402_5%~D

1

2

@R335

1K_0402_5%~D

1

2

TEST1

TEST2

TEST4

TEST6

PAD~D T30

PAD~D T31

TEST3

TEST5

Length match within 25 mils, Z0=27.4 ohm

B

Place R342 and R343 near CPU

+VCC_CORE

R342

For the purpose of testability, route these signals

through a ground referenced Z0 = 55ohm trace that

ends in a via that is near a GND via and is

accessible through an oscilloscope connection.

VCCSENSE

100_0402_1%~D

R343

1

VSSSENSE

100_0402_1%~D

FSB

BCLK

BSEL2

BSEL1

BSEL0

533

133

667

166

+1.05V_VCCP

Route VCCSENSE and VSSSENSE trace at

27.4 ohms, 7 mils spacing and 1 inch (max)

Place C490 close to the

CPU_TEST4 pin. Make sure

CPU_TEST4 routing is

reference to GND and away

from other noisy signal.

R341

V_CPU_GTLREF

200

1K_0402_1%~D

2

800

R344

2K_0402_1%~D

2

DELL CONFIDENTIAL/PROPRIETARY

Compal Electronics, Inc.

Layout close CPU PIN AD26

55 ohm, 0.5 inch (max)

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

3

Title

Merom Processor(2/2)

Size

Document Number

Date:

Thursday, March 01, 2007

Rev

0.4

LA-3302P

Sheet

1

of

66

+VCC_CORE

Place these inside 1

socket cavity on L8

(North side

Secondary)

2

1

C329

10U_0805_4VAM~D

2

1

C330

10U_0805_4VAM~D

1

C331

10U_0805_4VAM~D

1

C332

10U_0805_4VAM~D

C333

10U_0805_4VAM~D

C334

10U_0805_4VAM~D

2

1

C335

10U_0805_4VAM~D

1

C336

10U_0805_4VAM~D

1

C55

10U_0805_4VAM~D

C190

10U_0805_4VAM~D

+VCC_CORE

Place these inside 1

socket cavity on L8

(Sorth side

Secondary)

2

1

C222

10U_0805_4VAM~D

2

1

C223

10U_0805_4VAM~D

1

C224

10U_0805_4VAM~D

1

C225

10U_0805_4VAM~D

C227

10U_0805_4VAM~D

C226

10U_0805_4VAM~D

2

1

C228

10U_0805_4VAM~D

1

C229

10U_0805_4VAM~D

1

C69

10U_0805_4VAM~D

C185

10U_0805_4VAM~D

+VCC_CORE

Place these inside 1

socket cavity on L8

(North side

Primary)

2

1

C363

10U_0805_4VAM~D

2

1

C64

10U_0805_4VAM~D

1

C65

10U_0805_4VAM~D

1

C66

10U_0805_4VAM~D

1

C67

10U_0805_4VAM~D

C68

10U_0805_4VAM~D

+VCC_CORE

Place these inside 1

socket cavity on L8

(Sorth side

Primary)

2

1

C364

10U_0805_4VAM~D

2

1

C50

10U_0805_4VAM~D

1

C51

10U_0805_4VAM~D

1

C52

10U_0805_4VAM~D

10uF 0805 X6S -> 85 degree C

1

C53

10U_0805_4VAM~D

C54

10U_0805_4VAM~D

C

High Frequence Decoupling

Near VCORE regulator.

1

+

2

1

+

2

C365

220U_X_2VM_R7M~D

@ C338

220U_X_2VM_R7M~D

C366

220U_X_2VM_R7M~D

@ C178

220U_X_2VM_R7M~D

+VCC_CORE

C179

220U_X_2VM_R7M~D

South Side Secondary

C177

220U_X_2VM_R7M~D

+VCC_CORE

1

+

2

North Side Secondary

ESR <= 1.5m ohm

Capacitor > 1980uF

+

2

1

C870

0.1U_0402_10V7K~D

@

1

C871

0.1U_0402_10V7K~D

@

1

C872

0.1U_0402_10V7K~D

@

C873

0.1U_0402_10V7K~D

@

BITs WI97837

+1.05V_VCCP

1

C312

0.1U_0402_10V7K~D

1

C256

0.1U_0402_10V7K~D

1

C293

0.1U_0402_10V7K~D

1

C250

0.1U_0402_10V7K~D

1

C310

0.1U_0402_10V7K~D

C264

0.1U_0402_10V7K~D

Place these inside

socket cavity on L8

(North side

Secondary)

DELL CONFIDENTIAL/PROPRIETARY

Compal Electronics, Inc.

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

Title

CPU Bypass

Size

Document Number

Date:

Monday, February 26, 2007

Rev

0.4

LA-3302P

Sheet

1

of

66

H_SCOMP

H_SCOMP#

H_RESET#

H_CPUSLP#

B6

E5

H_CPURST#

H_CPUSLP#

H_DSTBN#0

H_DSTBN#1

H_DSTBN#2

H_DSTBN#3

H_DSTBN#0

H_DSTBN#1

H_DSTBN#2

H_DSTBN#3

8

8

8

8

H_DSTBP#_0

H_DSTBP#_1

H_DSTBP#_2

H_DSTBP#_3

L7

K2

AC2

AJ10

H_DSTBP#0

H_DSTBP#1

H_DSTBP#2

H_DSTBP#3

H_DSTBP#0

H_DSTBP#1

H_DSTBP#2

H_DSTBP#3

8

8

8

8

H_REQ#_0

H_REQ#_1

H_REQ#_2

H_REQ#_3

H_REQ#_4

M14

E13

A11

H13

B12

H_REQ#0

H_REQ#1

H_REQ#2

H_REQ#3

H_REQ#4

H_RS#_0

H_RS#_1

H_RS#_2

E12

D7

D8

H_RS#0

H_RS#1

H_RS#2

R350

B9

A9

H_VREF

H_AVREF

H_DVREF

R346

20_0402_1%~D

C491

0.1U_0402_16V4Z~D

V_DDR_MCH_REF

1

6 CLK_MCH_3GPLL

6 CLK_MCH_3GPLL#

8

8

8

8

H_REQ#0

H_REQ#1

H_REQ#2

H_REQ#3

H_REQ#4

H_RS#0

H_RS#1

H_RS#2

7

7

7

1

2

C498

0.01U_0402_16V7K~D

R363

1K_0402_1%~D

23

23

23

23

DMI_MRX_ITX_P0

DMI_MRX_ITX_P1

DMI_MRX_ITX_P2

DMI_MRX_ITX_P3

23

23

23

23

DMI_MTX_IRX_N0

DMI_MTX_IRX_N1

DMI_MTX_IRX_N2

DMI_MTX_IRX_N3

23

23

23

23

DMI_MTX_IRX_P0

DMI_MTX_IRX_P1

DMI_MTX_IRX_P2

DMI_MTX_IRX_P3

SM_RCOMP

SM_RCOMP#

BK31

BL31

SM_RCOMP_VOH

SM_RCOMP_VOL

V_DDR_MCH_REF

AR49

AW4

SM_VREF_0

SM_VREF_1

CLK_MCH_3GPLL

CLK_MCH_3GPLL#

B42

C42

H48

H47

DPLL_REF_CLK

DPLL_REF_CLK#

DPLL_REF_SSCLK

DPLL_REF_SSCLK#

K44

K45

PEG_CLK

PEG_CLK#

DMI_MRX_ITX_N0

DMI_MRX_ITX_N1

DMI_MRX_ITX_N2

DMI_MRX_ITX_N3

AN47

AJ38

AN42

AN46

DMI_RXN_0

DMI_RXN_1

DMI_RXN_2

DMI_RXN_3

DMI_MRX_ITX_P0

DMI_MRX_ITX_P1

DMI_MRX_ITX_P2

DMI_MRX_ITX_P3

AM47

AJ39

AN41

AN45

DMI_RXP_0

DMI_RXP_1

DMI_RXP_2

DMI_RXP_3

DMI_MTX_IRX_N0

DMI_MTX_IRX_N1

DMI_MTX_IRX_N2

DMI_MTX_IRX_N3

AJ46

AJ41

AM40

AM44

DMI_TXN_0

DMI_TXN_1

DMI_TXN_2

DMI_TXN_3

DMI_MTX_IRX_P0

DMI_MTX_IRX_P1

DMI_MTX_IRX_P2

DMI_MTX_IRX_P3

AJ47

AJ42

AM39

AM43

DMI_TXP_0

DMI_TXP_1

DMI_TXP_2

DMI_TXP_3

T42

T43

T44

T45

E35

A39

C38

B39

GFX_VID_0

GFX_VID_1

GFX_VID_2

GFX_VID_3

PAD~D T46

E36

GFX_VR_EN

CL_CLK0

CL_DATA0

ICH_CL_PWROK

CL_RST0#

CL_VREF

6 CLK_3GPLLREQ#

23 MCH_ICH_SYNC#

CLK_3GPLLREQ#

MCH_ICH_SYNC#

R774

2

2

AM49

AK50

AT43

AN49

AM50

CL_CLK

CL_DATA

CL_PWROK

CL_RST#

CL_VREF

H35

K36

G39

G40

0_0402_5%~D

A37

1

R32

1

SDVO_CTRL_CLK

SDVO_CTRL_DATA

CLK_REQ#

ICH_SYNC#

TEST_1

TEST_2

R357

20K_0402_5%~D

RSVD1

RSVD2

RSVD3

RSVD4

RSVD5

RSVD6

RSVD7

RSVD8

RSVD9

RSVD10

RSVD11

RSVD12

RSVD13

RSVD14

P36

P37

R35

N35

AR12

AR13

AM12

AN13

J12

AR37

AM36

AL36

AM37

D20

RSVD20

RSVD21

RSVD22

RSVD23

RSVD24

RSVD25

RSVD26

RSVD27

RSVD28

RSVD29

RSVD30

RSVD31

RSVD32

RSVD33

RSVD34

RSVD35

RSVD36

RSVD37

RSVD38

RSVD39

RSVD40

RSVD41

RSVD42

RSVD43

H10

B51

BJ20

BK22

BF19

BH20

BK18

BJ18

BF23

BG23

BC23

BD24

BH39

AW20

BK20

C48

D47

B44

C44

A35

B37

B36

B34

C34

CFG_0

CFG_1

CFG_2

CFG_3

CFG_4

CFG_5

CFG_6

CFG_7

CFG_8

CFG_9

CFG_10

CFG_11

CFG_12

CFG_13

CFG_14

CFG_15

CFG_16

CFG_17

CFG_18

CFG_19

CFG_20

P27

N27

N24

C21

C23

F23

N23

G23

J20

C20

R24

L23

J23

E23

E20

K23

M20

M24

L32

N33

L35

CFG5

CFG9

CFG16

CFG19

CFG20

PM_BM_BUSY#

PM_DPRSTP#

PM_EXT_TS#_0

PM_EXT_TS#_1

PWROK

RSTIN#

THERMTRIP#

DPRSLPVR

G41

L39

L36

J36

AW49

AV20

N20

G36

NC_1

NC_2

NC_3

NC_4

NC_5

NC_6

NC_7

NC_8

NC_9

NC_10

NC_11

NC_12

NC_13

NC_14

NC_15

NC_16

BJ51

BK51

BK50

BL50

BL49

BL3

BL2

BK1

BJ1

E1

A5

C51

B50

A50

A49

BK2

CPU_MCH_BSEL0 6,8

CPU_MCH_BSEL1 6,8

CPU_MCH_BSEL2 6,8

T63 PAD~D

T64 PAD~D

CFG5

12

T65 PAD~D

T66 PAD~D

T67 PAD~D

CFG9

12

T68 PAD~D

T69 PAD~D

T70 PAD~D

T71 PAD~D

T72 PAD~D

T73 PAD~D

CFG16

12

T74 PAD~D

T75 PAD~D

CFG19

12

CFG20

12

PM_BMBUSY#

H_DPRSTP#

PM_EXTTS#0

PM_EXTTS#1

ICH_PWRGD

PLTRST1#_R

THERMTRIP_MCH#

DPRSLPVR

+1.05V_VCCP

PM_BMBUSY#

H_DPRSTP#

PM_EXTTS#0

PM_EXTTS#1

ICH_PWRGD

23

8,22,48

16

17

23,42

THERMTRIP_MCH# 18

DPRSLPVR

23,48

PM_EXTTS#0

+3.3V_RUN

R352

10K_0402_5%~D

2

1

R354

10K_0402_5%~D

PM_EXTTS#1 2

1

R589

@ 0_0402_5%~D

2

1

R36

LE88CLPM A0 QM21_FCBGA1299~D

100_0402_5%~D

PLTRST1#_R 1

2

THERMTRIP_MCH# 1

R358

56_0402_5%~D

SMRCOMP_VOL

2

2

C497

0.1U_0402_16V4Z~D

2K_0402_1%~D

R362

100_0402_1%~D

C496

0.1U_0402_16V4Z~D

H_SWNG

R361

BL15

BK14

C495

2.2U_0603_6.3V6K~D

R359

3.01K_0402_1%~D

C494

0.01U_0402_16V7K~D

221_0402_1%~D

H_VREF

1K_0402_1%~D

SMRCOMP

SMRCOMP#

SMRCOMP_VOH

SMRCOMP_VOL

C493

0.1U_0402_16V4Z~D

SMRCOMP_VOH

+1.05V_VCCP

SM_ODT_0

SM_ODT_1

SM_ODT_2

SM_ODT_3

1

R351

392_0402_1~D

R353

1K_0402_1%~D

R356

DMI_MRX_ITX_N0

DMI_MRX_ITX_N1

DMI_MRX_ITX_N2

DMI_MRX_ITX_N3

23

CL_CLK0

23

CL_DATA0

23,39 ICH_CL_PWROK

23 CL_RST0#

R349

1K_0402_1%~D

+1.8V_SUS

R355

BH18

BJ15

BJ14

BE16

NC

+1.05V_VCCP

Layout Note:

H_RCOMP trace width

and spacing is 10/20

M_ODT0

M_ODT1

M_ODT2

M_ODT3

+1.25V_RUN

C499

2.2U_0603_6.3V6K~D

LE88CLPM A0 QM21_FCBGA1299~D

23

23

23

23

PAD~D

PAD~D

PAD~D

PAD~D

7

7

7

7

7

SM_CS#_0

SM_CS#_1

SM_CS#_2

SM_CS#_3

H_ADS#

7

H_ADSTB#0

7

H_ADSTB#1

7

H_BNR#

7

H_BPRI#

7

H_BR0#

7

H_DEFER#

7

H_DBSY#

7

CLK_MCH_BCLK 6

CLK_MCH_BCLK# 6

H_DPWR#

8

H_DRDY#

7

H_HIT#

7

H_HITM#

7

H_LOCK# 7

H_TRDY#

7

H_DINV#0

H_DINV#1

H_DINV#2

H_DINV#3

BG20

BK16

BG16

BE13

24.9_0402_1%~D

M_ODT0

M_ODT1

M_ODT2

M_ODT3

DDR_CS0_DIMMA#

DDR_CS1_DIMMA#

DDR_CS2_DIMMB#

DDR_CS3_DIMMB#

DDR

M7

K3

AD2

AH11

R345

20_0402_1%~D

1

2

1

2

16

16

17

17

SM_CKE_0

SM_CKE_1

SM_CKE_3

SM_CKE_4

CLK

H_DSTBN#_0

H_DSTBN#_1

H_DSTBN#_2

H_DSTBN#_3

DDR_CS0_DIMMA#

DDR_CS1_DIMMA#

DDR_CS2_DIMMB#

DDR_CS3_DIMMB#

BE29

AY32

BD39

BG37

DMI

H_DINV#0

H_DINV#1

H_DINV#2

H_DINV#3

H_SWING

H_RCOMP

K5

L2

AD13

AE13

16

16

17

17

DDR_CKE0_DIMMA

DDR_CKE1_DIMMA

DDR_CKE2_DIMMB

DDR_CKE3_DIMMB

ME

W1

W2

H_DINV#_0

H_DINV#_1

H_DINV#_2

H_DINV#_3

H_ADS#

H_ADSTB#_0

H_ADSTB#_1

H_BNR#

H_BPRI#

H_BREQ#

H_DEFER#

H_DBSY#

HPLL_CLK

HPLL_CLK#

H_DPWR#

H_DRDY#

H_HIT#

H_HITM#

H_LOCK#

H_TRDY#

DDR_CKE0_DIMMA

DDR_CKE1_DIMMA

DDR_CKE2_DIMMB

DDR_CKE3_DIMMB

SM_CK#_0

SM_CK#_1

SM_CK#_3

SM_CK#_4

MISC

H_RESET#

H_CPUSLP#

B3

C2

H_SCOMP

H_SCOMP#

G12

H17

G20

C8

E8

F12

D6

C10

AM5

AM7

H8

K7

E4

C6

G10

B7

H_ADS#

H_ADSTB#0

H_ADSTB#1

H_BNR#

H_BPRI#

H_BR0#

H_DEFER#

H_DBSY#

CLK_MCH_BCLK

CLK_MCH_BCLK#

H_DPWR#

H_DRD Y#

H_HIT#

H_HITM#

H_LOCK#

H_TRDY#

+1.8V_SUS

16

16

17

17

AW30

BA23

AW25

AW23

PM

7

8

H_SWNG

H_RCOMP

H_A#3

H_A#4

H_A#5

H_A#6

H_A#7

H_A#8

H_A#9

H_A#10

H_A#11

H_A#12

H_A#13

H_A#14

H_A#15

H_A#16

H_A#17

H_A#18

H_A#19

H_A#20

H_A#21

H_A#22

H_A#23

H_A#24

H_A#25

H_A#26

H_A#27

H_A#28

H_A#29

H_A#30

H_A#31

H_A#32

H_A#33

H_A#34

H_A#35

M_CLK_DDR#0

M_CLK_DDR#1

M_CLK_DDR#2

M_CLK_DDR#3

1

2

54.9_0402_1%~D

J13

B11

C11

M11

C15

F16

L13

G17

C14

K16

B13

L16

J17

B14

K19

P15

R17

B16

H20

L19

D17

M17

N16

J19

B18

E19

B17

B15

E17

C18

A19

B19

N19

H_A#_3

H_A#_4

H_A#_5

H_A#_6

H_A#_7

H_A#_8

H_A#_9

H_A#_10

H_A#_11

H_A#_12

H_A#_13

H_A#_14

H_A#_15

H_A#_16

H_A#_17

H_A#_18

H_A#_19

H_A#_20

H_A#_21

H_A#_22

H_A#_23

H_A#_24

H_A#_25

H_A#_26

H_A#_27

H_A#_28

H_A#_29

H_A#_30

H_A#_31

H_A#_32

H_A#_33

H_A#_34

H_A#_35

M_CLK_DDR#0

M_CLK_DDR#1

M_CLK_DDR#2

M_CLK_DDR#3

SM_CK_0

SM_CK_1

SM_CK_3

SM_CK_4

CFG

R347

54.9_0402_1%~D

R348

H_D#_0

H_D#_1

H_D#_2

H_D#_3

H_D#_4

H_D#_5

H_D#_6

H_D#_7

H_D#_8

H_D#_9

H_D#_10

H_D#_11

H_D#_12

H_D#_13

H_D#_14

H_D#_15

H_D#_16

H_D#_17

H_D#_18

H_D#_19

H_D#_20

H_D#_21

H_D#_22

H_D#_23

H_D#_24

H_D#_25

H_D#_26

H_D#_27

H_D#_28

H_D#_29

H_D#_30

H_D#_31

H_D#_32

H_D#_33

H_D#_34

H_D#_35

H_D#_36

H_D#_37

H_D#_38

H_D#_39

H_D#_40

H_D#_41

H_D#_42

H_D#_43

H_D#_44

H_D#_45

H_D#_46

H_D#_47

H_D#_48

H_D#_49

H_D#_50

H_D#_51

H_D#_52

H_D#_53

H_D#_54

H_D#_55

H_D#_56

H_D#_57

H_D#_58

H_D#_59

H_D#_60

H_D#_61

H_D#_62

H_D#_63

16

16

17

17

AV29

BB23

BA25

AV23

RSVD

+1.05V_VCCP

E2

G2

G7

M6

H7

H3

G4

F3

N8

H2

M10

N12

N9

H5

P13

K9

M2

W10

Y8

V4

M3

J1

N5

N3

W6

W9

N2

Y7

Y9

P4

W3

N1

AD12

AE3

AD9

AC9

AC7

AC14

AD11

AC11

AB2

AD7

AB1

Y3

AC6

AE2

AC5

AG3

AJ9

AH8

AJ14

AE9

AE11

AH12

AJ5

AH5

AJ6

AE7

AJ7

AJ2

AE5

AJ3

AH2

AH13

M_CLK_DDR0

M_CLK_DDR1

M_CLK_DDR2

M_CLK_DDR3

GRAPHICS VID

U29A

H_D#0

H_D#1

H_D#2

H_D#3

H_D#4

H_D#5

H_D#6

H_D#7

H_D#8

H_D#9

H_D#10

H_D#11

H_D#12

H_D#13

H_D#14

H_D#15

H_D#16

H_D#17

H_D#18

H_D#19

H_D#20

H_D#21

H_D#22

H_D#23

H_D#24

H_D#25

H_D#26

H_D#27

H_D#28

H_D#29

H_D#30

H_D#31

H_D#32

H_D#33

H_D#34

H_D#35

H_D#36

H_D#37

H_D#38

H_D#39

H_D#40

H_D#41

H_D#42

H_D#43

H_D#44

H_D#45

H_D#46

H_D#47

H_D#48

H_D#49

H_D#50

H_D#51

H_D#52

H_D#53

H_D#54

H_D#55

H_D#56

H_D#57

H_D#58

H_D#59

H_D#60

H_D#61

H_D#62

H_D#63

H_A#[3..35]

C492

0.1U_0402_16V4Z~D

H_D#[0..63]

HOST

16

16

17

17

MUXING

U29B

M_CLK_DDR0

M_CLK_DDR1

M_CLK_DDR2

M_CLK_DDR3

SB_NB_PCIE_RST# 21

R583

0_0402_5%~D

2

1PLTRST1#

PLTRST1#

21

DELL CONFIDENTIAL/PROPRIETARY

Compal Electronics, Inc.

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

Title

Crestline(1 of 6)

Size

Date:

Document Number

Rev

0.4

LA-3302P

Thursday, March 01, 2007

Sheet

1

10

of

66

DDR_A_D[0..63] 16

AT45

BD44

BD42

AW38

AW13

BG8

AY5

AN6

SA_DM_0

SA_DM_1

SA_DM_2

SA_DM_3

SA_DM_4

SA_DM_5

SA_DM_6

SA_DM_7

DDR_A_DQS0

DDR_A_DQS1

DDR_A_DQS2

DDR_A_DQS3

DDR_A_DQS4

DDR_A_DQS5

DDR_A_DQS6

DDR_A_DQS7

AT46

BE48

BB43

BC37

BB16

BH6

BB2

AP3

SA_DQS_0

SA_DQS_1

SA_DQS_2

SA_DQS_3

SA_DQS_4

SA_DQS_5

SA_DQS_6

SA_DQS_7

AT47

BD47

BC41

BA37

BA16

BH7

BC1

AP2

SA_DQS#_0

SA_DQS#_1

SA_DQS#_2

SA_DQS#_3

SA_DQS#_4

SA_DQS#_5

SA_DQS#_6

SA_DQS#_7

DDR_A_MA0

DDR_A_MA1

DDR_A_MA2

DDR_A_MA3

DDR_A_MA4

DDR_A_MA5

DDR_A_MA6

DDR_A_MA7

DDR_A_MA8

DDR_A_MA9

DDR_A_MA10

DDR_A_MA11

DDR_A_MA12

DDR_A_MA13

DDR_A_MA14

BJ19

BD20

BK27

BH28

BL24

BK28

BJ27

BJ25

BL28

BA28

BC19

BE28

BG30

BJ16

BJ29

SA_MA_0

SA_MA_1

SA_MA_2

SA_MA_3

SA_MA_4

SA_MA_5

SA_MA_6

SA_MA_7

SA_MA_8

SA_MA_9

SA_MA_10

SA_MA_11

SA_MA_12

SA_MA_13

SA_MA_14

BL17

BE18

BA19

SA_CAS#

SA_RAS#

SA_WE#

AY20

SA_RCVEN#

16 DDR_A_MA[0..14]

16 DDR_A_CAS#

16 DDR_A_RAS#

16 DDR_A_WE#

T10

DDR_A_CAS#

DDR_A_RAS#

DDR_A_WE#

SA_RCVEN#

MEMORY

DDR_A_DQS#0

DDR_A_DQS#1

DDR_A_DQS#2

DDR_A_DQS#3

DDR_A_DQS#4

DDR_A_DQS#5

DDR_A_DQS#6

DDR_A_DQS#7

SYSTEM

16 DDR_A_DQS#[0..7]

DDR

16 DDR_A_DQS[0..7]

AR43

AW44

BA45

AY46

AR41

AR45

AT42

AW47

BB45

BF48

BG47

BJ45

BB47

BG50

BH49

BE45

AW43

BE44

BG42

BE40

BF44

BH45

BG40

BF40

AR40

AW40

AT39

AW36

AW41

AY41

AV38

AT38

AV13

AT13

AW11

AV11

AU15

AT11

BA13

BA11

BE10

BD10

BD8

AY9

BG10

AW9

BD7

BB9

BB5

AY7

AT5

AT7

AY6

BB7

AR5

AR8

AR9

AN3

AM8

AN10

AT9

AN9

AM9

AN11

DDR_B_D[0..63] 17

U29E

DDR_A_D0

DDR_A_D1

DDR_A_D2

DDR_A_D3

DDR_A_D4

DDR_A_D5

DDR_A_D6

DDR_A_D7

DDR_A_D8

DDR_A_D9

DDR_A_D10

DDR_A_D11

DDR_A_D12

DDR_A_D13

DDR_A_D14

DDR_A_D15

DDR_A_D16

DDR_A_D17

DDR_A_D18

DDR_A_D19

DDR_A_D20

DDR_A_D21

DDR_A_D22

DDR_A_D23

DDR_A_D24

DDR_A_D25

DDR_A_D26

DDR_A_D27

DDR_A_D28

DDR_A_D29

DDR_A_D30

DDR_A_D31

DDR_A_D32

DDR_A_D33

DDR_A_D34

DDR_A_D35

DDR_A_D36

DDR_A_D37

DDR_A_D38

DDR_A_D39

DDR_A_D40

DDR_A_D41

DDR_A_D42

DDR_A_D43

DDR_A_D44

DDR_A_D45

DDR_A_D46

DDR_A_D47

DDR_A_D48

DDR_A_D49

DDR_A_D50

DDR_A_D51

DDR_A_D52

DDR_A_D53

DDR_A_D54

DDR_A_D55

DDR_A_D56

DDR_A_D57

DDR_A_D58

DDR_A_D59

DDR_A_D60

DDR_A_D61

DDR_A_D62

DDR_A_D63

DDR_B_BS0

DDR_B_BS1

DDR_B_BS2

17 DDR_B_BS0

17 DDR_B_BS1

17 DDR_B_BS2

17 DDR_B_DM[0..7]

AY17

BG18

BG36

SB_BS_0

SB_BS_1

SB_BS_2

DDR_B_DM0

DDR_B_DM1

DDR_B_DM2

DDR_B_DM3

DDR_B_DM4

DDR_B_DM5

DDR_B_DM6

DDR_B_DM7

AR50

BD49

BK45

BL39

BH12

BJ7

BF3

AW2

SB_DM_0

SB_DM_1

SB_DM_2

SB_DM_3

SB_DM_4

SB_DM_5

SB_DM_6

SB_DM_7

DDR_B_DQS0

DDR_B_DQS1

DDR_B_DQS2

DDR_B_DQS3

DDR_B_DQS4

DDR_B_DQS5

DDR_B_DQS6

DDR_B_DQS7

AT50

BD50

BK46

BK39

BJ12

BL7

BE2

AV2

SB_DQS_0

SB_DQS_1

SB_DQS_2

SB_DQS_3

SB_DQS_4

SB_DQS_5

SB_DQS_6

SB_DQS_7

DDR_B_DQS#0

DDR_B_DQS#1

DDR_B_DQS#2

DDR_B_DQS#3

DDR_B_DQS#4

DDR_B_DQS#5

DDR_B_DQS#6

DDR_B_DQS#7

AU50

BC50

BL45

BK38

BK12

BK7

BF2

AV3

SB_DQS#_0

SB_DQS#_1

SB_DQS#_2

SB_DQS#_3

SB_DQS#_4

SB_DQS#_5

SB_DQS#_6

SB_DQS#_7

DDR_B_MA0

DDR_B_MA1

DDR_B_MA2

DDR_B_MA3

DDR_B_MA4

DDR_B_MA5

DDR_B_MA6

DDR_B_MA7

DDR_B_MA8

DDR_B_MA9

DDR_B_MA10

DDR_B_MA11

DDR_B_MA12

DDR_B_MA13

DDR_B_MA14

BC18

BG28

BG25

AW17

BF25

BE25

BA29

BC28

AY28

BD37

BG17

BE37

BA39

BG13

BE24

SB_MA_0

SB_MA_1

SB_MA_2

SB_MA_3

SB_MA_4

SB_MA_5

SB_MA_6

SB_MA_7

SB_MA_8

SB_MA_9

SB_MA_10

SB_MA_11

SB_MA_12

SB_MA_13

SB_MA_14

DDR_B_CAS#

DDR_B_RAS#

DDR_B_WE#

BE17

AV16

BC17

SB_CAS#

SB_RAS#

SB_WE#

SB_RCVEN#

AY18

SB_RCVEN#

17 DDR_B_DQS[0..7]

17 DDR_B_DQS#[0..7]

17 DDR_B_MA[0..14]

17 DDR_B_CAS#

17 DDR_B_RAS#

17 DDR_B_WE#

T11

LE88CLPM A0 QM21_FCBGA1299~D

DDR_A_DM0

DDR_A_DM1

DDR_A_DM2

DDR_A_DM3

DDR_A_DM4

DDR_A_DM5

DDR_A_DM6

DDR_A_DM7

SA_DQ_0

SA_DQ_1

SA_DQ_2

SA_DQ_3

SA_DQ_4

SA_DQ_5

SA_DQ_6

SA_DQ_7

SA_DQ_8

SA_DQ_9

SA_DQ_10

SA_DQ_11

SA_DQ_12

SA_DQ_13

SA_DQ_14

SA_DQ_15

SA_DQ_16

SA_DQ_17

SA_DQ_18

SA_DQ_19

SA_DQ_20

SA_DQ_21

SA_DQ_22

SA_DQ_23

SA_DQ_24

SA_DQ_25

SA_DQ_26

SA_DQ_27

SA_DQ_28

SA_DQ_29

SA_DQ_30

SA_DQ_31

SA_DQ_32

SA_DQ_33

SA_DQ_34

SA_DQ_35

SA_DQ_36

SA_DQ_37

SA_DQ_38

SA_DQ_39

SA_DQ_40

SA_DQ_41

SA_DQ_42

SA_DQ_43

SA_DQ_44

SA_DQ_45

SA_DQ_46

SA_DQ_47

SA_DQ_48

SA_DQ_49

SA_DQ_50

SA_DQ_51

SA_DQ_52

SA_DQ_53

SA_DQ_54

SA_DQ_55

SA_DQ_56

SA_DQ_57

SA_DQ_58

SA_DQ_59

SA_DQ_60

SA_DQ_61

SA_DQ_62

SA_DQ_63

MEMORY

SA_BS_0

SA_BS_1

SA_BS_2

SYSTEM

BB19

BK19

BF29

DDR

U29D

DDR_A_BS0

DDR_A_BS1

DDR_A_BS2

16 DDR_A_BS0

16 DDR_A_BS1

16 DDR_A_BS2

16 DDR_A_DM[0..7]

SB_DQ_0

SB_DQ_1

SB_DQ_2

SB_DQ_3

SB_DQ_4

SB_DQ_5

SB_DQ_6

SB_DQ_7

SB_DQ_8

SB_DQ_9

SB_DQ_10

SB_DQ_11

SB_DQ_12

SB_DQ_13

SB_DQ_14

SB_DQ_15

SB_DQ_16

SB_DQ_17

SB_DQ_18

SB_DQ_19

SB_DQ_20

SB_DQ_21

SB_DQ_22

SB_DQ_23

SB_DQ_24

SB_DQ_25

SB_DQ_26

SB_DQ_27

SB_DQ_28

SB_DQ_29

SB_DQ_30

SB_DQ_31

SB_DQ_32

SB_DQ_33

SB_DQ_34

SB_DQ_35

SB_DQ_36

SB_DQ_37

SB_DQ_38

SB_DQ_39

SB_DQ_40

SB_DQ_41

SB_DQ_42

SB_DQ_43

SB_DQ_44

SB_DQ_45

SB_DQ_46

SB_DQ_47

SB_DQ_48

SB_DQ_49

SB_DQ_50

SB_DQ_51

SB_DQ_52

SB_DQ_53

SB_DQ_54

SB_DQ_55

SB_DQ_56

SB_DQ_57

SB_DQ_58

SB_DQ_59

SB_DQ_60

SB_DQ_61

SB_DQ_62

SB_DQ_63

AP49

AR51

AW50

AW51

AN51

AN50

AV50

AV49

BA50

BB50

BA49

BE50

BA51

AY49

BF50

BF49

BJ50

BJ44

BJ43

BL43

BK47

BK49

BK43

BK42

BJ41

BL41

BJ37

BJ36

BK41

BJ40

BL35

BK37

BK13

BE11

BK11

BC11

BC13

BE12

BC12

BG12

BJ10

BL9

BK5

BL5

BK9

BK10

BJ8

BJ6

BF4

BH5

BG1

BC2

BK3

BE4

BD3

BJ2

BA3

BB3

AR1

AT3

AY2

AY3

AU2

AT2

DDR_B_D0

DDR_B_D1

DDR_B_D2

DDR_B_D3

DDR_B_D4

DDR_B_D5

DDR_B_D6

DDR_B_D7

DDR_B_D8

DDR_B_D9

DDR_B_D10

DDR_B_D11

DDR_B_D12

DDR_B_D13

DDR_B_D14

DDR_B_D15

DDR_B_D16

DDR_B_D17

DDR_B_D18

DDR_B_D19

DDR_B_D20

DDR_B_D21

DDR_B_D22

DDR_B_D23

DDR_B_D24

DDR_B_D25

DDR_B_D26

DDR_B_D27

DDR_B_D28

DDR_B_D29

DDR_B_D30

DDR_B_D31

DDR_B_D32

DDR_B_D33

DDR_B_D34

DDR_B_D35

DDR_B_D36

DDR_B_D37

DDR_B_D38

DDR_B_D39

DDR_B_D40

DDR_B_D41

DDR_B_D42

DDR_B_D43

DDR_B_D44

DDR_B_D45

DDR_B_D46

DDR_B_D47

DDR_B_D48

DDR_B_D49

DDR_B_D50

DDR_B_D51

DDR_B_D52

DDR_B_D53

DDR_B_D54

DDR_B_D55

DDR_B_D56

DDR_B_D57

DDR_B_D58

DDR_B_D59

DDR_B_D60

DDR_B_D61

DDR_B_D62

DDR_B_D63

LE88CLPM A0 QM21_FCBGA1299~D

DELL CONFIDENTIAL/PROPRIETARY

Compal Electronics, Inc.

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

Title

Crestline(2 of 6)

Size

Date:

Document Number

Rev

0.4

LA-3302P

Thursday, March 01, 2007

Sheet

1

11

of

66

+VCC_PEG

R366

24.9_0402_1%~D

Strap Pin Table

U29C

LVDS_IBG

LVDS_VBG

LVDS_VREFH

LVDS_VREFL

D46

C45

D44

E42

LVDSA_CLK#

LVDSA_CLK

LVDSB_CLK#

LVDSB_CLK

G51

E51

F49

LVDSA_DATA#_0

LVDSA_DATA#_1

LVDSA_DATA#_2

G50

E50

F48

LVDSA_DATA_0

LVDSA_DATA_1

LVDSA_DATA_2

G44

B47

B45

LVDSB_DATA#_0

LVDSB_DATA#_1

LVDSB_DATA#_2

E44

A47

A45

LVDSB_DATA_0

LVDSB_DATA_1

LVDSB_DATA_2

E27

G27

K27

M35

P33

TV_DCONSEL_0

TV_DCONSEL_1

H32

G32

K29

J29

F29

E29

CRT_BLUE

CRT_BLUE#

CRT_GREEN

CRT_GREEN#

CRT_RED

CRT_RED#

K33

G35

F33

E33

CRT_DDC_CLK

CRT_DDC_DATA

CRT_HSYNC

CRT_VSYNC

C32

CRT_TVO_IREF

VGA

TVA_RTN

TVB_RTN

TVC_RTN

TV

TVA_DAC

TVB_DAC

TVC_DAC

F27

J27

L27

N43 PEGCOMP

M43

Low = DMI x 2

CFG5

DMI X2 Select

CFG9

PCI Express

Graphic Lane

Low = Reverse Lane

CFG16

FSB Dynamic

ODT

Low=Dynamic ODT Disable

DMI Lane

Reversal

Low=Normal (default)

SDVO/PCIE

Concurrent

Operation

High = DMI x 4 (Default)

PEG_MRX_GTX_N[0..15] 52

GRAPHICS

L41

L43

N41

N40

PEG_COMPI

PEG_COMPO

LVDS

L_BKLT_CTRL

L_BKLT_EN

L_CTRL_CLK

L_CTRL_DATA

L_DDC_CLK

L_DDC_DATA

L_VDD_EN

PCI-EXPRESS

J40

H39

E39

E40

C37

D35

K40

PEG_RX#_0

PEG_RX#_1

PEG_RX#_2

PEG_RX#_3

PEG_RX#_4

PEG_RX#_5

PEG_RX#_6

PEG_RX#_7

PEG_RX#_8

PEG_RX#_9

PEG_RX#_10

PEG_RX#_11

PEG_RX#_12

PEG_RX#_13

PEG_RX#_14

PEG_RX#_15

J51

L51

N47

T45

T50

U40

Y44

Y40

AB51

W49

AD44

AD40

AG46

AH49

AG45

AG41

PEG_MRX_GTX_N0

PEG_MRX_GTX_N1

PEG_MRX_GTX_N2

PEG_MRX_GTX_N3

PEG_MRX_GTX_N4

PEG_MRX_GTX_N5

PEG_MRX_GTX_N6

PEG_MRX_GTX_N7

PEG_MRX_GTX_N8

PEG_MRX_GTX_N9

PEG_MRX_GTX_N10