Académique Documents

Professionnel Documents

Culture Documents

Flip-Flop y 555

Transféré par

Oscar Jose CorteCopyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

Flip-Flop y 555

Transféré par

Oscar Jose CorteDroits d'auteur :

Formats disponibles

UNIVERSIDAD POLITECNICA DE TLAXCALA

INGENIERIA EN MECATRONICA

ASIGNATURA

ELCTRONICA DIGITAL

TEMA

FLIP-FLOP

CATEDRATICO

M. en C. MA. NATIVIDAD ROMANO RODRIGUEZ

ALUMNO

OSCAR JOSE CORTE

GRUPO

3 F

TEPEYANCO, TLAXCALA A 19 DE JULIO DE 2011

UNIVERSIDAD POLITECNICA DE TLAXCALA

ELECTRONICA DIGITAL OSCAR JOSE CORTE

FLIP-FLOP

El elemento de memoria ms importante es el flip-flop, que est formado por un ensamble de compuertas lgicas. Aunque una compuerta lgica, por si misma, no tiene capacidad de almacenamiento, pueden conectarse varias de ellas de manera que permiten almacenar informacin. Existen varias maneras de configuraciones de compuertas que se utilizan para producir estos flip-flops (FF). Conexin Serie-Serie Slo la entrada del primer flip-flop y la salida del ltimo son accesibles externamente. Se emplean como lneas de retardo digitales y en tareas de sincronizacin. Conexin Paralelo-Serie Son accesibles las entradas de todos los flip-flop, pero slo la salida del ltimo. Normalmente tambin existe una entrada serie, que slo altera el contenido del primer flip-flop, pudiendo funcionar como los del grupo anterior. Conexin Serie-Paralelo Son accesibles las salidas de todos los flip-flop, pero slo la entrada del primero. Este tipo y el anterior se emplean para convertir datos serie en paralelo y viceversa, por ejemplo para conexiones serie. Conexin Paralelo -Paralelo Tanto las entradas como las salidas son accesibles. Se usan para clculos aritmticos.

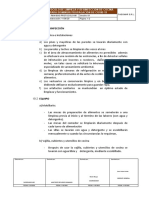

FLIP FLOP TIPO S-R

La operacin del FF S R disparado por flanco es similar a la operacin analizada anteriormente, con la diferencia de que el cambio de estado se efecta en el flanco de bajada del pulso de reloj. El estado S=R=1 sigue siendo un estado prohibido. La tabla caracterstica resume el comportamiento del FF tipo S R disparado por flanco negativo.

UNIVERSIDAD POLITECNICA DE TLAXCALA

ELECTRONICA DIGITAL OSCAR JOSE CORTE

Se puede construir uno fcilmente utilizando dos compuertas NAND o NOR conectadas de tal forma de realimentar la entrada de una con la salida de la otra, quedando libre una entrada de cada compuerta, las cuales sern utilizadas para control Set y Reset.

FLIP-FLOP MAESTRO-ESCLAVO

Un flip flop maestro-esclavo se construye con dos FF, uno sirve de maestro y otro de esclavo. Durante la subida del pulso de reloj se habilita el maestro y se deshabilita el esclavo. La informacin de entrada es transmitida hacia el FF maestro. Cuando el pulso baja nuevamente a cero se deshabilita el maestro lo cual evita que lo afecten las entradas externas y se habilita el esclavo. Entonces el esclavo pasa al el mismo estado del maestro. El comportamiento del flip-flop maestro-esclavo que acaba de describirse hace que los cambios de estado coincidan con la transicin del flanco negativo del pulso.

UNIVERSIDAD POLITECNICA DE TLAXCALA

ELECTRONICA DIGITAL OSCAR JOSE CORTE

FLIP-FLOP J-K

Este FLIP-FLOP es una versin modificada del FLIP-FLOP D, y su aplicacin es muy difundida en el Anlisis y Diseo de Circuitos Secuenciales. El funcionamiento de este dispositivo es similar al FLIP-FLOP S-R, excepto que en este no se presentan indeterminaciones cuando sus dos entradas se encuentran en 1 lgico, si no que el FLIP-FLOP entra en un modo de funcionamiento llamado modo complemento, en el cual, la salida Q cambia a su estado complementario despus de cada pulso de reloj.

FLIP-FLOP D

En este circuito no existe la posibilidad de que las dos entradas estn a nivel alto ya que posee un inversor entre la una y la otra de tal modo que R = ~S, aqu se supone la entrada Dato a nivel 0.

Veamos que ocurre cuando la entrada Dato, pasa a 1 y CK cambia de estado pasando tambin a 1, segn como se van transmitiendo los datos por las compuertas resulta Q = 1 y Q = 0.

Para que el FLIP-FLOP retorne a su estado inicial, la entrada Dato D deber pasar a 0 y slo se transferir a la salida si CK es 1. Nuevamente se repite el caso que para leer el datos debe ser CK = 1. En forma general se representa el FLIP-FLOPD con el siguiente smbolo.

Smbolo FLIP-FLOP D

UNIVERSIDAD POLITECNICA DE TLAXCALA

ELECTRONICA DIGITAL OSCAR JOSE CORTE

CIRCUITO INTEGRADO 555

Es un temporizador es tan verstil que se puede, incluso utilizar para modular una seal en frecuencia modulada (F.M.) Est constituido por una combinacin de comparadores lineales, Flip-Flops (bsculas digitales), transistor de descarga y excitador de salida. Es muy popular para hacer osciladores que sirven como reloj (base de tiempo) para el resto del circuito. A continuacin se explicara la configuracin de sus pines:

Pin 1 - Tierra o masa Pin 2 - Disparo: Es en esta patilla, donde se establece el inicio del tiempo de retardo, si el 555 es configurado como monostable. Este proceso de disparo ocurre cuando este pin va por debajo del nivel de 1/3 del voltaje de alimentacin. Este pulso debe ser de corta duracin, pues si se mantiene bajo por mucho tiempo la salida se quedar en alto hasta que la entrada de disparo pase a alto otra vez. Pin 3 - Salida: Aqu veremos el resultado de la operacin del temporizador, ya sea que est conectado como monostable, astable u otro. Cuando la salida es alta, el voltaje ser el voltaje de aplicacin (Vcc) menos 1.7 Voltios. Esta salida se puede obligar a estar en casi 0 voltios con la ayuda de la patilla reset (Pin 4) Pin 4 - Reset: Si se pone a un nivel por debajo de 0.7 Voltios, pone la patilla de salida 3 a nivel bajo. Si por algn motivo esta patilla no se utiliza hay que conectarla a Vcc para evitar que el 555 se "reinicie". Pin 5 - Control de voltaje: Cuando el temporizador se utiliza en el modo de controlador de voltaje, el voltaje en esta patilla puede variar casi desde Vcc (en la prctica como Vcc-1 voltio) hasta casi 0 V (aprox. 2 Voltios). As es posible modificar los tiempos en que la patilla 3 est en alto o en bajo independiente del diseo (establecido por las resistencias y condensadores conectados externamente al 555). El voltaje aplicado a la patilla 5 puede variar entre un 45 y un 90 % de Vcc en la configuracin monoestable. Cuando se utiliza la configuracin astable, el voltaje puede variar desde 1.7 voltios hasta Vcc. Modificando el voltaje en esta patilla en la configuracin astable causar la frecuencia original del astable sea modulada en frecuencia (FM). Si esta patilla no se utiliza, se recomienda ponerle un condensador de 0.01uF para evitar las interferencias. Pin 6 - Umbral: Es una entrada a un comparador interno que tiene el 555 y se utiliza para poner la salida (Pin 3) a nivel bajo. Pin 7 - Descarga: Utilizado para descargar con efectividad el condensador externo utilizado por el temporizador para su funcionamiento. Pin 8 - V+: Tambin llamado Vcc, es el pin donde se conecta el voltaje de alimentacin que va de 4.5 voltios hasta 16 voltios (mximo). Hay versiones militares de este integrado que llegan hasta 18 Voltios.

Vous aimerez peut-être aussi

- Informe - Benzoato de MetiloDocument5 pagesInforme - Benzoato de MetiloSaray AcostaPas encore d'évaluation

- Quimica OrganicaDocument4 pagesQuimica OrganicaYenniPas encore d'évaluation

- Ficha Técnica Clima Laboral (Cla)Document2 pagesFicha Técnica Clima Laboral (Cla)Alondra SantisPas encore d'évaluation

- Dia 1 Sem 14 ComDocument3 pagesDia 1 Sem 14 ComEdder Michel Geronimo SalinasPas encore d'évaluation

- ANALISIS DEl ContramaestroDocument4 pagesANALISIS DEl ContramaestroYuly Paola YurgakyPas encore d'évaluation

- Memoria DescriptivaDocument74 pagesMemoria DescriptivaJesus CaceresPas encore d'évaluation

- Revesta 73Document4 pagesRevesta 73Adrian Alberto MartinezPas encore d'évaluation

- El Zambullidor de JuninDocument2 pagesEl Zambullidor de Juninromulo soto meranoPas encore d'évaluation

- Tutorial para Presentar Solicitudes de Subvención Herramienta AYAEDocument19 pagesTutorial para Presentar Solicitudes de Subvención Herramienta AYAEEnriquePas encore d'évaluation

- Psicopatologia para EstudiantesDocument26 pagesPsicopatologia para EstudiantesCarlos Arturo Vallejo CiceriPas encore d'évaluation

- Adverbs of Degree, IntensifiersDocument5 pagesAdverbs of Degree, IntensifiersCariño de YunoPas encore d'évaluation

- Pensando Los Fundamentos de La Contabilidad Como Disciplina AcadémicaDocument6 pagesPensando Los Fundamentos de La Contabilidad Como Disciplina Académicajairo cuenuPas encore d'évaluation

- Protocolo Higiene y Desinfección de Cocina-TadomarDocument2 pagesProtocolo Higiene y Desinfección de Cocina-TadomarHenry GarabitoPas encore d'évaluation

- Informe 5 FisicoqumicaDocument3 pagesInforme 5 FisicoqumicaJhoana TamiPas encore d'évaluation

- SISTEMA DE CONTROL GUBERNAMENTAL BoliviaDocument54 pagesSISTEMA DE CONTROL GUBERNAMENTAL BoliviaAngel Mollinedo100% (7)

- Fluidos Newtonianos y No NewtonianosDocument2 pagesFluidos Newtonianos y No NewtonianosDiego_Segoviano19Pas encore d'évaluation

- GRUPO N°6 - Eurotubo S.A.C.Document66 pagesGRUPO N°6 - Eurotubo S.A.C.William Chico100% (1)

- PlanificacionDocument3 pagesPlanificacionJefferson PinanjotaPas encore d'évaluation

- Presentación4 PROBABILIDAD TEOREMASDocument32 pagesPresentación4 PROBABILIDAD TEOREMASRumble Dea re yankiPas encore d'évaluation

- Administracion Tarea 2Document4 pagesAdministracion Tarea 2Irvin Cajusol AyastaPas encore d'évaluation

- Experiencia 6Document13 pagesExperiencia 6emilia del carmenPas encore d'évaluation

- Metodología Del Marco LógicoDocument19 pagesMetodología Del Marco LógicoANDREA KARINA ORTIZ AYORAPas encore d'évaluation

- JOURNALINGDocument3 pagesJOURNALINGInmaculada SánchezPas encore d'évaluation

- Vasos ComunicantesDocument18 pagesVasos ComunicantesBRANDON JULIAN ROA MOJICAPas encore d'évaluation

- CD1 Practica 4 Equipo 5Document16 pagesCD1 Practica 4 Equipo 5Fernando EscobarPas encore d'évaluation

- Tarea Mapa Conceptual-Crystal AvellánDocument1 pageTarea Mapa Conceptual-Crystal AvellánCrystal Regina Avellan FuertesPas encore d'évaluation

- 12.18. Ref Estudio de Hidrologia Zarumilla Tumbes y Anexos 20200929 125221 455Document51 pages12.18. Ref Estudio de Hidrologia Zarumilla Tumbes y Anexos 20200929 125221 455Mirtha CastroPas encore d'évaluation

- EQUIPO 6, Phillip B. Crosby y Su Aportación A La CalidadDocument7 pagesEQUIPO 6, Phillip B. Crosby y Su Aportación A La CalidadOscar GaliciaPas encore d'évaluation

- Caso Practico Mercados FinancierosDocument22 pagesCaso Practico Mercados FinancierosMonserrath Monzalvo SilvaPas encore d'évaluation

- 1 Green Hipocrates-InformaciónDocument2 pages1 Green Hipocrates-Informaciónthiago emmanuelPas encore d'évaluation