Académique Documents

Professionnel Documents

Culture Documents

VLSI Design Syllabus

Transféré par

Jyoti RanjanCopyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

VLSI Design Syllabus

Transféré par

Jyoti RanjanDroits d'auteur :

Formats disponibles

VLSI DESIGN

Module I 08 Hours Introduction: Historical Perspective, VLSI Design Methodologies, VLSI Design Flow, Design Hierarchy, Concept of Regularity, Modularity and Locality, VLSI Design Styles, Computer-Aided Design Technology. Fabrication of MOSFETs: Introduction, Fabrication Processes Flow Basic Concepts, The CMOS n-Well Process, Layout Design Rules, Stick Diagrams, Full-Customs Mask Layout Design. MOS Transistor: The Metal Oxide Semiconductor (MOS) Structure, The MOS System under External Bias, Structure and Operation of MOS Transistor (MOSFET), MOSFET Current-Voltage Characteristics, MOSFET Scaling and Small-Geometry Effects, MOSFET Capacitance. (Chapter 1 to 3 of Text Book 1 and for Stick Diagram Text Book 2) Module II 14 Hours MOS Inverters Static Characteristics: Introduction, Resistive-Load Inverters, Inverters with n-Type MOSFET Load, CMOS Inverter. MOS Inverters Switching Characteristics and Interconnect Effects: Introduction, Delay-Time Definitions, Calculation of Delay-Times, Inverter Design with Delay Constraints, Estimation of Interconnect Parasitics, Calculation of Interconnect Delay, Switching Power Dissipation of CMOS Inverters. Combinational MOS Logic Circuits: Introduction, MOS Logic Circuits with Depletion nMOS Loads, CMOS Logic Circuits, Complex Logic Circuits, CMOS Transmission Gates (Pass Gates). (Chapter 5 to 7 of Text Book 1) Module III 18 Hours Sequential MOS Logic Circuits: Introduction, Behaviour of Bistable Elements, SR Latch Circuits, Clocked Latch and Flip-Flop Circuits, CMOS D-Latch and Edge-Triggered FlipFlop. Dynamic Logic Circuits: Introduction, Basic Principles of Pass Transistor Circuits, Voltage Bootstrapping, Synchronous Dynamic Circuit Techniques, Dynamic CMOS Circuit Techniques, High Performance Dynamic CMOS Circuits. Semiconductor Memories: Introduction, Dynamic Random Access Memory (DRAM), Static Random Access Memory (SRAM), Non-volatile Memory, Flash Memory. Design for Testability: Introduction, Fault Types and Models, Ad Hoc Testable Design Techniques, Scan-Based Techniques, Built-In Self-Test (BIST) Techniques, Current Monitoring IDDQ Test. Text Books: 1. Sung-Mo Kang and Yusuf Leblebici, CMOS Digital Integrated Circuits: Analysis and Design, 3rd Edn., Tata McGraw-Hill Publishing Company Limited, 2003. 2. K. Eshraghian and N.H.E. Weste, Principles of CMOS VLSI Design a Systems Perspective, 2nd Edn., Addison Wesley, 1993. Reference Books: 1. Jan M. Rabaey, Anantha Chandrakasan, Borivoje Nikolic, Digital Integrated Circuits A Design Perspective, 2nd Edn., PHI. 2. Wayne Wolf, Modern VLSI Design System on Chip Design, 3rd Edn., PHI. 3. Debaprasad Das, VLSI Design, Oxford University Press, New Delhi, 2010. 4. John P. Uyemura, CMOS Logic Circuit Design, Springer (Kluwer Academic Publishers), 2001. 5. Ken Martin, Digital Integrated Circuit Design, Oxford University Press, 2000.

VLSI DESIGN LABORATORY

1. Design Entry and simulation of combinational logic circuits (8 bit adders, 4 bit multipliers, address decoders, multiplexers), Test bench creation, functional verification, and concepts of concurrent and sequential execution to be highlighted. Design Entry and simulation of sequential logic circuits (counters, PRBS generators, accumulators). Test bench creation, functional verification, and concepts of concurrent and sequential execution to be highlighted. Synthesis, P&R and Post P&R simulation for all the blocks/codes developed in Expt. No. 1 and No. 2 given above. Concepts of FPGA floor plan, critical path, design gate count, I/O configuration and pin assignment to be taught in this experiment. Generation of configuration/fuse files for all the blocks/codes developed as part of Expt.1. and Expt. 2. FPGA devices must be configured and hardware tested for the blocks/codes developed as part of Expt. 1. and Expt. 2. The correctness of the inputs and outputs for each of the blocks must be demonstrated at least on oscilloscopes (logic analyzer preferred). Design a schematic and simple layout for CMOS Inverter, parasitic extraction and simulation. Design a schematic and simple layout for CMOS NAND gate, parasitic extraction and simulation. Design a schematic and simple layout for CMOS NOR gate, parasitic extraction and simulation. Design an ALU or a 4-bit Microprocessor with limited instructions.

2.

3.

4.

5. 6. 7. 8.

Vous aimerez peut-être aussi

- VLSI Design Course OverviewDocument4 pagesVLSI Design Course OverviewDr.P. RAJASEKARPas encore d'évaluation

- GOVERNMENT ENGINEERING COLLEGE VLSI TECHNOLOGY LESSION PLANDocument1 pageGOVERNMENT ENGINEERING COLLEGE VLSI TECHNOLOGY LESSION PLANHarish Kumar ReddyPas encore d'évaluation

- Vlsi DesignDocument3 pagesVlsi DesignGokulPas encore d'évaluation

- CMOS VLSI Design Introduction Overview Methodologies Flow Hierarchy ConceptsDocument1 pageCMOS VLSI Design Introduction Overview Methodologies Flow Hierarchy ConceptsArun KumarPas encore d'évaluation

- VTU - MTECH - VLSI Design& Embedded Systems Syllabus - RevisedDocument37 pagesVTU - MTECH - VLSI Design& Embedded Systems Syllabus - RevisedAshik PadmanabhaPas encore d'évaluation

- GTU VLSI Technology and Design Course OverviewDocument3 pagesGTU VLSI Technology and Design Course OverviewSachin JoshiPas encore d'évaluation

- M.E. Microelectronics Course StructureDocument19 pagesM.E. Microelectronics Course StructureSneha NargundkarPas encore d'évaluation

- Revised Syllabus MicroelectronicsDocument19 pagesRevised Syllabus MicroelectronicsBaluvu JagadishPas encore d'évaluation

- Mtech VLSI SyllabusDocument37 pagesMtech VLSI SyllabusRavindra vs100% (1)

- ME - Detailed Syllabus - 2016-17 OnwardsDocument24 pagesME - Detailed Syllabus - 2016-17 OnwardsfilmfilmfPas encore d'évaluation

- VLSI Technology and DesignDocument2 pagesVLSI Technology and DesignJigar PatelPas encore d'évaluation

- (13ec604) Vlsi Design S: Ds Ds M DsDocument1 page(13ec604) Vlsi Design S: Ds Ds M DsSai Jaswanth SinghPas encore d'évaluation

- VLSI DesignDocument1 pageVLSI Designडाँ सूर्यदेव चौधरीPas encore d'évaluation

- VLSI Design Fundamentals and Digital CircuitsDocument2 pagesVLSI Design Fundamentals and Digital Circuitsjames RPas encore d'évaluation

- VLSI SYllabus With CODocument1 pageVLSI SYllabus With COchandranv76Pas encore d'évaluation

- Elective-Iv Digital Vlsi DesignDocument4 pagesElective-Iv Digital Vlsi Designnayna bhosalePas encore d'évaluation

- Vlsi Vlsid Vlsisd Vlsi Me Ece PDFDocument18 pagesVlsi Vlsid Vlsisd Vlsi Me Ece PDFramanaidu1Pas encore d'évaluation

- VLSI Design Course OverviewDocument1 pageVLSI Design Course OverviewRajalingam BossPas encore d'évaluation

- CMOS VLSI and Aspect of ASIC DesignDocument3 pagesCMOS VLSI and Aspect of ASIC DesignBittU BhagatPas encore d'évaluation

- Ece2008 Vlsi System Design SyllabusDocument2 pagesEce2008 Vlsi System Design Syllabusyaswanth rPas encore d'évaluation

- Vlsi Design: Text BooksDocument2 pagesVlsi Design: Text BooksAshutoshBhattPas encore d'évaluation

- Vlsi SyllabusDocument3 pagesVlsi SyllabusmadhurPas encore d'évaluation

- Syllabus Vls Technology ApplicationsDocument2 pagesSyllabus Vls Technology ApplicationsPrajwalAgarwalPas encore d'évaluation

- CMOS Analog Design PDFDocument1 pageCMOS Analog Design PDFRanjith DevulapalliPas encore d'évaluation

- Review For Final Examination: ECE 4420 - Spring 2004Document3 pagesReview For Final Examination: ECE 4420 - Spring 2004Pay RentPas encore d'évaluation

- Vlsi SyllabusDocument2 pagesVlsi SyllabusAkhil NameirakpamPas encore d'évaluation

- VLSI Syllabus M.tech BurlaDocument27 pagesVLSI Syllabus M.tech BurlaBiswajit BeheraPas encore d'évaluation

- Unit I: Introduction To VLSI Circuits 7LDocument2 pagesUnit I: Introduction To VLSI Circuits 7LSaurabhMoharirPas encore d'évaluation

- VLSI Systems Design FundamentalsDocument4 pagesVLSI Systems Design FundamentalsMuhammad Kamran AkramPas encore d'évaluation

- Advanced VlsiDocument1 pageAdvanced VlsiPramod SnkrPas encore d'évaluation

- Btech New SyllabusDocument8 pagesBtech New SyllabusDrBhoopal RaoPas encore d'évaluation

- ChipedgeDocument4 pagesChipedgeMhappyCuPas encore d'évaluation

- Cmos Vlsi Design ContentDocument1 pageCmos Vlsi Design ContentdileepanmePas encore d'évaluation

- GTU PHD Core Syllabus CMOS Analog Circuit DesignDocument1 pageGTU PHD Core Syllabus CMOS Analog Circuit Designsubhash_tuhhPas encore d'évaluation

- EceDocument2 pagesEceDivya SeepanaPas encore d'évaluation

- EC8095 VLSI Design SyllabusDocument1 pageEC8095 VLSI Design SyllabusBaskar KPas encore d'évaluation

- Ds Ds M DsDocument1 pageDs Ds M DsarunaPas encore d'évaluation

- Vlsi Mtech 1st - Year - Jntu Kakinada SyllabusDocument8 pagesVlsi Mtech 1st - Year - Jntu Kakinada Syllabustele203Pas encore d'évaluation

- M.Tech. VLSI Design (OU) Syllabus I+II+III+IV SemDocument15 pagesM.Tech. VLSI Design (OU) Syllabus I+II+III+IV SemMs. Bhavini KumawatPas encore d'évaluation

- Course Contents of VLSIDocument2 pagesCourse Contents of VLSIOmer KhanPas encore d'évaluation

- Digital VLSI Design Course OverviewDocument1 pageDigital VLSI Design Course OverviewVishwajeet S BPas encore d'évaluation

- B.Tech. - CS - II-IVYear2009 37Document1 pageB.Tech. - CS - II-IVYear2009 37Ekta VaswaniPas encore d'évaluation

- Ece5015 Digital-Ic-Design Eth 1.0 40 Ece5015Document2 pagesEce5015 Digital-Ic-Design Eth 1.0 40 Ece5015Sivanantham SadhasivamPas encore d'évaluation

- Preface: Introduction To VLSI Circuits and SystemsDocument16 pagesPreface: Introduction To VLSI Circuits and SystemsraviPas encore d'évaluation

- 9f55d1 - Introduction To Vlsi DesignDocument4 pages9f55d1 - Introduction To Vlsi DesignAman ShivachhPas encore d'évaluation

- Syllabus EC-312Document2 pagesSyllabus EC-312U Rama KrishnaPas encore d'évaluation

- BIT401Document2 pagesBIT401Afshan KaleemPas encore d'évaluation

- Text BooksDocument2 pagesText BooksmtariqanwarPas encore d'évaluation

- R20-Vlsi SYLLABUSDocument2 pagesR20-Vlsi SYLLABUSdrkhamuruddeenPas encore d'évaluation

- Ec 544Document2 pagesEc 544Surbhi SinghPas encore d'évaluation

- Syllabus - Vlsi and Chip DesignDocument2 pagesSyllabus - Vlsi and Chip Designjana kPas encore d'évaluation

- VLSI Design SyllubusDocument1 pageVLSI Design SyllubusHarold WilsonPas encore d'évaluation

- Vlsi DesignDocument1 pageVlsi DesignlakshmipoPas encore d'évaluation

- Sem1 EmbbededDocument9 pagesSem1 Embbededvishwanath cPas encore d'évaluation

- Fundamentals of CMOS VLSI 10EC56Document214 pagesFundamentals of CMOS VLSI 10EC56Santhos KumarPas encore d'évaluation

- On-Chip Communication Architectures: System on Chip InterconnectD'EverandOn-Chip Communication Architectures: System on Chip InterconnectPas encore d'évaluation

- Bebop to the Boolean Boogie: An Unconventional Guide to ElectronicsD'EverandBebop to the Boolean Boogie: An Unconventional Guide to ElectronicsÉvaluation : 4 sur 5 étoiles4/5 (3)

- Designing SOCs with Configured Cores: Unleashing the Tensilica Xtensa and Diamond CoresD'EverandDesigning SOCs with Configured Cores: Unleashing the Tensilica Xtensa and Diamond CoresÉvaluation : 5 sur 5 étoiles5/5 (2)

- Advanced Test Methods for SRAMs: Effective Solutions for Dynamic Fault Detection in Nanoscaled TechnologiesD'EverandAdvanced Test Methods for SRAMs: Effective Solutions for Dynamic Fault Detection in Nanoscaled TechnologiesPas encore d'évaluation

- ER Tutorial 2: Chapter 9 - Questions 3, 4 and 5 V3.0Document9 pagesER Tutorial 2: Chapter 9 - Questions 3, 4 and 5 V3.0Deepak AroraPas encore d'évaluation

- WimaxDocument50 pagesWimaxJyoti RanjanPas encore d'évaluation

- Changing Your MAC Address in Window XPDocument6 pagesChanging Your MAC Address in Window XPJyoti RanjanPas encore d'évaluation

- Registry Past and PresentDocument2 pagesRegistry Past and PresentJyoti RanjanPas encore d'évaluation

- Math IIIDocument1 pageMath IIIJyoti RanjanPas encore d'évaluation

- Biochip AbsDocument1 pageBiochip AbsJyoti RanjanPas encore d'évaluation

- 2008 ItDocument44 pages2008 ItSwayamprakash RoutPas encore d'évaluation

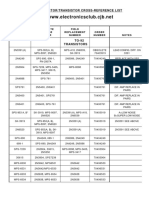

- SEMI-CONDUCTOR/TRANSISTOR CROSS-REFERENCE LISTDocument24 pagesSEMI-CONDUCTOR/TRANSISTOR CROSS-REFERENCE LISTangel miguel rodriguez moralesPas encore d'évaluation

- P-i-n Diode Working and TypesDocument9 pagesP-i-n Diode Working and TypesAshwin JoshiPas encore d'évaluation

- Syllabus (ELE 241)Document3 pagesSyllabus (ELE 241)PhoyagerPas encore d'évaluation

- HVR HVR Series Bi-Directional High Voltage Diodes For Microwave OvensDocument1 pageHVR HVR Series Bi-Directional High Voltage Diodes For Microwave OvensA A Asdasd DfPas encore d'évaluation

- Solar Photovoltaic Technologies: Lecture-6 Carrier Transport in SemiconductorDocument16 pagesSolar Photovoltaic Technologies: Lecture-6 Carrier Transport in SemiconductorTushar SanwareyPas encore d'évaluation

- BC 171Document4 pagesBC 171Beniamin Vasile ChetranPas encore d'évaluation

- Mecve 101 SPDMDocument2 pagesMecve 101 SPDMSalini SasidharanPas encore d'évaluation

- NPCBL Executive Trainee (Electronoics) 2018 QuestionsDocument6 pagesNPCBL Executive Trainee (Electronoics) 2018 QuestionsAnonymous BFawKerPas encore d'évaluation

- Isotype Junctions, Modulation Doping, and Quantum EffectsDocument4 pagesIsotype Junctions, Modulation Doping, and Quantum EffectsprashantsheetalPas encore d'évaluation

- 7-Circuit 500mA Darlington Transistor Array with Clamp DiodesDocument5 pages7-Circuit 500mA Darlington Transistor Array with Clamp DiodesRamasokolor778Pas encore d'évaluation

- Copper pillar bumping could change semiconductor packaging ecosystemDocument4 pagesCopper pillar bumping could change semiconductor packaging ecosystemrhaudiogeekPas encore d'évaluation

- Solid State Devices Dr. S. Karmalkar Dept. of Electrical Engineering I.I.T. MadrasDocument27 pagesSolid State Devices Dr. S. Karmalkar Dept. of Electrical Engineering I.I.T. MadrasgkkumarPas encore d'évaluation

- Low Power Bipolar Transistors: BC107 / BC108 SeriesDocument3 pagesLow Power Bipolar Transistors: BC107 / BC108 Seriesioan jeanPas encore d'évaluation

- Lab ExperimentDocument7 pagesLab ExperimentBryan Owen Salcedo SantosPas encore d'évaluation

- Design of A Low Power 10T SRAM Cell: Nternational Ournal of Nnovative Esearch in Cience, Ngineering and EchnologyDocument3 pagesDesign of A Low Power 10T SRAM Cell: Nternational Ournal of Nnovative Esearch in Cience, Ngineering and EchnologySuyash KumarPas encore d'évaluation

- Solar Energy - FinalDocument5 pagesSolar Energy - FinalRandomPas encore d'évaluation

- Semiconductor Device FundamentalsDocument13 pagesSemiconductor Device Fundamentalsnoor_dcet0% (4)

- Nte 601-700Document2 pagesNte 601-700api-242591736Pas encore d'évaluation

- A Dvanced A Nalysis Library List Pspice: R Elease 16.0 C Opyright © 2000-2007 C Adence D Esign System S, IncDocument247 pagesA Dvanced A Nalysis Library List Pspice: R Elease 16.0 C Opyright © 2000-2007 C Adence D Esign System S, Inca_damrongPas encore d'évaluation

- Module 04 Part 1Document20 pagesModule 04 Part 1Aviation World100% (2)

- Semiconductor Physics Part II GATE Problem PDFDocument19 pagesSemiconductor Physics Part II GATE Problem PDFUdai SinghPas encore d'évaluation

- Experiment No 2 (Fet)Document4 pagesExperiment No 2 (Fet)Jaideep SinghPas encore d'évaluation

- Weekly DPM Monitor SpreadsheetDocument3 pagesWeekly DPM Monitor SpreadsheetsmtdrkdPas encore d'évaluation

- TIP41 / TIP41C: FeaturesDocument2 pagesTIP41 / TIP41C: FeaturesCAMILA ROMINA LUCANAPas encore d'évaluation

- AOD 609 G - Transistor de Efeito de Campo PDFDocument12 pagesAOD 609 G - Transistor de Efeito de Campo PDFTiago LeonhardtPas encore d'évaluation

- Chapter 6 Mosfet BiasingDocument61 pagesChapter 6 Mosfet Biasingshubhankar pal100% (2)

- Fairchild Semiconductor International Power Solutions Collateral List May 2002Document3 pagesFairchild Semiconductor International Power Solutions Collateral List May 2002Jose Luis Castro AguilarPas encore d'évaluation

- The Blue Laser Diode: Shuji Nakamura Stephen Pear Ton Gerhard FasolDocument7 pagesThe Blue Laser Diode: Shuji Nakamura Stephen Pear Ton Gerhard Fasolvamsi kolla0% (2)

- Course Name: Basic Electronics Engineering Course Code: EC101 Metal Oxide Semiconductor Field Effect Transistor (MOSFET)Document37 pagesCourse Name: Basic Electronics Engineering Course Code: EC101 Metal Oxide Semiconductor Field Effect Transistor (MOSFET)Dr Sunipa RoyPas encore d'évaluation

- Vlsi NotesDocument91 pagesVlsi Notesarvindron50% (2)