Académique Documents

Professionnel Documents

Culture Documents

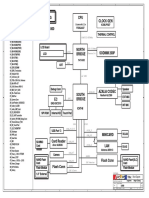

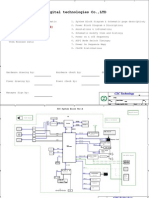

Smdk6410 Cpu BD Schematics Rev1.0

Transféré par

kit2Titre original

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

Smdk6410 Cpu BD Schematics Rev1.0

Transféré par

kit2Droits d'auteur :

Formats disponibles

5

SMDK6410 CPU B'd (S3C6410 Evaluation Board) Schematics

Revision

Rev 1.0

Description

Date

2008.07.14

Public Version

Table of Contents

Part Reference

Page

Function

------------------------------------------------------01

Revision History

02

S3C6410 (Addr/Data)/SW-TACT

03

S3C6410 (I/O 1)

04

S3C6410 (I/O 2)/ADC

05

S3C6410 (Power)

06

Power (ARM,INT)

07

Power (PLL,Alive,RTC)/USB Host/USB OTG

08

Power (I/O)

09

PMIC Socket

10

Memory (mDDR)

11

Buffers (SROM IF)

12

Buffers Control (SROM IF)/SS

13

SD_MMC/SPI

14

oneNAND/MIPI/JTAG/CLK

15

Camera Interface

16

B2B Connector

<Component><Number>

--------------------------------------------------U : Component or Regurator IC

C : Capacitor

CB : Capacitor Bypass

CT : Capacitor Tantal

CTB : Capacitor Tantal Bypass

J

: Jumper

JB : CPU or Base connector

JP : Jumper Power

R

: Resistor

RA : Resistor Array

RP : Resistor Power

VR : Variable Resistor

L

: Inductor

FB : Ferrite Bead

OSC : Oscillator

X : X-tal (Crystal)

Q : Transistor or FET

D : Diode

ZD : Zener Diode

LED : LED Diode

SW : SWitch Tact/Push

CON : CONnector

CFG : ConFiGure switch (DIP/Slide)

TP : Test Point (SMD)

TPH : Test Point Hole (Through Hole)

MTH: Mount Through Hole

MOD : MODule Interface connector

SAMSUNG ELECTRONICS CO.,LTD

Title

SMDK6410 CPU Board (S3C6410 Evaluation Board)

Size

A3

Date:

5

Document Number

Revision History

Monday, July 14, 2008

Rev

1.0

Sheet

1

of

16

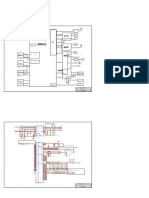

Xm0ADDR18/GPQ0

Xm0ADDR19/GPQ1

XGPQ2

XGPQ3

XGPQ4

XGPQ5

XGPQ6

Xm0ADDR17/GPQ7

Xm0ADDR16/GPQ8

Xm0BE0

Xm0BE1

R955

R956

R957

R958

R959

R960

R961

R962

10/R1005

10/R1005

10/R1005

10/R1005

10/R1005

10/R1005

10/R1005

10/R1005

Xm1WEn

Xm1CASn

Xm1RASn

Xm1SCLKn

Xm1SCLK

Xm1CKE1

Xm1CKE0

M19

L24

L22

A14

A13

M24

M18

R963

R964

R965

R966

R967

10/R1005

10/R1005

10/R1005

10/R1005

10/R1005

CB1

Xm1CSn1 [10]

Xm1CSn0 [10]

[10]

[10]

[10]

[10]

[10]

[10]

[10]

[10]

nBATF

1

2

3

SW-TACT (Gray)

TPG0 XGPO4

TPG1 XGPQ2

TPG2 XGPQ3

XGPQ3

TPG3 XGPQ4

XGPQ4

Xm0ADDR16

Xm0ADDR17

XGPQ6

XGPQ5

XGPQ4

XGPQ3

XGPQ2

Xm0ADDR19

Xm0ADDR18

TPG4 XGPQ5

VDD_D

CB3

R11

3

4

100K/R1005

nRESET

XnRESET

TP4

U5

ONKEYn

TP3

nMR

GND

SRT

nRESET [9]

4

C1

SW3

SW-TACT (Red)

100nF

A

R15

PMIC_ONKEYn [9]

SN74LVC1G11DBV

3

4

XnRESET [3,6,14,16]

SN74LVC1G17DBV

3

SAMSUNG ELECTRONICS CO.,LTD

Title

<Silk>

SMDK6410 CPU Board (S3C6410 Evaluation Board)

1

2

PMIC ON

SW4

Size

A3

SW-TACT (Red)

Date:

5

0/R1005

1

3

6

2

NC/R1005

100nF

U6

VCC nRESET

MAX6412UK22

1

2

VDD_D

R14

10K/R1005

10K/R1005

<Silk>

R12

100nF

U4

100K/R1005

CB4

R18

TPG5 XGPQ6

XGPQ6

Xm0BE1 [11]

Xm0BE0 [11]

VDD_D

[9] PMIC_nRST_OUT

SW1

C_PWR_5V

0/R1005

0/R1005

XnBATF [3,9]

<Silk>

Xm1WEn [10]

Xm1CASn [10]

Xm1RASn [10]

Xm1SCLKn [10]

Xm1SCLK [10]

Xm1CKE1 [10]

Xm1CKE0 [10]

[12] Xm0INTata/SS_REAL_IN

[12] Xm0RSTata/SS_IMG_IN

[12] Xm0INPACKata/SS_TCXO_CLK

[12] Xm0REGata/SS_GPO0

[12] Xm0WEata/SS_GPO1

[12] Xm0OEata/SS_GPO2

[12] Xm0CData/SS_GPO3

R16

R17

nBATF

TP1

SN74LVC1G17DBV

XGPQ2

[11] Xm0WAITn/IORDY

[11,14] Xm0RDY0/ALE

[11,14] Xm0RDY1/CLE

[11,14] Xm0INTsm0/FWEn

[11,12,14] Xm0INTsm1/FREn

[14] Xm0RPn/RnB

[9] nRESET

[16] AP_nRESET

[16] Modem_nRESET

100nF

U2

3

4

Xm1DQS3

Xm1DQS2

Xm1DQS1

Xm1DQS0

Xm1DQM3

Xm1DQM2

Xm1DQM1

Xm1DQM0

100K/R1005

XGPO4

Xm0CSn0

Xm0CSn1

Xm0CSn2

Xm0CSn3

Xm0CSn4

Xm0CSn5

XGPO4

[12] XGPO5

R13

R9

[11,12]

[11,12]

[14]

[14]

[11,12]

[11,12]

[11]

[11]

[11]

[11]

VDD_D

XGPQ5

10K/R1005

E25

B14

G9

D9

H22

D14

G8

A5

10K/R1005

Xm1DQS3

Xm1DQS2

Xm1DQS1

Xm1DQS0

Xm1DQM3

Xm1DQM2

Xm1DQM1

Xm1DQM0

R8

L18

L23

10K/R1005

Xm1CSn1

Xm1CSn0

R5

L25

M17

K22

K24

K19

M23

J22

K23

K18

J25

K25

L19

H25

J23

J24

H24

M0ADDR16

M0ADDR17

M0ADDR18

M0ADDR19

R7

Xm1ADDR[15:0] [10]

Xm1ADDR15

Xm1ADDR14

Xm1ADDR13

Xm1ADDR12

Xm1ADDR11

Xm1ADDR10

Xm1ADDR9

Xm1ADDR8

Xm1ADDR7

Xm1ADDR6

Xm1ADDR5

Xm1ADDR4

Xm1ADDR3

Xm1ADDR2

Xm1ADDR1

Xm1ADDR0

Xm1ADDR15

Xm1ADDR14

Xm1ADDR13

Xm1ADDR12

Xm1ADDR11

Xm1ADDR10

Xm1ADDR9

Xm1ADDR8

Xm1ADDR7

Xm1ADDR6

Xm1ADDR5

Xm1ADDR4

Xm1ADDR3

Xm1ADDR2

Xm1ADDR1

Xm1ADDR0

U2

P8

T1

U1

V3

T4

V2

U3

J1

L1

K7

Xm0INTata/SS_REALIN/GPP8

Xm0RSTata/SS_IMGIN/GPP9

Xm0INPACKata/SS_TCXO/GPP10

Xm0REGata/SS_GPO0/GPP11

Xm0WEata/SS_GPO1/GPP12

Xm0OEata/SS_GPO2/GPP13

Xm0CData/SS_GPO3/GPP14

R7

W3

AA2

AA3

V4

AB3

U7

Xm0OEn/nIORD_CF

Xm0WEn/nIOWR_CF

Xm0ADV/GPP0

Xm0SMCLK/GPP1

Xm0WAITn/IORDY/GPP2

Xm0RDY0/ALE/GPP3

Xm0RDY1/CLE/GPP4

Xm0INTsm0/FWEn/GPP5

Xm0INTsm1/FREn/GPP6

Xm0RPn/RnB/GPP7

L4

J2

Y2

L3

Xm0OEn/nIORD_CF

Xm0WEn/nIOWR_CF

Xm0ADV

Xm0SMCLK

S3C6410X

R4

R8

W2

Y3

U4

Y1

Xm0DATA0

Xm0DATA1

Xm0DATA2

Xm0DATA3

Xm0DATA4

Xm0DATA5

Xm0DATA6

Xm0DATA7

Xm0DATA8

Xm0DATA9

Xm0DATA10

Xm0DATA11

Xm0DATA12

Xm0DATA13

Xm0DATA14

Xm0DATA15

U1A

NC/R1005

NC/R1005

NC/R1005

NC/R1005

10K/R1005

H23

G25

G23

E24

G24

F25

F24

F23

D16

B15

D15

C15

C13

A12

B13

B12

D10

C11

B10

A11

D11

C12

A10

D12

C9

A9

C8

C6

B7

C7

A6

B6

N2

N1

M7

N3

M8

P2

N4

P3

M2

M4

L7

M3

L8

L2

K4

K1

N7

R3

P4

R2

T3

N8

T2

P7

[11,12,14]

[11,14]

[14]

[14]

Xm0DATA0

Xm0DATA1

Xm0DATA2

Xm0DATA3

Xm0DATA4

Xm0DATA5

Xm0DATA6

Xm0DATA7

Xm0DATA8

Xm0DATA9

Xm0DATA10

Xm0DATA11

Xm0DATA12

Xm0DATA13

Xm0DATA14

Xm0DATA15

Xm0ADDR0

Xm0ADDR1

Xm0ADDR2

Xm0ADDR3

Xm0ADDR4

Xm0ADDR5

Xm0ADDR6/GPO6

Xm0ADDR7/GPO7

Xm0ADDR8/GPO8

Xm0ADDR9/GPO9

Xm0ADDR10/GPO10

Xm0ADDR11/GPO11

Xm0ADDR12/GPO12

Xm0ADDR13/GPO13

Xm0ADDR14/GPO14

Xm0ADDR15/GPO15

Xm0CSn0

Xm0CSn1

Xm0CSn2/GPO0

Xm0CSn3/GPO1

Xm0CSn4/GPO2

Xm0CSn5/GPO3

XGPO4

XGPO5

C1

E3

D1

D2

H7

E1

F2

G4

F1

J8

G2

G1

H4

H2

J4

H3

Memory Port1

[11,14] Xm0DATA[15:0]

Xm0ADDR0

Xm0ADDR1

Xm0ADDR2

Xm0ADDR3

Xm0ADDR4

Xm0ADDR5

Xm0ADDR6

Xm0ADDR7

Xm0ADDR8

Xm0ADDR9

Xm0ADDR10

Xm0ADDR11

Xm0ADDR12

Xm0ADDR13

Xm0ADDR14

Xm0ADDR15

Xm1DATA31

Xm1DATA30

Xm1DATA29

Xm1DATA28

Xm1DATA27

Xm1DATA26/Xm0ADDR26

Xm1DATA25/Xm0ADDR25

Xm1DATA24/Xm0ADDR24

Xm1DATA23/Xm0ADDR23

Xm1DATA22/Xm0ADDR22

Xm1DATA21/Xm0ADDR21

Xm1DATA20/Xm0ADDR20

Xm1DATA19/Xm0ADDR19

Xm1DATA18/Xm0ADDR18

Xm1DATA17/Xm0ADDR17

Xm1DATA16/Xm0ADDR16

Xm1DATA15

Xm1DATA14

Xm1DATA13

Xm1DATA12

Xm1DATA11

Xm1DATA10

Xm1DATA9

Xm1DATA8

Xm1DATA7

Xm1DATA6

Xm1DATA5

Xm1DATA4

Xm1DATA3

Xm1DATA2

Xm1DATA1

Xm1DATA0

[11] Xm0ADDR[15:0]

Memory Port0

R1

R2

R3

R4

Xm0ADDR16

Xm0ADDR17

Xm0ADDR18

Xm0ADDR19

R6

Xm1DATA31

Xm1DATA30

Xm1DATA29

Xm1DATA28

Xm1DATA27

Xm1DATA26

Xm1DATA25

Xm1DATA24

Xm1DATA23

Xm1DATA22

Xm1DATA21

Xm1DATA20

Xm1DATA19

Xm1DATA18

Xm1DATA17

Xm1DATA16

Xm1DATA15

Xm1DATA14

Xm1DATA13

Xm1DATA12

Xm1DATA11

Xm1DATA10

Xm1DATA9

Xm1DATA8

Xm1DATA7

Xm1DATA6

Xm1DATA5

Xm1DATA4

Xm1DATA3

Xm1DATA2

Xm1DATA1

Xm1DATA0

Xm1DATA[31:0] [10]

Document Number

S3C6410 (Addr/Data)/SW-TACT

Monday, July 14, 2008

Rev

1.0

Sheet

1

of

16

[14]

[14]

[14]

[14]

[14]

D

XEFFVDD XnRSTOUT

TP5

TP6

XOM4

XOM3

XOM2

XOM1

XOM0

N22

P22

XusbDP

XusbDN

OTG2.0

A18

G13

B18

H13

C18

G12

XmmcCLK0/GPG0

XmmcCMD0/GPG1

XmmcDATA0_0/GPG2

XmmcDATA0_1/GPG3

XmmcDATA0_2/GPG4

XmmcDATA0_3/GPG5

XotgDP

XotgDM

XotgTI

XotgTO

XREXT

XVBUS

XotgID

XotgDRV_VBUS

HS-MMC

V9

AD15

AD16

AD14

AE15

AB16

T7

XnRESET

WR_TEST

XnRSTOUT

XspiMISO0/GPC0

XspiCLK0/GPC1

HS-SPI

XspiMOSI0/GPC2

XspiCS0/GPC3

XspiMISO1/mmcCMD2/GPC4/Xi2sMULTI_DO0

XspiCLK1/mmcCLK2/GPC5/Xi2sMULTI_DO1

XspiMOSI1/GPC6

XspiCS1/GPC7/Xi2sMULTI_DO2

I2C

XPWRRGTON

XnBATF

XSELNAND

XEFFVDD

B20

H14

A19

C20

B19

H12

C19

D17

VDD_SYS

XnRSTOUT [16]

R19

0/R1005

CLOCK

XEXTCLK

XXTO

XXTI

X27MXTO

X27MXTI

XrtcXTO

XrtcXTI

U1B

S3C6410X

W11

AC17

AC16

AB14

AB15

AD12

AB9

XEXTCLK [14]

XXTO [14]

XXTI [14]

X27MXTO [14]

X27MXTI [14]

XrtcXTO [14]

XrtcXTI [14]

D23

H16

C23

XPWM_TOUT1

XPWM_TOUT0

XPWM_ECLK [8,13,16]

AE17

V10

AD17

AB17

AE18

AC18

V11

AC19

W12

AE19

AB18

AD19

V12

AE20

W13

AD20

XEINT0/KP_ROW0

XEINT1/KP_ROW1

XEINT2/KP_ROW2

XEINT3/KP_ROW3

XEINT4/KP_ROW4

XEINT5/KP_ROW5

XEINT6/KP_ROW6

XEINT7/KP_ROW7

XEINT8 [16]

XEINT9 [16]

XEINT10 [16]

XEINT11 [6,16]

PWM Timer

XpwmTOUT1/GPF15

XpwmTOUT0/XCLKOUT/GPF14

XpwmECLK/GPF13

XEINT0/kpROW0/GPN0

XEINT1/kpROW1/GPN1

XEINT2/kpROW2/GPN2

XEINT3/kpROW3/GPN3

XEINT4/kpROW4/GPN4

XEINT5/kpROW5/GPN5

XEINT6/kpROW6/GPN6

XEINT7/kpROW7/GPN7

XEINT8/GPN8

EINT

XEINT9/GPN9

XEINT10/GPN10

XEINT11/GPN11

XEINT12/GPN12

XEINT13/GPN13

XENT14/GPN14

XEINT15/GPN15

XpcmDCLK0/I2sCLK/BITCLK/GPD0

XpcmEXTCLK0/i2sCDCLK/RESETn/GPD1

XpcmFSYNC0/i2sLRCK/SYNC/GPD2

XpcmSIN0/i2sDI/SDI/GPD3

XpcmSOUT0/i2sDO/SDO/GPD4

XpcmDCLK1/i2sCLK/BITCLK/GPE0

XpcmEXTCLK1/i2sCDCLK/RESETn/GPE1

XpcmFSYNC1/i2sLRCK/SYNC/GPE2

XpcmSIN1/i2sDI/SDI/GPE3

XpcmSOUT1/i2sDO/SDO/GPE4

Xi2cSCL0/GPB5

Xi2cSDA0/GPB6

10K/R1005

XEINT13 [6,13,16]

XEINT14 [6,16]

XEINT15 [6,16]

[16]

[16]

[16]

[16]

[16]

[16]

[16]

[8,16]

R20

0/R1005

R21

NC/R1005

XEINT12 [6,13,16]

PMIC_XEINT12_IRQn [9]

Audio

D7

B5

D6

B4

A3

C5

B3

C4

B2

C3

A20

G14

AE10

AE9

AD7

AD8

AC8

AD9

AD10

AE11

[7] XotgDP

[7] XotgDM

[7] XotgTI

[7] XotgTO

[7] XREXT

[7,9] XVBUS

[7] XotgID

[7] XotgDRV_VBUS

AD13

W9

AC13

V8

AE14

XuRXD0/GPA0

XuTXD0/GPA1

XuCTSn0/GPA2

JTAG

XuRTSn0/GPA3

XuRXD1/GPA4

XuTXD1/GPA5

UART/IrDA

XuCTSn1/GPA6

XuRTSn1/GPA7

XuRXD2/ExdREQ/IrRXD/GPB0/ADDR_CF0

XuTXD2/ExdACK/IrTXD/GPB1/ADDR_CF1

XuRXD3/IrRXD/ExdREQ/GPB2/ADDR_CF2/Xi2cSCL1

XuTXD3/IrTXD/ExdACK/GPB3/Xi2cSDA1

XirSDBW/XcamFIELD/BUF_DIR/GPB4

USBH

[7] XusbhDP

[7] XusbhDN

XOM0

XOM1

XOM2

XOM3

XOM4

XTRSTn

XTMS

XTCK

XTDI

XTDO

XRTCK

XDBGSEL

AB10

AE12

AB11

AB12

AC12

AE13

AB13

[13] XspiMISO0

[13] XspiCLK0

[13] XspiMOSI0

[13] XspiCS0

[13] XspiMISO1/mmcCMD2

[13] XspiCLK1/mmcCLK2

[13] XspiMOSI1

[13] XspiCS1

D20

A23

G16

A22

J15

B22

H15

C22

D19

A21

J14

B21

G15

XmmcCDN0/mmcCDN1/GPG6

XmmcCLK1/kpCOL0/GPH0

XmmcCMD1/kpCOL1/GPH1

XmmcDATA1_0/kpCOL2/GPH2

XmmcDATA1_1/kpCOL3/GPH3

XmmcDATA1_2/kpCOL4/GPH4

XmmcDATA1_3/kpCOL5/GPH5

XmmcDATA1_4/mmcDATA2_0/kpCOL6/i2sMULTI_BCLK/ADDR_CF0/GPH6

XmmcDATA1_5/mmcDATA2_1/kpCOL7/i2sMULTI_CDCLK/ADDR_CF1/GPH7

XmmcDATA1_6/mmcDATA2_2/i2sMULTI_LRCLK/ADDR_CF2/GPH8

XmmcDATA1_7/mmcDATA2_3/i2sMULTI_DI/GPH9

XnRESET [2,6,14,16]

R205

A17

J11

A16

H11

C17

B16

H10

A15

G11

C16

H9

[9,15,16] Xi2cSCL0

[9,15,16] Xi2cSDA0

XPWRRGTON

TP7

XPWRRGTON [7,9]

XnBATF [2,9]

XSELNAND [14]

[14] XDBGSEL

[14] XRTCK

[14] XTDO

[14] XTDI

[14] XTCK

[14] XTMS

[14] XTRSTn

[16] XuRXD_0

[16] XuTXD_0

[16] XuCTSn_0

[16] XuRTSn_0

[16] XuRXD_1

[16] XuTXD_1

[16] XuCTSn_1

[16] XuRTSn_1

[16] XuRXD_2/ExdREQ/IrRXD/ADDR_CF0

[16] XuTXD_2/ExdACK/IrTXD/ADDR_CF1

[11,16] XuRXD_3/ExdREQ/IrRXD/ADDR_CF2/Xi2cSCL1

[16] XuTXD_3/ExdACK/IrTXD/Xi2cSDA1

[12,15,16] XirSDBW

VDD_D

[13] XmmcCLK0

[13] XmmcCMD0

[13] XmmcDATA0_0

[13] XmmcDATA0_1

[13] XmmcDATA0_2

[13] XmmcDATA0_3

[13] XmmcCDN0/mmcCDN1

[13] XmmcCLK1

[13] XmmcCMD1

[13] XmmcDATA1_0

[13] XmmcDATA1_1

[13] XmmcDATA1_2

[13] XmmcDATA1_3

[13] XmmcDATA1_4/mmcDATA2_0/ADDR_CF0

[13] XmmcDATA1_5/mmcDATA2_1/ADDR_CF1

[13] XmmcDATA1_6/mmcDATA2_2/ADDR_CF2

[13] XmmcDATA1_7/mmcDATA2_3

R23

2K/R1005

2K/R1005

[9,15,16] Xi2cSDA0

[9,15,16] Xi2cSCL0

XCLKOUT

TP8

[9,16] XPCM_DCLK0/I2S_CLK0/AC97_BITCLK0

[9,16] XPCM_EXTCLK0/I2S_CDCLK0/AC97_RSTn0

[9,16] XPCM_FSYNC0/I2S_LRCLK0/AC97_SYNC0

[9,16] XPCM_SIN0/I2S_DI0/AC97_SDI0

[9,16] XPCM_SOUT0/I2S_DO0/AC97_SDO0

[9,16] XPCM_DCLK1/I2S_CLK1/AC97_BITCLK0

[9,16] XPCM_EXTCLK1/I2S_CDCLK1/AC97_RSTn0

[9,16] XPCM_FSYNC1/I2S_LRCLK1/AC97_SYNC0

[9,16] XPCM_SIN1/I2S_DI1/AC97_SDI0

[9,16] XPCM_SOUT1/I2S_DO1/AC97_SDO0

R22

XPWM_TOUT0

XPWM_TOUT1

R24

R25

0/R1005

0/R1005

PWM_TOUT0 [16]

PWM_TOUT1 [16]

A

SAMSUNG ELECTRONICS CO.,LTD

Title

SMDK6410 CPU Board (S3C6410 Evaluation Board)

Size

A3

Date:

Document Number

S3C6410 (I/O 1)

Monday, July 14, 2008

Rev

1.0

Sheet

1

of

16

[16]

[16]

[16]

[16]

[16]

[16]

[16]

[16]

Xhi_A0/ADDR_CF0/KP_COL0

Xhi_A1/ADDR_CF1/KP_COL1

Xhi_A2/ADDR_CF2/KP_COL2

Xhi_A3/KP_COL3/Xm0INTata

Xhi_A4/KP_COL4/Xm0RSTata

Xhi_A5/KP_COL5/Xm0INPACKata

Xhi_A6/KP_COL6/Xm0REGata

Xhi_A7/KP_COL7/Xm0CData

[6,16] Xhi_A8/CE_CF0

[6,16] Xhi_A9/CE_CF1

[6,16] Xhi_A10/IORD_CF

[16] Xhi_A11/IOWR_CF

[16] Xhi_A12/IORDY_CF

[16]

[16]

[16]

[16]

[16]

VDD_DAC

C2

100nF

XciCLK/GPF0

XciHREF/GPF1

XciPCLK/GPF2

XciRSTn/GPF3

XciVSYNC/GPF4

XciYDATA0/GPF5

XciYDATA1/GPF6

XciYDATA2/GPF7

XciYDATA3/GPF8

XciYDATA4/GPF9

XciYDATA5/GPF10

XciYDATA6/GPF11

XciYDATA7/GPF12

AC6

AE5

AE6

AE7

AC7

XdacOUT_0

XdacOUT_1

XdacIREF

XdacVREF

XdacCOMP

[15] XciYDATA[7:0]

[16] XdacOUT_0

[16] XdacOUT_1

R26

100nF

6.49K/R1005

AC1

AC2

AD2

AD3

AE3

AD4

AE4

AC3

Xadc_AIN0

Xadc_AIN1

Xadc_AIN2

Xadc_AIN3

Xadc_AIN4

Xadc_AIN5

Xadc_AIN6

Xadc_AIN7

Y4

Xadc_AIN0

Xadc_AIN1

Xadc_AIN2

Xadc_AIN3

Xadc_AIN4

Xadc_AIN5

Xadc_AIN6

Xadc_AIN7

XpllEFLITER

DISPLAY

1.8nF

XhiCSnmain/CE_CF1

XhiCSn/CE_CF0

XhiCSn_sub/CF_IORD

XhiWEn/CF_IOWR

XhiOEn/CF_IORDY

[8,12,16] XhiINTR

XhiINTR/BUF_DIR/GPM5

XhiOEn/CF_IORDY/EINT27/GPM4

XhiWEn/CF_IOWR/EINT26/GPM3

XhiCSn_sub/CF_IORD/EINT25/GPM2

XhiCSn/CE_CF0/EINT23/GPM0

XhiCSnmain/CE_CF1/EINT24/GPM1

XhiDATA17/EINT22/GPL14

XhiDATA16/EINT21/GPL13

XhiDATA15/kpROW7/CF_DATA15/GPK15

XhiDATA14/kpROW6/CF_DATA14/GPK14

XhiDATA13/kpROW5/CF_DATA13/GPK13

XhiDATA12/kpROW4/CF_DATA12/GPK12

XhiDATA11/kpROW3/CF_DATA11/GPK11

XhiDATA10/kpROW2/CF_DATA10/GPK10

XhiDATA9/kpROW1/CF_DATA9/GPK9

XhiDATA8/kpROW0/CF_DATA8/GPK8

XhiDATA7/txDATA/CF_DATA7/GPK7

XhiDATA6/txFLAG/CF_DATA6/GPK6

XhiDATA5/txWAKE/CF_DATA5/GPK5

XhiDATA4/txREADY/CF_DATA4/GPK4

XhiDATA3/rxDATA/CF_DATA3/GPK3

XhiDATA2/rxFLAG/CF_DATA2/GPK2

XhiDATA1/rxWAKE/CF_DATA1/GPK1

XhiDATA0/rxREADY/CF_DATA0/GPK0

AE21 XvVD0/GPI0

W14 XvVD1/GPI1

AE22 XvVD2/GPI2

V13 XvVD3/GPI3

AD21XvVD4/GPI4

AB20 XvVD5/GPI5

W15 XvVD6/GPI6

AE23 XvVD7/GPI7

V14 XvVD8/GPI8

AC21XvVD9/GPI9

AC22XvVD10/GPI10

W16 XvVD11/GPI11

V15 XvVD12/GPI12

AD23XvVD13/GPI13

W17 XvVD14/GPI14

AC24XvVD15/GPI15

V16 XvVD16/GPJ0

AD24XvVD17/GPJ1

Y22 XvVD18/GPJ2

AC25XvVD19/GPJ3

AB25 XvVD20/GPJ4

AB24 XvVD21/GPJ5

W18 XvVD22/GPJ6

AB23 XvVD23/GPJ7

C3

U1C

S3C6410X

ADC

CB5

Host I/F

DAC(TV)

DACVREF

TP9

XciYDATA0

XciYDATA1

XciYDATA2

XciYDATA3

XciYDATA4

XciYDATA5

XciYDATA6

XciYDATA7

G22

D25

F22

H19

D24

C25

E23

C24

G18

H17

B24

G17

B23

XhiADDR12/IORDY_CF/EINT20/GPL12

XhiADDR11/IOWR_CF/EINT19/GPL11

XhiADDR10/IORD_CF/EINT18/GPL10

XhiADDR9/CE_CF1/EINT17/GPL9

XhiADDR8/CE_CF0/EINT16/GPL8

XhiADDR7/kpCOL7/Xm0CData/GPL7

XhiADDR6/kpCOL6/Xm0REGata/GPL6

XhiADDR5/kpCOL5/Xm0INPACKata/GPL5

XhiADDR4/kpCOL4/Xm0RSTata/GPL4

XhiADDR3/kpCOL3/Xm0INTata/GPL3

XhiADDR2/kpCOL2/CF_ADDR2/GPL2

XhiADDR1/kpCOL1/CF_ADDR1/GPL1

XhiADDR0/kpCOL0/CF_ADDR0/GPL0

XciCLK

XciHREF

XciPCLK

XciRSTn

XciVSYNC

CAM I/F

[15]

[15]

[15]

[15]

[15]

Xhi_D8/DATA_CF8/KP_ROW0

Xhi_D9/DATA_CF9/KP_ROW1

Xhi_D10/DATA_CF10/KP_ROW2

Xhi_D11/DATA_CF11/KP_ROW3

Xhi_D12/DATA_CF12/KP_ROW4

Xhi_D13/DATA_CF13/KP_ROW5

Xhi_D14/DATA_CF14/KP_ROW6

Xhi_D15/DATA_CF15/KP_ROW7

[16] Xhi_D16

[16] Xhi_D17

R19

U23

U24

T19

U25

T18

V23

V25

U22

W23

U18

W24

U19

[16]

[16]

[16]

[16]

[16]

[16]

[16]

[16]

W25

V22

Y23

Y24

AA23

V18

M25

N17

N23

N18

N24

N25

P18

P23

P19

P25

R25

R24

R22

R23

T23

T24

T22

T25

AA25 XvHSYNC/GPJ8

W22 XvVSYNC/GPJ9

AA24 XvVDEN/GPJ10

V19 XvVCLK/GPJ11

XVD23

XVD22

XVD21

XVD20

XVD19

XVD18

XVD17

XVD16

XVD15

XVD14

XVD13

XVD12

XVD11

XVD10

XVD9

XVD8

XVD7

XVD6

XVD5

XVD4

XVD3

XVD2

XVD1

XVD0

[16]

[16]

[16]

[16]

[16]

XVD[23:0]

XHSYNC

XVSYNC

XVDEN

XVCLK

ADC

CON1

[14]

[14]

[14]

[14]

[14]

[14]

[14]

[14]

Xhi_D0/rxREADY/DATA_CF0

Xhi_D1/rxWAKE/DATA_CF1

Xhi_D2/rxFLAG/DATA_CF2

Xhi_D3/rxDATA/DATA_CF3

Xhi_D4/txREADY/DATA_CF4

Xhi_D5/txWAKE/DATA_CF5

Xhi_D6/txFLAG/DATA_CF6

Xhi_D7/txDATA/DATA_CF7

Xadc_AIN0

Xadc_AIN1

Xadc_AIN2

Xadc_AIN3

1

3

5

7

9

2

4

6

8

10

Xadc_AIN4

Xadc_AIN5

Xadc_AIN6

Xadc_AIN7

HDR10-2.54-MALE

R27

R28

R29

R30

0/R1005

0/R1005

0/R1005

0/R1005

Xadc_AIN4_YM

Xadc_AIN5_YP

Xadc_AIN6_XM

Xadc_AIN7_XP

[16]

[16]

[16]

[16]

SAMSUNG ELECTRONICS CO.,LTD

Title

SMDK6410 CPU Board (S3C6410 Evaluation Board)

Size

A3

Date:

5

Document Number

S3C6410 (I/O 2)/ADC

Monday, July 14, 2008

Rev

1.0

Sheet

1

of

16

VDD_LCD

VDD_SYS

VDD_MMC

VDD_PCM

VDD_UH

AE2

AD1

AD25

AE24

B25

A24

A2

B1

VDD_RTC

VDD_ARM0

VDD_ARM1

VDD_ARM2

VDD_ARM3

VDD_ARM4

VDD_ARM5

VDD_ARM6

VDD_ARM7

VDD_ARM8

VDD_ARM9

A7

D13

D18

H1

J18

L17

M22

P1

W1

Y25

AC20

AE16

VDD_INT0

VDD_INT1

VDD_INT2

VDD_INT3

VDD_INT4

VDD_INT5

VDD_INT6

VDD_INT7

VDD_INT8

VDD_INT9

VDD_INT10

VDD_INT11

R18

U15

AB19

W10

VDD_ALIVE0

VDD_ALIVE1

VDD_ALIVE2

VDD_ALIVE3

CTB2 CB7

+

VSS_SS

A8

B11

C2

C10

D3

D8

E2

F3

J3

K3

VDD_INT

U1D

S3C6410X

P9

100nF

VSS_OTGI

VSS_OTG1

VSS_OTG0

AB8

AE8

AB7

VSS_DAC

VSS_ADC

AC5

AD5

VSS_PERI7

VSS_PERI6

VSS_PERI5

VSS_PERI4

VSS_PERI3

VSS_PERI2

VSS_PERI1

VSS_PERI0

AC14

V17

U14

U12

U11

R17

J13

H18

VSS_MEM5

VSS_MEM4

VSS_MEM3

VSS_MEM1

VSS_MEM0

AB6

W8

U8

M9

J7

VSS_MPLL

VSS_EPLL

VSS_APLL

T8

V7

W4

0/R1005

CTB4 CB10

10uF/6.3V/T2012

VDD_EXT

CTB5 CB11

CTB6 CB12

100nF 100nF

10uF/6.3V/T2012

VDD_HI

CB9

+

100nF

10uF/6.3V/T2012

R204

CTB3 CB8

100nF

10uF/6.3V/T2012

VDD_OTGI

+

100nF

100nF

10uF/6.3V/T2012

1uF/6.3V/T2012

VDD_OTG

VDD_OTG1

FB1

CTB7 CB13 CB14

CTB8 CB15

BLM18BPG121

CTB10 CB19 CB20 CB21

CTB9 CB16 CB17 CB18

+

1uF

100nF 100nF

CTB11 CB22

+

1uF

100nF

10uF/6.3V/T2012

100nF 10nF

10uF/6.3V/T2012

100nF 10nF

10uF/6.3V/T2012

1uF

10uF/6.3V/T2012

10uF/6.3V/T2012

VDD_ALIVE

AC4 VDD_ADC

AD6 VDD_DAC

AC15VDD_SYS0

AD18VDD_SYS1

AC23VDD_LCD0

AD22VDD_LCD1

B17 VDD_MMC

A4 VDD_PCM

P24 VDD_HI0

V24 VDD_HI1

C21 VDD_EXT

N19 VDD_UH

AC9 VDD_OTG0

AD11VDD_OTG1

AC10VDD_OTGI

VDD_MEM0_0

VDD_MEM0_1

VDD_MEM0_2

VDD_MEM0_3

VDD_MEM0_4

VDD_MEM1_0

VDD_MEM1_1

VDD_MEM1_2

VDD_MEM1_3

VDD_MEM1_4

B8

B9

C14

G10

J19

V1

VDD_SS

VDD_APLL

VDD_EPLL

VDD_MPLL

F4

G3

K2

M1

R1

AA1

AB1

AB2

VDD_APLL

VDD_EPLL

VDD_MPLL

AC11VDD_RTC

CTB1 CB6

NC7

NC6

NC5

NC4

NC3

NC2

NC1

NC0

VDD_ARM

D

VSS_IP7

VSS_IP6

VSS_IP5

VSS_IP4

VSS_IP3

VSS_IP2

VSS_IP1

VSS_IP0

VDD_MEM0

U13

P17

R9

N9

L9

K8

J12

H8

CTB12

VDD_MEM1

CTB13

CB23 CB24 CB25 CB26 CB27 CB28

CTB14

CTB15 CB29 CB30 CB31 CB32 CB33

100nF 100nF 100nF 100nF 100nF 100nF

100nF 100nF 100nF 100nF 100nF

10uF/6.3V/T2012

10uF/6.3V/T2012

VDD_DAC

VDD_ADC

10uF/6.3V/T2012

10uF/6.3V/T2012

VDD_DAC

VDD_MPLL

VDD_APLL

VDD_EPLL

VDD_ALIVE

VDD_SS

FB2

VDD_SS

BLM18BPG121

CTB16 CB34

VDD_RTC

VDD_MEM0

100nF

100nF

VDD_OTG

VDD_LCD

CTB20 CB38

CTB21 CB39

CTB22 CB40

100nF

100nF

100nF

100nF

100nF

10uF/6.3V/T2012

10uF/6.3V/T2012

10uF/6.3V/T2012

10uF/6.3V/T2012

10uF/6.3V/T2012

10uF/6.3V/T2012

VDD_UH

VDD_MMC

VDD_PCM

CTB19 CB37

10uF/6.3V/T2012

VDD_OTG1

VDD_SYS

CTB18 CB36

CTB17

VDD_OTGI

VDD_MEM1

CB35

VDD_EXT

VDD_HI

VDD_ARM

VDD_INT

CTB23

CTB24

CB41 CB42 CB43 CB44 CB45 CB46 CB47

CTB25

CTB26

CTB27 CB48 CB49 CB50 CB51 CB52 CB53 CB54 CB55 CB56

SAMSUNG ELECTRONICS CO.,LTD

100nF 100nF 100nF 100nF 100nF 100nF 100nF

Title

100nF 100nF 100nF 100nF 100nF 100nF 100nF 100nF 100nF

SMDK6410 CPU Board (S3C6410 Evaluation Board)

10uF/6.3V/T2012

10uF/6.3V/T2012

Size

A3

10uF/6.3V/T2012

10uF/6.3V/T2012 10uF/6.3V/T2012

Date:

5

Document Number

S3C6410 (Power)

Monday, July 14, 2008

Rev

1.0

Sheet

1

of

16

C_PWR_5V

R34

100K/R1005

VDD_D

R32

100K/R1005

R33

100K/R1005

CT1

R35

330K/R1005

[7] XPWRRGTON_SW

[8] CORE_PWR_OK

R37

NC/R1005

10

R38

VDD_D

7

R36

100K/R1005

SN74LVC573APW

C6

6.8nF

U9A

R40

1

7

SN74LVC2G08DCTR

10K/R1005

PGDOD

VIN

27

TG

SW

FDS6982

BOOST

VID0

VID1

VID2

VID3

VID4

Q1A

C5

28

26

JP1

330pF

INTVCC

EXTVCC

VON

14

ITH

20

22

19

SGND

18

17

OPOUT

OP+

SENSE

FCB

BG

VFB

PGND

CT2

VDD_ARM

A2-2PA-2.54DSA

L1

2.2uH (LQH32CN2R2M33)

D1

11

C9

500pF

R41

<Silk>

ARM

RP1

0/R1608

PVDD_ARM

CMPSH-3

Q1B

330uF/16V/T6032

4

R39

1/R1005

VOSENSE

VRNG

23

13

FDS6982

OPVIN

OP-

15

16

CT3

+

4.7uF/6.3V/T3216

LTC3714EG

C

VDD_D

nARM_REG_LE

"Output H : Data

Change"

12

C7

100pF

C8

100pF

20K/R1005

[4,16] Xhi_A8/CE_CF0

C

21

7

8

9

24

25

0/R1005

[2,3,14,16] XnRESET

ION

LE

OE

RUN/SS

11

1

19

18

17

16

15

14

13

12

Q1

Q2

Q3

Q4

Q5

Q6

Q7

Q8

100uF/16V/T6032

20

D1

D2

D3

D4

D5

D6

D7

D8

VDD_D

2

3

4

5

6

7

8

9

XEINT11

XEINT12

XEINT13

XEINT14

XEINT15

C4

100nF

10

U8

GND

[3,16]

[3,13,16]

[3,13,16]

[3,16]

[3,16]

U7

VDD_ARM_VID1

VDD_ARM_VID2

VDD_D

10/R1005

R31

VDD_D

U10

1

4

2

CORE_REG_OE

SN74LVC1G00DBV

R42

CORE_REG_OE

"Output H : Latch

Output Enable"

VDD_D

10K/R1005

U9B

8

C_PWR_5V

SN74LVC2G08DCTR

VDD_D

VDD_D

[4,16] Xhi_A10/IORD_CF

CT4

VDD_ARM_VID1

VDD_ARM_VID2

VDD_INT_VID

CORE_REG_OE

11

1

LE

OE

VDD_D

20

[4,16] Xhi_A9/CE_CF1

8

7

6

5

D1

D2

D3

D4

D5

D6

D7

D8

Q1

Q2

Q3

Q4

Q5

Q6

Q7

Q8

19

18

17

16

15

14

13

12

SN74LVC573APW

R60

C14

100pF

R63

100K/R1005

C15

500pF

[1]

[2]

ON (1)

VDD_ARM

[2][1]

R51

6.8nF

R49

C12

20K/R1005

CFG1

R48

R58

100K/R1005

KHS04

R61

100K/R1005

10

RUN/SS

ION

21

12

PGDOD

VIN

27

TG

SW

FDS6982

BOOST

7

8

9

24

25

GND

R62

100K/R1005

CFG1

1

2

3

4

2

3

4

5

6

7

8

9

10

XEINT11

XEINT12

XEINT13

XEINT14

XEINT15

R57

R56

[3,16]

[3,13,16]

[3,13,16]

[3,16]

[3,16]

10K/R1005

10K/R1005

10K/R1005

R55

VDD_D

U12

100uF/16V/T6032

7

0/R1005

C10

100nF

VID0

VID1

VID2

VID3

VID4

11

VON

14

ITH

20

22

19

SGND

18

17

OPOUT

OP+

C11

INTVCC

EXTVCC

28

26

JP2

330pF

FCB

BG

VFB

PGND

CT5

VDD_INT

A2-2PA-2.54DSA

L2

2.2uH (LQH32CN2R2M33)

D2

SENSE

C13

100pF

Q2A

1

R54

VDD_D

R50

330K/R1005

U11

NC/R1005

R53

10/R1005

<Silk>

INT

RP2

0/R1608

PVDD_INT

CMPSH-3

Q2B

330uF/16V/T6032

4

R59

1/R1005

FDS6982

3

VDD_INT_VID

100K/R1005

NC/R1005

R45

XPWRRGTON_SW [7]

100K/R1005

R52

R47

10K/R1005

100K/R1005

R44

0/R1005

NC/R1005

R46

R43

100K/R1005

INT_REG_LE

VOSENSE

VRNG

23

13

OPVIN

OP-

15

16

CT6

+

4.7uF/6.3V/T3216

LTC3714EG

OFF (0)

11=1.0V

01=1.2V

10=1.1V

00=1.3V

SAMSUNG ELECTRONICS CO.,LTD

Title

SMDK6410 CPU Board (S3C6410 Evaluation Board)

[3]

VDD_INT 1.0V

VDD_INT 1.2V

[4]

PWRControl Enable

PWRControl Disable

Size

A3

Date:

Document Number

Power (ARM, INT)

Monday, July 14, 2008

Rev

1.0

Sheet

1

of

16

Vout=0.8(1+R1/R2)

R1=R2(Vout/0.8V-1)

[6] XPWRRGTON_SW

SHDN

VDD_D

1

2

D

CT7

IN0

IN1

10uF/6.3V/T2012

POK

OUT1

OUT0

3

8

7

JP3

SET

GND

(1.2V)

100K/R1005

R64

VDD_APLL

<Silk>

RP3

0/R1608

R65

15K/R1005

PVDD_PLL

R66

R1

A2-2PA-2.54DSA

MAX1806EUA15

R70

169K,1%/R1005

R2

33/R1005

VBUS

DD+

GND

CON3

[3,9]

[3]

[3]

[3]

USB(HOST)

SOCKET

MPLL

C16

VBUS

DD+

ID

GND

15K/R1005

USB-MINIAB

DN and DP should be routed evenly

<Silk>

1

2

3

4

5

XVBUS

XotgDM

XotgDP

XotgID

USB DUAL Port - A Type (Host)

VDD_MPLL

10uF/6.3V/T2012

1

2

3

4

R69

R67

JP4

CT8

CON2A

33/R1005

[3] XusbhDN

[3] XusbhDP

84.5K,1%/R1005

C_PWR_5V

APLL

R68

A2-2PA-2.54DSA

U13

4

CT9

100nF

RP4

0/R1608

10uF/6.3V/T2012

A2-2PA-2.54DSA

JP5

VDD_EPLL

R71

15K/R1005

<Silk>

EPLL

RP5

0/R1608

C_PWR_5V

C_PWR_5V

U14

CON2B

5

6

7

8

USBH_DTP10

R74

USBH_D+

TP11

VBUS

DD+

GND

USB(HOST)

SOCKET

[3] XotgDRV_VBUS

R72

0/R1005

R73

110K/R1005 2

USB DUAL Port - A Type (Host)

C19

15K/R1005

nSKIP

OUT

nSHDN

CXP

CXN

PGND

IN

GND

XVBUS [3,9]

C17

C18

0.47uF

2.2uF

MAX682ESA

1uF

Vout=0.8(1+R1/R2)

R1=R2(Vout/0.8V-1)

SHDN

1

2

IN0

IN1

POK

OUT1

OUT0

3

8

7

SET

GND

CT10

10uF/6.3V/T2012

R76

100K/R1005

A2-2PA-2.54DSA

R77

(1.2V)

R1

84.5K,1%/R1005

MAX1806EUA15

R78

169K,1%/R1005

R2

JP6

2

Alive

RP6

0/R1608

[8,15] REG_EN

CT13

RUN

SW

VFB

10uF/6.3V/T2012

PVDD_ALIVE

L3

2.2uH (LQH32CN2R2M33)

3

5

1M,1%/R1005

C22

22pF

VDD_RTC

1

<Silk>

R2

R1

(2.5V) JP7

2

R79

VDD

OE

OUT

GND

[3] XREXT

XotgTO [3]

RTC

CT12

RP7

0/R1608

X1

R75

R946

44.2 ohm,1%/R1005

48MHz (SMD,SCO-103)

A2-2PA-2.54DSA

+ LTC3406ES5

2

VIN

10uF/6.3V/T2012

U16

GND

XotgTI [3]

OSC1

Vout=0.6(1+R2/R1)

R2=R1(Vout/0.6V-1)

C_PWR_5V

XotgTO

TP12

<Silk>

CT11

NC (48MHz,CRYSTAL_SX-8)

VDD_D

VDD_Alive

4

VDD_D

[8,15] REG_EN

fundermental

Oscillator

tolerance +-100ppm

peak jitter 100ps

duty cycle

40/60~60/40

swing 3.3V

NC (1M)/R1005

U15

XotgTO [3]

For USB Clock

C20

C21

15pF

15pF

PVDD_RTC

10uF/6.3V/T2012

R80

316K,1%/R1005

XPWRRGTON_SW [6]

1

A1

A2

C1

B1

B2

C_PWR_5V

C2

[3,9] XPWRRGTON

CFG5

CFG5

CAS220A1

Use PMIC

R950 100K/R1005

Use Adapter

VDD_D

R952 NC (10K)/R1005

R951

100K/R1005

[8,15] REG_EN

SAMSUNG ELECTRONICS CO.,LTD

Title

SMDK6410 CPU Board (S3C6410 Evaluation Board)

Size

A3

Date:

Document Number

Power (PLL, Alive, RTC)/USB Host/USB OTG

Monday, July 14, 2008

Sheet

1

Rev

1.0

7

of

16

A2-2PA-2.54DSA

SYS

VDD_PCM

PVDD_AUDIO

RP10

<Silk>

A2-2PA-2.54DSA

Vout=0.6(1+R2/R1)

R2=R1(Vout/0.6V-1)

0/R1608

C_PWR_5V

VDD_ADC

RP12

<Silk>

ADC A2-2PA-2.54DSA

JP14

[7,15] REG_EN

VDD_DAC

VIN

RUN

SW

VFB

0/R1608

CT14

10uF/6.3V/T2012

DAC

R84

80K,1%/R1005

VDD_UH

UH

RP16

A2-2PA-2.54DSA

JP18

2

MMC

LED2

<Silk>

LED-Red (SMD 3216)

CORE

1

RP15

0/R1608

SMEM

[6] CORE_PWR_OK

R85

Q3

MMBT3904LT1

1K/R1005

A2-2PA-2.54DSA

VDD_SS

JP17

PVDD_SS

1

RP17

<Silk>

0/R1608

VDD_EXT

[3,13,16] XPWM_ECLK

VDD_D

PVDD_UH_MMC

[4,12,16] XhiINTR

[3,16] XEINT7/KP_ROW7

PVDD_EXT

RP19

R86

0/R1005

R87

R88

NC/R1005

NC/R1005

USB20_EN

NC/R1608

0/R1608

PVDD_AUDIO

A2-2PA-2.54DSA

VDD_LCD

1

RP22

LCD

0/R1608

0/R1608

RP20

<Silk>

RP13

JP20

3.3V

<Silk>

VR1

A2-2PA-2.54DSA

EXT

<Silk>

SS

JP19

PVDD_LCD

RP21

NC/R1608

0/R1608

VDD_D

VDD_D

R89

10K/R1005

VDD_HI

1

2

3

A2-3PA-2.54DSA

33uF/6.3V/T3528

0/R1608

RP18

JP22

100nF

<Silk>

VDD_MMC

<Silk>

LED1

DMEM A2-2PA-2.54DSA

JP15 VDD_SMEM

500K

R1

PVDD_UH_MMC

<Silk>

CT15

C23

A2-2PA-2.54DSA

JP16

500K,1%/R1005

R82

510/R1005

LED-Red (SMD 3216)

VDD_DMEM

<Silk>

R2

0/R1608

A2-2PA-2.54DSA

JP13

R83

LTC3406ES5

RP14

<Silk>

RP11

C_PWR_5V

R81

510/R1005

MEM1

L4

2.2uH (LQH32CN2R2M33)

0/R1608

<Silk>

VDD_1.8V

U17

GND

PCM

JP12

VDD_D

0/R1608

RP9

MEM0 A2-2PA-2.54DSA

JP11 VDD_MEM1

JP10

PVDD_MEM

<Silk>

A2-2PA-2.54DSA

VDD_MEM0

JP9

2

<Silk>

A2-2PA-2.54DSA

PVDD_SYS

0/R1608

RP8

VDD_SYS

1

JP8

2

VDD_D

Vout=0.8(1+R1/R2)

R1=R2(Vout/0.8V-1)

PVDD_HI

RP24

0/R1608

U18

4

VDD_1.8V

SHDN

C_PWR_5V

CT16

10uF/6.3V/T2012

1

2

SET

R91

GND

R2

100K,1%/R1005

A2-2PA-2.54DSA

(1.2V)

R1

84.5K,1%/R1005

VDD_OTGI

JP21

2

GND

GND

GND

MTH1

MTH2

MTH3

MTH4

PVDD_OTGI

1

RP23

<Silk>

GND

0/R1608

OTGI

R92

169K,1%/R1005

CT17

10uF/6.3V/T2012

U39

R953

0/R1005

R90

MAX1806EUA15

VDD_D

R968

10K/R1005

IN0

IN1

3

8

7

POK

OUT1

OUT0

USB20_EN

4

2

R954

0/R1005

Vout=0.8(1+R1/R2)

R1=R2(Vout/0.8V-1)

SN74AUC1G08DBV

3

[7,15] REG_EN

GND

GND

GND

GND

GND

GND

TPH1

TPH2

TPH3

TPH4

TPH5

TPH6

U19

4

C_PWR_5V

1

2

CT18

10uF/6.3V/T2012

SHDN

IN0

IN1

POK

OUT1

OUT0

3

8

7

R93

SET

R94

GND

MAX1806EUA33

R2

100K,1%/R1005

A2-2PA-2.54DSA

(3.3V)

R1

75K,1%/R1005

R95

24.3K,1%/R1005

JP23

2

<Silk>

VDD_OTG

PVDD_OTG

1

RP25

0/R1608

SAMSUNG ELECTRONICS CO.,LTD

OTG

Title

CT19

10uF/6.3V/T2012

SMDK6410 CPU Board (S3C6410 Evaluation Board)

Size

A3

Date:

Document Number

Power (I/O)

Monday, July 14, 2008

Rev

1.0

Sheet

1

of

16

ZD1

JACK1

Onsemi 1SMB5920BT3G (6.2V)

DC_5V

<Silk>

OFF

DC 5V,3A

PVDD_RTC

TP15

TP14

TP16

TP17

<Silk>

PWR ON

Battery

Connector

RP31

0/R1608

PVDD_MEM

PVCCAUX1

BUCK2_VDDINT

BUCK2_VDDINT

E5

E6

E7

F5

F6

F7

BUCK3_VDDMEM0/VDDMEM1

BUCK3_VDDMEM0/VDDMEM1

BUCK3_VDDMEM0/VDDMEM1

BUCK3_VDDMEM0/VDDMEM1

BUCK3_VDDMEM0/VDDMEM1

BUCK3_VDDMEM0/VDDMEM1

E19

F19

PVDD_PLL

F4

G4

PVDD_HI

E17

F17

PVCCAUX3

PVDD_UH_MMC

PVCCAUX2

B

PVDD_EXT

VLDO5_VDDUH/VDDMMC

VLDO5_VDDUH/VDDMMC

H6

J6

VLDO6_VCCAUX2

VLDO6_VCCAUX2

F2

G2

G8

TP38

PVDD_OTGI

H13

J13

PVDD_SYS

H18

J18

PVCCM2MTV

H3

J3

PVDD_LCD

H15

J15

PVDD_SS

F3

G3

PVDD_OTG

H17

J17

PVDD_ALIVE

H2

J2

PVDD_AUDIO

J5

H4

H5

TP44

SEAM-20-02.0-SM-10-2-A

VLDO7_VDDEXT

VLDO7_VDDEXT

VLDO8_VCCM3BT

VLDO8_VCCM3BT

LDO8_EN(Reserved)

VLDO9_VDDOTGI

VLDO9_VDDOTGI

VLDO10_VDDSYS

VLDO10_VDDSYS

B1

J16

J4

H16

G7

E18

C2

R98

R99

R100

R101

R102

0/R1005

0/R1005

0/R1005

0/R1005

0/R1005

PCM_CLK

PCM_FSYNC

PCM_SDI

PCM_SDO

C10

C9

C8

C7

R103

R104

R105

R106

0/R1005

0/R1005

0/R1005

0/R1005

A2

2

RP33

NC/R1608

CFG2

+

5268-02A

CAS220A1

C2

B2

6

Reserved

Reserved

Reserved

Reserved

Reserved

Reserved

C3

C4

C5

C6

ADC_IN4

ADC_IN5

ADC_IN6

ADC_IN7

F11

F12

E11

E12

G19

VVIB

TSI_XM

TSI_XP

TSI_YM

TSI_YP

H8

J8

G14

G15

H19

J19

MIC1_N

MIC1_P

MIC2_N

MIC2_P

MIC_BIAS_INT

MIC_BIAS_EXT

G16

G17

G18

WLED_BOOST

WLED_OUT1

WLED_OUT2

G12

G13

D12

LED_DRV1

LED_DRV2

FLASH_EN

H12

J12

E9

E10

D9

D10

D2

VCHGR

VCHGR

VCHGR

VCHGR

TBAT

CON5

0/R1608

XVBUS [3,7]

XPCM_EXTCLK1/I2S_CDCLK1/AC97_RSTn0 [3,16]

XPCM_EXTCLK0/I2S_CDCLK0/AC97_RSTn0 [3,16]

XPCM_DCLK0/I2S_CLK0/AC97_BITCLK0 [3,16]

XPCM_FSYNC0/I2S_LRCLK0/AC97_SYNC0 [3,16]

XPCM_SIN0/I2S_DI0/AC97_SDI0 [3,16]

XPCM_SOUT0/I2S_DO0/AC97_SDO0 [3,16]

XPCM_DCLK1/I2S_CLK1/AC97_BITCLK0 [3,16]

XPCM_FSYNC1/I2S_LRCLK1/AC97_SYNC0 [3,16]

XPCM_SIN1/I2S_DI1/AC97_SDI0 [3,16]

XPCM_SOUT1/I2S_DO1/AC97_SDO0 [3,16]

B8

B9

Xi2cSCL0 [3,15,16]

Xi2cSDA0 [3,15,16]

PWR_I2C_SCL

PWR_I2C_SDA

D11

C11

TP29

TP30

nVDD_FAULT

nBATT_FAULT

SYS_EN

PWR_EN

nPMIC_IRQ

nSLEEP

EXT_WAKEUP1

EXT_WAKEUP0

nONKEY

nEXTON

nRST_IN

REM_IN

nRST_OUT

B15

B13

B12

B11

B10

B5

B4

B3

B2

D19

D7

D6

D5

TP31

XnBATF [2,3]

TP32

XPWRRGTON [3,7]

PMIC_XEINT12_IRQn [3]

TP33

TP34

TP35

PMIC_ONKEYn [2]

TP36

R969

VMID

AUD_AMP_EN

AUDIO_LINEOUT

STEREO_CH2

STEREO_CH1

BEAR_SPK_N

BEAR_SPK_P

MONO_SPK_N

MONO_SPK_P

AUD_AUX3_IN

AUD_AUX2_IN

AUD_AUX1_IN

C17

D8

C19

C18

C16

C15

C14

C13

C12

B19

B18

B17

PMIC_STEREO_VMID [16]

TP37

PMIC_MODEM_MIC_P [16]

PMIC_STEREO_CH2 [16]

PMIC_STEREO_CH1 [16]

PMIC_BEAR_SPK_N [16]

PMIC_BEAR_SPK_P [16]

PMIC_MONO_SPK_N [16]

PMIC_MONO_SPK_P [16]

TP39

PMIC_MODEM_SPK_N [16]

PMIC_MODEM_SPK_P [16]

Reserved

Reserved

Reserved

Reserved

Reserved

Reserved

Reserved

Reserved

Reserved

B16

B14

B7

B6

D4

D3

D15

D14

D13

GND

GND

GND

GND

J20

J1

H20

H1

0/R1608

nRESET [2]

PMIC_REM_IN [16]

PMIC_nRST_OUT [2]

B

VLDO11_VCCM2MTV

VLDO11_VCCM2MTV

VLDO12_VDDLCD

VLDO12_VDDLCD

VLDO13_VDDGPS/VCCM1GPS

VLDO13_VDDGPS/VCCM1GPS

VLDO14_VDDOTG

VLDO14_VDDOTG

VLDO15_VDDALIVE

VLDO15_VDDALIVE

VLDO_AUDIO_VDDPCM/VDDADC/VDDDAC

VLDO_ADC(Reserved)

VBUS_XVBUS

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

A11

A12

A13

A14

A15

A16

A17

A18

A19

A20

C1

C20

D1

D20

G1

G20

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

[3,7] XVBUS

VLDO3_VDDHI

VLDO3_VDDHI

VLDO4_VCCAUX3

VLDO4_VCCAUX3

D18

D16

D17

F8

E8

I2C_SCL

I2C_SDA

VLDO2_VDDMPLL/VDDAPLL/VDDEPLL

VLDO2_VDDMPLL/VDDAPLL/VDDEPLL

E3

E4

I2S_CDCLK

I2S_BITCLK

I2S_SYNC

I2S_DATAOUT

I2S_DATAIN

MCLK

VLDO1_VCCAUX1

VLDO1_VCCAUX1

H7

J7

H14

J14

PVCCM3BT

H9

H10

H11

J9

J10

J11

G9

G10

G11

G5

G6

0/R1005

RP32

0/R1608

RP27

VCHGR

R97

A1

PVDD_INT

0/R1608

E2

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

RP26

SW5

CFG2

Power Off

CON3

(USB

OTG)

X

Operation & Charging

by DC

Charging by USB

TP40

TP41

TP42

TP43

JACK1

(DC)

CON4

(Battery)

X

X : Don't care

O : Insertion (Placement)

SAMSUNG ELECTRONICS CO.,LTD

K1

K2

K3

K4

K5

K6

K7

K8

K9

K10

K11

K12

K13

K14

K15

K16

K17

K18

K19

K20

E1

E16

E20

F1

F9

F10

F16

F20

B1

B20

PVDD_ARM

BUCK1_VDDARM

BUCK1_VDDARM

BUCK1_VDDARM

BUCK1_VDDARM

BUCK1_VDDARM

BUCK1_VDDARM

VRTC_VDDRTC

VRTC_VDDRTC

LED_PC

E13

E14

E15

F13

F14

F15

VBAT_IN

VBAT_IN

VBAT_IN

VBAT_IN

VBAT_IN

VBAT_IN

VBAT_IN

VBAT_IN

VBAT_IN

F18

2

1K/R1005

C1

LED-Red (SMD 3216)

CON4

RP30

NC/R1608

DC_5V

R96

NC/R1608

<Silk>

RP29

0/R1608

LED3

PMIC

RP28

CAS220A1

VBAT

C_PWR_5V

VCHGR TP13

TP28

TP27

TP19

TP21TP23 TP25

TP18 TP20 TP22TP24 TP26

VBAT

B1

<Silk>

POWER JACK (DC-JACK, DC-003)

SW5

B2

[16] WLED_OUT1

[16] WHITE_LED

[16]

[16]

[16]

[16]

PMIC_MIC1_N

PMIC_MIC1_P

PMIC_MIC2_N

PMIC_MIC2_P

F1

(1.5A, SMD, Poly Switch)

MicroSMD150-2

A1

2

3

A2

G

G

C1

C2

Title

SMDK6410 CPU Board (S3C6410 Evaluation Board)

Size

A3

Date:

Document Number

PMIC Socket

Monday, July 14, 2008

Rev

1.0

Sheet

1

of

16

U20

[2] Xm1ADDR[15:0]

Xm1ADDR0

Xm1ADDR1

Xm1ADDR2

Xm1ADDR3

Xm1ADDR4

Xm1ADDR5

Xm1ADDR6

Xm1ADDR7

Xm1ADDR8

Xm1ADDR9

Xm1ADDR10

Xm1ADDR11

Xm1ADDR12

J8

J9

K7

K8

K2

K3

J1

J2

J3

H1

J7

H2

H3

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10/AP

A11

A12

H8

H9

BA0

BA1

Xm1DQM0

Xm1DQM1

Xm1DQS0

Xm1DQS1

F8

F2

E8

E2

LDM

UDM

LDQS

UDQS

[2] Xm1CKE0

[2] Xm1SCLK

[2] Xm1SCLKn

G1

G2

G3

[2] Xm1ADDR14

[2] Xm1ADDR15

[2]

[2]

[2]

[2]

VDD_DMEM

CTB28

CB57 CB58 CB59 CB60 CB61 CB62

+

C

100nF 100nF 100nF 100nF 100nF 100nF

10uF/6.3V/T2012

Xm1DATA[31:0] [2]

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

A8

B7

B8

C7

C8

D7

D8

E7

E3

D2

D3

C2

C3

B2

B3

A2

nCS

nRAS

nCAS

nWE

H7

G9

G8

G7

CKE

CK

nCK

NC

NC

F3

F7

A9

F9

K9

VDD

VDD

VDD

VSS

VSS

VSS

A1

F1

K1

C9

E9

A7

B1

D1

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

C1

E1

A3

B9

D9

Xm1DATA0

Xm1DATA1

Xm1DATA2

Xm1DATA3

Xm1DATA4

Xm1DATA5

Xm1DATA6

Xm1DATA7

Xm1DATA8

Xm1DATA9

Xm1DATA10

Xm1DATA11

Xm1DATA12

Xm1DATA13

Xm1DATA14

Xm1DATA15

Xm1CSn0 [2]

Xm1RASn [2]

Xm1CASn [2]

Xm1WEn [2]

K4X51163PE-L(F)E/GC6

U22

[2] Xm1ADDR[15:0]

Xm1ADDR0

Xm1ADDR1

Xm1ADDR2

Xm1ADDR3

Xm1ADDR4

Xm1ADDR5

Xm1ADDR6

Xm1ADDR7

Xm1ADDR8

Xm1ADDR9

Xm1ADDR10

Xm1ADDR11

Xm1ADDR12

BA0

BA1

Xm1DQM2

Xm1DQM3

Xm1DQS2

Xm1DQS3

F8

F2

E8

E2

LDM

UDM

LDQS

UDQS

[2] Xm1CKE0

[2] Xm1SCLK

[2] Xm1SCLKn

G1

G2

G3

[2]

[2]

[2]

[2]

CTB30 CB69 CB70 CB71 CB72 CB73 CB74

A

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10/AP

A11

A12

H8

H9

[2] Xm1ADDR14

[2] Xm1ADDR15

VDD_DMEM

J8

J9

K7

K8

K2

K3

J1

J2

J3

H1

J7

H2

H3

Xm1DATA[31:0] [2]

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

A8

B7

B8

C7

C8

D7

D8

E7

E3

D2

D3

C2

C3

B2

B3

A2

nCS

nRAS

nCAS

nWE

H7

G9

G8

G7

CKE

CK

nCK

NC

NC

F3

F7

A9

F9

K9

VDD

VDD

VDD

VSS

VSS

VSS

A1

F1

K1

C9

E9

A7

B1

D1

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

C1

E1

A3

B9

D9

Xm1DATA16

Xm1DATA17

Xm1DATA18

Xm1DATA19

Xm1DATA20

Xm1DATA21

Xm1DATA22

Xm1DATA23

Xm1DATA24

Xm1DATA25

Xm1DATA26

Xm1DATA27

Xm1DATA28

Xm1DATA29

Xm1DATA30

Xm1DATA31

Just Only PADS on Lines

Xm1CSn0 [2]

Xm1RASn [2]

Xm1CASn [2]

Xm1WEn [2]

[2] Xm1ADDR0

TP45

M1A0

[2] Xm1DQM0

TP63

M1DQM0

[2] Xm1DATA0

TP47

M1D0

[2] Xm1DQM1

TP65

M1DQM1

[2] Xm1CKE0

TP49

M1CKE0

[2] Xm1DQM2

TP67

M1DQM2

[2] Xm1CKE1

TP51

M1CKE1

[2] Xm1DQM3

TP69

M1DQM3

[2] Xm1SCLK

TP53

M1SCLK

[2] Xm1DQS0

TP71

M1DQS0

[2] Xm1SCLKn

TP55

M1SCLKn

[2] Xm1DQS1

TP73

M1DQS1

[2] Xm1WEn

TP57

M1WEn

[2] Xm1DQS2

TP75

M1DQS2

[2] Xm1CASn

TP59

M1CASn

[2] Xm1DQS3

TP76

M1DQS3

[2] Xm1RASn

TP61

M1RASn

[2] Xm1CSn1

TP77

M1CSn1

TP78

Xm1CSn0

TP79

Xm1A13

[2] Xm1CSn0

[2] Xm1ADDR13

100nF 100nF 100nF 100nF 100nF 100nF

10uF/6.3V/T2012

SAMSUNG ELECTRONICS CO.,LTD

Title

SMDK6410 CPU Board (S3C6410 Evaluation Board)

K4X51163PE-L(F)E/GC6

Size

A3

Date:

5

Document Number

Memory (mDDR)

Monday, July 14, 2008

Rev

1.0

Sheet

1

10

of

16

VDD_D

VDD_BUF

A2-2PA-2.54DSA

VDD_BUF

VDD_SMEM

JP24

2

VDD_BUF

VDD_SMEM

<Silk>

U23

BUF

CB75

100nF

42

31

VCCA0

VCCA1

CB77

100nF

42

31

VCCA0

VCCA1

VCCB0

VCCB1

CB78

7

18

[2] Xm0ADDR[15:0]

100nF

[2,12] Xm0CSn0

[2,12] Xm0CSn1

[12,14] M0CSn2

[12,14] M0CSn3

[2,12] Xm0CSn4

[2,12] Xm0CSn5

[2] Xm0BE0

[2] Xm0BE1

B_ADDR[15:0] [16]

47

46

44

43

41

40

38

37

Xm0ADDR0

Xm0ADDR1

Xm0ADDR2

Xm0ADDR3

Xm0ADDR4

Xm0ADDR5

Xm0ADDR6

Xm0ADDR7

47

46

44

43

41

40

38

37

1A1

1A2

1A3

1A4

1A5

1A6

1A7

1A8

1B1

1B2

1B3

1B4

1B5

1B6

1B7

1B8

2

3

5

6

8

9

11

12

B_ADDR0

B_ADDR1

B_ADDR2

B_ADDR3

B_ADDR4

B_ADDR5

B_ADDR6

B_ADDR7

Xm0ADDR8

Xm0ADDR9

Xm0ADDR10

Xm0ADDR11

Xm0ADDR12

Xm0ADDR13

Xm0ADDR14

Xm0ADDR15

36

35

33

32

30

29

27

26

2A1

2A2

2A3

2A4

2A5

2A6

2A7

2A8

2B1

2B2

2B3

2B4

2B5

2B6

2B7

2B8

13

14

16

17

19

20

22

23

B_ADDR8

B_ADDR9

B_ADDR10

B_ADDR11

B_ADDR12

B_ADDR13

B_ADDR14

B_ADDR15

48

25

1OE

2OE

1DIR

2DIR

1

24

R108

DIR L : B->A

DIR H : A->B

[2,12,14] Xm0INTsm1/FREn

[2,14] Xm0INTsm0/FWEn

[2,14] Xm0RDY0/ALE

[2,14] Xm0RDY1/CLE

[12] Xm0OEata

[12] Xm0WEata

[12] Xm0RSTata

[12] Xm0REGata

VDD_SMEM

sn74AVCA164245

(A(1.8V) <-> B(3.3V))

A->B 1.6nS ~ 4.3nS

B->A 1.8nS ~ 5.5nS

100K/R1005

Propagation Delay

A->B 1.6nS ~ 4.3nS

B->A 1.8nS ~ 5.5nS

45

39

34

28

GND0

GND1

GND2

GND3

GND7

GND6

GND5

GND4

4

10

15

21

CB76

100nF

VCCB0

VCCB1

7

18

1A1

1A2

1A3

1A4

1A5

1A6

1A7

1A8

1B1

1B2

1B3

1B4

1B5

1B6

1B7

1B8

2

3

5

6

8

9

11

12

B_CSn_0 [16]

B_CSn_1 [16]

B_CSn_2 [16]

B_CSn_3 [16]

B_CSn_4 [16]

B_CSn_5 [16]

B_nBE0 [16]

B_nBE1 [16]

36

35

33

32

30

29

27

26

2A1

2A2

2A3

2A4

2A5

2A6

2A7

2A8

2B1

2B2

2B3

2B4

2B5

2B6

2B7

2B8

13

14

16

17

19

20

22

23

B_FREn [16]

B_FWEn [16]

B_ALE [16]

B_CLE [16]

B_OEata [16]

B_WEata [16]

B_RESET [16]

B_REGata [16]

48

25

1OE

2OE

1DIR

2DIR

1

24

45

39

34

28

GND0

GND1

GND2

GND3

GND7

GND6

GND5

GND4

4

10

15

21

U24

VDD_SMEM

R107

100K/R1005

SN74AVCA164245DGG

C

SN74AVCA164245DGG

VDD_BUF

VDD_SMEM

U25

CB79

100nF

42

31

VCCA0

VCCA1

Xm0DATA0

Xm0DATA1

Xm0DATA2

Xm0DATA3

Xm0DATA4

Xm0DATA5

Xm0DATA6

Xm0DATA7

47

46

44

43

41

40

38

37

Xm0DATA8

Xm0DATA9

Xm0DATA10

Xm0DATA11

Xm0DATA12

Xm0DATA13

Xm0DATA14

Xm0DATA15

CB80

VCCB0

VCCB1

7

18

1A1

1A2

1A3

1A4

1A5

1A6

1A7

1A8

1B1

1B2

1B3

1B4

1B5

1B6

1B7

1B8

2

3

5

6

8

9

11

12

B_DATA0

B_DATA1

B_DATA2

B_DATA3

B_DATA4

B_DATA5

B_DATA6

B_DATA7

36

35

33

32

30

29

27

26

2A1

2A2

2A3

2A4

2A5

2A6

2A7

2A8

2B1

2B2

2B3

2B4

2B5

2B6

2B7

2B8

13

14

16

17

19

20

22

23

B_DATA8

B_DATA9

B_DATA10

B_DATA11

B_DATA12

B_DATA13

B_DATA14

B_DATA15

48

25

1OE

2OE

1DIR

2DIR

1

24

45

39

34

28

GND0

GND1

GND2

GND3

GND7

GND6

GND5

GND4

4

10

15

21

100nF

[2,14] Xm0DATA[15:0]

VDD_BUF

VDD_SMEM

B_DATA[15:0] [16]

VDD_BUF

CB81

CB82

100nF

U26

100nF

42

31

VCCA0

VCCA1

VCCB0

VCCB1

7

18

47

46

44

43

41

40

38

37

1A1

1A2

1A3

1A4

1A5

1A6

1A7

1A8

1B1

1B2

1B3

1B4

1B5

1B6

1B7

1B8

2

3

5

6

8

9

11

12

36

35

33

32

30

29

27

26

2A1

2A2

2A3

2A4

2A5

2A6

2A7

2A8

2B1

2B2

2B3

2B4

2B5

2B6

2B7

2B8

13

14

16

17

19

20

22

23

48

25

1OE

2OE

1DIR

2DIR

1

24

45

39

34

28

GND0

GND1

GND2

GND3

GND7

GND6

GND5

GND4

4

10

15

21

R109

R110

4.7K/R1005

4.7K/R1005

[12] Xm0INTata

[12] Xm0INPACKata

[14] RnB

[12] Xm0CData

[2] Xm0WAITn/IORDY

TP80

TP82

[2]

[2]

[2]

[2]

M0ADDR16

M0ADDR17

M0ADDR18

M0ADDR19

[2,14] Xm0WEn/nIOWR_CF

[2,12,14] Xm0OEn/nIORD_CF

B_INTata [16]

B_INPACKata [16]

B_RnB [16]

B_CData [16]

B_WAITn/IORDY [16]

TP81

TP83

B_ADDR16

B_ADDR17

B_ADDR18

B_ADDR19

[16]

[16]

[16]

[16]

B_WEn/nIOWR_CF [16]

B_OEn/nIORD_CF [16]

VDD_SMEM

R111

R112

0/R1005

BUF_DIR [12]

SN74AVCA164245DGG

100K/R1005

VDD_SMEM

VDD_SMEM

8

R113

SN74AVCA164245DGG

[12] BCtrl_I0

[12] BCtrl_I1

U27A

100K/R1005

R114

SN74AUC2G08DCT

4

U27B

NC/R1005

SN74AUC2G08DCT

[3,16] XuRXD_3/ExdREQ/IrRXD/ADDR_CF2/Xi2cSCL1

SAMSUNG ELECTRONICS CO.,LTD

Title

SMDK6410 CPU Board (S3C6410 Evaluation Board)

Size

A3

Date:

5

Document Number

Buffers (SROM IF)

Monday, July 14, 2008

Rev

1.0

Sheet

1

11

of

16

CON14

SN74AUC2G08

Propagation Delay (CL30pF)

Typ: 1.5nS ( 1.2 ~ 2.1)

VDD_SMEM

VDD_SMEM

R115

100K/R1005

R117

100K/R1005

[2,11,14] Xm0INTsm1/FREn

R118

7

2

SN74AUC2G08DCT

VDD_SMEM

[2,11] Xm0CSn5

[2,11] Xm0CSn4

0/R1005

SN74AUC2G08DCT

R127

0/R1005

U28B

5

MP0_DOEn

[3,15,16] XIrSDBW

3

R129 NC/R1005

SN74AUC2G08DCT

[4,8,16] XhiINTR

R125

NC/R1005

R128

NC/R1005

R119

100K/R1005

R123

100K/R1005

BCtrl_I1 [11]

6

SN74AUC2G08DCT

U31B

[2] Xm0REGata/SS_GPO0

R126 0/R1005

U29B

R1300/R1005

SN74AUC2G08DCT

VDD_SMEM

R122

4.7K/R1005

nOE_CF

U30B

BUF_DIR [11]

4

R121

NC/R1005

U30A

100K/R1005

U29A

[2,11,14] Xm0OEn/nIORD_CF

U28A

R116

SN74AUC2G08DCT

5

3

6

R131

0/R1005

SN74AUC2G08DCT

C

VDD_SMEM

SN74AUC2G08

Propagation Delay (CL30pF)

Typ: 1.5nS ( 1.2 ~ 2.1)

R135

0/R1005

nOE

2

3

SN74AUC2G08DCT

100K/R1005

R124

100K/R1005

[11,14] M0CSn2

[11,14] M0CSn3

U32B

R133

100K/R1005

GND

VDD_SMEM

R120

VCC

VDD_SMEM

C_PWR_5V

[3,15,16] XIrSDBW

NC(0)/R1005 1

[2,11] Xm0CSn1

SS_TCXO_CLK

U31A

U33

R206

MP0_DOEn

SN74AUC1G125DBV

U32A

7

BCtrl_I0 [11]

SN74AUC2G08DCT

SS_GPO0

SS_GPO1

SS_GPO3

SS_REAL_IN

SS_GPO2

[2] XGPO5

[2,11] Xm0CSn0

VDD_SMEM

R132

100K/R1005

VDD_SMEM

GND

VDD_SMEM

VDD_SMEM

2

4

6

8

10

12

14

16

18

20

22

24

26

28

30

32

34

36

38

40

42

44

46

48

50

52

54

56

58

60

62

64

66

68

70

72

74

76

78

80

82

84

86

88

90

92

94

96

98

100

102

104

106

108

110

112

114

116

118

120

1

3

5

7

9

11

13

15

17

19

21

23

25

27

29

31

33

35

37

39

41

43

45

47

49

51

53

55

57

59

61

63

65

67

69

71

73

75

77

79

81

83

85

87

89

91

93

95

97

99

101

103

105

107

109

111

113

115

117

119

SN74AUC2G08DCT

QSE-060-01-L-D-A

VDD_SMEM

VDD_SMEM

U34

[2] Xm0REGata/SS_GPO0

[2] Xm0WEata/SS_GPO1

[2] Xm0OEata/SS_GPO2

[2] Xm0CData/SS_GPO3

[2] Xm0INTata/SS_REAL_IN

[2] Xm0RSTata/SS_IMG_IN

[2] Xm0INPACKata/SS_TCXO_CLK

R932

R933

R934

R935

R936

R937

R938

0/R1005

0/R1005

0/R1005

0/R1005

0/R1005

0/R1005

0/R1005

R939

R940

R941

R942

R943

R944

R945

0/R1005

0/R1005

0/R1005

0/R1005

0/R1005

0/R1005

0/R1005

1

SS_GPO0

SS_GPO1

SS_GPO2

SS_GPO3

SS_REAL_IN

2

[2] Xm0OEata/SS_GPO2

IN

GND

VCC

NC

COM

NO

R134

0/R1005

XhiINTR [4,8,16]

nOE_CF

TS5A3159DBV_SPDT

SS_TCXO_CLK

Xm0REGata [11]

Xm0WEata [11]

Xm0OEata [11]

Xm0CData [11]

Xm0INTata [11]

Xm0RSTata [11]

Xm0INPACKata [11]

SAMSUNG ELECTRONICS CO.,LTD

Title

SMDK6410 CPU Board (S3C6410 Evaluation Board)

Size

A3

Date:

5

Document Number

Buffers Control (SROM IF)/SS

Monday, July 14, 2008

Rev

1.0

Sheet

1

12

of

16

VDD_MMCD

DAT3

5

6

7

8

9

10

11

12

DAT4

NC

CMD

NC

DAT5

NC

VSS

NC

13

14

15

NC

VDD

NC

[3] XmmcDATA1_0

16

17

18

19

20

21

22

23

24

25

NC

CLK

NC

DAT6

NC

VSS

NC

DAT7

NC

DAT0

[3] XmmcDATA1_1

26

DAT1

[3] XmmcCDN0/mmcCDN1

27

SD_CD

28

SD_WP

[3] XmmcCMD1

[3] XmmcDATA1_5/mmcDATA2_1/ADDR_CF1

R152

VDD_MMCD

[3] XmmcCLK1

[3] XmmcDATA1_6/mmcDATA2_2/ADDR_CF2

C

[3] XmmcDATA1_7/mmcDATA2_3

R155

[3,8,16] XPWM_ECLK

SD0_nWP

NC/R1005

VDD_MMCD

JP25

MMCD

A2-3PA-2.54DSA

B_MMC_CMD

R153

NC/R1005

PVDD_UH_MMC

VDD_MMCD

B_MMC_DATA0

29

<Silk>

MMC CD

2

For HS-SPI test

[3]

[3]

[3]

[3]

CON8

[3] XspiCS0

[3] XspiMISO0

[3] XspiMOSI0

[3] XspiCLK0

1

2

3

4

D1+

D1D2+

D2-

GND

GND

XmmcDATA0_0

XmmcDATA0_1

XmmcDATA0_2

XmmcDATA0_3

[3] XmmcCLK0

[3] XmmcCMD0

RA1

R159

R160

0/R1005

0/R1005

13

14

15

NC

VDD

NC

16

17

18

19

20

21

22

23

24

25

NC

CLK

NC

DAT6

NC

VSS

NC

DAT7

NC

DAT0

26

DAT1

0/R1005

27

SD_CD

R157

NC/R1005

28

SD_WP

R158

NC/R1005

B_MMC_DATA0

B_MMC_DATA1

B_MMC_DATA2

B_MMC_DATA3

B_MMC_CLK

B_MMC_CMD

30

P30/GND

DAT4

NC

CMD

NC

DAT5

NC

VSS

NC

SD/HSMMC Socket (Taisol 156-1001000901))

LED-Green (SMD 3216)

[3] XmmcCDN0/mmcCDN1

[3,6,16] XEINT13

LED4

<Silk>

Channel 1

DAT3

5

6

7

8

9

10

11

12

R156

B_MMC_DATA1

[3] XmmcCDN0/mmcCDN1

[3,6,16] XEINT12

SD/HSMMC Socket (Taisol 156-1001000901))

DAT2

VDD_MMCD

B_MMC_CLK

R154

330/R1005

NC

NC

B_MMC_DATA2

B_MMC_DATA3

<Silk>

1

2

3

1

2

P29/GND

P29/GND

[3] XmmcDATA1_2

[3] XmmcDATA1_3

[3] XmmcDATA1_4/mmcDATA2_0/ADDR_CF0

NC/R1005

30

VDD_D

29

DAT2

50K/R1005

50K/R1005

10K/R1005

50K/R1005

50K/R1005

NC

NC

CON7

R147

R148

R149

R150

R151

1

2

SDDATA & CLK path must be

same length and route

P30/GND

CON6

R136

R137

R138

R139

R140

R141

R142

R143

R144

R145

R146

50K/R1005

50K/R1005

50K/R1005

10K/R1005

50K/R1005

50K/R1005

50K/R1005

50K/R1005

50K/R1005

50K/R1005

50K/R1005

VDD_MMCD

SDDATA & CLK path must be

same length and route

<Silk>

CFG6

IIS 5.1 [ON]

Channel 0

IIS 5.1[OFF]

[1]

[ON]

[OFF]

[2]

[ON]

[OFF]

[3]

[ON]

[OFF]

[4]

[ON]

[OFF]

CFG6

[3]

[3]

[3]

[3]

1

2

3

4

XmmcDATA1_4/mmcDATA2_0/ADDR_CF0

XmmcDATA1_5/mmcDATA2_1/ADDR_CF1

XmmcDATA1_6/mmcDATA2_2/ADDR_CF2

XmmcDATA1_7/mmcDATA2_3

8

7

6

5

B_HSMMC_DAT4/i2sMULTI_BCLK [16]

B_HSMMC_DAT5/i2sMULTI_CDCLK [16]

B_HSMMC_DAT6/i2sMULTI_LRCLK [16]

B_HSMMC_DAT7/i2sMULTI_DI [16]

KHS04

IEEE1394/SD-54030

CON9

[3] XspiCS1

[3] XspiMISO1/mmcCMD2

[3] XspiMOSI1

[3] XspiCLK1/mmcCLK2

1

2

3

4

D1+

D1D2+

D2-

GND

GND

IEEE1394/SD-54030

[3]

[3]

[3]

[3]

XspiCS0

XspiMISO0

XspiMOSI0

XspiCLK0

[3]

[3]

[3]

[3]

XspiCS1

XspiMISO1/mmcCMD2

XspiMOSI1

XspiCLK1/mmcCLK2

RA4

NC

RA5

R161

R162

NC/R1005

NC/R1005

RA3

B_SPI0_CSn [16]

B_SPI0_MISO [16]

B_SPI0_MOSI [16]

B_SPI0_CLK [16]

B_SPI1_CSn/i2sMULTI_DO2 [16]

B_SPI1_MISO/MMC2_CMD/i2sMULTI_DO0 [16]

B_SPI1_MOSI [16]

B_SPI1_CLK/MMC2_CLK/i2sMULTI_DO1 [16]

[3]

[3]

[3]

[3]

XmmcCLK1

XmmcCMD1

XmmcDATA1_0

XmmcDATA1_1

B_MMC_CLK

B_MMC_CMD

[3] XmmcDATA1_2

[3] XmmcDATA1_3

NC

B_MMC_DATA0

B_MMC_DATA1

B_MMC_DATA2

B_MMC_DATA3

RA8

R930

R931

0/R1005

0/R1005

B_XmmcCLK1 [16]

B_XmmcCMD1 [16]

B_XmmcDATA1_0 [16]

B_XmmcDATA1_1 [16]

B_XmmcDATA1_2 [16]

B_XmmcDATA1_3 [16]

SAMSUNG ELECTRONICS CO.,LTD

Title

SMDK6410 CPU Board (S3C6410 Evaluation Board)

Size

A3

Date:

5

Document Number

SD_MMC/SPI

Monday, July 14, 2008

Rev

1.0

Sheet

1

13

of

16

VDD_D

CON10

4

Xhi_D5/txWAKE/DATA_CF5 [4]

[4] Xhi_D3/rxDATA/DATA_CF3

Xhi_D7/txDATA/DATA_CF7 [4]

[4] Xhi_D2/rxFLAG/DATA_CF2

Xhi_D6/txFLAG/DATA_CF6 [4]

[4] Xhi_D0/rxREADY/DATA_CF0

[16]

[16]

[16]

[16]

RA6

Xhi_D1/DATA_CF1

Xhi_D3/DATA_CF3

Xhi_D2/DATA_CF2

Xhi_D0/DATA_CF0

10

11

12

13

14

15

16

Xhi_D4/txREADY/DATA_CF4

RA7

R164

NC/R1005 10K/R1005

[4]

Xhi_D5/DATA_CF5

Xhi_D7/DATA_CF7

Xhi_D6/DATA_CF6

Xhi_D4/DATA_CF4

AXK7L16227G

R163

R165

R166

10K/R1005

10K/R1005

[3] XTRSTn

[3] XTDI

[3] XTMS

[3] XTCK

[3] XRTCK

[3] XTDO

[2,3,6,16] XnRESET

[16]

[16]

[16]

[16]

R167

VDD_D

CON11

1

3

5

7

9

11

13

15

17

19

0/R1005

R169

470/R1005

R171

MIPI Connector

1

3

5

7

9

11

13

15

17

19

2

4

6

8

10

12

14

16

18

20

6

5

4

3

2

1

2

4

6

8

10

12

14

16

18

20

CFG3

KHS06

7

8

9

10

11

12

VDD_D

1

[4] Xhi_D1/rxWAKE/DATA_CF1

[3] XOM0

[3] XOM1

HIF3F-20PA-2.54DS (Box,Male,Right Angle)

10K/R1005

[3] XOM2

<Silk>

JTAG

[3] XOM3

[3] XOM4

[3] XSELNAND

VDD_SMEM

CON12

CTB31

CB83

[2,11] Xm0RDY0/ALE

[2,11] Xm0RDY1/CLE

[2,11] Xm0INTsm0/FWEn

[2,11,12] Xm0INTsm1/FREn

R178

0/R1005

R179

NC/R1005

R180

0/R1005

R181

0/R1005

R182

NC/R1005

R183

0/R1005

R184

0/R1005

R185

NC/R1005

R186

0/R1005

R176

100K/R1005

M0CSn3 [11,12]

R177

nCS_EXT_ONE

nCS_EXT_TWO

nCS_EXT_TWO

nCS_EXT_ONE