Académique Documents

Professionnel Documents

Culture Documents

Unidad2 Adquisicion

Transféré par

Ing Lourdes Gabriela Rodríguez RodríguezTitre original

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

Unidad2 Adquisicion

Transféré par

Ing Lourdes Gabriela Rodríguez RodríguezDroits d'auteur :

Formats disponibles

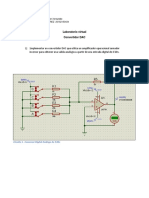

PRACTICA 1.

Muestreo Natural

y de Cresta Plana

1.1.1 Filtro anti-alias

Configuracin tipo Bessel pasa-bajas de 6 orden

Los amplificadores operacionales

Requieren alimentarse tanto con voltaje positivo como negativo

La seal de entrada

Debe ajustarse a un valor pequeo (cientos de milivolts) con el

fin de evitar saturacin de los amplificadores operacionales.

La saturacin se observa como una seal de salida del filtro

cortada o achatada en amplitud. Se debe a una ganancia alta

del filtro (A Ventrada), que no pueden soportar los op-amps pues

solo pueden proporcionar voltajes de salida ligeramente

inferiores a su voltaje de polarizacin positivo y/o negativo.

Imprima y revise las hojas de

especificaciones de los circuitos

utilizados, para garantizar su

correcto funcionamiento.

1.1.2 Prueba del filtro

Frecuencia

de entrada

Voltaje de

Entrada

Voltaje de

Salida

Ganancia

(Vsalida/Ventrada)

50 Hz

100Hz

200 Hz

300Hz

600 Hz

700 Hz

800 Hz

850 Hz

.

.

.

1000 Hz

5000 Hz

1.1.3 Determinacin de la frecuencia de corte prctica

Frecuencia de corte:

Es aquella frecuencia de entrada para la cual

la amplitud de salida decae a 0.7 veces de la

amplitud mxima (0.7Vp).

Cul es la frecuencia de corte real del filtro

anti-alias?______________

1.2 Muestreo Natural

CD4066

Es un switch electrnico, cuya frecuencia de cambio est dada por la

frecuencia del reloj (CI 555 en configuracin astable).

Si la seal de entrada es bipolar (p.e. una senoidal) es necesario alimentar al switch

con fuente positiva y negativa, en las terminales indicadas como VDD y VSS

respectivamente.

Imprima y revise las hojas

de especificaciones de los

circuitos utilizados, para

garantizar su correcto

funcionamiento.

1.2.1 Formas de onda resultantes

Dibuje las formas de onda resultantes del proceso de muestreo

natural o bien tome una foto de ellas.

1.3 Muestreo de Cresta Plana

1.3.1 Para este experimento se utilizar un circuito de

Muestreo/Retencin (el LF398)

Revise las hojas de

especificaciones de los

circuitos utilizados

1.3.2 Formas de Onda

Dibuje o tome una foto de la seal de la seal de entrada y salida

1.4 Conclusiones

Cite los principales problemas que enfrent durante la

prctica, as como su opinin de ella.

PAM DIGITAL (PCM)

En la MODULACION POR CODIFICACION DE

PULSOS (PCM), una seal analgica

muestreada se cuantifica en cierto nmero de

niveles discretos (niveles de cuantizacin) y se

usa un cdigo para designar cada nivel en cada

tiempo de muestra.

Ejemplo

Muestreo de la seal analgica

PAM usando 8 niveles de cuantizacin.

En cada tiempo de muestra debe decidirse cul de los 8 niveles es la

mejor aproximacin a la seal analgica. Elegido el valor ms

cercano, se mantiene hasta el siguiente tiempo de muestra, etc.

ERROR DE CUANTIZACION

El proceso de cuantizacin introduce algunas

fluctuaciones con respecto al valor real. Esto

resulta en un error cuando el cdigo se convierte

nuevamente a analgico. Este error se denomina

error de cuantizacin (Qe).

Qemax= VLSB

Donde: VLSB es el voltaje de resolucin o tamao del escaln, se

define como la diferencia entre dos niveles de cuantizacin

sucesivos.

Codificacin PCM (Seal Digital)

Para conocer el cdigo PCM de una muestra

especfica, se divide el voltaje de la muestra por

el voltaje de resolucin y se convierte a un cdigo

binario de n bits. Si el cociente anterior no genera

un cdigo PCM vlido (fraccionario), la muestra

se redondea o trunca al valor ms cercano.

RUIDO DE CANAL INACTIVO U OCIOSO

Durante los tiempos en que no haya una seal de entrada

analgica, la nica entrada al generador PCM ser el

ruido trmico aleatorio. Este ruido se llama Ruido de

Canal Inactivo y ocioso, el cual se codifica tal como si

fuera una seal.

RUIDO DE CANAL INACTIVO U OCIOSO

La figura muestra una manera de reducir el ruido de canal

inactivo, por un mtodo llamado CUANTIZACION DE

MEDIO ESCALON.

CUANTIFICADOR TIPO MID - THREAD

Posee un nmero de niveles n impar y

existe nivel cero de cuantizacin

CUANTIFICADOR TIPO MID - THREAD

Un cuantificador se disea para un rango de valores de entrada

esperados (-Amax, Amax). En general el tamao del escaln se

especifica como:

Donde:

n es el nmero de niveles de cuantizacin

es el tamao del escaln

max

2A

n

o =

o

CUANTIFICADOR TIPO MID - RISER

Posee un nmero

de niveles n par y

NO EXISTE

NIVEL CERO DE

CUANTIZACION

COMPANSION DIGITAL

Compansin se denomina al proceso de

comprimir una seal y despus expandirla.

La compansin digital en un sistema PCM,

involucra la compresin, por el lado de la

transmisin, despus de que la muestra ha

sido convertida en cdigo PCM lineal y la

expansin, en el lado de la recepcin, antes de

la decodificacin PCM.

Diagrama de bloques de un sistema PCM

compandido

Entrada

Analgica

Filtro

pasabajas

Circuito de

muestreo y

retencin

Convertidor

A/D

Compresor

Digital

Expansor

Convertidor

D/A

Circuito de

retencin

Filtro

pasabajas

Salida

Analgica

Seal PAM

Canal

COMPANSION DIGITAL

Los sistemas PCM comprimidos de manera

digital actuales, utilizan un cdigo lineal de

12 bits y un cdigo comprimido de 8 bits.

COMPANSION DIGITAL

COMPANSION DIGITAL

0

0

7

(

)

x 1

ID N Identificador de segmento

N Numerodeceros principales es el numero de ceros

que existen entre el bit de signo y el primer uno

Numero de bits perdidos ma imo ID

=

=

Intervalo de Cuantizacion ABCD

4 bits menos

significativos

TABLA DE COMPRESION Y EXPANSION

segmento

Cdigo lineal de 12

bits

Cdigo

comprimido

de 8 bits

0 S0000000ABCD S000ABCD

1 S0000001ABCD S001ABCD

2 S000001ABCDX S010ABCD

3 S00001ABCDXX S011ABCD

4 S0001ABCDXXX S100ABCD

5 S001ABCDXXXX S101ABCD

6 S01ABCDXXXXX S110ABCD

7 S1ABCDXXXXXX S111ABCD

Cdigo

comprimido

de 8 bits

Cdigo

recuperado de 12

bits

segmento

S000ABCD S0000000ABCD 0

S001ABCD S0000001ABCD 1

S010ABCD S000001ABCD1 2

S011ABCD S00001ABCD10 3

S100ABCD S0001ABCd100 4

S101ABCD S001ABCD1000 5

S110ABCD S01ABCD10000 6

S111ABCD S1ABCD100000 7

Ejemplo de cdigo PCM compandido

Para una resolucin de 0.01 Volts y un voltaje analgico de la

muestra Vmuestra= 0.05 V. Determine:

(a) El cdigo lineal de 12 bits

(b) El cdigo comprimido de 8 bits

(c) El cdigo recuperado de 12 bits

SOLUCION:

(a)

Ejemplo de cdigo PCM compandido

(a)

(b)

Ejemplo de cdigo PCM compandido

(c)

Ejercicio:

Si un sistema PCM cuenta con una resolucin de 10

mV , y voltajes de muestras analgicas de:

a)-0.321 Volts

b)-10.23 Volts

Determine el cdigo lineal de 12 bits, el cdigo

comprimido de 8 bits y el cdigo recuperado.

Sistemas Prcticos de Conversin

Analgico a Digital

Conversin Digital / Analgico (DAC)

Es el proceso de tomar un valor

representado en cdigo digital y convertirlo

en un voltaje o corriente que sea

proporcional al valor digital

DAC de 4 bits

D C B A Vout

(volts)

0 0 0 0 0

0 0 0 1 1

0 0 1 0 2

0 0 1 1 3

0 1 0 0 4

0 1 0 1 5

0 1 1 0 6

0 1 1 1 7

1 0 0 0 8

1 0 0 1 9

1 0 1 0 10

1 0 1 1 11

1 1 0 0 12

1 1 0 1 13

1 1 1 0 14

1 1 1 1 15

DAC de 4 bits

Obsrvese que

cada entrada digital

contribuye con una

cantidad diferente

de salida analgica.

Examnense los

casos marcados en

la tabla

D C B A Vout

(volts)

0 0 0 0 0

0 0 0 1 1

0 0 1 0 2

0 0 1 1 3

0 1 0 0 4

0 1 0 1 5

0 1 1 0 6

0 1 1 1 7

1 0 0 0 8

1 0 0 1 9

1 0 1 0 10

1 0 1 1 11

1 1 0 0 12

1 1 0 1 13

1 1 1 0 14

1 1 1 1 15

DAC de 4 bits

As a las contribuciones de

cada entrada digital se les

asignan valores segn su

posicin en el nmero binario.

Para hallar por ejemplo Vout

para la entrada digital 0111,

tenemos que:

0 + 4V + 2V + 1V =7 V

8 4 2 1

D C B A

RESOLUCION (tamao del escaln)

Se define como la menor variacin que puede ocurrir en la

salida analgica como resultado de un cambio en la entrada

digital.

La resolucin siempre es igual al valor en volts del LSB

Resulta til expresar a la resolucin como un porcentaje de

la salida de escala completa:

Re

% 100%

solucion en volts

R

Voltaje mximo

=

RESOLUCION (tamao del escaln)

1

% 100%

R

N Total de escalones

=

1

% 100%

2 1

N

R =

Para un cdigo de entrada binario de N bits, tenemos que:

DAC de 4 bits

D C B A Vout

(volts)

0 0 0 0 0

0 0 0 1 ?

0 0 1 0 ?

0 0 1 1 ?

0 1 0 0 ?

0 1 0 1 ?

0 1 1 0 ?

0 1 1 1 ?

1 0 0 0 ?

1 0 0 1 ?

1 0 1 0 ?

1 0 1 1 ?

1 1 0 0 ?

1 1 0 1 ?

1 1 1 0 ?

1 1 1 1 ?

DAC de 4 bits

D

8

C

4

B

2

A

1

Vout

(volts)

0 0 0 0 0

0 0 0 1 1.333

0 0 1 0 2.666

0 0 1 1 4

0 1 0 0 5.333

0 1 0 1 6.666

0 1 1 0 7.996

0 1 1 1 9.329

1 0 0 0 10.666

1 0 0 1 11.993

1 0 1 0 17.326

1 0 1 1 14.659

1 1 0 0 16

1 1 0 1 17.333

1 1 1 0 18.666

1 1 1 1 20

Ejercicio:

Un DAC de 10 bits tiene un tamao de escaln de

10mV. Determine el voltaje de salida de escala

completa y la resolucin porcentual

SOLUCION:

Con 10 bits habr el siguiente nmero de escalones

de 10 mV cada uno:

La salida de escala completa :

Y el porcentaje de resolucin:

1023 1 2

10

=

1 . 0 % 100

23 . 10

10

% ~ =

V

mV

R

V mV 23 . 10 1023 10 =

Ejercicio:

Si a la entrada del convertidor D/A anterior se conecta

un contador de 10 bits que cambia cada segundo.

Dibuje la forma de onda resultante

Circuitos prcticos DAC Circuitos prcticos DAC

|

|

.

|

\

|

+ + + =

A

F

B

F

C

F

D

F

OUT

V

R

R

V

R

R

V

R

R

V

R

R

V

4 3 2 1

Circuitos prcticos DAC Circuitos prcticos DAC

D C B A Vout

(volts)

0 0 0 0 0

0 0 0 1 -0.625

0 0 1 0 -1.2502

0 0 1 1 -1.875

0 1 0 0 -2.5

0 1 0 1 -3.1

0 1 1 0 -3.75

0 1 1 1 -4.375

1 0 0 0 -5

1 0 0 1 -5.625

1 0 1 0 -6.25

1 0 1 1 -6.875

1 1 0 0 -7.5

1 1 0 1 -8.125

1 1 1 0 -8.7502

1 1 1 1 -9.375

|

.

|

\

|

+ + + =

A B C D OUT

V V V V V

8

1

4

1

2

1

Circuitos prcticos DAC Circuitos prcticos DAC

La resolucin de este convertidor D/A es :

La precisin que logre este circuito al producir los valores de salida,

depender de 2 factores:

1) La precisin de las resistencias

2) La precisin de los niveles de voltaje de entrada

V 625 . 0 5

8

1

=

Circuitos prcticos DAC

Convertidor D/A con entradas ponderadas

Circuitos prcticos DAC

Convertidor D/A R-2R (escalera).

1.-MONOTICIDAD

2. PRECISION

3.-ERROR DE DESPLAZAMIENTO (off-set)

4.-TIEMPO DE ESTABLECIMIENTO

5.-RESOLUCION

Caracteristcas de un DAC

Caracteristcas de un DAC

1.- Monotonicidad.- Un DAC es monotnico, si su salida

aumenta a medida que la entrada binaria se incrementa de

un valor a otro.

2.- Resolucin (tamao del escalon)

Se define como la menor variacin que puede ocurrir en

la salida analgica como resultado de una cambio en la

entrada digital. Tambin se puede representar a la

resolucin como un porcentaje de la salida

de escala completa esto es:

Caracteristcas de un DAC

1

% 100%

2 1

N

R =

3.- Precisin, se expresa como un porcentaje de la salida

a escala completa. Los fabricantes de DACs tienen varias

maneras de especificar la precisin, siendo las dos ms

comunes las llamadas error de escala completa y error de

linealidad .

-Error de escala completa. Es la mxima desviacin de

salida del DAC de su valor estimado (terico).

-Error de linealidad. Es la desviacion mxima en el

tamao de escaln del terico.

Caracteristcas de un DAC

4.- Error de desplazamiento. (off-set).-En el caso

ideal, la salida de un DAC ser de cero volts, cuando

el cdigo a su entrada sea cero. Pero en la practica

habr un voltaje de cada muy pequeo para esta

situacin y se llama error de desplazamiento. Si este

error de desplazamiento no se corrige se sumar a la

salida del DAC.

Caracteristcas de un DAC

5.- Tiempo de establecimiento.-Es el tiempo requerido para

que la salida del DAC cambie de 0 a su valor de escala

completa, cuando todos los bits de la entrada binaria cambien

de 0 a 1.

En la practica el tiempo de establecimiento es de +/- del

tamao de paso de su valor final (tiempo aprox 50ns 10us).

Caracteristcas de un DAC

Ejemplo :

-Un convertidor D/A de cinco bits tiene una corriente

cmo salida. Para una entrada digital de 10100, se produce

una corriente de salida de 10 mA Cul ser el valor de

Isal para una entrada digital de 11101?

Ejemplo :

- Cul es el porcentaje de resolucin

experimentado por un DAC de 8 bits que genera

1.0 V para una entrada digital de 00110010?

DAC BIPOLAR.

Hasta este momento se ha supuesto que la entrada binaria

al DAC es un nmero binario sin signo y que la salida del

DAC es un voltaje o corriente positiva. Algunos DAC's

estn diseados para producir valores positivos como

negativos, tales como

-10V a +10V.

En general lo anterior se hace utilizando la entrada binaria

como un nmero con signo, donde el MSB es el bit de

signo (0 para + y 1 para -).

CONVERTIDOR D/A

Con frecuencia, los valores de entrada negativos estn

representados en forma de complemento a dos, aunque

algunos DAC'S utilizan la forma de magnitud verdadera.

Por ejemplo, suponga que tenemos un DAC bipolar de 6

bits que utiliza el sistema de complemento a dos y que

ofrece una resolucin de 0.2Volts. Los valores binarios en

la entrada varan de 100000 (-32) a 011111 (+31) para

producir salidas analgicas que van desde hasta.

Entre estos limites negativos y positivos existen 63

pasos o escalones de 0.2V.

-6.4V

6.2V

DAC BIPOLAR

Un convertidor A/D toma un voltaje de entrada

analgico y despus de cierto tiempo produce un

cdigo de salida digital que representa la entrada

analgica. El proceso de conversin A/D es

generalmente ms complejo y largo que el proceso

D/A, y se han creado y utilizado muchos mtodos.

Algunos ADC comunes utilizan un DAC como parte

de sus circuitos.

Conversin Analgico/Digital

(ADC)

Conversin Analgico/Digital

(ADC)

ADC DE RAMPA DIGITAL

Conversin Analgico/Digital

(ADC)

ADC DE RAMPA DIGITAL

Voltaje de referencia

Conversin Analgico/Digital

(ADC)

ADC DE RAMPA DIGITAL

Suponga los siguientes valores para el ADC de rampa

digital: frecuencia de reloj (CLK)= 1MHz; VT=0.1mV.

El DAC interno tiene una salida a plena escala= 2.55V

y una entrada de 8 bits. Determine los siguientes

valores:

(a)El equivalente digital obtenido por VA= 1.728 Volts

(b)El tiempo de conversin

(c)La resolucin de este convertidor

Conversin Analgico/Digital

(ADC)

SOLUCION:

El DAC tiene entrada de 8 bits y una salida mxima de 2.55 Volts.

As el nmero total de posibles escalones es:

Por lo tanto el tamao del escaln :

Esto significa que VAX se incrementa en escalones de 10mV cuando

el contador cuenta hacia arriba desde cero

255 1 2

8

=

mV 10

255

55 . 2

=

Conversin Analgico/Digital

(ADC)

SOLUCION:

Como VA= 1.728 y VT=0.1mV

Vreferencia debe alcanzar 1.7281V o ms antes que el

comparador cambie a BAJO. Esto requerira que:

escalones escalones

mV

173 81 . 172

10

7281 . 1

~ =

Conversin Analgico/Digital

(ADC)

(b) Se requieren 173 escalones para completar la

conversin. As ocurrieron 173 pulsos de reloj a la

frecuencia de uno por microsegundo. Esto da un tiempo

total de conversin de 173 microsegundos.

(c) La resolucin de este convertidor es igual al tamao del

escaln del DAC, que es de 10 mV. En porcentaje es:

% 39 . 0 % 100

255

1

=

Conversin Analgico/Digital

(ADC)

ADC DE PENDIENTE SIMPLE O UNICA

+

_

CONTADOR

Clear

In

CERROJOS

Enabled

...

...

Reloj

Pulso

de inicio

SALIDA

DIGITAL

Vcc

S1

S2

Vin

Io

Inv_1

Inv_2

Conversin Analgico/Digital

(ADC)

ADC DE APROXIMACIONES SUCESIVAS

LATCH

LOGICA DE

CONTROL

REGISTRO

D A C

Reloj

Pulso

de inicio

. . .

. . .

V

ref

V

entrada

INICIO

BORRAR

TODOS

LOS BITS

COLOCAR

BIT 1=1

INCIAR

CON MSB

IR AL BIT

SIGUIENTE

SE HAN

REVISADO

TODOS

LOS BITS ?

V

ref

> V

in

BORRAR BIT

( BIT =0 )

FIN

CONVERSION

COMPLETA?

SI

NO

SI

NO

Conversin Analgico/Digital

(ADC)

ADC

PARALELO

O FLASH

Circuito practico: ADC0804

De Aproximaciones Sucesivas

Circuito practico: ADC0804

De Aproximaciones Sucesivas

Circuito practico: ADC0804

De Aproximaciones Sucesivas

CI de 20 terminales CMOS

Salida de 8 bits de tres estados,

Vresol=5V/255=19.6mV

Tiene un reloj interno con una

frecuencia f = 1/ (1.1RC).

Tipicamente R=10k y C=150pF

para una frecuencia de 606kHz

Con f= 606kHz, tiempo de

conversin de 100 microsegundos

Tiene 2 entradas analgicas:

VENT(+) y VENT(-). As :

VENT analogico= VENT(+) - VENT(-)

Circuito practico: ADC0804

De Aproximaciones Sucesivas

Tierra analgica y digital

Habilitacin del circuito

(READ) Las salidas tienen

niveles lgicos que representan el

resultado de la ltima conversin

(ESCRIBIR). Un pulso bajo

seala el inicio de una nueva

conversin

(INTERRUMPIR). Esta

salida retornar a BAJO al final de

una conversin.

Esta es una entrada

opcional. Si se conecta un voltaje

externo a esta terminal, la

referencia interna cambia y su

valor es el doble del voltaje

externo.

CS

RD

WR

INTR

2 /

REF

V

Circuito practico: ADC0804

De Aproximaciones Sucesivas

UNIDAD 3

Procesamiento

Digital de seales

3.1.1 Seales y Sistemas en

tiempo discreto

SEALES. Matemticamente son funciones de una o ms variables

independientes. Ejemplo: la seal de voz (es una funcin del

tiempo), una imagen fotogrfica(es una funcin del brillo respecto a

dos variables espaciales), una imagen de video(es una funcin del

brillo respecto a dos variables espaciales y al tiempo).

LA VARIABLE INDEPENDIENTE DE LA REPRESENTACION

MATEMATICA DE UNA SEAL PUEDE SER CONTINUA O DISCRETA

3.1.1 Seales y Sistemas en tiempo discreto

SEALES EN TIEMPO

CONTINUO

Se definen en un continuo

temporal y se representan por

tanto con una variable

independiente continua .

3.1.1 Seales y Sistemas en tiempo discreto

SEALES EN TIEMPO DISCRETO.

Se definen en instantes discretos

del tiempo y, por tanto, la variable

independiente toma valores

discretos, es decir, los instantes

discretos del tiempo se

representan como secuencias de

nmeros.

3.1.1 Seales y Sistemas en tiempo discreto

SEALES ANALOGICAS

Son aquellas que son

analgicas tanto en el

tiempo como en la

amplitud.

SEALES DIGITALES

Son aquellas que son

discretas tanto en el

tiempo como en la

amplitud.

ADEMAS DEL CARCTER CONTINUO O DISCRETO DE LA VARIABLE

INDEPENDIENTE, LA AMPLITUD DE LA SEAL PUEDE SER TAMBIEN

CONTINUA O DISCRETA.

3.1.1 Seales y Sistemas en tiempo discreto

SISTEMAS EN TIEMPO

CONTINUO Son aquellos

para los que tanto la

entrada como la salida

son seales en tiempo

continuo

SISTEMAS EN TIEMPO

DISCRETO.

Son aquellos para los

cuales tanto la entrada

como la salida son

seales en tiempo

discreto

Los sistemas de tratamiento de seales se pueden clasificar de una forma

similar a las seales.

3.1.1 Seales y Sistemas en tiempo discreto

SISTEMAS DIGITAL

Es aquel para el que

tanto la entrada como la

salida son seales

digitales.

El tratamiento o procesamiento digital de seales trata, entonces de la

transformacin de seales que son discretas tanto en tiempo como

amplitud

Una secuencia de nmeros X, en los que el n-simo nmero se

indica como x(n), se escribe formalmente como: X = {x(n)}

Las seales en tiempo discreto pueden aparecer al muestrear una

seal en tiempo continuo Xa(t).

Xa(nT)=x(n)

Siendo T el periodo de muestreo y su inversa es la frecuencia de

muestreo.

As que las seales en tiempo discreto se representan

matemticamente como secuencias de nmeros,

Tal que el n-simo nmero de la secuencia es igual al valor de la

seal analgica Xa(t), en el instante temporal nT,

3.1.1 Seales y Sistemas en tiempo discreto

3.1.1 Seales y Sistemas en tiempo discreto

Las seales en tiempo

discreto, (es decir las

SECUENCIAS),

Se representan en forma

grfica como se indica

Es importante notar de

que x(n) est definida

slo para valores

enteros de n.

Para valores no enteros

simplemente x(n) no est

definida, no es cero.

3.1.1 Seales y Sistemas en tiempo discreto

Secuencias bsicas

Impulso unitario

discreto

3.1.1 Seales y Sistemas en tiempo discreto

Secuencias bsicas

Escaln unitario

discreto

3.1.1 Seales y Sistemas en tiempo discreto

Secuencias bsicas

Exponencial

discreta

3.1.1 Seales y Sistemas en tiempo discreto

Secuencias bsicas

Funcin Rampa

discreta

3.1.1 Seales y Sistemas en tiempo discreto

Secuencias bsicas

Funcin Sinusoide

discreta

3.1.1 Seales y Sistemas en tiempo discreto

Diversas representaciones de una seal discreta

3.1.1 Seales y Sistemas en tiempo discreto

Diversas representaciones de una seal discreta

3.1.1 Seales y Sistemas en tiempo discreto

Operaciones bsicas entre secuencias

(seales discretas)

El producto y la suma de dos

secuencias x(n) y y(n),

Se definen como el producto

y la suma muestra a muestra

Ejemplo:

X(n)={0,1,1,-2,-2,3,0}

Y(n)={0,1, 2, 3, 4, 5, 7}

X(n)+y(n)={0,2,3,1,2,8,7}

X(n).Y(n)={0,1,2,-6,-8,15,0}

3.1.1 Seales y Sistemas en tiempo discreto

Operaciones bsicas entre secuencias

(seales discretas)

Se dice que una secuencia

y(n) es una versin retrasada

o desplazada de x(n) si:

y(n) = x(n - no)

Siendo no un numero entero

Ejemplo:

Si:

X(n)={0,1,1,-2,-2,3,0}

Entonces

Y(n)=x(n+2) es:

Y(n)={0,1,1,-2,-2,3,0}

&

Y(n)=x(n-2) es:

Y(n)={0,0,0,1,1,-2,-2,3,0}

3.1.1 Seales y Sistemas en tiempo discreto

Operaciones bsicas entre secuencias

(seales discretas)

Se dice que una secuencia

y(n) es una versin reflejada

de x(n) si:

y(n) = x(- n)

Siendo no un numero entero

Ejemplo:

Si:

X(n)={0,1,1,-2,-2,3,0}

Entonces:

Y(n)=x(-n) es:

Y(n)={0,3,-2,-2,1,1,0}

3.1.1 Seales y Sistemas en tiempo discreto

Operaciones bsicas entre secuencias

(seales discretas)

Se dice que una secuencia

y(n) es una versin

INTERPOLADA DE x(n) POR

UN FACTOR a , si:

y(n) = x(n/a)

Siendo a un numero entero

(sobremuestreo)

Llamamos INTERPOLACION,

a la operacin de aumentar la

frecuencia de muestreo de la

seal analogica que antecede

a la secuencia en cuestin.

Si : x(n)= X(nT)

Entonces:

x(n/a)= X(nT/a)

3.1.1 Seales y Sistemas en tiempo discreto

Operaciones bsicas entre secuencias

(seales discretas)

Se dice que una secuencia

y(n) es una versin

DIEZMADA DE x(n) POR UN

FACTOR a , si:

y(n) = x(an)

Siendo a un numero entero

(submuestreo)

Llamamos DIEZMACION, a la

operacin de reducir la

frecuencia de muestreo de la

seal analogica que antecede

a la secuencia en cuestin.

Si : x(n)= X(nT)

Entonces:

x(na)= X(n aT)

3.1.1 Seales y Sistemas en tiempo discreto

Ejemplo: Sea

OBSERVESE QUE LA OPERACIN DE DIEZMADO ES

CONTRARIA A LA OPERACIN DE INTERPOLADO, PERO

NO AL REVES.

} 0 , 4 , 0 , 0 , 0 , 7 , 0 , 1 , 0 , 1 {

2

} 4 , 0 , 7 , 1 , 1 { ) ( ) 2 (

} 4 , 3 , 0 , 6 , 7 , 3 , 1 , 2 , 1 { ) (

=

|

.

|

\

|

= =

=

n

y

n y n x

n x

Sea

} 4 , 3 , 0 , 6 , 7 , 3 , 1 , 2 , 1 { ) ( = n x

} 0 , 4 , 0 , 3 , 0 , 0 , 0 , 6 , 0 , 7 , 0 , 3 , 0 , 1 , 0 , 2 , 0 , 1 { ) (

2

= =

|

.

|

\

|

n y

n

x

} 4 , 3 , 0 , 6 , 7 , 3 , 1 , 2 , 1 {

2

2 ) 2 ( =

|

.

|

\

|

=

n

x n y

} 4 , 3 , 0 , 6 , 7 , 3 , 1 , 2 , 1 { ) ( = n x

3.1.1 Seales y Sistemas en tiempo discreto

} 4 , 3 , 0 , 6 , 7 , 3 , 1 , 2 , 1 { ) ( = n x

} 4 , 0 , 7 , 1 , 1 { ) ( ) 2 ( = = n y n x

} 0 , 4 , 0 , 0 , 0 , 7 , 0 , 1 , 0 , 1 {

2

=

|

.

|

\

|

n

y

3.1.1 Seales y Sistemas en tiempo discreto

OPERACIONES QUE COMBINAN DIEZMADO, INTERPOLADO

Y DEPLAZAMIENTO:

3.1.1 Seales y Sistemas en tiempo discreto

EJERCICIOS PROPUESTOS:

Vous aimerez peut-être aussi

- Introducción a la conversión digital-analógicaDocument69 pagesIntroducción a la conversión digital-analógicaKarla Patricia100% (1)

- Convewrtidor ADC 2Document14 pagesConvewrtidor ADC 2Edson RodasPas encore d'évaluation

- Convertidores AD-DADocument8 pagesConvertidores AD-DAJosé Miguel DíazPas encore d'évaluation

- Convertidor Analógico-Digital: ConvertDocument7 pagesConvertidor Analógico-Digital: ConvertnicolasPas encore d'évaluation

- Interfaz Con El Mundo AnalogicoDocument70 pagesInterfaz Con El Mundo Analogicojorge741Pas encore d'évaluation

- Lab08 - Adc y DacDocument11 pagesLab08 - Adc y DacYeffersom EscobedoPas encore d'évaluation

- S13 - DacDocument34 pagesS13 - DacP T RPas encore d'évaluation

- Laboratorio de circuitos ADC y DAC de 3 bitsDocument12 pagesLaboratorio de circuitos ADC y DAC de 3 bitsosmarPas encore d'évaluation

- Catagña Alcoser Yupanqui Conversor Analogico Digital p3Document9 pagesCatagña Alcoser Yupanqui Conversor Analogico Digital p3luisPas encore d'évaluation

- ADC en Un AVR - Present PDFDocument18 pagesADC en Un AVR - Present PDFrickypinaPas encore d'évaluation

- Practica Convertidor Analogico-DigitalDocument17 pagesPractica Convertidor Analogico-DigitalLuis Eduardo Martinez RamosPas encore d'évaluation

- Circuito ProyectoDocument8 pagesCircuito ProyectoVictor Fabricio Nasimba NPas encore d'évaluation

- Convertidor DACDocument7 pagesConvertidor DACSerch TorresPas encore d'évaluation

- Coleccion Ejercicios PDFDocument118 pagesColeccion Ejercicios PDFEmilio CortiPas encore d'évaluation

- Practica 8 Lab. Elect. IIDocument8 pagesPractica 8 Lab. Elect. IILuis Ernesto PalmarPas encore d'évaluation

- Conversor DACDocument7 pagesConversor DACDuo Doble APas encore d'évaluation

- Cuarto Examen Circuitos 2021Document3 pagesCuarto Examen Circuitos 202122460270Pas encore d'évaluation

- Problemas Capitulo 15Document7 pagesProblemas Capitulo 15Pablo Santillan100% (6)

- examen_encastatsDocument18 pagesexamen_encastatseles2501.eesPas encore d'évaluation

- Unidad 3Document23 pagesUnidad 3Carlos OrtegaPas encore d'évaluation

- Conversor Analogico DigitalDocument47 pagesConversor Analogico DigitalJhordanStepPascualPas encore d'évaluation

- Convertidores AD y DADocument51 pagesConvertidores AD y DAClei Shin100% (1)

- Relevadores MicroprocesadosDocument23 pagesRelevadores MicroprocesadosCarlos Justino Díaz100% (1)

- Tarea Digitales Lunes 22Document6 pagesTarea Digitales Lunes 22lokilloPas encore d'évaluation

- DAC y ADC. Eo. IIIDocument20 pagesDAC y ADC. Eo. IIICarlossideregtsPas encore d'évaluation

- Instrumentación ADC para Condicionemiento de SeñalDocument22 pagesInstrumentación ADC para Condicionemiento de SeñalCristian TascónPas encore d'évaluation

- Ex3pInstII ADocument2 pagesEx3pInstII ARobTamPas encore d'évaluation

- PRACTICA9Document20 pagesPRACTICA9Mauricio OrtegaPas encore d'évaluation

- Interfaz Con El Mundo AnalógicoDocument5 pagesInterfaz Con El Mundo AnalógicoSyd BarrettPas encore d'évaluation

- Convertidor Digital AnalógicoDocument9 pagesConvertidor Digital AnalógicoWaked Mohamed100% (1)

- Adc Pic 18F4550Document6 pagesAdc Pic 18F4550Aalfredo Lezama RamirezPas encore d'évaluation

- Ad 0804-7106Document5 pagesAd 0804-7106Josue ChavarriaPas encore d'évaluation

- Reporte Del Convertidor Analogico A DigitalDocument10 pagesReporte Del Convertidor Analogico A DigitalRICHARD LAZARO0% (1)

- Funcionamiento Del Convertidor Analógico Digital ADC0809Document5 pagesFuncionamiento Del Convertidor Analógico Digital ADC0809Jorge CaballeroPas encore d'évaluation

- TECNICAS OPTIMIZACION CONVERSION ANALOGICO-DIGITALDocument4 pagesTECNICAS OPTIMIZACION CONVERSION ANALOGICO-DIGITALBismarck CarrionPas encore d'évaluation

- 2013 Clase Fpga AdcDocument22 pages2013 Clase Fpga AdcnospherathusPas encore d'évaluation

- Convertidores Digital-Analogicos PDFDocument41 pagesConvertidores Digital-Analogicos PDFMileniPanduroLopePas encore d'évaluation

- Circuito Analogico DigitalDocument11 pagesCircuito Analogico Digitalerik0688Pas encore d'évaluation

- 7DACDocument20 pages7DACCRISTIAN CEFERINO LIVIMORO LOAZAPas encore d'évaluation

- S15 - DacDocument20 pagesS15 - DacDerlyPas encore d'évaluation

- CAPITULO 01 CONVERSOR Digital A AnalogoDocument58 pagesCAPITULO 01 CONVERSOR Digital A AnalogoFernando RodriguezPas encore d'évaluation

- Conversores Ad de 10 y 12 BitsDocument8 pagesConversores Ad de 10 y 12 Bitskapri1001Pas encore d'évaluation

- Labo 6Document6 pagesLabo 6ROLY MAYO GODOYPas encore d'évaluation

- Práctica ADC - DACDocument5 pagesPráctica ADC - DACgaragetuning2808Pas encore d'évaluation

- UPS-ConvDigitalAnalogicaDocument4 pagesUPS-ConvDigitalAnalogicaVanessa VelásquezPas encore d'évaluation

- Convert I Do Resa DCDocument20 pagesConvert I Do Resa DCLev LandauPas encore d'évaluation

- Adc Pic 18F4550Document6 pagesAdc Pic 18F4550Aalfredo Lezama RamirezPas encore d'évaluation

- Conversor Analógico DigitalDocument7 pagesConversor Analógico DigitalRODRIGO ALONZO VELASQUEZ FLORESPas encore d'évaluation

- Convertidores PDFDocument39 pagesConvertidores PDFLuis Antonio Mendoza MexicanoPas encore d'évaluation

- Interfaces y microcontroladores: Teorema de muestreo, DAC y ADCDocument29 pagesInterfaces y microcontroladores: Teorema de muestreo, DAC y ADCAngel Muñoz0% (1)

- DAC y ADCDocument55 pagesDAC y ADCleonelPas encore d'évaluation

- DAC: Convertidor digital analógicoDocument10 pagesDAC: Convertidor digital analógicoLuis VrgsPas encore d'évaluation

- Trabajo de Convertidores 1Document17 pagesTrabajo de Convertidores 1Andy Moncada MenaPas encore d'évaluation

- Introducción Al Psoc5Lp: Teoría y aplicaciones prácticaD'EverandIntroducción Al Psoc5Lp: Teoría y aplicaciones prácticaPas encore d'évaluation

- Ejercicios prácticos con Electrónica: Proyectos de electrónica con Arduino y Raspberry PiD'EverandEjercicios prácticos con Electrónica: Proyectos de electrónica con Arduino y Raspberry PiÉvaluation : 5 sur 5 étoiles5/5 (1)

- Armónicas en Sistemas Eléctricos IndustrialesD'EverandArmónicas en Sistemas Eléctricos IndustrialesÉvaluation : 4.5 sur 5 étoiles4.5/5 (12)

- 100 circuitos de shields para arduino (español)D'Everand100 circuitos de shields para arduino (español)Évaluation : 3.5 sur 5 étoiles3.5/5 (3)

- Simulación de circuitos electrónicos con OrCAD® PSpice®D'EverandSimulación de circuitos electrónicos con OrCAD® PSpice®Pas encore d'évaluation

- Aprender Arduino, prototipado y programación avanzada con 100 ejerciciosD'EverandAprender Arduino, prototipado y programación avanzada con 100 ejerciciosÉvaluation : 5 sur 5 étoiles5/5 (5)

- DSC Fme U2 Act04Document1 pageDSC Fme U2 Act04Jorge TorresPas encore d'évaluation

- Wort SchatzDocument1 pageWort SchatzIng Lourdes Gabriela Rodríguez RodríguezPas encore d'évaluation

- Fme U1 A4 LorrDocument2 pagesFme U1 A4 LorrIng Lourdes Gabriela Rodríguez RodríguezPas encore d'évaluation

- Actividad 2. Registro Contable de Operaciones, Estado de Situación FinancieraDocument6 pagesActividad 2. Registro Contable de Operaciones, Estado de Situación Financierajorge271989Pas encore d'évaluation

- Ide U1 Eu LorrDocument4 pagesIde U1 Eu LorrIng Lourdes Gabriela Rodríguez RodríguezPas encore d'évaluation

- Conceptos de Comportamiento OrganizacionalDocument15 pagesConceptos de Comportamiento OrganizacionalIng Lourdes Gabriela Rodríguez RodríguezPas encore d'évaluation

- Eti U2 A4 LorrDocument4 pagesEti U2 A4 LorrIng Lourdes Gabriela Rodríguez RodríguezPas encore d'évaluation

- Ic U2 Eu LorrDocument50 pagesIc U2 Eu LorrIng Lourdes Gabriela Rodríguez RodríguezPas encore d'évaluation

- Co U1 A3 LorrDocument3 pagesCo U1 A3 LorrIng Lourdes Gabriela Rodríguez RodríguezPas encore d'évaluation

- Diseño filtro anti-alias muestreo señalesDocument4 pagesDiseño filtro anti-alias muestreo señalesIng Lourdes Gabriela Rodríguez RodríguezPas encore d'évaluation

- Mapa 2 CompiladoresgabyDocument1 pageMapa 2 CompiladoresgabyIng Lourdes Gabriela Rodríguez RodríguezPas encore d'évaluation

- Unad MatematicasDocument1 pageUnad MatematicasIng Lourdes Gabriela Rodríguez Rodríguez100% (3)

- 6.5.1.2 Lab - Building A Switch and Router NetworkDocument6 pages6.5.1.2 Lab - Building A Switch and Router NetworkHarrison QUINTERO CAICEDOPas encore d'évaluation

- PDF Demodulador FSK Con PLL DDDocument3 pagesPDF Demodulador FSK Con PLL DDAndres TolozaPas encore d'évaluation

- Como Trabajan Los SnifferDocument2 pagesComo Trabajan Los SnifferdavidPas encore d'évaluation

- Mtcna 21 06 2022Document103 pagesMtcna 21 06 2022Maritza PolancoPas encore d'évaluation

- Radio DigitalDocument7 pagesRadio DigitalCandy Andrea Condori SanchezPas encore d'évaluation

- Características de Un Sistema CAN Bus en El AutomóvilDocument20 pagesCaracterísticas de Un Sistema CAN Bus en El AutomóvilElectricitat-Electrònica IES Milà i FontanalsPas encore d'évaluation

- Análisis Del Protocolo Ipv6Document229 pagesAnálisis Del Protocolo Ipv6willfrank89Pas encore d'évaluation

- Que Es La FOP - Ponencia-Edificios-Inteligentes-CasacomDocument14 pagesQue Es La FOP - Ponencia-Edificios-Inteligentes-CasacomImpulsa colladoPas encore d'évaluation

- Informe de SDHDocument17 pagesInforme de SDHRonald ErazoPas encore d'évaluation

- Ampliación WiFi con mallaDocument10 pagesAmpliación WiFi con mallaDanny kostiaPas encore d'évaluation

- Herramientas y Elementos Necesarios en RedDocument26 pagesHerramientas y Elementos Necesarios en Redgenkidamada genkidamadaPas encore d'évaluation

- GarcíaDocument106 pagesGarcíajorge.dettPas encore d'évaluation

- Carrasco Cayambe Daniela RocioDocument14 pagesCarrasco Cayambe Daniela RocioDanny CarrascoPas encore d'évaluation

- Lab 01 Todo Sobre Internet - FinDocument11 pagesLab 01 Todo Sobre Internet - FinGeancarlo Dubual Zegarra QuispePas encore d'évaluation

- (Versión para El Instructor) : Packet Tracer: Configuración Del Protocolo Ospfv3 Básico en Un Área ÚnicaDocument4 pages(Versión para El Instructor) : Packet Tracer: Configuración Del Protocolo Ospfv3 Básico en Un Área ÚnicaJoha Mejia GutierrezPas encore d'évaluation

- A14 Reporte EYNRDocument7 pagesA14 Reporte EYNRErika Navarro RomeroPas encore d'évaluation

- Metodos de Acceso A La RedDocument26 pagesMetodos de Acceso A La Redjorgeecc64100% (1)

- Protocolos IndustrialesDocument7 pagesProtocolos IndustrialesLizbeth RamirezPas encore d'évaluation

- Radio multi-modo SE-530K POC/UHF 4W versátil comunicaciónDocument2 pagesRadio multi-modo SE-530K POC/UHF 4W versátil comunicaciónArnaldo J Brito ÑPas encore d'évaluation

- Manual de Conexión Local PTNDocument29 pagesManual de Conexión Local PTNdlgt63100% (1)

- Protocolo Atencion de Consultas Usuario Externo Historias ClinicasDocument2 pagesProtocolo Atencion de Consultas Usuario Externo Historias ClinicasDavid GuzmanPas encore d'évaluation

- Syllabus MICROONDAS 2019-2Document5 pagesSyllabus MICROONDAS 2019-2AbelPas encore d'évaluation

- Uso Del Hub y El SwitchDocument4 pagesUso Del Hub y El SwitchJuan Camilo RINCON ALONSOPas encore d'évaluation

- Dump CL - REST - HTTP - CLIENT, UNCAUGHT - EXCEPTION, CX - REST - CLIENT - EXCEPTION, No Se Puede Encontrar La Entrada en El Almacenamiento Seguro, Cliente HTTP - Error de ComunicaciónDocument3 pagesDump CL - REST - HTTP - CLIENT, UNCAUGHT - EXCEPTION, CX - REST - CLIENT - EXCEPTION, No Se Puede Encontrar La Entrada en El Almacenamiento Seguro, Cliente HTTP - Error de Comunicaciónny2kPas encore d'évaluation

- Red Wifi y Wifi DirectDocument7 pagesRed Wifi y Wifi DirectAlejandroRosPas encore d'évaluation

- Presentación Final 3 2Document27 pagesPresentación Final 3 2Oscar Javier DominguezPas encore d'évaluation

- Dossier N - EmailDocument21 pagesDossier N - EmailManolo RuizPas encore d'évaluation

- Problemas Subnetting 1Document5 pagesProblemas Subnetting 1cgadeafPas encore d'évaluation

- MovistarDocument3 pagesMovistarMaria Isabel Gimenez ZuninoPas encore d'évaluation

- Ejercicio Ruteo CCNA2Document1 pageEjercicio Ruteo CCNA2Alejandro Ramírez CruzPas encore d'évaluation