Académique Documents

Professionnel Documents

Culture Documents

Digital Voltmeter

Transféré par

Raghul RamasamyDescription originale:

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

Digital Voltmeter

Transféré par

Raghul RamasamyDroits d'auteur :

Formats disponibles

DESIGN A SINGLE CHANNEL DIGITAL VOLTMETER USING FPGA (J0605162)

KHIN AYE MU

DESIGN A SINGLE CHANNEL DIGITAL VOLTMETER USING FPGA

TITLE OF RESEARCH DESIGN A SINGLE CHANNEL DIGITAL VOLTMETER USING FPGA) NAME KHIN AYE MU (J0605162) YEAR 2009

Project No: JAN 09/BEHE/11

KHIN AYE MU (J0605162)

Project No: JAN 09/BEHE/11

SCHOOL OF SCIENCE AND TECHNOLOGY SIM UNIVERSITY

2009

DESIGN A SINGLE CHANNEL DIGITAL VOLTMETER USING FPGA (J0605162)

KHIN AYE MU

DESIGN A SINGLE CHANNEL DIGITAL VOLTMETER USING FPGA

KHIN AYE MU

(J0605162)

Project No: JAN 09/BEHE/11

School of Science and Technology

ENG 499 CAPSTONE PROJECT COURSE

A THESIS SUBMITTED TO SIM UNIVERSITY IN PARTIAL FULFILLMENT OF THE REQUIREMENT FOR THE BACHELOR DEGREE OF ELECTRONICS ENGINEERING

2009

DESIGN A SINGLE CHANNEL DIGITAL VOLTMETER USING FPGA (J0605162)

KHIN AYE MU

ABSTRACT

This purpose of this project is to develop and implement a general purpose VLSI (Very Large Scale Integration) Test Module based on a FPGA (Field Programmable Gate Array) system to model a digital voltmeter which is enable to measure both DC and AC voltage signal. This is achieved by using the Xilinx Spartan 3A FPGA toolkit which has a fully embedded system (ADC, LCD module, etc). All the work is done by VHDL programming. Architect, programming logic, simulation and hardware of this system is included in the following chapters.

DESIGN A SINGLE CHANNEL DIGITAL VOLTMETER USING FPGA (J0605162)

KHIN AYE MU

ACKNOWLEDGMENTS

Firstly, I would like to express my sincere and heartfelt appreciation to my project supervisor, Mr Mak Lin Seng for his exceptional guidance, invaluable advice and wholehearted support in matters of practical and theoretical nature throughout the project. His expert experience in design and programming parts of FPGA and VHDL Design, valuable comments and suggestions have been very helpful in solving problems of the project.

I am gratefully appreciative of UniSIM capstone project instructors for providing me the opportunity to study in the exciting and challenging areas of Design a Single Channel Digital Voltmeter using FPGA.

I am indebted to my employer, Advanced Micro Devices (AMD) for allowing me to further study towards Bachelor Degree. I am also grateful to my superiors Mr Benjamin Ng, Mr Medrick for allowing me to take time off from work during the course of my project work as well as my normal academic years.

Finally, my special thanks to my parents, husband and upcoming baby for their love, inspiration and constant moral support throughout my academic years.

DESIGN A SINGLE CHANNEL DIGITAL VOLTMETER USING FPGA (J0605162)

KHIN AYE MU

LISTS OF FIGURES Figure 1.1: Xilinx Spartan 3A Starter Kit ........................................................................... 2 Figure 1.2: Digital voltmeter (Left) and Analog voltmeter (Right) .................................... 3 Figure 2.1: The architect of digital voltmeter ..................................................................... 4 Figure 3.1: Structure of an FPGA ..................................................................................... 10 Figure 3.2: The Spartan-3A Development System Board Photo ...................................... 12 Figure 3.4: The timing diagram of Spartan 3A ADC gain setting .................................... 15 Figure 3.5: Analog-to-Digital Conversion Interface ......................................................... 15 Figure 3.6: The connection between LCD and FPGA ...................................................... 17 Figure 3.7: The character location in DD RAM ............................................................... 18 Figure 3.8: The waveform for LCD 4-bit data interfaces operation ................................ 19 Figure 4.1: Major Activities in FPGA Design .................................................................. 20 Figure 4.2: ModelSim Interface ........................................................................................ 22 Figure 4.3: Precision RTL Interface ................................................................................. 23 Figure 4.4: FPGA Design Flow Overview in ISE ............................................................ 25 Figure 4.5: ISE Implementation Interface ........................................................................ 26 Figure 5.1: Flow chart of Amplifiers Gain Setting .......................................................... 28 Figure 5.2: Waveform of Amplifiers Gain Setting .......................................................... 29 Figure 5.3: Flow chart of Analog to Digital Signal Capture ............................................ 30 Figure 5.4: Detailed SPI Timing to ADC ......................................................................... 31 Figure 5.5: Flow chart of BCD Conversion ...................................................................... 32 Figure 5.6: Different Magnitude of Sinusoidal Wave ...................................................... 34

DESIGN A SINGLE CHANNEL DIGITAL VOLTMETER USING FPGA (J0605162)

KHIN AYE MU

Figure 5.7: Spartan-3A Hardware Setting for Sine Wave ................................................ 36 Figure 5.8: Software Implementation of RMS Function .................................................. 37 Figure 6.1: The simulated waveform of amplifier gain setting ........................................ 38 Figure 6.2: The simulated waveform of ADC data capture .............................................. 39 Figure 6.3: Waveform of getting ADC data ..................................................................... 40 Figure 6.4: Waveform of computing VIN ........................................................................ 40 Figure 6.5: Waveform of getting BCD data format .......................................................... 41 Figure 6.6: Overall waveform ........................................................................................... 41 Figure 7.1: DC Voltage Measurement Setup .................................................................... 42 Figure 7.2: Sine Wave Signal Measurement Setup .......................................................... 43

DESIGN A SINGLE CHANNEL DIGITAL VOLTMETER USING FPGA (J0605162)

KHIN AYE MU

LIST OF TABLES

Table 2.1: Technical Specification of Single Channel Digital Voltmeter .......................... 7 Table 3.1: Programmable Gain Settings for Pre-Amplifier .............................................. 16 Table 3.2: Table for LCD displaying ................................................................................ 18 Table 5.1: Binary to BCD Conversion .............................................................................. 33 Table 7.1: DC Voltage Measurement ............................................................................... 42 Table 7.2: RMS Sine Wave Voltage Measurement .......................................................... 43

DESIGN A SINGLE CHANNEL DIGITAL VOLTMETER USING FPGA (J0605162)

KHIN AYE MU

TABLE OF CONTENTS

Page

ABSTRACT ............................................................................................... i ACKNOWLEDGEMENT....................................................................... ii LISTS OF FIGURES .............................................................................. iii LIST OF TABLES .................................................................................. iv Chapter 1 Introduction ................................................................................1 Chapter 2 Voltmeter Architect....................................................................4 2.1 Functional Block of designed digital voltmeter ................................4 2.2 Designed digital voltmeters operation ..............................................6 2.3 Technical Specification of the Single Channel Digital Voltmeter .....7 Chapter 3 Spartan-3A Development System ..............................................9 3.1 VLSI and FPGA Technology Introduction ........................................9 3.2 The Spartan-3A Development System............................................. 11 3.2.1 Analog Capture Circuit .................................................................13 3.2.2 Character LCD Screen ..................................................................16 Chapter 4 FPGA Implementation .............................................................19 4.1 Simulation Tool: ModelSim.............................................................21 4.2 Synthesis Tool: Precision RTL ........................................................22 4.3 Implementation: ISE ........................................................................24 4.4 Role of HDL ....................................................................................26 Chapter 5 Programming Logic .................................................................27

DESIGN A SINGLE CHANNEL DIGITAL VOLTMETER USING FPGA (J0605162)

KHIN AYE MU

5.1 Amplifiers Gain Setting ..................................................................27 5.2 Analog-to-Digital signal capture......................................................29 5.3 Binary to BCD decoding .................................................................31 5.4 RMS Voltage Calculation for Sinusoidal Wave ...............................33 5.4.1 Magnitude of a Sine Wave ............................................................33 5.4.2 Implementation of RMS Function in Spartan-3A Board..............35 Chapter 6 Simulation ................................................................................38 Chapter 7 Hardware Realization ...............................................................42 7.1 DC Voltage Measurement Verification ............................................42 7.2 RMS Sine Wave Measurement Verification ....................................43 Chapter 8 Conclusion and Recommendation ...........................................44 8.1 Conclusion .......................................................................................44 8.2 Recommendations for future study..................................................44 Critical Review and Reflections ...............................................................45 Bibliography45 APPENDICES APPENDIX: VHDL CODE FOR VOLTMETER ...................................48 GLOSSARY.65

DESIGN A SINGLE CHANNEL DIGITAL VOLTMETER USING FPGA (J0605162)

KHIN AYE MU

Chapter 1 Introduction

This project is to develop and model a digital voltmeter which is enable to measure both DC and AC voltage signal using FPGA technology. In the next few paragraph, there is some basic background information on FPGA and voltmeter.

Field-programmable gate array (FPGA) is an integrated chip designed to be configured by the customer or designer after manufacturing. It can be configured to perform complex combinational functions, or merely simple logic gates like AND and XOR. The ability to update the functionality and re-programming, offer advantages for many applications. Its flexibility and low cost make it stands out from programmable read only memory (PROM) and programmable logic devices (PLDs). Xilinx invented the first commercially viable field programmable gate array in 1985. In the later 15 years, FPGAs found their way into consumer, automotive, and industrial applications. Now, applications of FPGAs include digital signal processing, software-defined radio, aerospace and defense systems, ASIC prototyping, medical imaging, computer vision, speech recognition, cryptography, bioinformatics, computer hardware emulation, radio astronomy and a growing range of other areas.

To define the behavior of the FPGA, the user provides hardware description languages (HDL), which are VHDL and Verilog. A technology-mapped netlist is generated to link up the soft code and hardware. Once the design and validation

1

DESIGN A SINGLE CHANNEL DIGITAL VOLTMETER USING FPGA (J0605162)

KHIN AYE MU

process is complete, the binary file generated (is used to configure the FPGA).

Xilinx Spartan 3a Starter Kit is used for this digital voltmeter design as shown in Figure1.1. The Spartan-3A FPGA platform is a full feature platform of five devices with system gates ranging from 50K to 1.4M gates, and I/Os ranging from 108 to 502 I/Os, with density migration. The Spartan-3A FPGAs also support up to 576 Kbits of fast-block RAM with byte-write enable, and up to 176 Kbits of distributed RAM. The peripheral devices are LEDs, LCD, Clock, RAM, ROM, Ethernet, ADC, DAC, switches, buttons and etc.

Figure 1.1: Xilinx Spartan 3A Starter Kit

DESIGN A SINGLE CHANNEL DIGITAL VOLTMETER USING FPGA (J0605162)

KHIN AYE MU

Voltmeter is an instrument used for measuring the electrical potential difference between two points in an electric circuit. It is categorized into two types, analog and digital voltmeter as shown in Figure 1.2. Analog voltmeters move a pointer across a scale in proportion to the voltage of the circuit; digital voltmeters give a numerical display of voltage by use of an analog to digital converter. The voltage range and accuracy are two important parameters to define a voltages usage. For high voltage usage, the voltmeter is designed to sustain high voltage measurement. A powerful voltmeter can measure voltage for a few mV to hundred volts. A well designed voltmeter can give the accurate measurement that is important in testing purpose.

Figure 1.2: Digital voltmeter (Left) and Analog voltmeter (Right)

DESIGN A SINGLE CHANNEL DIGITAL VOLTMETER USING FPGA (J0605162)

KHIN AYE MU

Chapter 2 Voltmeter Architect 2.1 Functional Block of designed digital voltmeter

AC DC

AMP

1 bit

CLK

Serial port

ADC

1 bit

CLK

Binary to BCD Decoder

LCD

CLK

8 bits

Parallel Port

FPGA

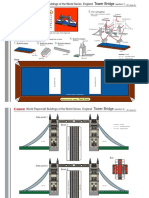

Figure 2.1: The architect of digital voltmeter

In this digital voltmeter design, there are three main components, FPGA, ADC (Analog Digital Converter) capture circuit and LCD display as shown in Figure 2.1. The input signals are fed to the ADC capture circuits Amplifier module; whereas the output data is transmit to LCD for displaying. The FPGA is designed with 6 functional block, serial port, binary to BCD

4

DESIGN A SINGLE CHANNEL DIGITAL VOLTMETER USING FPGA (J0605162)

KHIN AYE MU

(binary-coded decimal) decoder, clocks. ADC capture circuit consists of two component, AMP (Amplifier) and ADC (Analog-Digital Converter) modules. ADC and LCD are the peripheral devices of Spartan 3a board and its hardware design is fixed. Therefore, the main task of this project is to program FPGA which can perform proper communicate between these two devices and execute digital signal processing.

The serial port interface communicates to the ADC and the parallel port communicates to the LCD. Serial port transmits and receives data bit by bit; whereas the parallel port can transmit all data at the same time. For this digital voltmeter design, it transmits 8 bits data to LCD display in parallels.

The timing of processing data between FPGA and LCD or ADC is controlled by clocks. Different peripherals have the different limitation on speed of processing. Therefore, it needs three different timing clocks for this systems data processing.

The Binary to BCD Decoder is to decode the binary data into BCD data format for displaying data on LCD. The binary-coded decimal (BCD) is an encoding for decimal numbers in which each digit is represented by its own binary sequence. Its main virtue is that it allows easy conversion to decimal digits for printing or display, and allows faster decimal calculations. In BCD, a digit is usually represented by four bits which, in general, represent the values/digits/characters 09. Other bit combinations are sometimes used for a sign or other indications.

5

DESIGN A SINGLE CHANNEL DIGITAL VOLTMETER USING FPGA (J0605162)

KHIN AYE MU

The analog-to-digital converter (ADC) is a device which converts continuous signals to discrete digital numbers. Typically, ADC is an electronic device that converts an input analog voltage to a digital number proportional to the magnitude of the voltage. The ADC device in Spartan 3a board is Linear Technology LTC1407A-1 ADC.

The amplifier increases the amplitude of a signal. The relationship of the input to the output of an amplifierusually expressed as a function of the input frequencyis called the transfer function of the amplifier, and the magnitude of the transfer function is termed the gain. The ADC device in Spartan 3a board is Linear Technology LTC6912-1.

The liquid crystal display (LCD) used for electronically displaying information such as text. The Spartan-3A/3AN Starter Kit board prominently features a 2-line by 16-character LCD.

2.2 Designed digital voltmeters operation

The digital voltmeter is designed to measure DC voltage and ACs RMS (Root mean Square) voltage ranges from 0.4V to 2.9V. As the system is power up, FPGA initializes ADC gain setting and LCD setting. The FPGA generate clock signal to ADC and serially output the gain value to amplifier. Once the input signal is fed to amplifier input, the ADC converts input signal to 14 bits digital signal based on gain setting. The 14 bits signal is serially transferred to FPGA later.

6

DESIGN A SINGLE CHANNEL DIGITAL VOLTMETER USING FPGA (J0605162)

KHIN AYE MU

As the LCD only recognize BCD data format, it needs to perform 14 bits binary to BCD conversion. And it is done in BCD decoder. Once the data is decoded, it sends 8 bits data to LCD in parallel. LCD shows the voltage value of input signal.

The system will keep on reading the input signal and update the voltage level. For the DC input signal, the ADC just read the value and as for the AC signal, the ADC gets the peak voltage of signal and performs conversion.

2.3 Technical Specification of the Single Channel Digital Voltmeter

Before any product can be developed, there is a requirement to draft out the technical specification of digital voltmeter. This technical specification (Table 2.1) is drafted based on the commercial widely available digital volt meter and will be used as a general guideline for the current project. No. 1 2 3 4 5 6 7 8 9 10 11 12 Specification Channel Measurement Phase Precision Measurement Type Function Maximum/Minimum Range Maximum Digital Representation Sampling Rate Operating Temperature Display Additional Feature My Single Channel Voltmeter Single AC & DC Single Phase 3 Digit Voltage only VRMS, VPP +0.4V & 2.9V 14 bit (two complement) 1.5MHz -10 to 85 Spartan-3A Onboard LCD Auto Ranging

7

Table 2.1: Technical Specification of Single Channel Digital Voltmeter

DESIGN A SINGLE CHANNEL DIGITAL VOLTMETER USING FPGA (J0605162)

KHIN AYE MU

Based on the specification above, there is requirement to evaluate the Spartan-3A board specification & capability in order to achieve the above technical requirement for a digital voltmeter. Additional feature is added to the current digital volt meter to make this product more marketable and competitive.

DESIGN A SINGLE CHANNEL DIGITAL VOLTMETER USING FPGA (J0605162)

KHIN AYE MU

Chapter 3 Spartan-3A Development System

3.1 VLSI and FPGA Technology Introduction

With the increasing complexity of todays Integrated Circuits systems and rapidly advancing technology a single chip with smaller and smaller size can integrate more and more functionality [18]. VLSI technology makes it possible to combine thousands of transistor-based circuits into a single chip. This has opened up opportunities to do things that were not possible before. VLSI circuits are everywhere, in computers, cars, cameras, cell phones etc. ASIC (Application-Specific Integrated Circuits), CPLD (Complex Programmable Logic Devices) and FPGA are all VLSI systems. FPGA is developed from CPLD. Both FPGA and CPLD include a relatively large number of programmable logic elements. CPLD logic gate densities range from the equivalent of several thousand to tens of thousands of logic gates, while FPGA typically range from tens of thousands to several million [1]. Architecture is the primary difference between CPLD and FPGA. CPLD is less flexible, with the advantage of more predictable timing delays and a higher logic-to-interconnect ratio [3]. FPGA architectures are dominated by their interconnect. This makes them far more flexible but also far more complex to design for. Another notable difference between CPLD and FPGA is the presence in most FPGAs of higher-level embedded functions (such as adders and multipliers) and embedded

9

DESIGN A SINGLE CHANNEL DIGITAL VOLTMETER USING FPGA (J0605162)

KHIN AYE MU

memories. A related, important difference is that many modern FPGA support full or partial in-system reconfiguration. Some FPGAs have the capability of partial re-configuration that lets one portion of the device be re-programmed while other portions continue delivering services. [4]. As FPGA draw more power, usually FPGA is slower than their ASIC counterparts. But FPGA has the ability to re-program in the field to fix bugs. The designs are developed on regular FPGA and then migrated into a fixed version that more resembles an ASIC.

Figure 3.1: Structure of an FPGA

FPGA is one kind of important VLSI system, which generally contains many (64 to over 10,000) identical programmable logic blocks that can be viewed as standard components. The logic blocks can be programmed to duplicate the functionality of basic logic gates such as AND, OR, XOR, NOT or more complex combinational

10

DESIGN A SINGLE CHANNEL DIGITAL VOLTMETER USING FPGA (J0605162)

KHIN AYE MU

functions such as decoders or simple mathematical functions. In most FPGAs, these programmable logic blocks also include memory elements, which may be simple flip-flops or more complete blocks of memories. The individual blocks are interconnected by a matrix of wires and programmable switches. The switches and wires allow the logic blocks of an FPGA to be interconnected as needed by the system designer. These logic blocks and interconnects can be programmed after the manufacturing process by the customer/designer to implement any logical function. An illustration of a typical FPGA architecture is shown in Figure 3.1 [5]. FPGA has the advantages of a short time to market, ability to re-program in the field to fix bugs, and lower non-recurring engineering costs

3.2 The Spartan-3A Development System

The Spartan-3A, a kind of FPGA board, is implemented to design the VLSI Test Module, which provides an advanced hardware platform that can be used to create a complex system, (see Figure 3.2). The Spartan-3A family is specifically designed to meet the needs of high volume, cost-sensitive consumer electronic applications.

11

DESIGN A SINGLE CHANNEL DIGITAL VOLTMETER USING FPGA (J0605162)

KHIN AYE MU

Figure 3.2: The Spartan-3A Development System Board Photo The Spatan-3A contains these important features:

Very

low

cost,

high-performance

logic

solution

for

high-volume,

consumer-oriented applications.

Proven advanced 90-nanometer process technology. Eight discrete LEDs Four slide switches Four push-button switches Xilinx XC3S500E Spartan-3E FPGA: up to 232 user-I/O pins, 320-pin FPGA package, and over 10,000 logic cells.

Multi-voltage, multi-standard SelectIO interface pins. Up to eight DCMs. Complete Xilinx ISE and Webpack development system support. A 2-line by 16-character LCD [6].

12

DESIGN A SINGLE CHANNEL DIGITAL VOLTMETER USING FPGA (J0605162)

KHIN AYE MU

VGA display port. PS/2 mouse or keyboard port. On-board USB-based FPGA/CPLD download/debug interface. 50 MHz clock oscillator. Hirose FX2 expansion connector. Three Digilent 6-pin expansion connectors. Four-output, SPI-based DAC.

Including the above functions, Spartan-3E has these specific features:

Parallel NOR flash configuration MultiBoot FPGA configuration from parallel NOR flash PROM SPI serial flash configuration MicroBlaze 32-bit embedded RISC processor KCPSM3 8-bit embedded controller DDR memory interfaces [7]

3.2.1 Analog Capture Circuit

The Spartan-3A/3AN FPGA Starter Kit board includes a two-channel analog capture circuit, consisting of a programmable scaling pre-amplifier, Linear Tech LTC6912-1 Dual Amp, and an analog-to-digital converter (ADC), Linear Tech LTC1407A-1 Dual A/D. The functional block diagram is shown in the following Figure 3.3.

13

DESIGN A SINGLE CHANNEL DIGITAL VOLTMETER USING FPGA (J0605162)

KHIN AYE MU

Figure 3.3: The functional block diagram of Spartan 3A ADC

This circuit involves two operations: (1) Amplifiers gain setting Set 0 to AMP_CS, then FPGA starts to send out the 8bits data (gain setting value) bit by bit through SPI_MOSI. As the amplifier is only supporting about 10 MHz clock frequencies, it is unable to connect it to the hardware 50MHz clock. The SPI_SCK signal can be generated through the software programming. AMP_SHDN is to reset the gain setting by assigning 1.AMP_OUT echoes amplifier gain setting as shown in Figure 3.4.

14

DESIGN A SINGLE CHANNEL DIGITAL VOLTMETER USING FPGA (J0605162)

KHIN AYE MU

Figure 3.4: The timing diagram of Spartan 3A ADC gain setting

(2) Analog-to-Digital signal capture Set the AD_CONV to 1 to start analog-to-digital conversion process (Figure 3.5). Then, the ADC_OUT will output the 28 bits data serially but it is one sample and two SPI_SCK clock cycles later. Therefore, it needs a total of 34 bits to get all the digital data. This module only can support max 1.5MHz; the SPI_SCK can be generated by software programming.

Figure 3.5: Analog-to-Digital Conversion Interface To be noted, it is a two-channel ADC AMP module. The input can be connected to Connector J22, pin VINA &VINB. The behavior of ADC is designed as a state machine. The flow of this design is included in the following part.

15

DESIGN A SINGLE CHANNEL DIGITAL VOLTMETER USING FPGA (J0605162)

KHIN AYE MU

The 14bits digital data can be calculated as the formula below:

The gain setting for this design is -1. Hence, the input voltage range is from 0.4V to 2.9V.

Table 3.1: Programmable Gain Settings for Pre-Amplifier

3.2.2 Character LCD Screen

The Spartan-3A/3AN Starter Kit board prominently features a 2-line by 16-character liquid crystal display (LCD). The FPGA controls the LCD via the eight-bit data interface or the four-bit data interface, as sown in figure 3.6. There are 8-bits data lines, one bit LCD_E, and one bit LCD_RS and one bit LCD_RW connections from FPGA to LCD. The 8-bit data line are bi-directional connection, hence it can read data from LCD and write data to LCD. LCD_E is the enable signal; it is assigned logic 1 to enable writing and reading of LCD. LCD_RS is an instruction register when it is assigned logic 0 or data for reading/writing operation when it is assigned logic1.

16

DESIGN A SINGLE CHANNEL DIGITAL VOLTMETER USING FPGA (J0605162)

KHIN AYE MU

LCD_RW is writing operation when it is assigned logic 0 or reading operation when it is assigned logic 1.

Figure 3.6: The connection between LCD and FPGA

In this digital voltmeter design, the four-bit data interface is used to control LCD and initialization sequence must be established to before display data on LCD. The initialization sequence of LCD is as below: 1. Wait 15 ms or longer, although the display is generally ready when the FPGA finishes configuration. The 15 ms interval is 750,000 clock cycles at 50 MHz. 2. Write LCD_DB<7:4> = 0x3, and pulse LCD_E High for 12 clock cycles. 3. Wait 4.1 ms or longer, which is 205,000 clock cycles at 50 MHz. 4. Write LCD_DB<7:4> = 0x3, and pulse LCD_E High for 12 clock cycles. 6. Write LCD_DB<7:4> = 0x3, and pulse LCD_E High for 12 clock cycles. 8. Write LCD_DB<7:4> = 0x2, and pulse LCD_E High for 12 clock cycles.

.

After initialization, it can start to write or read to LCD. When writing or reading to LCD, it is needs to set the location of data display on LCD by writing data to the DD

17

DESIGN A SINGLE CHANNEL DIGITAL VOLTMETER USING FPGA (J0605162)

KHIN AYE MU

RAM. Refer to the Figure 3.7 below, which shows the address of each display character location. Physically, there are 80 total character locations in DD RAM with 40 characters available per line. Locations 0x10 through 0x27 and 0x50 through 0x67 can be used to store other non-display data. Later, it can start to send data to LCD for displaying or read data from LCD. The data which send to LCD can refer to table. The third row is to set DD RAM address; the last two rows are writing or reading data to or from DD RAM.

Figure 3.7: The character location in DD RAM

Table 3.2: Table for LCD displaying

Each commands execution time for LCD is much lower to the FPGAs clock operation. Therefore, it is need to control each commands timing accurately. The Figure 3.8 below show the timing waveform of 4-bit data interface for LCD.

18

DESIGN A SINGLE CHANNEL DIGITAL VOLTMETER USING FPGA (J0605162)

KHIN AYE MU

Figure 3.8: The waveform for LCD 4-bit data interfaces operation

Chapter 4 FPGA Implementation

The development flow of FPGAs is outlined in Figure 4.1. The first step in the design process is to expand the idea in terms of the behavior of the target circuit. Design

19

DESIGN A SINGLE CHANNEL DIGITAL VOLTMETER USING FPGA (J0605162)

KHIN AYE MU

description is an activity independent of the target technology or manufacturer. It results in a description of the digital circuit. Through stages of programming, a design description is developed in terms of well defined standard constructs and conventions [8].

Figure 4.1: Major Activities in FPGA Design Through simulations process the design is verified, checked, and ensured to meet the requirements of the design description. After one simulation run, the errors are corrected and another simulation run carried out. From this cyclic, iterative process, error-free design is evolved. To translate the design description into a real circuit, physical design is a necessary process. It is to be realized as the final circuit using a million components in the foundrys library. Typically physical design includes these steps: system partitioning, floor planning, placement, and routing.

20

DESIGN A SINGLE CHANNEL DIGITAL VOLTMETER USING FPGA (J0605162)

KHIN AYE MU

4.1 Simulation Tool: ModelSim

As mentioned before, the design descriptions are tested for their functionality. One has to check whether all the functions are carried out as expected and rectify errors in them. All such activities are fulfilled by the simulation tool. The important features of FPGA simulation are ease of use, robustness of the debug environment, and enough capacity to handle most ambitious VHDL or Verilog models. Since FPGA is also a melting pot of designers coming from different disciplines, support for easy integration of models written in other languages is also valuable [9]. FPGA simulation tools, such as ModelSim from Mentor Graphics, and FPGA fitter tools, for example Alliance from Xilinx. ModelSim was selected to simulate my FPGA design. This tool also has an editor to make corrections to the source code. ModelSim provides a comprehensive simulation and debug environment for complex ASIC and FPGA designs, Figure 4.2 is an example of ModelSim interface. Support is provided for multiple languages including Verilog, SystemVerilog, and VHDL. And the enhanced GUI (Graphical User Interface) makes it easy to view and access powerful capabilities. ModelSim provides instance-based coverage results for all supported metric types, including statement, branch, condition, and expression coverage. [10].

21

DESIGN A SINGLE CHANNEL DIGITAL VOLTMETER USING FPGA (J0605162)

KHIN AYE MU

Figure 4.2: ModelSim Interface

4.2 Synthesis Tool: Precision RTL

After simulation, the logical design is complete. The corresponding circuit hardware realization is finished by a synthesis tool. FPGA synthesis tools include Synplify from Synplicity, Leonardo Spectrum from Mentor Graphics and so on. Precision RTL, from Mentor Graphics, is also introduced. Precision RTL Synthesis is the industrys foremost FPGA design solution, offering ease of use; high-productivity flows and outstanding quality of results with a complete vendor-independent design methodology (see Figure 4.3). Precision RTL can support as many as 19 FPGA device families significantly broader than that supported by competing tools.

22

DESIGN A SINGLE CHANNEL DIGITAL VOLTMETER USING FPGA (J0605162)

KHIN AYE MU

Figure 4.3: Precision RTL Interface Precision RTL improves designer efficiency through an intuitive user interface, and provides excellent quality of results using advanced optimization techniques. Incremental-debug and analysis environment identifies and fixed problems early in the design process [11]. Precision RTL supports any combination of VHDL, Verilog, SystemVerilog and EDIF usage. All the design description is fully simulated, but not fully synthesizable. There are several constructs that do not have valid representations in a digital circuit. Other constructs do, in theory, have a representation in a digital circuit, but cannot be reproduced with guaranteed accuracy. Delay time modeling is an example of this. After the synthesis process, designers can arrive at a circuit implementation that

23

DESIGN A SINGLE CHANNEL DIGITAL VOLTMETER USING FPGA (J0605162)

KHIN AYE MU

satisfies the timing and area constraints set for a given target circuit. All the VHDL code in the Appendix is simulated in ModelSim and synthesized in Precision RTL.

4.3 Implementation: ISE

With all programming, simulation and synthesis completed, the last step is to implement the design in the FPGA system (physical design). The implementation tool used has to support the Spartan-3E development system. The Xilinx ISE system is an integrated design environment that consists of a set of programs to create, simulate and implement digital designs in a FPGA or CPLD target device [12]. ISE provides a graphical user interface (GUI) to users, which allows all operations in ISE to be executed from toolbars, menus or icons. The following steps are involved in moving designs from design entry to Xilinx device programming. The ISE managers and processes the design through the following steps in the ISE design flow (see Figure 4.4). [13] Design Entry: Based on design ideas and design objectives, source files can be created by using a Hardware Description Language (HDL), such as VHDL, Verilog, or ABEL, or using a schematic Notice: Xilinx ISE does not support SystemC. VHDL is used in this part. Synthesis: After design entry and simulation, VHDL, Verilog, or mixed language designs are integrated to netlist files that are accepted as input to the implementation step, ISE synthesis interface is display.

24

DESIGN A SINGLE CHANNEL DIGITAL VOLTMETER USING FPGA (J0605162)

KHIN AYE MU

Figure 4.4: FPGA Design Flow Overview in ISE Implementation: the logical design is converted into a physical file format that can be downloaded to the selected target device. Different implementation processes are adopted depending on FPGA module or CPLD module. Verification: the functionality of the design can be verified at several points in the design flow. Simulator software can be used to verify the functionality and timing of the design or a portion of the design. The simulator interprets VHDL or Verilog code into circuit functionality and displays logical results of the described HDL to determine correct circuit operation. In-circuit verification also can be run after programming device. It is possible to design and verify complicated functions in a relatively small amount of time by simulation. Device Configuration: after generating a programming file, need configure the device.

25

DESIGN A SINGLE CHANNEL DIGITAL VOLTMETER USING FPGA (J0605162)

KHIN AYE MU

During configuration, configuration files are generated and the programming files are downloaded from a host computer to a Xilinx device. The interface of all these steps in ISE is displayed in Figure 4.5.

Figure 4.5: ISE Implementation Interface

4.4 Role of HDL

It is impossible to split the FPGA implementation from HDL. Verilog or VHDL provides the framework for the complete logical design of the FPGA. Verilog and VHDL are the two most commonly used hardware description languages today. Both have constructs with which the design can be fully described at all the levels [14]. There are additional constructs available to spell out test vectors, set up the test bench and read the outputs from the designed unit. All the programs in the dissertation are written in VHDL

26

DESIGN A SINGLE CHANNEL DIGITAL VOLTMETER USING FPGA (J0605162)

KHIN AYE MU

Chapter 5 Programming Logic

Xilinx ISE is the software used for Verilog programming in this project design. It is the ideal downloadable solution for FPGA and CPLD design offering HDL synthesis and simulation, implementation, device fitting, and JTAG programming. In the following explains the programming logic of this digital voltmeter design. It has five parts: amplifiers gain setting, ADC data capture, calculation of input voltage Binary to BCD decoder and the RMS voltage reading.

5.1 Amplifiers Gain Setting

This is need to serially transmit 8 bits data to the amplifier and a clock signal lower than 10MHz is also be fed to the amplifier. The Figure 5.1 shows us the flow chart to set the amplifier gain. When it is started, initialize two counters to zero. BIT_COUNT is the counter to control number of bit to send and the COUNTER is the control the clock signal to amplifier. When processing at HI state, system will stay there for three clocks before proceed to LO state and SCK is assigned to logic1. Similarly, system will stay at LO state for three clocks and SCK is assigned to logic0. In result, the clock signal SCK of 50MHz/6 is generated. The resultant clock signal waveform is shown in the Figure. For each SCK pulse, one bit of gain data is transmitted. The transmitted gain data is started from bit 7 to bit 0, total is 8 bits. Therefore, the system loops for state HI to state LO_DUMMY for eight times, that is when BIT_COUNTER is eight, the whole process for amplifier gain setting is completed.

27

DESIGN A SINGLE CHANNEL DIGITAL VOLTMETER USING FPGA (J0605162)

KHIN AYE MU

IDLE

BIT_COUNT = 0 COUNTER = 0

START

START2

COUNTER

HI

COUNTER ++

COUNTER = 2

COUNTER = 0

HIDUMMY BIT_COUNT

COUNTER

LO

COUNTER ++

COUNTER = 2 LODUMMY BIT_COUNT =8

COUNTER = 0

FINE

Figure 5.1: Flow chart of Amplifiers Gain Setting

28

DESIGN A SINGLE CHANNEL DIGITAL VOLTMETER USING FPGA (J0605162)

KHIN AYE MU

50MHz Clock SCK

MOSI

Bit 7

Bit 6

Bit 5

Figure 5.2: Waveform of Amplifiers Gain Setting This waveform (Figure 5.2) above shows the setting of amplifiers gain by serially output the 8 bits data to amplifier module (LTC6912-1), that is MOSI output waveform. Meanwhile, it generates a clock SCK with period of 6 clock- cycles for this amplifier module.

5.2 Analog-to-Digital signal capture

As two channel of ADC is activated, total is 34 bit of data must be captured. But actual digital data for each ADC channel only 14 bits. As the ADC module can work at a frequency no more than 1.5MHZ. The 50MHZ clock is divided into 15MHz SCK signal. The flow chart of the ADC data capture is shown at Figure 5.3. At HI_AD state, the SCK is assigned to logic 1. At LO_AD state, the SCK is assigned to logic 0. The SCK waveform can be generated, as shown in the Figure 5.4. It uses a COUNTER to control number of data to be received. When COUNTER is 34, all the digital data is

29

DESIGN A SINGLE CHANNEL DIGITAL VOLTMETER USING FPGA (J0605162)

KHIN AYE MU

Figure 5.3: Flow chart of Analog to Digital Signal Capture

captured and stored in the system memory. Later, the system continues read the data from ADC input and capture the next ADC data.

50MHz Clock SCK ADC output 30

-----

-----

Bit13

Bit12

Bit11

Bit10

Bit9

Bit8

37

DESIGN A SINGLE CHANNEL DIGITAL VOLTMETER USING FPGA (J0605162)

KHIN AYE MU

Figure 5.4: Detailed SPI Timing to ADC This waveform above shows the capture of serial data, 34 bits from A/D module( LTC6912-1). Meanwhile, it generates a clock with period of 2 clock-cycles for this A/D module.

5.3 Binary to BCD decoding

The ADC digital data is captured and stored in the memory. Before start to perform Binary to BCD decoding, it is need to perform calculation to find the Vin. The formula is as below:

The calculated values are 2s complement data. If the signed bit is 1, it means negative decimal values and it needs to do conversion to find it actual decimal values. The operation can be done as follow:

ADC3 <= ADC1 XOR "11111111111111"; ADC4 <= ADC3 +1; ADC4(13)<='0';

Finally, actual binary data is resulted and the LCD only recognizes BCD format. The system continues to perform binary to BCD conversion.

DECODE1

31

DESIGN A SINGLE CHANNEL DIGITAL VOLTMETER USING FPGA (J0605162)

KHIN AYE MU

Figure 5.5: Flow chart of BCD Conversion For Binary to BCD conversion, it is easily to explain by using the table below. Binary data 1111 1111 is used as example, shifting the MSB binary bit first. Shifting bit by bit until the Units columns values more than 4 (operation Shift 3), then it needs to add 3 to that column (Operation Add3). Later, it continues the shifting. When values add up more than 4, add 3 to the values. When all the data is shifted, the operation is ended. Finally, the BCD value can be obtained (last row).

32

DESIGN A SINGLE CHANNEL DIGITAL VOLTMETER USING FPGA (J0605162)

KHIN AYE MU

Table 5.1: Binary to BCD Conversion For the programming logic, four 4-bits register is allocated for shifting and it is done at state BCD_INIT. In next state, system performs the adjustment to check the registers data whether need to add 3. Then, system performs the shifting. System does adjustment for every shifting of bit. The COUNTER is used to control number of bit need to shift. At last, the BCD data is ready for LCD display.

5.4 RMS Voltage Calculation for Sinusoidal Wave 5.4.1 Magnitude of a Sine Wave

There are 3 ways to quantify the magnitude of a sine wave (Figure 5.6)

33

DESIGN A SINGLE CHANNEL DIGITAL VOLTMETER USING FPGA (J0605162)

KHIN AYE MU

Figure 5.6: Different Magnitude of Sinusoidal Wave

Peak Voltage: Peak voltage tells you how far the voltage swings, either positive or negative, from the point of reference. Peak voltage is only a moderately useful way of measuring voltage when trying to express the amount of work that will be done when driving a specified load.

Peak-Peak Voltage: It is rarely used. It is probably more useful in the case of a non-symmetrical wave form. Otherwise you would probably express its value as peak voltage.

RMS Voltage: RMS voltage is absolutely the most common way to measure/quantify AC voltage. It is also the most useful. Because AC voltage is constantly changing and is at or near

34

DESIGN A SINGLE CHANNEL DIGITAL VOLTMETER USING FPGA (J0605162)

KHIN AYE MU

the highest and lowest points in the cycle for only a tiny fraction of the cycle, the peak voltage is not a good way to determine how much work can be done by an AC power source (e.g. your amplifier, a wall outlet in your house...). DC voltage is constant. Its voltage level can be plugged directly into the formulas for power (on the Ohm's law page) and you will get an accurate image of its ability to do work. RMS voltage will give you the same ability to predict how much work will be done by an AC voltage. The RMS voltage of a pure sine wave is approximately 0.707*peak voltage and is expressed as below equation.

If you read voltage with a voltmeter you are generally given the RMS voltage of the wave form. Some meters display an 'average' voltage which is very close to RMS. When reading voltage with a voltmeter, the display indicates the RMS or average voltage not the peak or peak-peak voltage

5.4.2 Implementation of RMS Function in Spartan-3A Board

The simplest method to calculate the RMS reading of the sinusoidal wave to use take

35

DESIGN A SINGLE CHANNEL DIGITAL VOLTMETER USING FPGA (J0605162)

KHIN AYE MU

the peak reading and divide by square root 2 (equation 1). For the Spartan-3A board hardware, the maximum peak range of the sinusoidal wave will be 1.25V (Maximum RMS < 0.88V), centered on the reference voltage, 1.65V as shown in Figure 5.7. There is some hardware and software manipulation need to be done in order to achieve the correct reading of RMS voltage

2.90V

1.65V

0.40V

Figure 5.7: Spartan-3A Hardware Setting for Sine Wave For the hardware, the sinusoidal wave will be generated by the signal generator and the DC offset of the signal generator need to be set to 1.65V. For the software portion, we need to hold the maximum reading from ADC and display on LCD as RMS voltage by subtracting the offset of 1.65V and divide by square root 2 as shown in Figure 5.8.

START

36 Sampling the input ADC voltage value

DESIGN A SINGLE CHANNEL DIGITAL VOLTMETER USING FPGA (J0605162)

KHIN AYE MU

Figure 5.8: Software Implementation of RMS Function

37

DESIGN A SINGLE CHANNEL DIGITAL VOLTMETER USING FPGA (J0605162)

KHIN AYE MU

Chapter 6 Simulation

The following simulation result shows us the waveform of the behavior model of amplifier gain setting. It runs from state IDLE to FINE. The mosi is the data transmit to amplifier from MSB to LSB, which is 00010001 in binary.

BIT 7

BIT 6

BIT 5

BIT 4

BIT 3

BIT 2

BIT 1 BIT 0

Figure 6.1: The simulated waveform of amplifier gain setting

38

DESIGN A SINGLE CHANNEL DIGITAL VOLTMETER USING FPGA (J0605162)

KHIN AYE MU

The simulation waveform below is about analog-to-digital signal capture. The input is ready at SPI_MISO signal. When the IDLE_ID start, the first two bits are dummy data. ADC1[13:0] starts to get data at third bits. It needs 34 cycles to capture all the data. Whole process is ended at FINE_AD state.

34 cycles to capture digital data

Figure 6.2: The simulated waveform of ADC data capture

39

DESIGN A SINGLE CHANNEL DIGITAL VOLTMETER USING FPGA (J0605162)

KHIN AYE MU

The following waveform shows the calculation of Vin. As the ADC is negative data, 2s complement need to be perform before the calculation of Vin.

The captured ADC data is hex 3FFF, signed bi is 1, 2s complement conversion is performed and result 0001 in hexadecimal.

Figure 6.3: Waveform of getting ADC data

The computed value VIN is ready for binary to BCD conversion.

Vin =125, that is 1.25V of input signal

Figure 6.4: Waveform of computing VIN

40

DESIGN A SINGLE CHANNEL DIGITAL VOLTMETER USING FPGA (J0605162)

KHIN AYE MU

The following waveform shows that BCD code 125 is ready for the LCD displaying.

BCD3 is 0, BCD2 is 1, BCD1 is 2, BCD is 5

Figure 6.5: Waveform of getting BCD data format The following waveform is a continuous loop to read data, calculate VIN and decode into BCD format.

Figure 6.6: Overall waveform

41

DESIGN A SINGLE CHANNEL DIGITAL VOLTMETER USING FPGA (J0605162)

KHIN AYE MU

Chapter 7 Hardware Realization 7.1 DC Voltage Measurement Verification

To verify the functionality of DC volt meter, a AAA battery of 1.5V is connected the ADC VINA and GND as show in the Figure 7.1.

AAA Battery (1.5V) DMM

+V COM

Figure 7.1: DC Voltage Measurement Setup

AAA Battery 1.5V

DMM Reading 1.483V

My Single Volt Meter Reading 1.462V

Table 7.1: DC Voltage Measurement

42

DESIGN A SINGLE CHANNEL DIGITAL VOLTMETER USING FPGA (J0605162)

KHIN AYE MU

7.2 RMS Sine Wave Measurement Verification

To verify the functionality of RMS functions for sine wave measurement, a function generator is connected the ADC VINA and GND as show in the Figure 7.2. The sampling frequency of ADC is initial set to 1 kHz.

Function Generator (DC Offset = 1.65V)

Oscilloscope

+V COM

Figure 7.2: Sine Wave Signal Measurement Setup

Vpp (Fun Gen) 0.2V 0.2V

Frequency (Fun Gen) 100Hz 10kHz

VRMS (Volt Meter) 0.135V 0.111V

Sampling frequency 1 kHz 1 kHz

Remarks

Not accurate due to low sampling frequency

0.2V 1.0V

10KHz 10kHz

0.136 0.704

20 kHz 20kHz

Table 7.2: RMS Sine Wave Voltage Measurement

43

DESIGN A SINGLE CHANNEL DIGITAL VOLTMETER USING FPGA (J0605162)

KHIN AYE MU

Chapter 8 Conclusion and Recommendation 8.1 Conclusion

This thesis described the design and validation of a VLSI Test Module implemented on the Spantan3A FPGA system that can be deployed to model a digital voltmeter as long as the signal voltage is within the range of ADC hardware (+0.4V ~ 2.9V). The main problem faced in this project is difficult to understand the hardware initialization and setting within the Spartan-3A board. A lot of effort and time is spend debugging the hardware ADC circuit and LED panel even though the simulation waveform is perfectly working fine in the ModelSIM. Hardware verification result shows that the digital voltmeter using FPGA showed that the result is quite accurate if the sampling frequency is high enough. If the sampling frequency is set to too high, it will capture unwanted noise and as result degrade the performance of the volt meter. Ideally, the sampling frequency will be best to be set around 4~5 time of the signal frequency

8.2 Recommendations for Future Study The input signal for the single channel digital voltmeter is limited to analog DC voltage and sine wave. Future work can also included different types of input signal (square wave, etc) and also enable to read the frequency of the signal. There is also ADC hardware limitation which can only measure the range between 0.4V and 2.9. In order to increase the dynamic voltage range of this digital voltmeter, external circuit can be installed to attenuate the voltage before the Spartan3A ADC circuit.

44

DESIGN A SINGLE CHANNEL DIGITAL VOLTMETER USING FPGA (J0605162)

KHIN AYE MU

Critical Review and Reflections

Although the general purpose VLSI (Very Large Scale Integration) Test Module based on a FPGA (Field Programmable Gate Array) system attracted much research during the past few decades, the embedded system to model a digital voltmeter research is a new and challenging subject for me. One of the most important parts of the project which is the Literature research, on the overview of Architecture of FPGAs and VHDL programming were carried out first. With the help of project workshop, searching of reference materials were relatively easy. Ngee Ann Polytechnic Library, Lee Kong Chian reference library, IEEE technical papers and World Wide Web were main sources for my literature research. Nevertheless, it is hard to understand most of the research papers initially. After spending more than one month for the literature research, my understanding on the project and technical paper reading skills have improved noticeably.

As a second phase, I prepared my project initial report which includes project objectives, investigation of project background, project management, proposed approaches and methods to be employed as well as skills review. As initial planning is important in order to complete the objectives, proposed approaches were systematically analyzed and selected. Project plan was also scheduled with details.

Similar to any other students, so many obstacles were encountered while doing the project. The first problem encountered was to understand of the embedded FPGA board (Spartan-3A). Although the Spartan-3A board comes with the instructions and starter kit board user guide, but there is a lot of problem faced when programming the initialization and setting of the hardware. If these setting of the values are not set correct, the program will either not run or hang up. .

45

DESIGN A SINGLE CHANNEL DIGITAL VOLTMETER USING FPGA (J0605162)

KHIN AYE MU

From this project, we have learnt new skills like drawing a Gantt chart and VHDL programming. Existing skills such as research, analytical, problem solving, project and time management and technical report writing were improved significantly. In short, this project has provided us with terrific chance for learning and improving ourselves technical and critical thinking skills.

46

DESIGN A SINGLE CHANNEL DIGITAL VOLTMETER USING FPGA (J0605162)

KHIN AYE MU

Bibliography

[1] http://en.wikipedia.org/wiki/Field-programmable_gate_array [2] http://en.wikipedia.org/wiki/Voltmeter [3] Clive Lee. IPT Guidance for Acquisition of Systems with Complex Programmable Hardware using DO-254. Jun. (2007). ASSC. [4] Thomas David Vancourt. LAMP: Tools for Creating Application-Specific FPGA Coprocessors. (2006) [5] Stephan Brown and Jonathan Rose, Architecture of FPGAs and CPLDs : A Tutorial, University of Toronto, P7. [6] Xilinx Inc., Spartan-3A FPGA Family: Completer Data Sheet, DS529 March 6, 2009 [7] Xilinx Inc., Spartan-3A Starter Kit Board User Guide, UG334 (v1.0) June 19, 2008 [8]Introduction to VLSI Design. [9] Kevin Morris, FPGA Simulation: Forget what you learned in ASIC design. FPGA and Programmable Logic Journal. Jun. (2004). [10] Mentor Graphics Inc., URL: http://www.mentor.com/ [11] Mentor Graphics Inc., LeonardoSpectrum HDL Synthesis [12] University of Pennsylvania, Introduction to Xilinx ISE 8.2i [13] Xilinx Inc. Xilinx ISE 8 Software Manuals and Help. ISE 8 Manuals. [14] Guillaume Savaton, Jerome Delatour, Karl Courtel. Roll your own Hardware Description Language: An Experiment in Hardware Development using Model Driven Software Tools.

47

DESIGN A SINGLE CHANNEL DIGITAL VOLTMETER USING FPGA (J0605162)

KHIN AYE MU

APPENDIX: VHDL CODE FOR VOLTMETER

---------------------------------------------------------------------------------- Company: -- Engineer: --- Create Date: -- Design Name: -- Module Name: -- Project Name: -- Target Devices: -- Tool versions: -- Description: --- Dependencies: --- Revision: -- Revision 0.01 - File Created -- Additional Comments: ---------------------------------------------------------------------------------library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_ARITH.ALL; use IEEE.STD_LOGIC_UNSIGNED.ALL; use IEEE.numeric_bit.all; ---- Uncomment the following library declaration if instantiating ---- any Xilinx primitives in this code. --library UNISIM; --use UNISIM.VComponents.all; entity voltmeter is Port ( AMP_CS : out AMP_SHDN : out CE_AMP : in CLK : in LCD : out CONV : out LCD_E : out LCD_RS : out LCD_RW : out STD_LOGIC; STD_LOGIC; voltmeter - Behavioral 10:30:58 08/01/2009

STD_LOGIC; STD_LOGIC;

STD_LOGIC; STD_LOGIC_VECTOR (7 downto 4); STD_LOGIC; STD_LOGIC; STD_LOGIC;

48

DESIGN A SINGLE CHANNEL DIGITAL VOLTMETER USING FPGA (J0605162)

START_CONV : in LED : out MOSI : out PUSH_B : in SCK : out SW : in AMP : in end voltmeter; architecture Behavioral of voltmeter is STD_LOGIC;

KHIN AYE MU

STD_LOGIC_VECTOR (7 downto 0); STD_LOGIC; STD_LOGIC_VECTOR (3 downto 0); STD_LOGIC; STD_LOGIC;

SPI_MISO : in

STD_LOGIC_VECTOR (3 downto 0); STD_LOGIC);

type state_type is (IDLE, START,START2,HI,HI_DUMMY,LO,LO_DUMMY,FINE, IDLE_AD, START_AD,HI_AD,LO_AD,FINE_AD, DECODE1, DECODE2, BCD_START, BCD_INIT, BCD_ADJ, BCD_SHIFT, BCD_NEXT, BCD_DONE, PRINT_LCD_START, PRINT_LCD_CODE, PRINT_LCD_DUMMY); signal next_state, state : state_type; signal counter : integer range 0 to 35 :=0; signal sample : std_logic; signal gain : std_logic_vector(7 downto 0):=x"11"; signal ADC1 : std_logic_vector(13 downto 0):="00000000000000"; signal ADC2 : std_logic_vector(13 downto 0); signal ADC3 : std_logic_vector(13 downto 0); signal ADC4 : std_logic_vector(13 downto 0);

signal sum1 : integer range 0 to 32768:=0; signal sum2 : integer range 0 to 32768:=0; signal sum3 : integer range 0 to 32768:=0; signal sum4 : integer range 0 to 32768:=0; signal sum5 : integer range 0 to 32768:=0; signal sum6 : integer range 0 to 32768:=0; signal sum7: integer range 0 to 32768:=0; signal sum8 : integer range 0 to 32768:=0; signal sum9 : integer range 0 to 32768:=0; signal sum10 : integer range 0 to 32768:=0; signal sum11 : integer range 0 to 32768:=0; signal sum12 : integer range 0 to 32768:=0;

49

DESIGN A SINGLE CHANNEL DIGITAL VOLTMETER USING FPGA (J0605162)

signal sum13 : integer range 0 to 32768:=0; signal sum : integer range 0 to 32768:=0; signal total_sum : integer range 0 to 32768:=0; signal result : integer range 0 to 32768:=0; signal result2 : integer range 0 to 32768:=0; signal Vin : std_logic_vector(12 downto 0); signal decoder_on : integer range 0 to 7:=0;

KHIN AYE MU

signal BCD_on :STD_LOGIC; signal Vin_reg,Vin_shift: std_logic_vector (12 downto 0); signal bcd3_reg, bcd2_reg, bcd1_reg, bcd0_reg: STD_LOGIC_VECTOR (3 downto 0); signal bcd3_adj, bcd2_adj, bcd1_adj, bcd0_adj: downto 0); signal bcd3_shift, bcd2_shift, bcd1_shift, bcd0_shift: STD_LOGIC_VECTOR (3 downto 0); signal bcd3 : signal bcd2 : signal bcd1 : signal bcd0 : STD_LOGIC_VECTOR (3 downto 0); STD_LOGIC_VECTOR (3 downto 0); STD_LOGIC_VECTOR (3 downto 0); STD_LOGIC_VECTOR (3 downto 0); STD_LOGIC_VECTOR (3

signal code : signal code1 : signal code2 :

STD_LOGIC_VECTOR (3 downto 0); STD_LOGIC_VECTOR (5 downto 0); STD_LOGIC_VECTOR (5 downto 0);

signal int_count signal int_count2

: integer range 0 to 49999999 :=0; : integer range 0 to 49999999 :=0;

signal display: integer range 0 to 1:=0; signal clk_display : std_logic_vector(7 downto 0) := "00000000"; signal gain_display : std_logic_vector(7 downto 0) := "00000000"; signal lcd_code: std_logic_vector (5 downto 0); signal text1:std_logic_vector (5 downto 0):="100011"; signal text2:std_logic_vector (5 downto 0):="100000"; signal text3:std_logic_vector (5 downto 0):="100011"; signal text4:std_logic_vector (5 downto 0):="100000"; signal text5:std_logic_vector (5 downto 0):="100011";

50

DESIGN A SINGLE CHANNEL DIGITAL VOLTMETER USING FPGA (J0605162)

signal text6:std_logic_vector (5 downto 0):="100000"; signal text7:std_logic_vector (5 downto 0):="100011"; signal text8:std_logic_vector (5 downto 0):="100000"; signal text9:std_logic_vector (5 downto 0):="100011"; signal text10:std_logic_vector (5 downto 0):="100000"; signal text11:std_logic_vector (5 downto 0):="100011"; signal text12:std_logic_vector (5 downto 0):="100000"; signal line:std_logic_vector (5 downto 0); --signal text1:std_logic_vector (5 downto 0):="100101"; --signal text2:std_logic_vector (5 downto 0):="100011"; -- signal text3:std_logic_vector (5 downto 0):="100101"; -- signal text4:std_logic_vector (5 downto 0):="100100"; -- signal text5:std_logic_vector (5 downto 0):="100100"; -- signal text6:std_logic_vector (5 downto 0):="100001"; -- signal text7:std_logic_vector (5 downto 0):="100101"; -- signal text8:std_logic_vector (5 downto 0):="100010"; -- signal text9:std_logic_vector (5 downto 0):="100101"; -- signal text10:std_logic_vector (5 downto 0):="100100"; --signal line:std_logic_vector (5 downto 0):="001000"; begin process(START_CONV,CE_AMP,state,counter) variable bit_count : integer range 0 to 15; variable BCD_bit_count : integer range 0 to 15; variable LCD_char_count : integer range 0 to 15; begin case state is when IDLE => if CE_AMP ='1' then next_state <= START; else next_state <= IDLE; end if; when START => next_state <= START2; bit_count :=0; when START2 => next_state <= HI; when HI => if counter = 2 then next_state <= HI_DUMMY;

KHIN AYE MU

51

DESIGN A SINGLE CHANNEL DIGITAL VOLTMETER USING FPGA (J0605162)

else next_state <= HI; end if; when HI_DUMMY => bit_count := bit_count + 1; next_state <= LO; when LO => if counter = 2 then next_state <= LO_DUMMY; else next_state <= LO; end if; when LO_DUMMY => if bit_count = 8 then next_state <= FINE; else next_state <= HI; end if; when FINE => next_state <= IDLE_AD; when IDLE_AD => if start_conv ='1' then next_state <= START_AD; else next_state <= IDLE_AD; end if; when START_AD => next_state <= HI_AD; when HI_AD => next_state <= LO_AD; when LO_AD => if counter = 34 then next_state <= FINE_AD; else next_state <= HI_AD; end if; when FINE_AD => next_state <= DECODE1; when DECODE1 => next_state <= DECODE2; when DECODE2 =>

KHIN AYE MU

52

DESIGN A SINGLE CHANNEL DIGITAL VOLTMETER USING FPGA (J0605162)

next_state <= BCD_START; when BCD_START => next_state <= BCD_INIT; BCD_bit_count:=0; when BCD_INIT => next_state <= BCD_ADJ; when BCD_ADJ=> next_state <= BCD_SHIFT; when BCD_SHIFT => next_state <= BCD_NEXT; when BCD_NEXT => if BCD_bit_count=12 then next_state <= BCD_DONE; else BCD_bit_count:=BCD_bit_count+1; next_state <= BCD_ADJ; end if; when BCD_DONE => next_state <= PRINT_LCD_START; LCD_char_count:=0; when PRINT_LCD_START => next_state <= PRINT_LCD_CODE; when PRINT_LCD_CODE => if LCD_char_count=4 then next_state <= IDLE_AD; else LCD_char_count:=LCD_char_count+1; next_state <= PRINT_LCD_DUMMY; end if; when PRINT_LCD_DUMMY => next_state <= PRINT_LCD_START; when others => next_state <= IDLE_AD; end case; end process;

KHIN AYE MU

process (CLK) variable count: std_logic_vector(26 downto 0) :="000000000000000000000000000";

53

DESIGN A SINGLE CHANNEL DIGITAL VOLTMETER USING FPGA (J0605162)

variable initialise : integer range 0 to 1:=0; begin if (CLK'event and CLK='1') then count := count + 1; --sf_ce0 <= '1'; case (count(26 downto 21)) is when "000000" => lcd_code <= "000011"; initialization when "000001" => lcd_code <= "000011"; when "000010" => lcd_code <= "000011"; when "000011" => lcd_code <= "000010"; when "000100" => lcd_code <= "000010"; when "000101" => lcd_code <= "001000"; when "000110" => lcd_code <= "000000"; when "000111" => lcd_code <= "000110"; when "001000" => lcd_code <= "000000"; control when "001001" => lcd_code <= "001100"; when "001010" => lcd_code <= "000000"; when "001011" => lcd_code <= "000001"; when "001100" => lcd_code <= "100101"; when "001101" => lcd_code <= "100010"; when "001110" => lcd_code <= "100100"; when "001111" => lcd_code <= "101101"; when "010000" => lcd_code <= "100101"; when "010001" => lcd_code <= "100011"; --when "010010" => lcd_code <= "001100"; address to 40 --when "010011" => lcd_code <= "000000"; when "010100" => lcd_code <= "100101"; when "010101" => lcd_code <= "100110"; when "010110" => lcd_code <= "100110"; when "010111" => lcd_code <= "101111"; when "011000" => lcd_code <= "100110"; when "011001" => lcd_code <= "101100"; --- function set -- power-on

KHIN AYE MU

-- entry mode set -- display on/off

-- display clear

-- R 100101 100010 --- M 100100 101101 --- S 100101 100011 --- Set DD RAM

-- V 100101 100110 --- o 100110 101111 --- l 100110 101100 --

54

DESIGN A SINGLE CHANNEL DIGITAL VOLTMETER USING FPGA (J0605162)

KHIN AYE MU

when "011010" => lcd_code <= "100111"; when "011011" => lcd_code <= "100100"; when "011100" => lcd_code <= "100110"; when "011101" => lcd_code <= "100001"; when "011110" => lcd_code <= "100110"; when "011111" => lcd_code <= "100111"; when "100000" => lcd_code <= "100110"; when "100001" => lcd_code <= "100101"; when "100010" => lcd_code <= "001100"; to 40 when "100011" => lcd_code <= "000000"; when "100100"=> lcd_code <= text1; when "100101"=> lcd_code <= text2; when "100110"=> lcd_code <= text3; when "100111"=> lcd_code <= text4; when "101000"=> lcd_code <= "101010"; when "101001"=> lcd_code <= "100101"; when "101010"=> lcd_code <= text7; to 40 when "101011"=> lcd_code <= text8; when "101100"=> lcd_code <= text9; when "101101"=> lcd_code <= text10; when "101110" => lcd_code <= "001100"; to 40 when "101111" => lcd_code <= "001001"; when "110000"=> lcd_code <= text11; when "110001"=> lcd_code <= text12; when others => lcd_code <= "010000"; end case; --

-- t 100111 100100 --- a 100110 100001 --- g 100110 100111 --- e 100110 100101 --- Set DD RAM address --- R 100101 100010 --- M 100100 101101 --- S 100101 100011 --- Set DD RAM address

-- V 100101 100110 --- Set DD RAM address --- V 100101 100110 --

55

DESIGN A SINGLE CHANNEL DIGITAL VOLTMETER USING FPGA (J0605162)

end if; LCD_E <= (count(20) xor count(19)) and (not lcd_code(4)); the clock rate by 2^21 LCD_RS <= lcd_code(5); LCD_RW <= lcd_code(4); LCD(7) <= lcd_code(3); LCD(6) <= lcd_code(2); LCD(5) <= lcd_code(1); LCD(4) <= lcd_code(0); end process ;

KHIN AYE MU

--divide

process(CLK) begin if decoder_on=0 then if CLK'event and CLK ='1' then state <= next_state; end if; sum<=0;sum1<=0;sum2<=0;sum3<=0;sum4<=0;sum5<=0;sum6<=0;sum7<=0;su m8<=0;sum9<=0;sum10<=0;sum11<=0;sum12<=0;sum13<=0;

else if ADC1(13)='1' then ADC3 <= ADC1 XOR "11111111111111"; ADC4 <= ADC3 +1; ADC4(13)<='0'; else ADC4 <= ADC1; end if; if ADC4(0)='1' then sum1<=1; end if; if ADC4(1)='1' then sum2<= 2; end if; if ADC4(2)='1' then sum3<= 4; end if; if ADC4(3)='1' then sum4<= 8; end if; if ADC4(4)='1' then sum5<= 16; end if; if ADC4(5)='1' then sum6<= 32; end if; if ADC4(6)='1' then sum7<= 64; end if;

56

DESIGN A SINGLE CHANNEL DIGITAL VOLTMETER USING FPGA (J0605162)

if ADC4(7)='1' then sum8<= 128; end if; if ADC4(8)='1' then sum9<= 256; end if; if ADC4(9)='1' then sum10<=512; end if; if ADC4(10)='1' then sum11<=1024; end if; if ADC4(11)='1' then sum12<=2048; end if; if ADC4(12)='1' then sum13<=4096; end if;

KHIN AYE MU

total_sum<=sum1+sum2+sum3+sum4+sum5+sum6+sum7+sum8+sum9+sum10+sum 11+sum12+sum13; end if; end process;

process (CLK) variable index1 : integer range 0 to 15; variable index2 : integer range 0 to 15; variable print_char_no : integer range 0 to 7; variable gain_count : integer range 0 to 7; begin AMP_SHDN <= '0'; if CLK'event and CLK ='1' then case state is when IDLE => SCK <= '0'; AMP_CS <= '1'; MOSI <='0'; counter <=0; gain_count:=0; LED<=X"00"; text11<="100100"; text12<="100001";

when START => AMP_CS <= '0'; index1 := 7; -- 8 bit value LED<=X"01"; when START2 =>

57

DESIGN A SINGLE CHANNEL DIGITAL VOLTMETER USING FPGA (J0605162)

MOSI <= gain(index1); LED<=X"02"; when HI => SCK <= '1'; counter <= counter +1; LED<=X"03"; when HI_DUMMY => counter <=0; LED<=X"04"; when LO => SCK <= '0'; counter <= counter +1; LED<=X"05"; when LO_DUMMY => MOSI <= gain(index1); LED<=X"06"; index1 := index1-1; counter <=0; when FINE => AMP_CS <='1'; SCK <= '0'; MOSI <= '0'; LED<=X"07"; text11<="100100"; text12<="100010"; when IDLE_AD => SCK <= '0'; CONV <= '0'; sample <='0'; LED<=X"08"; text11<="100100"; text12<="100010"; when START_AD => SCK <= '0'; CONV <= '1'; counter <= 0;

KHIN AYE MU

58

DESIGN A SINGLE CHANNEL DIGITAL VOLTMETER USING FPGA (J0605162)

sample <='0'; index1 := 13; -- 14 bit value index2 := 13; -- 14 bit value LED<=X"09"; when HI_AD => SCK <= '1'; CONV <= '0'; counter <= counter +1; sample <='0'; LED<=X"0A"; when LO_AD => SCK <= '0'; CONV <= '0'; LED<=X"0B"; if(counter >2 and counter < 17) then --if index1 = 13 then -- ADC1(index1) --else ADC1(index1) --end if; index1 := index1 -1; sample <='1'; <= SPI_MISO; <= not SPI_MISO;

KHIN AYE MU

elsif(counter > 18 and counter < 33) then --if index2 = 13 then -- ADC2(index2) --else ADC2(index2) --end if; index2 := index2 -1; sample <='1'; else <= SPI_MISO; <= not SPI_MISO;

59

DESIGN A SINGLE CHANNEL DIGITAL VOLTMETER USING FPGA (J0605162)

sample <='0'; end if; when FINE_AD => counter <= 0; sample <='0'; SCK <= '0'; CONV <= '0'; LED<=X"0C"; decoder_on<=1; when DECODE1 => SCK <= '0'; CONV <= '0'; AMP_CS <= '1'; MOSI <='0'; LED<=X"0D"; decoder_on<=0; text11<="100100"; text12<="100011"; when DECODE2 => SCK <= '0'; CONV <= '0'; AMP_CS <= '1'; MOSI <='0'; LED<=X"0E"; if ADC1(13)='1' then result2 <= total_sum*125/8192 +125; else result2 <=125-total_sum*125/8192 ; end if; when BCD_START => SCK <= '0'; CONV <= '0'; AMP_CS <= '1'; MOSI <='0'; LED<=X"0F"; Vin <=conv_std_logic_vector(result2,13); BCD_on <= '1'; when BCD_INIT => SCK <= '0';

KHIN AYE MU

60

DESIGN A SINGLE CHANNEL DIGITAL VOLTMETER USING FPGA (J0605162)

CONV <= '0'; AMP_CS <= '1'; MOSI <='0'; LED<=X"10"; BCD_on <= '1'; Vin_reg <=Vin; bcd3_reg<=(others =>'0'); bcd2_reg<=(others =>'0'); bcd1_reg<=(others =>'0'); bcd0_reg<=(others =>'0');

KHIN AYE MU

when BCD_ADJ => SCK <= '0'; CONV <= '0'; AMP_CS <= '1'; MOSI <='0'; LED<=X"12"; BCD_on <= '1'; if bcd0_reg > 4 then bcd0_adj <=bcd0_reg+3; else bcd0_adj <= bcd0_reg; end if; if bcd1_reg > 4 then bcd1_adj <=bcd1_reg+3; else bcd1_adj <= bcd1_reg; end if; if bcd2_reg > 4 then bcd2_adj <=bcd2_reg+3; else bcd2_adj <= bcd2_reg; end if; if bcd3_reg > 4 then bcd3_adj <=bcd3_reg+3; else bcd3_adj <= bcd3_reg; end if;

61

DESIGN A SINGLE CHANNEL DIGITAL VOLTMETER USING FPGA (J0605162)

KHIN AYE MU

when BCD_SHIFT => SCK <= '0'; CONV <= '0'; AMP_CS <= '1'; MOSI <='0'; LED<=X"13"; BCD_on <= '1'; Vin_shift <= Vin_reg(11 downto 0) & '0'; bcd0_shift <= bcd0_adj(2 downto 0) & Vin_reg(12); bcd1_shift <= bcd1_adj(2 downto 0) & bcd0_adj(3); bcd2_shift <= bcd2_adj(2 downto 0) & bcd1_adj(3); bcd3_shift <= bcd3_adj(2 downto 0) & bcd2_adj(3); when BCD_NEXT => SCK <= '0'; CONV <= '0'; AMP_CS <= '1'; MOSI <='0'; LED<=X"14"; BCD_on <= '1'; Vin_reg <= Vin_shift; bcd0_reg <=bcd0_shift; bcd1_reg <=bcd1_shift; bcd2_reg <=bcd2_shift; bcd3_reg <=bcd3_shift;

when BCD_DONE => SCK <= '0'; CONV <= '0'; AMP_CS <= '1'; MOSI <='0'; LED<=X"15"; BCD_on <= '0'; bcd0 <= std_logic_vector (bcd0_reg); bcd1 <= std_logic_vector (bcd1_reg); bcd2 <= std_logic_vector (bcd2_reg); bcd3 <= std_logic_vector (bcd3_reg); print_char_no:=0;

62

DESIGN A SINGLE CHANNEL DIGITAL VOLTMETER USING FPGA (J0605162)

KHIN AYE MU

when PRINT_LCD_START => SCK <= '0'; CONV <= '0'; AMP_CS <= '1'; MOSI <='0'; LED<=X"16"; if print_char_no=0 then code<= bcd0; elsif print_char_no=1 then code<= bcd1; elsif print_char_no=2 then code<= bcd2; else code<= bcd3; end if; text11<="100100"; text12<="100100"; when PRINT_LCD_CODE => case code is when "0000" => code1 <= "100011"; code2 <= "100000"; when "0001" => code1 <= "100011"; code2 <= "100001"; when "0010" => code1 <= "100011"; code2 <= "100010"; when "0011" => code1 <= "100011"; code2 <= "100011"; when "0100" => code1 <= "100011"; code2 <= "100100"; when "0101" => code1 <= "100011"; code2 <= "100101"; when "0110" => code1 <= "100011"; code2 <= "100110"; when "0111" => code1 <= "100011"; code2 <= "100111"; when "1000" => code1 <= "100011"; code2 <= "101000"; when "1001" => code1 <= "100011"; code2 <= "101001"; when others => code1 <= "100010"; code2 <= "100011"; end case; when PRINT_LCD_DUMMY => if print_char_no=0 then text9<= code1; text10<= code2; elsif print_char_no=1 then text7<= code1; text8<= code2; elsif print_char_no=2 then text3<= code1;

63

DESIGN A SINGLE CHANNEL DIGITAL VOLTMETER USING FPGA (J0605162)

text4<= code2; else text1<= code1; text2<= code2; end if; print_char_no:=print_char_no+1; LED<=X"FF"; when others => SCK <= '0'; CONV <= '0'; AMP_CS <= '1'; MOSI <='0'; LED<=X"00"; end case; end if; end process; end Behavioral;

KHIN AYE MU

64

DESIGN A SINGLE CHANNEL DIGITAL VOLTMETER USING FPGA (J0605162)

KHIN AYE MU

Glossary

AC In alternating current (AC, also ac) the movement (or flow) of electric charge periodically reverses direction. An electric charge would for instance move forward, then backward, then forward, then backward, over and over again BCD In computing and electronic systems, binary-coded decimal (BCD) (sometimes called natural binary-coded decimal, NBCD) is an encoding for decimal numbers in which each digit is represented by its own binary sequence DC In direct current (DC), the movement (or flow) of electric charge is only in one direction. Flowchart A flowchart is a common type of diagram that represents an algorithm or process showing the steps as boxes of various kinds, and their order by connecting these with arrows. Flowcharts are used in analyzing, designing, documenting or managing a process or program in various fields FPGA FPGAs contain programmable logic components called "logic blocks", and a hierarchy of reconfigurable interconnects that allow the blocks to be "wired together"somewhat like a one-chip programmable breadboard. Logic blocks can be configured to perform complex combinational functions, or merely simple logic gates like AND and XOR. In most FPGAs, the logic blocks also include memory elements, which may be simple flip-flops or more complete blocks of memory HDL In electronics, a hardware description language or HDL is any language from a class of computer languages and/or programming languages for formal description of electronic circuits, and more specifically, digital logic. It can describe the circuit's operation, its design and organization, and tests to verify its operation by means of simulation LCD A liquid crystal display (LCD) is a thin, flat panel used for electronically displaying information such as text, images, and moving pictures.

65

DESIGN A SINGLE CHANNEL DIGITAL VOLTMETER USING FPGA (J0605162)

KHIN AYE MU

Sampling Frequency The sampling rate, sample rate, or sampling frequency defines the number of samples per second (or per other unit) taken from a continuous signal to make a discrete signal. For time-domain signals, it can be measured in samples per second (S/s),[1] or hertz (Hz).[2] The inverse of the sampling frequency is the sampling period or sampling interval, which is the time between samples

RMS The RMS value of a set of values (or a continuous-time waveform) is the square root of the arithmetic mean (average) of the squares of the original values (or the square of the function that defines the continuous waveform).

VLSI Very-large-scale integration (VLSI) is the process of creating integrated circuits by combining thousands of transistor-based circuits into a single chip. VLSI began in the 1970s when complex semiconductor and communication technologies were being developed

End of Report

66

Vous aimerez peut-être aussi

- 74HC4067 Analog Multiplexer TutorialDocument14 pages74HC4067 Analog Multiplexer TutorialpolikarpaPas encore d'évaluation

- Analog MultiplexerDocument13 pagesAnalog MultiplexerSanjoy PandaPas encore d'évaluation

- Esr LCR r2d2Document6 pagesEsr LCR r2d2Toñi Lopez Vilches100% (1)

- Multimeter ReportDocument15 pagesMultimeter Reportapi-244226518Pas encore d'évaluation

- Hioki 3532 50 LCR MeterDocument8 pagesHioki 3532 50 LCR MeterSourabh ChoudharyPas encore d'évaluation

- Manual Data Aplication HP3457Document141 pagesManual Data Aplication HP3457FrancoilPas encore d'évaluation

- Digital Multimeter Circuit Using IclDocument6 pagesDigital Multimeter Circuit Using IclOnyebuchi SundayPas encore d'évaluation

- Adafruit Amg8833 8x8 Thermal Camera SensorDocument35 pagesAdafruit Amg8833 8x8 Thermal Camera SensorAschtung YepPas encore d'évaluation

- I S Bus Specification: 1.0 2.0 Basic Serial Bus RequirementsDocument7 pagesI S Bus Specification: 1.0 2.0 Basic Serial Bus RequirementseballiriPas encore d'évaluation

- Four Output Bench Supply ArticleDocument4 pagesFour Output Bench Supply ArticleOscar RomeuPas encore d'évaluation

- Pull-Up and Pull-Down Resistors For Micro Controllers by ShanDocument3 pagesPull-Up and Pull-Down Resistors For Micro Controllers by Shanshantilaal100% (1)

- PIC Single-Chip 4-Digit 99-Minute Timer: DiscussionDocument4 pagesPIC Single-Chip 4-Digit 99-Minute Timer: Discussionravikiran1955Pas encore d'évaluation

- Analog Solutions For Xilinx FPGAsDocument36 pagesAnalog Solutions For Xilinx FPGAsestraj1954Pas encore d'évaluation

- VHDL Code For Adc0804, Comparator and Parity GeneratorDocument26 pagesVHDL Code For Adc0804, Comparator and Parity GeneratorAparnaSkp100% (1)

- Analog-To-digital Converter - Wikipedia, The Free EncyclopediaDocument6 pagesAnalog-To-digital Converter - Wikipedia, The Free EncyclopediaAziz SahatPas encore d'évaluation

- Embedded Systems Projects ListDocument38 pagesEmbedded Systems Projects ListMayank ChauhanPas encore d'évaluation

- Multiplex CommunicationDocument17 pagesMultiplex CommunicationlogammicPas encore d'évaluation

- Digital Multimeter Working Principle - Electrical A2ZDocument7 pagesDigital Multimeter Working Principle - Electrical A2Zrohitsingh2909Pas encore d'évaluation

- 02 PIC ADC Final PDFDocument68 pages02 PIC ADC Final PDFRagini GuptaPas encore d'évaluation

- Rfid Security Access Control System: Submitted byDocument20 pagesRfid Security Access Control System: Submitted byVale Conde CuatzoPas encore d'évaluation

- T89C51 Training Board Manual GuideDocument44 pagesT89C51 Training Board Manual GuidedavidegrimaPas encore d'évaluation

- ABB RS232 wiring standards guideDocument7 pagesABB RS232 wiring standards guidel1f3b00kPas encore d'évaluation

- nRF52840 PS v1.5Document631 pagesnRF52840 PS v1.5Benyamin Farzaneh AghajariePas encore d'évaluation

- Interfacing Programs For 8085Document37 pagesInterfacing Programs For 8085archankumarturagaPas encore d'évaluation

- 25.ACCESSIBLE DISPLAY DESIGN TO CONTROL HOME AREA NETWORKSDocumentDocument84 pages25.ACCESSIBLE DISPLAY DESIGN TO CONTROL HOME AREA NETWORKSDocumentdileeppatraPas encore d'évaluation

- Unit 6 I ADCDocument29 pagesUnit 6 I ADCcacaPas encore d'évaluation

- Schematic LCR MeterDocument1 pageSchematic LCR MeterTrường Phúc Lưu100% (1)