Académique Documents

Professionnel Documents

Culture Documents

Circuito RLC-Paralelo

Transféré par

Rafael CarvalhoTitre original

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

Circuito RLC-Paralelo

Transféré par

Rafael CarvalhoDroits d'auteur :

Formats disponibles

FAT Faculdade de Tecnologia de Resende Departamento de Energia e Mecnica Eletricidade Terica e Experimental Prtica 4 Ttulo: CIRCUITO RLC PARALELO

LO 1. Objetivo: Verificar, experimentalmente, o comportamento de um circuito RLC paralelo. 2. Introduo Terica: O circuito RLC paralelo composto por um resistor, um capacitor e um indutor, associados em paralelo, conforme mostra a figura 1.

Figura 1: Circuito RLC paralelo Na construo do diagrama vetorial visto na figura 2, consideraremos como referncia a tenso, sendo que neste caso, ela est adiantada de /2 rad em relao corrente do capacitor.

Figura 2: Diagrama vetorial de um circuito RLC paralelo Para fins de diagrama vetorial, utiliza-se a resultante, pois, os vetores que representam a corrente no capacitor e a corrente no indutor tm a mesma direo e sentidos opostos. Observando o diagrama, notamos que ICef maior que ILef, portanto temos como resultante um vetor (ICef ILef). No caso de termos ILef maior que ICef, obteremos um vetor resultante (I Lef ICef) com sentido oposto ao anteriormente descrito. Do diagrama, temos que, a soma vetorial da corrente resultante com a do resistor igual a corrente total do circuito. Assim sendo, podemos escrever. Ief2 = IRef2 + (ICef ILef )2 Dividindo todos os termos por Vef2, temos: (Ief / Vef)2 = (IRef / Vef)2 + [(ICef / Vef) (ILef / Vef )]2 Onde: Ief / Vef = 1 / Z, IRef / Vef = 1 / R, ILef / Vef = 1 / XL e ICef / Vef = 1 / XC. Portanto, podemos escrever: (1 / Z)2 = (1 / R)2 + [(1 / XL 1 / XC)]2 2 ou Z = 1 / [(1 / R) + (1 / XL 1 / XC)2]1/2, que o valor da impedncia no circuito.

O ngulo a defasagem entre a tenso e a corrente no circuito e pode ser determinado atravs das relaes trigonomtricas do tringulo retngulo: sen = (ICef ILef ) / Ief = (1 / XL 1 / XC) / (1 / Z) cos = IRef / Ief = (1 / R) / (1 / Z) = Z / R tg = (ICef ILef ) / IRef = (1 / XC 1 / XL) / (1 / R) = R (1 / XC 1 / XL) Da mesma forma que no circuito RLC srie, o circuito RLC paralelo estar em ressonncia, quando tivermos valores iguais para as reatncias indutiva e capacitiva. Tal fato, acontece na freqncia de ressonncia (f0), determinada por: f0 = 1 / 2(LC)1/2 Para o circuito RLC paralelo em ressonncia, teremos a mxima impedncia (Z = R), sendo a curva da impedncia em funo da freqncia vista na figura 3.

Figura 3 Podemos, tambm, levantar a curva da corrente em funo da freqncia para o mesmo circuito. Esta curva vista na figura 4.

Figura 4 Pelo grfico, observamos que, para a freqncia de ressonncia, a corrente mnima (I 0), pois a impedncia mxima (Z = R). 3. Material Experimental: Gerador de sinais Osciloscpio Capacitor: 0,01 F Indutor: 10 mH Resistores: 10 e 2,2 K

4. Prtica: 1 - Monte o circuito da figura 5. Ajuste o gerador de sinais para 5 Vpp, onda senoidal.

Figura 5 2 - Varie a freqncia do gerador de sinais, conforme o quadro 1. Para cada valor ajustado, mea e anote a tenso pico-a-pico no resistor de 10 . F (KHz) 10 11 12 13 14 15 16 17 18 19 20 V1pp V1ef Ief Z

Quadro 1 5. Questes: 1 - Calcule o valor eficaz das tenses no resistor de 10 , preenchendo o quadro 1. 2 - Calcule o valor eficaz das correntes no circuito, utilizando Ief = V1ef / 10, preenchendo o quadro 1. 3 - Calcule a impedncia para cada caso, utilizando Z = Vef / Ief, preenchendo o quadro 1. 4 - Construa os grficos Z = f (f) e Ief = f (f). 5 - Determine a freqncia de ressonncia no grfico Z = f(f). 6 Calcule a impedncia na freqncia de ressonncia do circuito da figura 6, quando a chave S estiver aberta e quando estivar fechada. Discuta os resultados.

Figura 6

Vous aimerez peut-être aussi

- Zeros Reais Newton Raphson e Secante 2018 2Document8 pagesZeros Reais Newton Raphson e Secante 2018 2HORUS_KHANPas encore d'évaluation

- Injeção Direta de Gasolina Bosch MotronicDocument60 pagesInjeção Direta de Gasolina Bosch MotronicRogério Moreno100% (2)

- Campo ElétricoDocument26 pagesCampo ElétricoDaniel Silva Photo e DesignPas encore d'évaluation

- Experiência-1 - OsciloscopioDocument7 pagesExperiência-1 - OsciloscopioThalis CaixetaPas encore d'évaluation

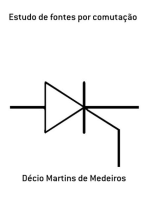

- Relatório 04 - Retificador Monofásico de Meia OndaDocument7 pagesRelatório 04 - Retificador Monofásico de Meia OndaArmando SusinPas encore d'évaluation

- Aula Sobre Pequenas Cirurgias - Liga Acadêmica de Cirurgia e Anatomia - Universidade Estadual Do CearáDocument112 pagesAula Sobre Pequenas Cirurgias - Liga Acadêmica de Cirurgia e Anatomia - Universidade Estadual Do Cearáthomasnm100% (4)

- APS Sinais e SistemasDocument17 pagesAPS Sinais e SistemasFernando CezarPas encore d'évaluation

- Convolução de Sinais e SistemasDocument29 pagesConvolução de Sinais e SistemasludokellyPas encore d'évaluation

- Relatório Prática de Laboratório de Eletrônica Analógica.Document11 pagesRelatório Prática de Laboratório de Eletrônica Analógica.Rafael RodriguesPas encore d'évaluation

- EletromagnetismoDocument26 pagesEletromagnetismoEduardoPas encore d'évaluation

- Relatorio de Fisica 3 - Medida de Tensão Contínua - NILTONDocument8 pagesRelatorio de Fisica 3 - Medida de Tensão Contínua - NILTONAlexandre Carvalho BuenoPas encore d'évaluation

- Eletricidade e Magnetismo - Lista de Exercícios - VetoresDocument2 pagesEletricidade e Magnetismo - Lista de Exercícios - VetoresDarkArkangel2100% (1)

- Laboratório de Eletricidade Aplicada - Relatório 1 PDFDocument7 pagesLaboratório de Eletricidade Aplicada - Relatório 1 PDFAlinne AdleyPas encore d'évaluation

- Experimento 1 - Osciloscópio de Raios CatódicosDocument6 pagesExperimento 1 - Osciloscópio de Raios CatódicosMurilo Aguiar SilvaPas encore d'évaluation

- Quatro Aplicações Da Álgebra Linear Na EngenhariaDocument62 pagesQuatro Aplicações Da Álgebra Linear Na EngenhariaTaubamanPas encore d'évaluation

- Instrumentação Analógica e DigitalDocument10 pagesInstrumentação Analógica e DigitalMussage Virgilio SaidePas encore d'évaluation

- Cauê de Souza Coutinho Nogueira PDFDocument35 pagesCauê de Souza Coutinho Nogueira PDFAna Isabel Alves OsorioPas encore d'évaluation

- Relatório 08 - Potência em Corrente AlternadaDocument8 pagesRelatório 08 - Potência em Corrente AlternadaLarissa Rafaelly100% (1)

- Relatório - Termistores e Ponte de WheatstoneDocument10 pagesRelatório - Termistores e Ponte de WheatstoneJorge Messa JuniorPas encore d'évaluation

- Lista de Exercícios I ConversãoDocument11 pagesLista de Exercícios I ConversãoDeby NFerPas encore d'évaluation

- Físic 2 Acs 2020 PDFDocument20 pagesFísic 2 Acs 2020 PDFPedro Rafael Afonso AfonsoPas encore d'évaluation

- Transformada de LaplaceDocument25 pagesTransformada de Laplacechiutano jose joaoPas encore d'évaluation

- Problemas Sobre Quadripolos (2014)Document3 pagesProblemas Sobre Quadripolos (2014)Alberto Chicava SecoPas encore d'évaluation

- Cálculo Numérico Provas e Gabaritos - DCCUFRJDocument35 pagesCálculo Numérico Provas e Gabaritos - DCCUFRJJuracy SantanaPas encore d'évaluation

- Série de Fourier - APOSTILADocument41 pagesSérie de Fourier - APOSTILALuiz Alberto Dos SantosPas encore d'évaluation

- Apostila Mec Aplicada 2011Document232 pagesApostila Mec Aplicada 2011illedrat100% (1)

- Fisica 02 Dinamica Gravitacao Propostos PDFDocument104 pagesFisica 02 Dinamica Gravitacao Propostos PDFWendell Carlos0% (1)

- Trabalho Laboratorial Lançamento de ProjéteisDocument8 pagesTrabalho Laboratorial Lançamento de ProjéteisaffrodPas encore d'évaluation

- Lista 1 Convers o de EnergiaDocument21 pagesLista 1 Convers o de EnergiaLeonardo França100% (1)

- Eena A1 S2 PDFDocument46 pagesEena A1 S2 PDFJose DiasPas encore d'évaluation

- Aula 04 - Comandos Condicionais Simples e Compostos (If-Else-Switch)Document20 pagesAula 04 - Comandos Condicionais Simples e Compostos (If-Else-Switch)Acauan RibeiroPas encore d'évaluation

- Aula 1 - Medidas, Algarismos Significativos e ErrosDocument11 pagesAula 1 - Medidas, Algarismos Significativos e ErrosAtailson OliveiraPas encore d'évaluation

- Transdutores CapacitivosDocument24 pagesTransdutores CapacitivosaraujoPas encore d'évaluation

- Equações de Maxwell e Ondas EletromagnéticasDocument3 pagesEquações de Maxwell e Ondas EletromagnéticasmanelmrqPas encore d'évaluation

- 2 - Apostila Mecânica Técnica - ESTÁTICADocument74 pages2 - Apostila Mecânica Técnica - ESTÁTICAGirlaine De CarvalhoPas encore d'évaluation

- Aula de Fluxo MagnéticoDocument8 pagesAula de Fluxo Magnéticonicacio_89507470Pas encore d'évaluation

- Circuito MagnéticoDocument23 pagesCircuito MagnéticoAlex FerreiraPas encore d'évaluation

- Apostila de EletromagnetismoDocument109 pagesApostila de Eletromagnetismomagallanes36100% (2)

- Algoritmo Quantico de ShorDocument45 pagesAlgoritmo Quantico de ShorEuder RodriguesPas encore d'évaluation

- 3° Lista de CircuitosDocument5 pages3° Lista de CircuitosJayssa NobrePas encore d'évaluation

- Oscilador ControleAutomaticoGanhoDocument19 pagesOscilador ControleAutomaticoGanhoLuan C. Martins Dos SantosPas encore d'évaluation

- Exercícios - Pratos Paralelos e Guias RetangularesDocument6 pagesExercícios - Pratos Paralelos e Guias RetangularesAnderson SantosPas encore d'évaluation

- Princípios Da Conversão de EnergiaDocument81 pagesPrincípios Da Conversão de EnergiaLaura CamposPas encore d'évaluation

- Aula 09 - Papel LogaritmicoDocument4 pagesAula 09 - Papel LogaritmicoEduardo VieiraPas encore d'évaluation

- Lista 1 Cap21 Halliday Fis 270D Acervo DisciplinaDocument9 pagesLista 1 Cap21 Halliday Fis 270D Acervo DisciplinaAndre Rossetti100% (1)

- Descomplicando A Eletricidade:: Um Guia Básico para IniciantesDocument17 pagesDescomplicando A Eletricidade:: Um Guia Básico para IniciantesDouglas CordeiroPas encore d'évaluation

- Eletronica IIDocument102 pagesEletronica IILucas Ramos100% (1)

- Relatório Ladder - Lab 1 de AutomaçãoDocument18 pagesRelatório Ladder - Lab 1 de AutomaçãoORANGIIE100% (1)

- Manual de Analise de CircuitosDocument158 pagesManual de Analise de CircuitosGilberto Maguele100% (1)

- 4351 31.10.2016 10.35.17 Lista4CapacitanciaeDieletricosDocument2 pages4351 31.10.2016 10.35.17 Lista4CapacitanciaeDieletricosNágela IanePas encore d'évaluation

- Como Funciona Chuveiros Lampadas Fusiveis Potencia Instalacoes ResidenciaDocument28 pagesComo Funciona Chuveiros Lampadas Fusiveis Potencia Instalacoes ResidenciaGaston Eteban Farias Droguett100% (1)

- Retificadores de Meia Onda e Onda CompletaDocument13 pagesRetificadores de Meia Onda e Onda CompletaVinícius KrebsPas encore d'évaluation

- Aulas de Análise MatemáticaDocument396 pagesAulas de Análise MatemáticaRafa BenitezPas encore d'évaluation

- IV EletromagnetismoDocument16 pagesIV EletromagnetismoLucas BoneziPas encore d'évaluation

- Aula 01 Sequencias Sinais e Sistemas DiscretosDocument93 pagesAula 01 Sequencias Sinais e Sistemas DiscretosallanromarioPas encore d'évaluation

- Chuveiro EletricoDocument4 pagesChuveiro EletricohugofodaoPas encore d'évaluation

- ELE I 2008 2blkDocument81 pagesELE I 2008 2blkFelipe LimaPas encore d'évaluation

- Bateria De Gravidade: Convertendo energia gravitacional em eletricidadeD'EverandBateria De Gravidade: Convertendo energia gravitacional em eletricidadePas encore d'évaluation

- SopDocument49 pagesSopRafael CarvalhoPas encore d'évaluation

- MRP - MPSDocument77 pagesMRP - MPSRafael CarvalhoPas encore d'évaluation

- Supply ChainDocument15 pagesSupply ChainRafael CarvalhoPas encore d'évaluation

- Brainstorming - Análise de Causa e EfeitoDocument19 pagesBrainstorming - Análise de Causa e EfeitoRafael CarvalhoPas encore d'évaluation

- Leis de KirchhoffDocument4 pagesLeis de KirchhoffRafael CarvalhoPas encore d'évaluation

- Relatorio ModeloDocument10 pagesRelatorio ModeloRafael CarvalhoPas encore d'évaluation

- Lei de Newton e ViscosidadeDocument4 pagesLei de Newton e ViscosidadeFBASTOSEQ100% (1)

- Métodos de Separação de MisturasDocument16 pagesMétodos de Separação de MisturasAnlaue InsaPas encore d'évaluation

- Conceitos e Metodos V3 - BioquimicaDocument105 pagesConceitos e Metodos V3 - BioquimicaDanielle MariePas encore d'évaluation

- FISPQ - Aerosil 200Document6 pagesFISPQ - Aerosil 200Jana RodriguesPas encore d'évaluation

- Emergência QuímicaDocument187 pagesEmergência QuímicaSamária RochaPas encore d'évaluation

- Manual Do Usuario Humapen LuxuraDocument12 pagesManual Do Usuario Humapen LuxuraTiago Cardoso de SousaPas encore d'évaluation

- ArgiloterapiaDocument19 pagesArgiloterapiaAriana BeltramePas encore d'évaluation

- F Trab BiomoleculasDocument2 pagesF Trab BiomoleculasPaula LopesPas encore d'évaluation

- Formulas e Composicao - ExerciciosDocument4 pagesFormulas e Composicao - ExerciciosJanaina Leitinho100% (1)

- Isolamento Térmicos - 1 PDFDocument13 pagesIsolamento Térmicos - 1 PDFLuísPas encore d'évaluation

- SPERLING, 2005 - RBRH - Etimologia Aquática PDFDocument9 pagesSPERLING, 2005 - RBRH - Etimologia Aquática PDFLenise Nogueira SoaresPas encore d'évaluation

- 1-Materiais Cerâmicos - EstruturasDocument85 pages1-Materiais Cerâmicos - EstruturasAbimaelPas encore d'évaluation

- Apostila Particulados PDFDocument10 pagesApostila Particulados PDFJuliana TrindadePas encore d'évaluation

- Apostila TPCSVCDocument28 pagesApostila TPCSVCGil Coloia0% (1)

- Planner+iQui Mica+com+exerci Cios+-+extensivo+2021Document11 pagesPlanner+iQui Mica+com+exerci Cios+-+extensivo+2021Beatriz Lima ResendePas encore d'évaluation

- Pré Relatório 6 FQDocument14 pagesPré Relatório 6 FQGuilherme Bueno Pereira AfonsoPas encore d'évaluation

- Avaliação de Recuperação 8 SerieDocument4 pagesAvaliação de Recuperação 8 SerieMarcos Henrique QuerinPas encore d'évaluation

- Consumo de Oxigênio No ExercícioDocument28 pagesConsumo de Oxigênio No ExercícioArthur Sacramento100% (5)

- Definições de MAF e HWEDocument38 pagesDefinições de MAF e HWEAnaque PiresPas encore d'évaluation

- Avaliação Do 9º Ano A - Tabela e Ligações Químicas - 3º BimestreDocument1 pageAvaliação Do 9º Ano A - Tabela e Ligações Químicas - 3º BimestreMarina Cangussu Starling AmorimPas encore d'évaluation

- Vácuo em TransformadoresDocument1 pageVácuo em TransformadoresRodrigo Javier RomayPas encore d'évaluation

- Ligações Intermoleculares - Jogo de Partículas 10º CDocument3 pagesLigações Intermoleculares - Jogo de Partículas 10º CAna Raquel PintoPas encore d'évaluation

- Catálogo M500 2018Document8 pagesCatálogo M500 2018Marshall LimaPas encore d'évaluation

- D12 (1º Ano - L.P)Document21 pagesD12 (1º Ano - L.P)Deborah CostaPas encore d'évaluation

- Reforço de Estruturas de Concreto Com Chapas e Perfis de AçoDocument24 pagesReforço de Estruturas de Concreto Com Chapas e Perfis de Açomateus456Pas encore d'évaluation

- Catalogo TrancilDocument7 pagesCatalogo TrancilMauricioMartelliPas encore d'évaluation

- Fispq Inseticida Termimax Fipronil 250Document8 pagesFispq Inseticida Termimax Fipronil 250GleidianePas encore d'évaluation

- Impurezas Do PetroleoDocument8 pagesImpurezas Do PetroleoRodolfoPas encore d'évaluation