Académique Documents

Professionnel Documents

Culture Documents

Progettazione Di Elettronica Analogica

Transféré par

Tommaso CaldognettoTitre original

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

Progettazione Di Elettronica Analogica

Transféré par

Tommaso CaldognettoDroits d'auteur :

Formats disponibles

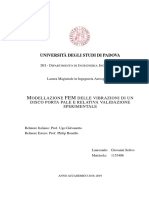

UNIVERSIT

`

A DI PADOVA

DIPARTIMENTO DI INGEGNERIA DELLINFORMAZIONE

CORSO DI LAUREA IN INGEGNERIA ELETTRONICA

Progettazione di Elettronica Analogica

Progetto:

Amplicatore in Classe AB con driver Optoisolato

Studenti:

Davide BIADENE

Tommaso CALDOGNETTO

Docente:

Prof. Leopoldo ROSSETTO

Anno Accademico 2011/2012

ii

Indice

Introduzione 1

1 Studio e Denizione della Struttura dellAmplicatore 5

1.1 Optoisolatori . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

1.2 Stadio di drive degli optoisolatori . . . . . . . . . . . . . . . . . . . . . . . . . 7

1.3 Stadio di uscita . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

1.4 Moltiplicatore di V

BE

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

1.5 Schema elettrico . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

2 Analisi e Primo Dimensionamento 17

2.1 Stadio optoisolatori . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

2.1.1 Dimensionamento resistenza di polarizzazione R

B

. . . . . . . . . . . . 17

2.1.2 Dimensionamento resistenza di polarizzazione R

FQ

. . . . . . . . . . . 18

2.1.3 Dimensionamento resistenza di segnale R

F

. . . . . . . . . . . . . . . 21

2.1.4 Diodi zener D

Z,p

e D

Z,n

. . . . . . . . . . . . . . . . . . . . . . . . . 23

2.2 Stadio di uscita . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

2.2.1 Caratteristica ingresso-uscita: scelta delle correnti in quiescenza . . . . 25

2.2.2 Comportamento in frequenza . . . . . . . . . . . . . . . . . . . . . . . 34

2.3 Stadio di ingresso e compensazione . . . . . . . . . . . . . . . . . . . . . . . 37

2.3.1 Compensazione dellamplicatore . . . . . . . . . . . . . . . . . . . . 38

2.3.2 Filtro di ingresso . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

2.4 Mantenimento in SOA dello stadio di uscita . . . . . . . . . . . . . . . . . . . 43

2.4.1 Tensione massima ai terminali dei transistor . . . . . . . . . . . . . . . 44

2.4.2 Corrente massima ai terminali dei transistor . . . . . . . . . . . . . . . 44

2.4.3 Temperatura dei transistor dello stadio di uscita . . . . . . . . . . . . . 45

2.5 Circuito di smaltimento del calore . . . . . . . . . . . . . . . . . . . . . . . . 47

2.5.1 Derivazione dello schema a blocchi delle interazioni termiche-elettriche 49

2.5.2 Considerazioni sulla scelta della resistenza R

E

. . . . . . . . . . . . . 50

2.5.3 Derivazione del circuito termico . . . . . . . . . . . . . . . . . . . . . 52

2.5.4 Simulazione degli aspetti termici . . . . . . . . . . . . . . . . . . . . . 54

2.6 Circuito moltiplicatore di V

BE

. . . . . . . . . . . . . . . . . . . . . . . . . . . 56

2.6.1 Analisi del circuito . . . . . . . . . . . . . . . . . . . . . . . . . . . . 56

2.6.2 Dimensionamento del circuito . . . . . . . . . . . . . . . . . . . . . . 58

3 Ottimizzazione & Risultati 61

3.1 Ottimizzazione . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 61

3.2 Misure sul circuito nale . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 68

3.2.1 Risposta al gradino di tensione . . . . . . . . . . . . . . . . . . . . . . 68

3.2.2 Risposta allonda quadra con bias . . . . . . . . . . . . . . . . . . . . 68

iii

3.2.3 Misura della distorsione armonica . . . . . . . . . . . . . . . . . . . . 70

3.2.4 Misura della massima escursione del segnale di uscita . . . . . . . . . 71

3.2.5 Verica del funzionamento del circuito di limite di corrente . . . . . . 73

3.2.6 Test in corto circuito . . . . . . . . . . . . . . . . . . . . . . . . . . . 73

3.2.7 Prova termica . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 74

3.3 Strumentazione impiegata . . . . . . . . . . . . . . . . . . . . . . . . . . . . 76

4 Conclusioni 77

A Cenni sulla Correzione di Errore 81

A.1 Descrizione della tecnica di correzione di errore alla Hawksford . . . . . . . . 81

A.2 Applicazioni valutate . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 83

B Resistenza Termica di Interfaccia 85

B.1 Modello termico di Antonetti e Yovanovich . . . . . . . . . . . . . . . . . . . 85

B.2 Riscontri applicativi . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 86

Bibliograa consultata . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 88

iv

Note Tecniche

La notazione adottata nella relazione ` e denita in gura I. Si impiegano:

- lettere minuscole con pedici maiuscoli per indicare grandezze istantanee,

- lettere maiuscole con pedici maiuscoli per indicare il valore DC di una grandezza e

- lettere minuscole con pedici minuscoli per indicare grandezze incrementali.

Figura I: Convenzioni sulla notazione

Per indicare il valore massimo assoluto di una generica grandezza v

X

sopportabile da un

dispositivo si utilizza la notazione:

v

Max

X

,

mentre per indicare il massimo valore che pu` o assumere nel funzionamento del circuito la

grandezza v

X

:

v

max

X

.

v

Introduzione

I

L PRESENTE DOCUMENTO ` e la relazione nale relativa alla progettazione di un circuito elet-

tronico svolta per il corso di Progettazione di Elettronica Analogica. Lo scopo che si propo-

ne ` e di descrivere le fasi che hanno portato dalle speciche assegnate alle misure sul prototipo

nale e insieme riportare quanto si ` e appreso dallattivit` a di progettazione e di test del sistema

che si ` e scelto di implementare.

Target di progetto. Il progetto riguarda un amplicatore in classe AB con driver optoisolato,

le cui speciche sono riportare in tabella 1.

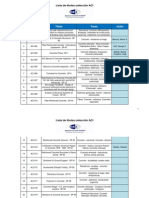

Tabella 1: Speciche Amplicatore in Classe AB con Driver Optoisolato

Parametro Simbolo Valore Unit` a

Corrente di uscita i

OUT

0500 mA

Tensione di uscita v

OUT

024 V

Tensione di ingresso v

IN

02.4 V

Banda passante B [0, 50] kHz

Dissipazione complessiva a riposo P

Q%

2.5 %

(1)

(1)

La dissipazione complessiva a riposo ` e indicata rispetto alla massima

potenza erogabile in uscita, corrispondente a v

Max

OUT

i

Max

OUT

.

Si evidenziano le seguenti particolarit` a:

X lamplicatore deve poter gestire anche segnali a frequenza nulla,

X la dissipazione totale in quiescenza, cio` e quando ` e applicato il segnale nullo in ingresso,

deve essere limitata entro il 2.5% della massima potenza erogabile in uscita,

X il guadagno dellamplicatore viene considerato pari a dieci, pari al rapporto tra il valore

massimo di tensione e di corrente in uscita.

Il processo di progettazione. Lapproccio alla progettazione che si ` e voluto adottare ` e quel-

lo che predilige lo studio dei problemi iniziando dalla loro analisi e passando poi, una volta

compresi i fenomeni coinvolti, al combinare le conoscenze acquisite al ne di determinare delle

adeguate soluzioni.

Seguendo lapproccio denito, con lattivit` a di progettazione svolta, si ` e delineato il usso

di progetto illustrato in gura 1. Nel diagramma si pu` o distinguere la peculiarit` a dellattivit` a di

progettazione, cio` e la sequenza di operazioni: studio-progettazione-sintesi-analisi.

1

2 INTRODUZIONE

S

t

u

d

i

o

P

r

o

g

e

t

t

a

z

i

o

n

e

S

i

n

t

e

s

i

A

n

a

l

i

s

i

Fase

Specifiche

Schemi a blocchi

Schemi a blocchi

Schemi di principio

Equazioni

Schemi elettrici

Schemi elettrici

Equazioni

Formule/Codice

Circuiti

(implementazione

reale o simulata)

Tipo di astrazione

Parte non

automatizzabile

Figura 1: Esempio di schematizzazione del metodo di progetto adottato

INTRODUZIONE 3

(a) Design represented as a feedback loop in which

the result is compared with the Specication, and di-

screpancies corrected by use of the analysis result in

reverse.

(b) The Design Process consists of smooth progress

from left to right in this Accuracy/Simplicity

trade-off picture. The Design feedback loop is

iterated until the Specications are met.

Figura 2: Rappresentazioni grache del signicato di Progettazione proposte da R.D. Middlebrook

[13]

Pi ` u nel dettaglio, il processo di progettazione tipicamente ha inizio con lo studio delle speci-

che e dellambito del progetto. Successivamente, dalla descrizione ad alto livello dellobiettivo

perseguito, nel processo si avanza circoscrivendo i problemi e quindi costruendo una possibile

struttura delle soluzioni. In questultima fase lelemento determinante ` e la capacit` a, propria del

progettista, di immaginare e poi rendere concreti possibili modi di procedere per risolvere le

problematiche individuate. Nondimeno, il progettista deve saper riconoscere la raggiungibilit` a

degli obiettivi, tenendo conto di limiti tecnici (e.g., rispetto ai materiali e alle tecnologie) ed

economici (e.g., rispetto al tempo e alle risorse).

Individuata una soluzione con la precedente fase, con la fase di sintesi la soluzione viene

denita in ogni suo aspetto, ed eventualmente completata, ottenendo un circuito assemblabile.

Il risultato ottenuto ` e quindi analizzato per vericare la rispondenza alle speciche iniziali.

Inne il processo studio-progettazione-sintesi-analisi viene iterato sulle imperfezioni riscontrate

dallanalisi del risultato ottenuto, no a giungere ad una realizzazione soddisfacente.

Rappresentazione secondo Middlebrook. In gura 2 ` e riportata la rappresentazione

intuitiva del processo appena descritto proposta dal Dr. Middlebrook [13].

Lillustrazione di gura 2a esprime il fatto che la progettazione si pu` o immaginare come un

sistema a retroazione. Nel percorso diretto si trova il blocco che rappresenta lanalisi, mentre

nel percorso di feedback si trova il blocco indicato con A N A L Y S I S , che rappresenta il processo di

progettazione e sintesi. Agli ingressi indicati con models and tentative values si possono

associare, per un confronto, ai risultati della fase di studio descritta nel paragrafo precedente.

In gura 2b si vuole rappresentare invece come evolve nel tempo il sistema di gura 2a.

Interpretando la gura 2b, si pu` o affermare che con la progettazione si inizia da idee e sche-

mi elementari di ci ` o che si vuole ottenere e poi, nel procedere, tali idee vengono sviluppate,

completate e perfezionate; il processo per evolvere richiede scelte, ognuna delle quali riduce i

gradi di libert` a a disposizione del progettista, giungendo a risultati sempre pi` u precisi e preoc-

cupandosi di problematiche sempre pi` u particolari. Parte dellattivit` a di progetto ` e anche quella

di riconoscere quando i risultati ottenuti sono soddisfacenti ed ` e perci ` o necessario portare a

termine il processo.

4 INTRODUZIONE

Sui modelli. La dualit` a tra lanalisi e la progettazione-sintesi e levoluzione dal generale al

particolare tipicamente si riette nei modelli impiegati durante il progetto. Con riferimento alla

gura 3, se lanalisi del circuito porta alla denizione di modelli via via di pi` u alto livello e

di validit` a generale, con la progettazione si inizia da rappresentazioni ad alto livello per poter

giungere, gradualmente, alla rappresentazione circuitale della rappresentazione ad alto livello

di partenza.

Circuito Schema Equazioni

Schema

a blocchi

Misure Specifiche

Progettazione

Analisi

Figura 3: Ordine delle rappresentazioni nei processi di analisi e di progettazione

Contenuto della relazione. I capitoli che seguono descrivono le principali attivit` a svolte nella

progettazione dellamplicatore:

X il capitolo 1 riassume le valutazioni e le scelte principali che hanno portato alla denizione

del circuito implementato;

X il capitolo 2 ` e dedicato allanalisi del circuito e alla descrizione dei criteri di

dimensionamento dello stesso;

X il capitolo 3 riporta le misure sul prototipo realizzato dellamplicatore e descrive le

modiche apportate al circuito per un miglioramento delle prestazioni sulla base delle

misurazioni effettuate;

X lappendice A fornisce dei cenni sullargomento correzione derrore e propone un paio

di applicazioni della tecnica sul sistema progettato;

X lappendice B riporta una modellizzazione dellimpedenza termica di interfaccia tra due

superci. Si ritiene questa permetta di assumere un conveniente punto di vista per consi-

derazioni applicative in merito allassemblaggio dei dispositivi al ne della dissipazione

termica.

Capitolo 1

Studio e Denizione della Struttura

dellAmplicatore

Dalle speciche assegnate si pu` o comporre uno schema di massima del sistema da sviluppare,

come in gura 1. La corretta impostazione dello sviluppo dei vari blocchi dipende dalla co-

noscenza delle peculiarit` a dei dispositivi che saranno impiegati e da valutazioni riguardanti le

criticit` a relative alle possibili soluzioni.

Il capitolo riassume le valutazioni e le scelte principali che hanno portato alla denizione del

circuito implementato. Oggetto delle valutazioni sono le parti che caratterizzano lapplicazione

assegnata. Sono descritti i tipi di optoisolatori disponibili, la tecnica di comando dei diodi degli

optoisolatori, delle topologie di stadio di uscita nelle quali siano introducibili gli optoisolatori,

e il circuito atto al controllo della polarizzazione in classe AB dello stadio di uscita.

Le valutazioni che seguono lo studio conducono alla scelta della struttura del circuito e,

inne, allo schema elettrico.

1.1 Optoisolatori

Un optoisolatore, o fotoaccoppiatore, ` e un dispositivo a due porte che ottiene lisolamento tra

la parta di ingresso e quella di uscita mediante limpiego di radiazioni ottiche per trasferire il

segnale elettrico di ingresso alluscita.

I produttori propongono diversi tipi di optoisolatori. In gura 2 sono riportate le tipologie

considerate, e pi` u comuni, di dispositivi optoisolatori. Esse sono accomunate dalla presen-

za di un dispositivo emettitore, tipicamente un diodo LED GaAs/AlGaAs (semiconduttori che

permettono un band-gap diretto), e da un fotoricevitore, cio` e un fotodiodo o un fototransistor.

Invece le tipologie si distinguono per aspetti quali, ad esempio, la velocit` a di risposta, la ru-

Stadio di

ingresso

Buffer/Drive

Stadio

optoisolatore

Rete di

retroazione

+

-

Uscita Ingresso

Stadio di

uscita

M

o

l

t

.

Figura 1: Schema a blocchi iniziale

5

6

CAPITOLO 1. STUDIO E DEFINIZIONE DELLA STRUTTURA

DELLAMPLIFICATORE

(a) Uscita fotodiodo (b) Uscita fototransistor

(c) Uscita Darlington (d) Uscita fotodiodo e HS transistor

Figura 2: Tipologie di optoisolatori

morosit` a e il current transfer ratio (CTR), cio` e il rapporto tra la corrente di uscita e quella di

ingresso. Per i casi in oggetto si ha che:

(a) il componente di gura 2a offre le prestazioni migliori in termini di velocit` a di risposta e

di rumore; lo svantaggio pi` u importante ` e il basso rapporto tra la corrente fornita in uscita

rispetto a quella iniettata in ingresso, tipicamente attorno a 0.2% [20];

(b) il componente di gura 2b presenta un ricevitore a fototransistor, che offre il vantaggio di

un maggiore CTR, tipicamente attorno a 50%, e pi` u elevate correnti di uscita rispetto al

ricevitore a fotodiodo. Rispetto al precedente risulta pi ` u lento, tipicamente quattro ordini

di grandezza pi` u lento, e pi ` u rumoroso [20]. Alcuni componenti presentano laccesso

alla base del fototransistor, consentendo un miglioramento delle prestazioni in termini

di velocit` a (laccesso alla base permette il drenaggio da parte del circuito esterno delle

cariche in eccesso, altrimenti eliminate solo per ricombinazione), ma lo svantaggio di

una maggiore cifra di rumore complessiva. Il funzionamento normale del dispositivo si

ottiene operando il transistor di uscita in zona attiva;

(c) il componente di gura 2c, realizzando una congurazione Darlington in uscita, accentua

i vantaggi e gli svantaggi del precedente di gura 2b. Un potenziale ulteriore svantaggio ` e

il fatto che adeguate polarizzazioni delluscita richiedono una tensione maggiore rispetto

al caso precedente;

(d) la congurazione di gura 2d combina le congurazioni di gura 2a e gura 2b per-

mettendo di ottenere dispositivi di buone caratteristiche in termini di velocit` a, CTR e

di corrente disponibile in uscita; spesso i produttori specicano il transistor di uscita di

carattere High-Speed per marcare la differenza con il caso di gura 2b.

1.2 Stadio di drive degli optoisolatori 7

+

+

+

+

+

(a) Esempio di amplicatore non optoisolato

+

+

+

+

+

(b) Esempio di amplicatore optoisolato

Figura 3: Effetto dellimpiego di optoisolatori

Evidenizati i pregi e i difetti dei tipi di dispositivi disponibili per lisolamento ottico,

al ne della scelta della congurazione ottimale si riporta lattenzione sullapplicazione. Con

riferimento alle speciche assegnate, loptoisolatore dovr` a essere impiegato per il comando di

qualche dispositivo dello stadio di uscita, il pi` u vicino possibile alluscita dellamplicatore.

`

E ragionevole aspettarsi che i dispositivi di uscita, essendo dispositivi di potenza, richiedano

robusti segnali di pilotaggio. Di conseguenza si pu` o pensare che gli optoisolatori verranno im-

piegati per comandare la corrente di ingresso di BJT in congurazione Darlington, ad esempio,

e non direttamente il transistor nale di potenza. In ogni caso saranno necessarie correnti di

comando dellordine delle frazioni di milli ampere, le quali non sono erogabili dai dispositivi

di gura 2a. Si potrebbe pensare di preamplicare le correnti di uscita dai dispositivi del tipo di

gura 2a, tuttavia in questo modo si introducono, con elevata probabilit` a, complicazioni proget-

tuali o risultati non soddisfacenti. Daltra parte, si ritiene opportuno evitare la congurazione di

gura 2c data la lentezza e le necessit` a di polarizzazione che la caratterizzano. A questo punto,

anche a seguito della consultazione dei cataloghi dei produttori, tra le congurazioni di gura

2b e di gura 2d si sceglie la seconda poich e disponibile con prestazioni migliori e costo simile.

Motivo dimpiego degli optoisolatori. Nellambito dellamplicatore in oggetto limpiego di

optoisolatori permette di separare i circuiti di ingresso e di uscita della catena di amplicazione.

Ci` o riduce lentit` a di alcune interazioni indesiderate, sia tra le due parti, sia dellamplicatore

intero con lambiente esterno. Tale affermazione si rafgura nellesempio proposto in gura 3:

limpiego degli optoisolatori interrompe il circuito diretto di amplicazione ed elimina la ma-

glia evidenziata con il tratteggio rosso in gura 3a, che pu` o accoppiare segnali dallesterno o

irradiare quelli processati dallamplicatore.

1.2 Stadio di drive degli optoisolatori

Il ruolo del circuito di comando degli optoisolatori ` e quello di iniettare nei diodi LEDdi ingresso

una corrente che ` e funzione solo del segnale di comando v

F

.

Ponendo di impiegare una struttura simmetrica con due optoisolatori, per il comando si ` e

scelto il circuito in gura 4. Lelevato guadagno degli operazionali per frequenze inferiori alla

frequenza di taglio, permette di considerare il nodo del morsetto invertente a massa virtuale,

ovvero un nodo di somma per le correnti. Cos`, la connessione mediante la resistenza R

F

del-

lingresso v

F

e mediante la resistenza R

FQ

della tensione di alimentazione produce la seguente

8

CAPITOLO 1. STUDIO E DEFINIZIONE DELLA STRUTTURA

DELLAMPLIFICATORE

Figura 4: Circuito di drive degli optoisolatori

corrente attraverso i diodi LED:

i

F,p

=

1

R

F

v

F

+

1

R

FQ

V

S

, (1.1)

i

F,n

=

1

R

F

v

F

+

1

R

FQ

V

S

, (1.2)

che, a meno di un termine costante, ` e proporzionale al segnale di comando v

F

. Il termine pro-

porzionale funge da corrente di polarizzazione per gli optoisolatori, i quali non operano come

da speciche nellintorno di corrente i

F

nulla. Utilizzando lo stadio di gura 5 la corrente diffe-

renziale di comando dello stadio di uscita aumenta o diminuisce concordemente allandamento

della tensione v

F

.

Un vantaggio offerto dallimpiego di un operazionale per il comando di ogni diodo ` e il fatto

di poter disporre del nodo di somma delle correnti, cos` da poter gestire in modo indipendente

la componente di segnale dalla componente di polarizzazione.

Inne si osserva che la banda del circuito di drive ` e elevata, approssimativamente pari alla

frequenza a guadagno unitario delloperazionale, poich e questultimo ` e in congurazione a re-

troazione unitaria quando un diodo ` e acceso. I diodi D

L

garantiscono la presenza di un percorso

tra uscita e morsetto invertente, anche nelleventualit` a che il diodo D

E

venga contropolarizzato

e, se questo ` e il caso, limita la tensione di contropolarizzazione a valori sicuri per i LED degli

optoisolatori.

1.3 Stadio di uscita

Esistono diverse topologie di stadi di uscita, alcune si trovano descritte in testi quali i titoli [3]

e [18] della bibliograa, altre, diverse, sono suggerite dai manuali [2].

Qui, per la denizione della topologia, si ` e considerata la necessit` a di realizzare il comando

isolato dello stadio di uscita come indicato dalle speciche. Lobiettivo ` e quindi il comando

dello stadio di uscita impiegando dispositivi optoisolatori inseriti pi` u a valle possibile nella

catena di amplicazione, cio` e vicini ai nali di potenza.

Tenendo conto delle limitazioni dei dispositivi, le due topologie sulle quali ci si ` e

maggiormente soffermati sono quelle illustrate in gura 5.

Nella topologia di gura 5a gli optoisolatori operano in maniera opposta rispetto ai nali

di potenza. Essi sono comandati in modo complementare e a riposo sono entrambi percorsi

1.3 Stadio di uscita 9

(a) Current driven output stage (b) Voltage driven output stage

Figura 5: Stadi di uscita optoisolati

da una corrente di polarizzazione. Quindi, in risposta ad un segnale che tende ad aumentare

il segnale di uscita, loptoisolatore del ramo opposto rispetto a quello che deve aumentare la

corrente erogata alluscita, cio` e loptoisolatore del ramo negativo, aumenta la sua conducibilit` a

riducendo la tensione di comando del relativo transistor di uscita, cio` e Q

O,n

, mentre laltro

optoisolatore, cio` e quello del ramo positivo, riduce la sua conducibilit` a con leffetto di deviare

la corrente I

B

verso la base del relativo dispositivo di uscita, cio` e Q

O,p

. Si ha linverso nel caso

di riduzione della tensione di uscita.

La congurazione descritta presenta alcune caratteristiche non favorevoli. Uno svantaggio

` e la necessit` a di regolare la corrente di riposo che scorre negli optoisolatori. In particolare, nel

caso in cui la corrente di riposo degli optoisolatori non sia sufcientemente elevata, lo stadio

di uscita non pu` o erogare la massima corrente denita dalle speciche. Invece, se la corrente

di riposo che attraversa gli optoisolatori ` e eccessiva, allora esiste un intervallo del segnale di

comando degli optoisolatori nellintorno di zero entro il quale il movimento dellingresso non

causa il movimento delluscita. Un ulteriore svantaggio ` e il fatto che la tensione ai capi dello

stadio di uscita delloptoisolatore non pu` o essere costante poich e deve variare assieme al se-

gnale prodotto dallamplicatore ed il suo valore dipende dalla tensione tra base ed emettitore

dei transistor. Invece, il funzionamento lineare e ottimale del componente optoisolatore, in ter-

mini di invarianza del CTR e di velocit` a, avviene se tale tensione ` e sufcientemente elevata e

costante.

Passando a considerare la topologia di gura 5b, in questa gli optoisolatori sono disposti in

modo da realizzare, assieme ai generatori di corrente I

B

, dei generatori di corrente comandati dal

segnale di ingresso. I due optoisolatori sono comandati in modo complementare e a riposo en-

trambi possono essere percorsi da una corrente di polarizzazione. In termini di funzionamento,

la congurazione, in risposta ad un segnale che tende ad aumentare il segnale di uscita, aumenta

la corrente erogata dalloptoisolatore del ramo positivo e si riduce quella assorbita dal ramo ne-

gativo. (Viceversa per il caso di riduzione della tensione di uscita.) La conseguente differenza

di corrente si chiude nellimpedenza al nodo di ingresso dello stadio di uscita realizzando cos`

il comando in tensione per lingresso allo stadio inseguitore di emettitore.

Questa topologia presenta lo svantaggio, simile a quello evidenziato per il caso di gura 5a,

10

CAPITOLO 1. STUDIO E DEFINIZIONE DELLA STRUTTURA

DELLAMPLIFICATORE

di avere un modo di funzionamento dipendente dalle correnti di polarizzazione (come descritto

in maggior dettaglio nel paragrafo 2.1.1). Daltra parte, presenta alcuni vantaggi rispetto alla

congurazione precedente. Infatti nella congurazione di gura 5b in primo luogo ` e possibi-

le ssare la tensione ai capi della sezione di uscita delloptoisolatore al ne di ottimizzarne il

funzionamento, in secondo luogo le condizioni di polarizzazione, o il soddisfacimento di condi-

zioni sulla massima potenza dissipabile a riposo, qui non introducono limitazioni sulla massima

corrente che si pu` o scambiare al nodo di uscita dellamplicatore.

Per quanto esposto, fra le due topologie si ` e preferita quella di gura 5b.

Scelta dei dispositivi di uscita. Nella trattazione della sezione 1.1 si ` e proposto come esempio

limpiego di dispositivi BJT per realizzare lo stadio di uscita. Una alternativa potrebbero invece

essere dispositivi in tecnologia MOS [3]. Di seguito si valutano alcuni degli aspetti di cui si pu` o

tener conto al ne della scelta della tecnologia dei transistor, per valutarne la validit` a.

I dispositivi MOS rispetto ai BJT:

+ presentano guadagno di corrente continua innito, per effetto della struttura MOS, dal

gate;

- presentano tensione di soglia circa pari a 3.5V;

- presentano transconduttanza minore (circa 5 volte minore);

+/- presentano maggiore frequenza di taglio f

T

:

MOSFET: f

MOS

T

=

1

2

g

m

C

gs

+C

gd

+C

gb

, BJT: f

BJT

T

=

1

2

g

m

C

+C

, (1.3)

e tendenza a sviluppare oscillazioni in alta frequenza, a causa della struttura a celle del

dispositivo di potenza;

- sebbene siano noti come dispositivi a coefciente di temperatura negativo, evidenziando

un comportamento resistivo in zona triodo (R

DS

(ON)

aumenta allaumentare della tempe-

ratura), per basse correnti di uscita il coefciente di temperatura negativo della tensione

di soglia provoca, a tensione V

GS

costante, un aumento della corrente di drain a fronte di

un aumento della temperatura (ad esempio, il dispositivo NDF06N60Z 600V/5A presenta

V

GS

/T 4.8mV/

C @ I

D

= 2A);

+ non presentano il fenomeno del breakdown secondario;

- possono richiedere correnti di pilotaggio impulsive per effetto della capacit` a equivalente

di gate.

Lapplicazione in oggetto non richiede la gestione di elevate potenze, invece ` e necessario un

buon controllo del punto di lavoro dello stadio di uscita, per soddisfare la specica sulla massi-

ma dissipazione a riposo, ed ` e favorevole impiegare dispositivi con bassa tensione di soglia, per

non ridurre lestensione dellintervallo di tensioni ottenibili di uscita.

Tali motivi giusticano la preferenza verso dispositivi BJT piuttosto che MOSFET.

1.4 Moltiplicatore di V

BE

11

(a) (b) (c) (d)

Figura 6: Stadi moltiplicatore di V

BE

1.4 Moltiplicatore di V

BE

Un circuito moltiplicatore di V

BE

` e un regolatore di tensione di tipo shunt che ` e in grado di

generare una tensione proporzionale alla tensione v

BE

di uno o pi` u transistor impiegati nel

circuito.

Dalla letteratura si posso ricavare diverse topologie di moltiplicatore, che spaziano da con-

gurazioni semplici, come quelle riportate in [17], no ad arrivare a soluzioni pi ` u complesse,

come quelle descritte in [6], e riportate in appendice A, dove si utilizza il medesimo circuito

per effettuare una correzione derrore sul segnale duscita. Come prima analisi, si predilige lo

studio delle topologie elementari di gura 6, per le quali la complessit` a circuitale ` e ridotta ed ` e

possibile ottenere espressioni in forma chiusa al ne della loro ottimizzazione.

I circuiti di gura 6 sono accomunati dalla presenza di un primo ramo, composto dalle

resistenze R

1

e R

2

, che deniscono il fattore moltiplicativo, e da un secondo ramo nel quale

si trovano i transistor Q

1

e Q

2

, che forniscono la tensione v

BE

di riferimento. Indichiamo tali

transistor come transistor di riferimento, per il loro ruolo di denire la tensione di riferimento

a cui ` e proporzionale la tensione generata dal moltiplicatore.

Il principio di funzionamento del circuito si basa sul fatto che la corrente i

R

2

sulla resistenza

R

2

` e determinata unicamente dalla tensione v

BE

del transistor di riferimento (o dalla tensione

ai capi della serie delle giunzioni B-E, nel caso di pi` u transistor). Considerando trascurabile la

corrente assorbita in base ai transistor, la corrente i

R

2

corrisponde a quella sulla resistenza R

1

,

dando origine, ai capi del moltiplicatore di V

BE

, a una tensione che ` e combinazione lineare delle

v

BE

dei transistor di riferimento. La differenza tra corrente di polarizzazione I

B

e quella sulle

resistenze si richiude attraverso gli altri rami di cui ` e composto il moltiplicatore.

Supponendo che la corrente di polarizzazione I

B

sia costante, si ha che il transistor di ri-

ferimento ` e percorso da una corrente costante. Cos`, noto dalle caratteristiche v

BE

i

C

dei

BJT che la tensione v

BE

decresce al tasso di 2 2.5mV/

C, si ottiene che la tensione gene-

rata dal moltiplicatore decresce linearmente allaumentare della temperatura dei transistor di

riferimento.

La dipendenza descritta dalla temperatura ` e utilizzata per assicurare la stabilit` a termica dei

dispositivi di potenza, scongiurando il vericarsi del fenomeno di fuga termica, che tipicamente

12

CAPITOLO 1. STUDIO E DEFINIZIONE DELLA STRUTTURA

DELLAMPLIFICATORE

0

T/2

T

0 T/2 T

Ingresso

sinusoidale

Punto

operativo

Caratteristica di

trasferimento V-V

dispositivo di uscita

Regione di cutoff

dispositivo di uscita

Segnale

di uscita

Tempo

Tempo

Input

Output

AB

B

A

Figura 7: Andamenti qualitativi ingresso-uscita per la polarizzazione in classe AB. Per un confronto,

sono anche riportati gli eventuali punti di polarizzazione nelle classi A e B

ha effetti rovinosi sui dispositivi di uscita. Questo fenomeno viene innescato dalla dissipazione

di potenza nei transistor, la quale comporta un aumento della temperatura di giunzione, deter-

minando a sua volta un incremento della corrente di collettore e quindi della potenza dissipata.

Si evidenzia una retroazione rigenerativa che, se non gestita adeguatamente, porta alla rottura

dei dispositivi duscita. Ad alte temperature e alte correnti, la giunzione viene particolarmente

stressata poich e la corrente non si distribuisce uniformemente su tutta la supercie della giun-

zione, ma tende a concentrarsi nelle aree dove la resistenza risulta minore, cio` e la temperatura

maggiore, no a causare fusioni parziali del semiconduttore che compromettono il dispositivo.

Il fenomeno che si manifesta nel caso estremo ` e denominato breakdown secondario.

In questo senso il moltiplicatore di V

BE

pu` o presentare una valida soluzione alla polariz-

zazione degli stadi duscita di amplicatori in classe AB, per i quali il punto di lavoro dei

transistor ` e caratterizzato da una corrente di quiescenza non nulla, come illustrato nella gura

7. Accoppiando termicamente e in modo opportuno i transistor di riferimento con quelli du-

scita si pu` o introdurre una retroazione negativa nella catena dei fenomeni termici, poich e un

aumento della temperatura genera una diminuzione della tensione ai capi del moltiplicatore,

con conseguente diminuzione della tensione v

BE

dei transistor duscita che, se di entit` a supe-

riore al contributo della retroazione positiva, produce addirittura una sovracompensazione che

porta alla diminuzione della corrente di collettore.

Da queste considerazioni, il moltiplicatore di V

BE

pu` o essere rappresentato come un ge-

neratore di tensione V

BB

dipendente dalla temperatura al quale viene associata una resistenza

serie R

B

che tiene conto delle variazioni di tensione dovute alle variazioni della corrente di

polarizzazione I

B

, modello impiegato in gura 5.

Al ne della scelta della topologia del moltiplicatore, i parametri discriminanti sono la pos-

sibilit` a di regolare agevolmente la tensione di riposo, di regolare il suo gradiente rispetto

alla temperatura, di effettuare un sensing termico su tutti i dispositivi a rischio di fuga termica

e di disporre di resistenza serie R

B

bassa cos` che lo stadio duscita non venga sollecitato da

variazioni della corrente di polarizzazione del moltiplicatore.

Ispezionando gli schemi di gura 6 si possono trarre le seguenti conclusioni:

(a) il circuito di gura 6a non permette il sensing della temperatura di entrambi i dispositivi

1.5 Schema elettrico 13

duscita separatamente, costringendo, per una congurazione simmetrica, la collocazione

del sensing sul dissipatore. Laccoppiamento termico cos` realizzato potrebbe non ga-

rantire un tempo di risposta del sistema basato su moltiplicatore di V

BE

sufcientemente

rapido da proteggere i dispositivi nel caso peggiore (per il quale solo un ramo duscita ` e

in conduzione) a causa dalla elevata capacit` a termica del dissipatore. Oltretutto in questo

circuito non ` e possibile una regolazione indipendente del valore di tensione V

BB

dal suo

gradiente rispetto alla temperatura;

(b) rispetto alla precedente, nella topologia di gura 6b, la presenza dei due transistor di rife-

rimento, Q

1

e Q

2

, permette di gestire indipendentemente il sensing delle temperature dei

due dispositivi duscita. Questo tipo di circuito presenta comunque una resistenza serie

dellordine delle centinaia di ohm, il che potrebbe compromettere la polarizzazione dello

stadio di uscita nel caso si vericassero delle variazioni nella corrente di polarizzazione

I

B

. Anche questa congurazione non risolve la gestione separata tra la tensione V

BB

e il

suo gradiente rispetto alla temperatura;

(c) nel circuito di gura 6c, lunica differenza che si nota con lo schema di gura 6b ` e lesi-

stenza di un terzo ramo contenente un altro transistor, Q

3

, che non svolge per` o la funzione

di sensing n e di riferimento. Questa congurazione permette di gestire separatamente la

corrente di polarizzazione dei transistor Q

1

e Q

2

rispetto a Q

3

mediante la resistenza R

3

.

In questo modo ` e possibile creare un percorso alternativo alla corrente di polarizzazione

a pi ` u bassa impedenza e avere unamplicazione della reazione di Q

1

e Q

2

alle variazioni

di V

BB

, raggiungendo cos` una resistenza serie equivalente sulle decine di ohm;

(d) lultima congurazione, in gura 6d, offre tutti i vantaggi del circuito 6c, ma la presenza

del generatore di tensione V

D

introduce un grado di libert` a in pi ` u nella determinazione

delle resistenze, rendendo possibile la gestione separata della tensione V

BB

rispetto al suo

gradiente in temperatura.

Per quanto descritto, la scelta del circuito moltiplicatore di V

BE

ricade sulla congurazione

di gura 6d.

1.5 Schema elettrico

Alla luce delle valutazioni riassunte nei paragra precedenti, con il progetto del sistema

assegnato si ` e prodotto lo schema elettrico riportato in gura 8.

Nel circuito si distinguono le seguenti parti:

X stadio di ingresso, ha la funzione di ltrare i segnali forniti allingresso dellamplicatore

e di operare il controllo della tensione di uscita;

X stadio optoisolatori, ` e composto dalle sottoparti:

stadio di drive degli optoisolatori, ha la funzione di comandare i diodi LED degli

optoisolatori afnch e la corrente che li attraversa sia proporzionale al segnale di

comando v

F

;

stadio optoisolatore, realizza la separazione ottica chiesta dalle speciche;

stadio di polarizzazione e di buffering, permette la corretta polarizzazione dello sta-

dio di uscita degli optoisolatori e di realizzare un buffer per la corrente di uscita

degli optoisolatori;

14

CAPITOLO 1. STUDIO E DEFINIZIONE DELLA STRUTTURA

DELLAMPLIFICATORE

X stadio di polarizzazione dello stadio di uscita, costituito da un circuito moltiplicatore di

V

BE

, ha la funzione di mantenere la polarizzazione dello stadio di uscita in classe AB

anche a fronte di variazioni della temperatura operativa dei transistor di uscita;

X stadio di uscita, ha la funzione di amplicare in corrente il segnale fornito dallo stadio

optoisolatore per lalimentazione del carico collegato ai morsetti di uscita;

X rete di retroazione, ha la funzione di sentire la tensione di uscita v

OUT

, che ` e la grandezza

controllata dal sistema.

I componenti per i quali si ` e effettuata una ricerca specica sui cataloghi dei fornitori sono:

X gli optoisolatori, si sono scelti il tipo e il modello di dispositivi che dalla consultazione

dei cataloghi si sono presentati pi ` u adeguati allapplicazione, come descritto nella sezione

1.1;

X i transistor nali di potenza e i transistor di drive, per i quali si ` e vericato che le tensioni,

le correnti e le potenze massime che si possono levare durante il funzionamento fossero

inferiori ai valori massimi assoluti; nelle scelte si sono preferiti dispositivi per i quali

fosse disponibile una buona documentazione e indirizzata al tipo di applicazione lineare

in oggetto;

X il dissipatore, si ` e cercato un dissipatore di resistenza termica non superiore a

quella determinata in fase di dimensionamento, di forma adeguata al metodo di

prototipazione/assemblaggio adottato e di costo contenuto;

X gli amplicatori operazionali, si sono consultati alcuni databook, come, ad esempio, il

titolo [2] della bibliograa, al ne di individuare i dispositivi adatti allapplicazione in

termini di GBWP, correnti erogabili in uscita, range di tensioni di alimentazioni e di

uscita, slew-rate e rumore.

I componenti scelti sono indicati in tabella 1.1.

Il prossimo capitolo ` e dedicato allanalisi e al dimensionamento del circuito in gura 8.

Tabella 1.1: Principali componenti attivi scelti per il progetto

Componente Sigla

Optoisolatore HCNW4562

Transistor di potenza NPN/PNP MJE15030/MJE15031

Transistor di segnale (per il drive) NPN/PNP MPS8099/MPS8599

Amplicatore operazionale TL081

1.5 Schema elettrico 15

F

i

g

u

r

a

8

:

S

c

h

e

m

a

d

e

l

c

i

r

c

u

i

t

o

A

m

p

l

i

c

a

t

o

r

e

i

n

C

l

a

s

s

e

A

B

O

p

t

o

i

s

o

l

a

t

o

16

CAPITOLO 1. STUDIO E DEFINIZIONE DELLA STRUTTURA

DELLAMPLIFICATORE

Capitolo 2

Analisi e Primo Dimensionamento

Il capitolo ` e dedicato alla descrizione, al dimensionamento e allanalisi delle sezioni circuita-

li di cui lamplicatore in gura 8 ` e composto. Lanalisi ` e rivolta alla determinazione delle

relazioni utili al ne del progetto. Alcune analisi permettono di ricavare le formule da impie-

gare nella fase di dimensionamento del circuito, altre di ricavare delle relazioni che forniscono

dellinformazione utile allo steering delle scelte di progetto.

2.1 Stadio optoisolatori

In questa sezione si analizzano le relazioni tra i parametri che determinano il funzionamento e

le prestazioni dello stadio costituito dagli optoisolatori e dal circuito di comando dello stadio di

uscita. Il ne ` e quello di:

X determinare i valori delle resistenze R

FQ

di polarizzazione dei diodi LED degli

optoisolatori,

X determinare i valori delle resistenze R

F

mediante le quali viene costruito il segnale di

corrente che scorre attraverso i diodi LED,

X determinare i valori delle resistenze di polarizzazione R

B

che determinano la corren-

te di polarizzazione a riposo del moltiplicatore di V

BE

assieme allo stadio di comando

delluscita.

2.1.1 Dimensionamento resistenza di polarizzazione R

B

Deniamo I

BQ

la corrente di quiescenza che percorre il moltiplicatore di V

BE

. Mediante le

scelte di R

B

ed R

FQ

si intende imporre la corrente I

BQ

afnch e sia garantito il funzionamento

del moltiplicatore di V

BE

e ridotto limpatto sulla dissipazione in quiescenza

I

.

A tal ne si osserva che la corrente di polarizzazione del moltiplicatore di V

BE

si pu` o

scomporre nelle due componenti I

BQ,opto

e I

BQ,res

, cio` e:

I

BQ

= I

BQ,res

+I

BQ,opto

. (2.1)

Per una prima analisi si pu` o approssimare che lo stadio a base comune realizzato dai transi-

stor Q

C

presenti una resistenza di ingresso trascurabile. Questa approssimazione consente di

ricavare mediante un calcolo diretto le correnti I

BQ,res

e I

BQ,opto

:

I

BQ,res

=

V

Z

V

BE

Q

C

R

B

, (2.2)

17

18 CAPITOLO 2. ANALISI E PRIMO DIMENSIONAMENTO

I

BQ,opto

=CTR I

FQ

. (2.3)

Dalla equazione (2.2) si osserva che I

BQ,res

risulta ben determinata poich e dipende dal riferi-

mento di tensione V

Z

, da una tensione V

BE

e dalla resistenza R

B

; mentre dalla (2.3) risulta che

I

BQ,opto

non ` e ben determinata a causa della dipendenza dal parametro CTR, che ` e fortemente

variabile.

1

Data la topologia, risulta che ` e possibile ottenere il controllo su I

BQ

rendendo tra-

scurabile il contributo variabile I

BQ,opto

. In particolare si ` e scelto di assegnare lintera corrente

minima che garantisce il funzionamento del moltiplicatore di V

BE

alla componente poco va-

riabile I

BQ,res

, mentre assegnare a I

BQ,opto

una corrente che, anche se non ben determinata, sia

piccola rispetto a I

BQ

e abbia poco peso nel

I

.

2

Dimensionamento della resistenza R

B

Seguendo lapproccio descritto si ottiene subito lespressione della corrente I

BQ,res

e di

conseguenza il corrispondente valore di R

B

:

I

BQ,res

=

V

Z

V

BE

Q

C

R

B

= I

max

BQ

R

B

=

5V0.65V

1mA

4.35k R

B

= 4.7k .

(2.4)

Per quanto riguarda la corrente I

B,opto

nel seguito si valuta quale valore ` e conveniente

assegnare mediante unanalisi pi` u attenta del circuito.

2.1.2 Dimensionamento resistenza di polarizzazione R

FQ

.

Introdurre una corrente di polarizzazione costante nei diodi degli optoisolatori ` e necessario

per non avere dei buchi di amplicazione e forti variazioni delle prestazioni del componente

nel processamento di segnali ampi che occupano un range operativo per i

F

che comprende lo

zero. Tuttavia le speciche date sul massimo consumo a riposo rendono difcile garantire la

polarizzazione delloptoisolatore afnch e possa sempre lavorare ai piccoli segnali, cio` e con

correnti i

F

<< I

FQ

.

Un altro aspetto da evidenziare ` e che la corrente iniettata al nodo B ` e il contributo della

corrente del ramo positivo sommato al contributo del ramo negativo quando |i

F

| < |I

FQ

|, men-

tre ` e il contributo di uno solo dei due rami nel caso complementare. Di conseguenza emerge

una distorsione dovuta alla variazione del guadagno in funzione dellampiezza del segnale da

amplicare che ` e intrinseca nel modo di funzionamento del circuito, cio` e che permane anche se

i componenti fossero ideali.

Inoltre, se i componenti non fossero ideali, con la semplicazione di assumere il nodo B ad

alta impedenza, allora gli inevitabili sbilanciamenti tra i dispositivi del ramo positivo e negativo

portano, in presenza del controllo, ad uno sbilanciamento delle effettive correnti di polariz-

zazione I

FQ

, ora diverse per i due dispositivi, complicando il modo di denire le condizioni

da soddisfare per avere un funzionamento non affetto dal dimezzamento del guadagno appena

evidenziato.

Risulta quindi interessante comprendere gli effetti delle scelte di I

FQ

sui modi di funzio-

namento del circuito per valutare come e se ` e possibile ottenere un funzionamento che non

introduca distorsioni.

1

Il current transfer ratio di un optoisolatore standard pu` o variare da 80% a 600% del valore nominale (e.g.,

NEC PS2501-1), mentre optoisolatori pi` u accurati presentano una variazione da 80% a 120% del valore nominale

(e.g., Avago HCPL-4562).

2

[...] working on the trusty engineering principle that what cannot be controlled must be made irrelevant cit.

Douglas Self

2.1 Stadio optoisolatori 19

Figura 1: Regioni di funzionamento nel comando dei diodi LED

Analisi preliminare

Con lanalisi del circuito in oggetto, si giunge alla relazione:

i

F,eq

(v

F

) =

_

v

F

R

F

+I

FQ

_

(v

F

+I

FQ

R

F

) +

_

v

F

R

F

I

FQ

_

(v

F

+I

FQ

R

F

) (2.5)

dove i

F,eq

` e la corrente equivalente che scorrerebbe allingresso di un optoisolatore ideale bi-

polare e ` e il segnale gradino unitario. Per ispezione della (2.5) di osserva che nellintorno

di zero (|v

in

| < I

FQ

R

F

) il guadagno al piccolo segnale, se I

FQ

= 0, ` e doppio rispetto al caso

|v

in

| > I

FQ

R

F

. Tale comportamento ` e fonte di distorsione.

`

E possibile eliminare la dipendenza evidenziata del guadagno i

F,eq

/v

F

dal livello del segnale

v

F

ponendo:

{|v

F

(t)| < I

FQ

R

F

, t} EXOR {|v

F

(t)| > I

FQ

R

F

, t} . (2.6)

Da questo punto di vista ` e utile osservare che, in prima approssimazione, la massima cor-

rente fornita in uscita dallamplicatore ` e di 0.5A. Supponendo lo stadio Darlington di uscita

con guadagno di corrente (minimo) di

c

= 100 40 = 4000, si ha che la coppia di optoisolatori

devono fornire al nodo B uno sbilanciamento di corrente di circa I

max

out

/

c

= 125A, cio` e, sup-

posto di operare nella regione |v

F

| < I

FQ

R

F

, ciascuno deve variare la sua corrente di uscita di

65A.

Scelta della resistenza R

FQ

Nel primo tentativo di raggiungere la situazione corrispondente alla prima condizione della

(2.6) si impone un vincolo sulla massima variazione consentita della corrente I

B

. Si pone che

I

B

<3/2I

min

B

, cio` e che I

B

non aumenti, in alcuna condizione, pi ` u del 50% del suo valore minimo,

che corrisponde ad un margine di circa il 10% sulla massima corrente totale in quiescenza.

Questo modo di procedere concede anche del margine per garantire il corretto funzionamento

del moltiplicatore di V

BE

.

In questo modo si ha che:

I

BQ

_

1+

1

2

_

I

min

BQ

= I

BQ,res

+I

max

BQ,opto

, (2.7)

20 CAPITOLO 2. ANALISI E PRIMO DIMENSIONAMENTO

cio` e:

I

BQ,res

+CTR

max

I

FQ

|

CRT

max

=62%

=

3

2

I

min

BQ

I

FQ

=

1.5mA1mA

0.62

800A. (2.8)

Inne, considerando la tensione di alimentazione dello stadio di ingresso si ha:

R

FQ

=

V

S

I

FQ

=

12V

800A

= 15k R

FQ

= 15k . (2.9)

Con R

FQ

= 15k si pu` o calcolare il valore minimo della corrente I

B,opto

:

I

min

BQ,opto

= I

FQ

CTR

min

= 800A 0.19 = 152A. (2.10)

Quindi, con riferimento alla gura 1, si pu` o affermare che almeno in situazioni statiche la

regione operativa utilizzata ` e la 1 .

Effetti delle non simmetrie

I calcoli nora eseguiti suppongono gli optoisolatori identici. Il seguente procedimento consen-

te di tener conto del valore assoluto del CTR del singolo optoisolatore e della differenza tra i

CTR dei due optoisolatori.

Anzitutto deniamo le seguenti quantit` a:

X Current transfer ratio medio:

K =

CTR

P

+CTR

N

2

; (2.11)

X Rapporto tra i current transfer ratio degli optoisolatori:

=

CTR

P

CTR

N

. (2.12)

Dalle denizioni segue che:

CTR

P

=

2K

1+

, CTR

N

=

2K

1+

. (2.13)

La retroazione tende a far valere, nel range operativo di interesse, le seguenti:

_

I

BQ

+

V

F

R

F

_

CTR

P

=

_

I

BQ

V

F

R

F

_

CTR

N

,

V

F

R

F

=

1

1+

I

FQ

, (2.14)

e afnch e la regione operativa sia la 1 si deve avere che:

V

F

R

F

i

out

o

2K

< I

FQ

1

1+

I

FQ

+

i

out

o

2K

< I

FQ

, (2.15)

cio` e accade che:

I

FQ

max

_

|i

out

|

2

D

O

CTR

P

,

|i

out

|

2

D

O

CTR

N

_

(2.16)

ottenendo una condizione sul minimo valore di I

FQ

. Il caso peggiore, per il quale la corrente I

FQ

che soddisfa la (2.15) ` e massima, si verica con massima non simmetria tra i due optoisolatori

e massima corrente di uscita. In questa situazione la corrente a riposo sul diodo delloptoi-

solatore con maggior CTR risulta ridotta rispetto al valore teorico di I

FQ

che si ha in assenza

di mismatch, e si riduce ulteriormente in condizioni di carico che portano ad un aumento di

corrente per loptoisolatore del ramo opposto, con minor CTR.

Numericamente, con il valore I

FQ

= 800A determinato precedentemente porta a lavorare

nella regione 1 per correnti di uscita non superiori a 1.15A, considerando CTR

min

= 0.18,

CTR

max

= 1.125 e = 6.25.

2.1 Stadio optoisolatori 21

2.1.3 Dimensionamento resistenza di segnale R

F

La scelta del valore della resistenza R

F

determina il guadagno al piccolo segnale v

b

/v

f

e, assie-

me al limite imposto dalla saturazione degli operazionali, un limite sullo slew rate ottenibile al

punto B.

In particolare, sia il guadagno al piccolo segnale rispetto al punto F sia lo slew rate al nodo

B sono inversamente proporzionali al valore della resistenza R

F

, infatti:

v

out

v

in

=

1

R

F

G

in

(s)CRT(s)

R

BB

1+sR

BB

C

BB

G

o

(s), (2.17)

dove:

X G

in

` e la funzione di trasferimento tra il segnale di ingresso v

in

ed il segnale presente al

punto F;

X CRT ` e la funzione di trasferimento tra la corrente i

f

e la corrente i

b

iniettata al nodo B;

X R

BB

` e la resistenza equivalente verso massa vista dal nodo B;

X C

BB

` e la capacit` a equivalente verso massa vista dal nodo B;

X G

o

` e la funzione di trasferimento v

out

/v

b

tra lingresso e luscita dello stadio di potenza

(per semplicit` a 1).

Lo slew rate massimo al nodo B, indicato con SR

B

, rappresenta la massima velocit` a con

cui pu` o variare la tensione al nodo B. Quindi, afnch e una sinusoide in banda e di ampiezza

nominale non generi distorsione, tale parametro deve essere maggiore o uguale alla derivata

della sinusoide calcolata al passaggio per lo zero, cio` e:

SR

B

max

tR

_

dv

B

(t)

dt

_

= max

tR

{A sin(t)} = A

max

max

, (2.18)

Dal punto di vista elettrico per il punto B si pu` o scrivere:

i

C

B

(t) =C

B

dv

C

B

(t)

dt

, (2.19)

quindi la condizione espressa dalla (2.18) e losservazione (2.19) implicano la seguente

condizione sul valore di corrente massimo da iniettare dal punto B:

i

max

C

B

C

B

A

max

max

. (2.20)

Lequazione (2.20), perch e si traduca in una condizione numerica da impiegare nel dimen-

sionamento, necessita di una stima del valore della capacit` a equivalente al punto B. Invece i

valori di frequenza ed ampiezza sono dati dalle speciche.

Le componenti di C

B

possono essere individuate nelle seguenti:

X capacit` a di uscita, una capacit` a collegata in uscita ` e in prima approssimazione riportata al

nodo B divisa per il guadagno di corrente dello stadio Darlington;

X capacit` a parassite dei transistor collegati al nodo B, sono le capacit` a delle giunzioni base-

emettitore (prevalentemente capacit` a di diffusione che aumenta allaumentare della cor-

rente di base) e base-collettore (prevalentemente capacit` a di giunzione, che diminuisce

allaumentare della polarizzazione inversa della giunzione collettore-base) del transistor;

22 CAPITOLO 2. ANALISI E PRIMO DIMENSIONAMENTO

X capacit` a parassite verso massa dei componenti, sono le capacit` a dovute alla struttura sica

dei componenti e al layout.

Tra le varie componenti elencate la prevalente ` e quella dovuta alle capacit` a di giunzione dei

transistor direttamente collegati al nodo B e alle capacit` a parassite. Con i modelli proposti nella

successiva sezione 2.2 si giunge alla stima C

B

20pF. Data la non criticit` a degli effetti di una

sovrastima controllata del parametro, si sceglie di introdurre del margine considerando invece

C

B

= 100pF. Questo al ne di compensare le differenze rispetto alla realt` a introdotte dalle

approssimazioni dellanalisi e di evitare di perturbare il funzionamento del circuito quando in

fase di test si collegheranno al punto B terminali per il prelievo del segnale, come le sonde

delloscilloscopio.

Dalla scelta adottata risulta una corrente massima di drive delluscita di:

i

max

B

= 100pF 30V 2 50kHz = 943A, (2.21)

cio` e una corrente massima di almeno 1mA, a cui corrisponde un valore minimo della corrente

massima di drive del diodo LED delloptoisolatore di:

i

max

F

=

i

max

B

CTR

min

=

1mA

0.19

= 5.26mA. (2.22)

Considerando limpiego di amplicatori operazionali TL081, le schede tecniche specicano un

tipico output swing di 12V se alimentati con V

S

= 15V. Supponendo la riduzione di tensione

pari a V

sat

=3V, indipendentemente dalla tensione di alimentazione, allora si ha che la minima

tra le tensioni massime di uscita delloperazionale ` e pari a:

min{v

max

F

} =V

S

V

sat

= 12V3V = 9V. (2.23)

In questa condizione per soddisfare la (2.22) si deve avere:

min{v

max

F

}

R

F

= i

max

F

, (2.24)

quindi risulta che:

R

B

=

9V

5.26mA

1.71k R

F

= 1.5k . (2.25)

Rimane ora da vericare se nella situazione che si ` e denita il dispositivo opera ancora entro il

range operativo consentito.

Il minimo valore I

Max

F(avg)

ricavato dai fogli tecnici dei dispositivi considerati ` e 12mA, quindi

con il dimensionamento effettuato il dispositivo opera in ogni caso con correnti di ingresso I

F

non pericolose. Veriche analoghe vanno effettuate anche per la conseguente massima corrente

di uscita e la potenza dissipata:

I

max

B,opto

= I

max

F

CTR

max

=

12V

1.5k

0.62 5mA < 8mA = min

Dispositivi

_

I

Max

B,opto

_

(2.26)

per la potenza di uscita, dato che i valori assoluti massimi di corrente e tensione sono soddisfatti,

si potrebbe considerare la quantit` a:

P

max

opto

t+

t

i

opto

(x) v

opto

(x)dx, (2.27)

con opportuno, funzione della resistenza termica verso lambiente del dispositivo e della

sua capacit` a termica, ma nel caso in esame ` e rispettata anche la pi` u stringente:

P

max

opto

I

max

B

opto

V

max

CE

opto

= 5mA (5V0.65V) = 21.75mWP

Max

opto

= 45mW, (2.28)

quindi i valori calcolati si possono ritenere opportuni per un primo dimensionamento dello

stadio.

2.1 Stadio optoisolatori 23

2.1.4 Diodi zener D

Z,p

e D

Z,n

Per i diodi Zener D

Z

si deve individuare il valore di tensione e la corrente di polarizzazione.

La tensione V

Z

` e impiegata per la polarizzazione delluscita dei componenti optoisolatori.

In seguito alla consultazione dei fogli tecnici, si intende alimentare lo stadio di uscita dellop-

toisolatore alla tensione pi ` u elevata possibile, in modo da migliorare le condizioni di lavoro del

relativo transistor di uscita e fotodiodo rivelatore.

La corrente di polarizzazione I

DZ

viene scelta per il corretto funzionamento del diodo. Na-

turalmente, tale corrente di polarizzazione inuenza anche altri aspetti del circuito complessivo,

che per` o non verranno considerati nel dettaglio.

Scelta della tensione V

Z

La KVL della maglia che comprende il diodo Zener e luscita si ha:

V

max

out

..

24V

+V

D(on)

. .

1V

+ 2V

BE

..

2 0.7V

+V

CE(sat)

. .

0.3V

+ V

Z

..

V

Z

V

BE

..

0.65V

= V

A

..

30V

V

Z

= 4.61V, (2.29)

` e la massimo valore assegnabile a V

Z

. Valori maggiori di tensione porterebbero il regolatore

a non funzionare in modo corretto quando lamplicatore opera con segnali sufcientemente

ampi, perch e si osserverebbe un aumento della resistenza differenziale del diodo ed una cattiva

polarizzazione delluscita degli optoisolatori.

Si sceglie il componente LM4040AIZ-4.1, che presenta V

Z

= 4.1V .

Scelta della corrente di polarizzazione I

DZ

I fogli tecnici dei dispositivi LM4040AIZ-4.1 scelti, indicano una corrente minima di catodo

per garantire il funzionamento di 73A. Per la scelta della resistenza R

ZQ

si deve tener conto

della seguente relazione:

R

ZQ

<

V

A

V

Z

I

Min

Z

+i

max

B

/

min

Q

C

=

30V4.1V

73A+5mA/100

210k R

ZQ

= 56k , (2.30)

che polarizza il diodo con una corrente di circa 450A.

Si ritiene opportuno inserire in parallelo al diodo zener una capacit` a al ne di ridurre lim-

pedenza equivalente del generatore di tensione che il diodo realizza. Mantenere tale impedenza

di uscita contenuta porta il vantaggio di ridurre il carico per il circuito di uscita del componente

optoaccoppiatore, che nel circuito opera come generatore di corrente. I fogli tecnici mostrano

landamento della impedenza di uscita in funzione della frequenza, evidenziando che senza la

capacit` a C

Z

limpedenza di uscita del riferimento di tensione cresce al crescere della frequenza,

come illustrato nella gura 2.

Nella gura ` e riportato landamento dellimpedenza complessiva del riferimento di tensione

Z

Z

in parallelo alla capacit` a C

Z

= 1F, e si pu` o affermare che con il valore di polarizzazione

scelto e con tale scelta di C

Z

` e possibile mantenere limpedenza al di sotto di circa 10. Si

osserva inne che non ` e conveniente aumentare molto al di sopra di tale valore la capacit` a nel

tentativo di ridurre ulteriormente limpedenza di uscita.

Questultima affermazione si giustica considerando la gura 3, che rappresenta la parte di

circuito impiegato per liniezione della corrente di segnale erogata dagli optoisolatori. La gura

riporta anche il corrispondente schema di principio ai piccoli segnali, nel quale ` e indicata con

R

x

la resistenza di base del transistor Q

C

che realizza lo stadio amplicatore a base comune.

24 CAPITOLO 2. ANALISI E PRIMO DIMENSIONAMENTO

IR = IRMIN + 100 A

V

R

= 5V

2.5V

100 1k 10k 100k 1M

FREQUENCY (Hz)

C

L

= 1F

TANTALUM

X

CL

1k

100

10

1

0.1

I

M

P

E

D

A

N

C

E

(

)

T

J

= 25 C, I

R

= 0.1 I

R

CL = 0

(a) senza capacit` a di bypass collegata in

parallelo

I

R

= 1mA

T

J

= 25 C, I

R

= I

R

C

L

= 0

C

L

= 1F

TANTALUM

V

R

= 5V

2.5V

1k

100

10

1

0.1

100 1k 10k 100k 1M

FREQUENCY (Hz)

I

M

P

E

D

A

N

C

E

(

)

(b) con capacit` a di bypass collegata in

parallelo

Figura 2: Andamento del modulo dellimpedenza di uscita del riferimento di tensione V

Z

Il ne del circuito ` e quello di presentare una impedenza di ingresso R

m

pi` u bassa possibile per

non caricare luscita delloptoisolatore e di fare in modo che la corrente di uscita i

out

segua la

corrente di ingresso i

m

estratta dalloptoisolatore.

Il calcolo della impedenza di ingresso R

m

porta al seguente risultato:

R

m

=

v

m

i

m

=

_

_

_

_

r

C

+R

b

r

C

g

mC

1+

R

out

r

oC

1+

r

C

+R

b

r

oC

g

mC

r

C

_

_

_

_

//(R

b

+r

C

)//R

B

, (2.31)

mentre il calcolo del guadagno di corrente i

out

/i

m

:

i

out

i

m

=

i

out

(1+

P

) i

s

=

_

1

R

m

R

B

R

m

R

b

+r

C

_

, (2.32)

dove R

b

` e la resistenza vista dalla base del transistor Q

C

. Ci` o implica che, per ridurre

ulteriormente e in maniera efcace la quantit` a R

m

, ` e necessario ridurre anche i contributi

Figura 3: Schematizzazioni del circuito di buffer della corrente in uscita dai moduli optoisolatori

2.2 Stadio di uscita 25

R

x

5, ssa poich e determinata dalle caratteristiche siche del dispositivo, ma soprattut-

to r

=/g

m

2.5k, che per` o ` e determinata dal punto operativo scelto sulla base di altre

considerazioni di maggiore priorit` a, e dal guadagno del transistor.

Prima di procedere oltre, si osserva che dalle (2.31) e (2.32) si possono ricavare altre

relazioni di particolare interesse. Queste sono:

X lespressione del current transfer ratio effettivo misurato sul circuito, denito come:

CTR(s)|

s=0

=

i

b

i

f

s=0

= K

tr

CTR

nom.

i

b

i

s

, (2.33)

dove K

tr

` e un parametro che vale 1 oppure 2 a seconda del modo di funzionamento del

circuito, come ` e descritto in 2.1.2,

X lespressione che lega la corrente iniettata al nodo B, ingresso di tensione dello stadio di

uscita, alla tensione al nodo F ai piccoli segnali:

i

out

v

f

=

K

tr

R

F

CRT

nom.

i

out

i

s

. (2.34)

Inne si sottolinea che per ottenere stime corrette dalle relazioni precedenti ` e necessario

tenere conto delle resistenze di uscita nite dei transistor. Inoltre si deve tener conto che il

current transfer ratio ` e dichiarato dai datasheet pari a 0.45 con riferimento ad un particolare

circuito di test, ma ` e rilevato pari a circa 0.49 con uscita in cortocircuito, 0.45 con carico di

uscita di 48 e 0.26 con uscita in circuito aperto. Si osserva la caratteristica vantaggiosa di

avere CRT effettivi elevati per elevate correnti richieste in uscita, o per basse impedenze al nodo

B.

2.2 Stadio di uscita

Le analisi condotte relativamente allo stadio di uscita sono dirette a caratterizzare il comporta-

mento dello stadio in termini di risposta in frequenza e in termini di distorsione. Tali analisi

hanno dato la possibilit` a di determinare il criterio con cui dimensionare i componenti dello

stadio di uscita e individuarne il corretto punto di lavoro.

2.2.1 Caratteristica ingresso-uscita: scelta delle correnti in quiescenza

Lo stadio EF in esame tipicamente presenta della distorsione di crossover. La distorsione ` e

dovuta al fatto che correnti positive in uscita sono prevalentemente fornite dal ramo positivo,

viceversa, correnti negative sono fornite dal ramo negativo. In questo modo nellintorno di

corrente di uscita nulla si ha il contributo di entrambi i transistor, per basse correnti di uscita

si ha il contributo di un solo transistor poco acceso e per elevate correnti di uscita si ha il

contributo di un transistor acceso. Il passaggio di stato dei transistor inuenza la caratteristica

di trasferimento dello stadio di uscita.

Il circuito di polarizzazione realizzato mediante il moltiplicatore di V

BE

ha il ne di denire

una corrente di polarizzazione tale da mantenere costante, per quanto possibile, il guadagno in

tensione v

OUT

/v

B

dello stadio al passaggio per lo zero. In gura 4 sono schematizzati le tipiche

conseguenze della scelta della corrente di polarizzazione.

26 CAPITOLO 2. ANALISI E PRIMO DIMENSIONAMENTO

input

o

u

t

p

u

t

(a)

input

o

u

t

p

u

t

(b)

input

o

u

t

p

u

t

(c)

Figura 4: Condizioni di polarizzazione. Nellordine gli effetti di: scarsa, ottimale ed eccessiva corrente

di polarizzazione

Uno strumento che pu` o essere impiegato per ottenere una stima dellinuenza del livello di

corrente di polarizzazione sulla linearit` a dello stadio di uscita ` e lanalisi del guadagno ai piccoli

segnali. La gura 5 mostra leffetto della corrente di polarizzazione su tale guadagno.

Pi ` u in particolare, essendo il guadagno ai piccoli segnali v

out

/v

b

la derivata del segnale di

uscita rispetto al segnale di ingresso, dallinformazione ottenuta dallo studio ` e possibile indivi-

duare un metodo per determinare un opportuno valore di corrente di polarizzazione che renda

il pi ` u possibile costante il guadagno v

OUT

/v

B

. Inoltre, cos` facendo, il metodo pu` o essere even-

tualmente implementato al calcolatore per conoscere particolari risultati numerici, essendo note

dallanalisi ai piccoli segnali le relazioni tra il guadagno ed il punto di lavoro dei transistor.

Lapplicazione del procedimento al caso in esame risulta utile in quanto, sebbene nota la

corrente totale dissipabile in quiescenza dallo stadio di uscita,

3

` e incognita la porzione di cor-

rente da impiegare per la polarizzazione dei transistor Q

D

di driver e dei transistor nali di

potenza Q

O

.

Per i motivi indicati si ` e seguito quanto descritto al ne di risolvere lindeterminazione sulle

correnti di polarizzazione dello stadio di uscita. In particolare, sono state calcolate le funzioni

di trasferimento di interesse in regime quasi statico:

X resistenza di ingresso dello stadio di uscita:

r

in

=

1+(g

m1

+g

m3

) r

3

//r

1

+r

le

_

r

1

2

+g

m2

+r

1

4

+g

m4

_

(1+(g

m1

+g

m3

) r

1

//r

3

) +

r

1

//r

3

r

2

//r

4

1/r

4

+1/r

2

,

(2.35)

dove r

le

= R

E

+R

L

, denendo R

L

= 2R

L

nel caso di funzionamento parallelo o R

L

= R

L

nel caso di funzionamento singolo. Nellipotesi valga

1

,

2

>> 1 e lo stadio sia

simmetrico, cio` e r

1

= r

3

e r

2

= r

4

, la (2.35) si pu` o semplicare nella seguente:

r

in

=

r

1

+

1

r

2

+

1

r

2

g

m2

r

le

2

. (2.36)

X guadagno ai piccoli segnali dello stadio di uscita:

v

out

v

in

=

r

le

r

in

_

1+

1

+

3

2

_

(1+(g

m2

+g

m4

) r

2

//r

4

)

r

l

r

l

+r

e

/2

, (2.37)

3

La corrente in quiescenza dallo stadio di uscita ` e quella che produce una dissipazione a riposo dello stadio che

soddisfa, in modo stretto, il requisito sulla dissipazione di potenza a riposo diminuito della dissipazione a riposo

necessaria per la polarizzazione delle altre parti del circuito.

2.2 Stadio di uscita 27

Time

300ms 350ms 400ms 450ms 500ms 550ms 600ms 650ms 700ms

d(V(VOUT))/(48)

0.4000

0.6000

0.8000

1.0000

0.2306

Figura 5: Guadagno ai piccoli segnali dello stadio di uscita al variare delle condizioni di polarizzazione

che si semplica, sempre sotto le ipotesi del punto precedente, nella:

v

out

v

in

=

R

L

g

m1

g

m2

2

g

m2

+g

m1

2

+r

le

g

m1

g

m2

2

. (2.38)

Successivamente, chiamate:

I

Q

la corrente in quiescenza totale assorbita dallo stadio di uscita,

I

O,Q

= I

Q

I

D,Q

la corrente assorbita dai transistor nali e

I

D,Q

= (1I

O,Q

/I

Q

)I

Q

la corrente assorbita dai transistor di drive,

si ` e calcolato:

X il guadagno ai piccoli segnali dello stadio nellintorno di tensione di uscita nulla, con

un carico resistivo tale che assorba la corrente nominale quando in uscita si misura la

tensione nominale, e

X il guadagno ai piccoli segnali dello stadio quando la corrente assorbita dal carico ` e quella

nominale.

Quindi si ` e calcolato il valore di distorsione armonica totale che si misura alluscita di un am-

plicatore avente per ingresso una sinusoide di ampiezza nominale e la cui caratteristica statica

` e composta sulla base dellapprossimazione illustrata in gura 6. Il procedimento, iterato pi` u

28 CAPITOLO 2. ANALISI E PRIMO DIMENSIONAMENTO

Time

200ms 300ms 400ms 500ms 600ms 700ms 800ms

V(VOUT) V(E3:4,VBB-)

-2.50V

0V

2.50V

-3.84V

4.85V

Andamento ideale

Andamento eettivo

Andamento aprossimato

O

u

t

p

u

t

V

o

l

t

a

g

e

Spezzamenti