Académique Documents

Professionnel Documents

Culture Documents

74HC193 74HCT193: NXP Semiconductors

Transféré par

kjfenTitre original

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

74HC193 74HCT193: NXP Semiconductors

Transféré par

kjfenDroits d'auteur :

Formats disponibles

NXP Semiconductors

74HC193; 74HCT193

Presettable synchronous 4-bit binary up/down counter

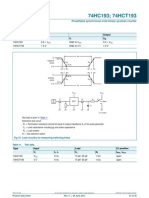

Table 9. Symbol trec

Dynamic characteristics type 74HCT193 continued Parameter recovery time Conditions Min PL to CPU, CPD; see Figure 11 VCC = 4.5 V MR to CPU, CPD; see Figure 12 VCC = 4.5 V 10 0 13 15 ns 10 2 13 15 ns 25 C Typ Max 40 C to +85 C 40 C to +125 C Unit Min Max Min Max

tsu

set-up time

Dn to PL; see Figure 13; note: CPU = CPD = HIGH VCC = 4.5 V 16 8 20 24 ns Dn to PL; see Figure 13 VCC = 4.5 V CPU to CPD, CPD to CPU; see Figure 15 VCC = 4.5 V 16 7 20 24 ns 0 6 0 0 ns

th

hold time

fmax

maximum frequency power dissipation capacitance

CPU, CPD; see Figure 9 VCC = 4.5 V 20

[2]

43 26

16 -

13 -

MHz pF

CPD

VI = GND to VCC 1.5 V; VCC = 5 V; fi = 1 MHz

[1] [2]

tpd is the same as tPHL and tPLH. CPD is used to determine the dynamic power dissipation (PD in W): PD = CPD VCC2 fi N + (CL VCC2 fo) where: fi = input frequency in MHz; fo = output frequency in MHz; CL = output load capacitance in pF; VCC = supply voltage in V; N = number of inputs switching; (CL VCC2 fo) = sum of outputs.

74HC_HCT193

All information provided in this document is subject to legal disclaimers.

NXP B.V. 2013. All rights reserved.

Product data sheet

Rev. 4 24 June 2013

17 of 30

NXP Semiconductors

74HC193; 74HCT193

Presettable synchronous 4-bit binary up/down counter

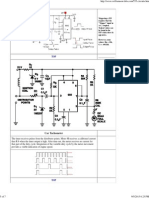

11. Waveforms

1/fmax VI CPU, CPD input GND tW t PHL VOH Qn output VOL VM

001aag413

VM

t PLH

Measurement points are given in Table 10. tPLH and tPHL are the same as tpd. Logic levels VOL and VOH are typical output voltage levels that occur with the output load.

Fig 9. The clock (CPU, CPD) to output (Qn) propagation delays, the clock pulse width, and the maximum clock pulse frequency

VI CPU, CPD input GND tPHL VOH TCU, TCD output VOL VM

001aag414

VM

tPLH

Measurement points are given in Table 10. tPLH and tPHL are the same as tpd. Logic levels VOL and VOH are typical output voltage levels that occur with the output load.

Fig 10. The clock (CPU, CPD) to terminal count output (TCU, TCD) propagation delays

74HC_HCT193

All information provided in this document is subject to legal disclaimers.

NXP B.V. 2013. All rights reserved.

Product data sheet

Rev. 4 24 June 2013

18 of 30

Vous aimerez peut-être aussi

- 74 HC 163Document12 pages74 HC 163Pablo Petrowitsch CrignolaPas encore d'évaluation

- 74HC4520Document8 pages74HC4520pnlinh28Pas encore d'évaluation

- 74hc126 74hct126Document6 pages74hc126 74hct126shatruddha123Pas encore d'évaluation

- Data SheetDocument10 pagesData SheetShowPiecePas encore d'évaluation

- Integrated Circuits Data Sheet for 74HC/HCT125 Quad BufferDocument6 pagesIntegrated Circuits Data Sheet for 74HC/HCT125 Quad BufferAndes IndrayantoPas encore d'évaluation

- Integrated Circuits Data Sheet - 74HC/HCT574 Octal D-Type Flip-FlopDocument8 pagesIntegrated Circuits Data Sheet - 74HC/HCT574 Octal D-Type Flip-Flopthinh040Pas encore d'évaluation

- Data Sheet: 74HC/HCT93Document8 pagesData Sheet: 74HC/HCT93swapnilharalPas encore d'évaluation

- 74 HC 193Document14 pages74 HC 193Rafael GutierrezPas encore d'évaluation

- 74 HC 93Document7 pages74 HC 93Brzata PticaPas encore d'évaluation

- Presettable synchronous BCD decade counter data sheetDocument11 pagesPresettable synchronous BCD decade counter data sheetIrvson SilveiraPas encore d'évaluation

- 74 HC 73Document7 pages74 HC 73Jorge Alberto100% (1)

- 74HC HCT365 CNV 2Document8 pages74HC HCT365 CNV 2Mini Veiga AlbánPas encore d'évaluation

- Integrated Circuits Data Sheet: 8-bit Parallel-In/Serial-Out Shift RegisterDocument11 pagesIntegrated Circuits Data Sheet: 8-bit Parallel-In/Serial-Out Shift RegisterNegru P. PlantatiePas encore d'évaluation

- 74HC4094Document11 pages74HC4094Gustavo BarcasnegrasPas encore d'évaluation

- Datasheet 74hct40103Document17 pagesDatasheet 74hct40103Yettie OgunduboyePas encore d'évaluation

- 74HC HCT166 CNVDocument10 pages74HC HCT166 CNVroozbehxoxPas encore d'évaluation

- Integrated Circuits Data Sheet: 74HC/HCT173 Quad D-Type Flip-FlopDocument11 pagesIntegrated Circuits Data Sheet: 74HC/HCT173 Quad D-Type Flip-FlopBryan Bethke IIIPas encore d'évaluation

- 74HC165 8-Bit PISO Shift RegisterDocument10 pages74HC165 8-Bit PISO Shift Registeroscar_ceja_02Pas encore d'évaluation

- 74HC HCT640 CNV PDFDocument6 pages74HC HCT640 CNV PDFCesar VilledaPas encore d'évaluation

- 74HCT75 PDFDocument7 pages74HCT75 PDFDeni KhanPas encore d'évaluation

- 74HC193 74HCT193: 10. Dynamic CharacteristicsDocument2 pages74HC193 74HCT193: 10. Dynamic CharacteristicskjfenPas encore d'évaluation

- Data Sheet: 74HC/HCT377Document7 pagesData Sheet: 74HC/HCT377kien_hatinhPas encore d'évaluation

- 74HC190Document13 pages74HC190Enzo Paolo D'Angelo0% (1)

- 74HC190 DatasheetDocument14 pages74HC190 Datasheetmym786Pas encore d'évaluation

- Integrated Circuits Data Sheet for Octal Bus TransceiverDocument8 pagesIntegrated Circuits Data Sheet for Octal Bus TransceiverOscar Zabaleta LaverdePas encore d'évaluation

- 2Document7 pages2Rama Krishna Reddy GudooruPas encore d'évaluation

- 74HC4040 12 Stage Binary Ripple CounterDocument8 pages74HC4040 12 Stage Binary Ripple CounterPablo RosasPas encore d'évaluation

- Data Sheet: 74HC/HCT126Document7 pagesData Sheet: 74HC/HCT126gotcha75Pas encore d'évaluation

- 74HC14 74HCT14: 1. General DescriptionDocument21 pages74HC14 74HCT14: 1. General DescriptionDao Nguyen Trong TinPas encore d'évaluation

- Datasheet Pc74hc123Document18 pagesDatasheet Pc74hc123Diego HenriquePas encore d'évaluation

- 74HC193 74HCT193: 5. Pinning InformationDocument2 pages74HC193 74HCT193: 5. Pinning InformationkjfenPas encore d'évaluation

- Data Sheet: 74HC/HCT175Document14 pagesData Sheet: 74HC/HCT175wtn2013Pas encore d'évaluation

- 74HC174Document14 pages74HC174wtn2013Pas encore d'évaluation

- Ic 74HC194Document10 pagesIc 74HC194ReyesPas encore d'évaluation

- 74LS175Document3 pages74LS175Yesenia RojoPas encore d'évaluation

- Integrated Circuits Data Sheet for 74HC/HCT297 Digital Phase-Locked-Loop FilterDocument13 pagesIntegrated Circuits Data Sheet for 74HC/HCT297 Digital Phase-Locked-Loop FilterDeepa DevarajPas encore d'évaluation

- General Description: 8-Bit Synchronous Binary Down CounterDocument25 pagesGeneral Description: 8-Bit Synchronous Binary Down CounterspotPas encore d'évaluation

- 74HC193 74HCT193: NXP SemiconductorsDocument2 pages74HC193 74HCT193: NXP SemiconductorskjfenPas encore d'évaluation

- Data Sheet: 74HC/HCT74Document13 pagesData Sheet: 74HC/HCT74Anubhav YadavPas encore d'évaluation

- 74HC4543Document12 pages74HC4543Anung PriyantoPas encore d'évaluation

- 74 HC 4060Document13 pages74 HC 4060anyenkts2Pas encore d'évaluation

- 74HCT4060Document12 pages74HCT4060shamshim2000Pas encore d'évaluation

- 74HC193 74HCT193: 1. General DescriptionDocument29 pages74HC193 74HCT193: 1. General Descriptionsupriyo110Pas encore d'évaluation

- 74HC04 74HCT04: 1. General DescriptionDocument18 pages74HC04 74HCT04: 1. General DescriptionDistribuidorIBoolPedregalDeSantoDomingoPas encore d'évaluation

- Integrated Circuits Data Sheet - Hex Inverting Schmitt TriggerDocument8 pagesIntegrated Circuits Data Sheet - Hex Inverting Schmitt Triggerdragon-red0816Pas encore d'évaluation

- Integrated Circuits Data Sheet for 74HC/HCT10 Triple 3-Input NAND GateDocument5 pagesIntegrated Circuits Data Sheet for 74HC/HCT10 Triple 3-Input NAND GateKapila Dhammika EdirisinghePas encore d'évaluation

- Integrated Circuits Data Sheet: 74HC/HCT243 Quad Bus TransceiverDocument8 pagesIntegrated Circuits Data Sheet: 74HC/HCT243 Quad Bus TransceiverseppPas encore d'évaluation

- HCF 4510Document11 pagesHCF 4510SoeAyePas encore d'évaluation

- 7473Document8 pages7473Merényi OszkárPas encore d'évaluation

- 74HC132 74HCT132: 1. General DescriptionDocument19 pages74HC132 74HCT132: 1. General DescriptionAnonymous xTGQYFrPas encore d'évaluation

- 74HC HCT4514Document9 pages74HC HCT4514Visweswaran MvsPas encore d'évaluation

- 5.2 PWM 7 Mac 2017Document34 pages5.2 PWM 7 Mac 2017Elawarasi Nadarajan100% (1)

- DM74LS174 - DM74LS175 Hex/Quad D-Type Flip-Flops With Clear: General Description FeaturesDocument8 pagesDM74LS174 - DM74LS175 Hex/Quad D-Type Flip-Flops With Clear: General Description FeatureshuvillamilPas encore d'évaluation

- 74HC08 74HCT08: 1. General DescriptionDocument15 pages74HC08 74HCT08: 1. General DescriptionFlavio KwiecinskiPas encore d'évaluation

- Foaie Catalog MUX 74HC153Document7 pagesFoaie Catalog MUX 74HC153Andrei MolochPas encore d'évaluation

- The PIC Microcontroller: Your Personal Introductory CourseD'EverandThe PIC Microcontroller: Your Personal Introductory CourseÉvaluation : 1 sur 5 étoiles1/5 (2)

- Digital Signal Processing Using the ARM Cortex M4D'EverandDigital Signal Processing Using the ARM Cortex M4Évaluation : 1 sur 5 étoiles1/5 (1)

- Selo 1Document26 pagesSelo 1kjfenPas encore d'évaluation

- Timer Tutorials 555Document1 pageTimer Tutorials 555kjfenPas encore d'évaluation

- 7SA522 CatalogueDocument53 pages7SA522 CataloguePhilip D'cruzPas encore d'évaluation

- Water Treatments: Steam Water Cycle TreatmentDocument2 pagesWater Treatments: Steam Water Cycle TreatmentkjfenPas encore d'évaluation

- 74HC193 74HCT193: 17. Contact InformationDocument2 pages74HC193 74HCT193: 17. Contact InformationkjfenPas encore d'évaluation

- Timer Tutorials 555Document1 pageTimer Tutorials 555kjfenPas encore d'évaluation

- 7 Ways Signal Noise Can Impact Your Electrical EquipmentDocument5 pages7 Ways Signal Noise Can Impact Your Electrical EquipmentkjfenPas encore d'évaluation

- Temperature Monitoring: FaizanDocument5 pagesTemperature Monitoring: FaizankjfenPas encore d'évaluation

- REG670Document88 pagesREG670Rafael Hoffmann PaludoPas encore d'évaluation

- Timer Tutorials 555Document1 pageTimer Tutorials 555kjfenPas encore d'évaluation

- Load Forecasting and Standardized Load CurvesDocument10 pagesLoad Forecasting and Standardized Load CurveskjfenPas encore d'évaluation

- 74HC193 74HCT193: 14. AbbreviationsDocument2 pages74HC193 74HCT193: 14. AbbreviationskjfenPas encore d'évaluation

- Sub 131Document10 pagesSub 131kjfenPas encore d'évaluation

- 555 Timer Tutorial - How to Build CircuitsDocument1 page555 Timer Tutorial - How to Build CircuitskjfenPas encore d'évaluation

- Timer Tutorials 555Document1 pageTimer Tutorials 555kjfenPas encore d'évaluation

- Timer Tutorials 555Document1 pageTimer Tutorials 555kjfenPas encore d'évaluation

- 74HC193 74HCT193: NXP SemiconductorsDocument2 pages74HC193 74HCT193: NXP SemiconductorskjfenPas encore d'évaluation

- 74HC193 74HCT193: NXP SemiconductorsDocument2 pages74HC193 74HCT193: NXP SemiconductorskjfenPas encore d'évaluation

- 74HC193 74HCT193: NXP SemiconductorsDocument2 pages74HC193 74HCT193: NXP SemiconductorskjfenPas encore d'évaluation

- 74HC HCT193Document2 pages74HC HCT193kjfenPas encore d'évaluation

- Timer Tutorials 555Document1 pageTimer Tutorials 555kjfenPas encore d'évaluation

- 74HC193 74HCT193: 13. Package OutlineDocument2 pages74HC193 74HCT193: 13. Package OutlinekjfenPas encore d'évaluation

- 74HC193 74HCT193: 10. Dynamic CharacteristicsDocument2 pages74HC193 74HCT193: 10. Dynamic CharacteristicskjfenPas encore d'évaluation

- 74HC193 74HCT193: 10. Dynamic CharacteristicsDocument2 pages74HC193 74HCT193: 10. Dynamic CharacteristicskjfenPas encore d'évaluation

- 74HC193 74HCT193: NXP SemiconductorsDocument2 pages74HC193 74HCT193: NXP SemiconductorskjfenPas encore d'évaluation

- 74HC193 74HCT193: 9. Static CharacteristicsDocument2 pages74HC193 74HCT193: 9. Static CharacteristicskjfenPas encore d'évaluation

- 74HC193 74HCT193: NXP SemiconductorsDocument2 pages74HC193 74HCT193: NXP SemiconductorskjfenPas encore d'évaluation

- 74HC193 74HCT193: NXP SemiconductorsDocument2 pages74HC193 74HCT193: NXP SemiconductorskjfenPas encore d'évaluation

- 74HC193 74HCT193: 5. Pinning InformationDocument2 pages74HC193 74HCT193: 5. Pinning InformationkjfenPas encore d'évaluation