Académique Documents

Professionnel Documents

Culture Documents

74HC193 74HCT193: NXP Semiconductors

Transféré par

kjfenTitre original

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

74HC193 74HCT193: NXP Semiconductors

Transféré par

kjfenDroits d'auteur :

Formats disponibles

NXP Semiconductors

74HC193; 74HCT193

Presettable synchronous 4-bit binary up/down counter

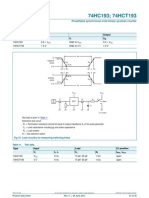

VI Dn input GND VI PL input GND tW VI CPU, CPD input GND t PLH VOH Qn output VOL

001aag415

VM

VM t rec VM

t PHL

VM

Measurement points are given in Table 10. tPLH and tPHL are the same as tpd. Logic levels VOL and VOH are typical output voltage levels that occur with the output load.

Fig 11. The parallel load input (PL) and data (Dn) to Qn output propagation delays and PL removal time to clock input (CPU, CPD)

VI MR input GND tW VI CPU, CPD input GND t PHL VOH Qn output VOL 90 % VM 10 % t THL t TLH

001aag416

VM

t rec VM

Measurement points are given in Table 10. tPLH and tPHL are the same as tpd. Logic levels VOL and VOH are typical output voltage levels that occur with the output load.

Fig 12. The master reset input (MR) pulse width, MR to Qn propagation delays, MR to CPU, CPD removal time and output transition times

74HC_HCT193

All information provided in this document is subject to legal disclaimers.

NXP B.V. 2013. All rights reserved.

Product data sheet

Rev. 4 24 June 2013

19 of 30

NXP Semiconductors

74HC193; 74HCT193

Presettable synchronous 4-bit binary up/down counter

VI Dn input GND VI PL input GND VOH Qn output VOL

001aag417

VM tsu th VM tsu th

The shaded areas indicate when the input is permitted to change for predictable output performance. Measurement points are given in Table 10. Logic levels VOL and VOH are typical output voltage levels that occur with the output load.

Fig 13. The data input (Dn) to parallel load input (PL) set-up and hold times

VI PL, MR, Dn input GND tPLH VOH TCU, TCD output VOL

001aag418

VM

tPHL

VM

Measurement points are given in Table 10. tPLH and tPHL are the same as tpd. Logic levels VOL and VOH are typical output voltage levels that occur with the output load.

Fig 14. The data input (Dn), parallel load input (PL) and the master reset input (MR) to the terminal count outputs (TCU, TCD) propagation delays

VI CPU or CPD input GND th VI CPD or CPU input GND VM

001aag419

VM

Measurement points are given in Table 10.

Fig 15. The CPU to CPD or CPD to CPU hold times

74HC_HCT193

All information provided in this document is subject to legal disclaimers.

NXP B.V. 2013. All rights reserved.

Product data sheet

Rev. 4 24 June 2013

20 of 30

Vous aimerez peut-être aussi

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeD'EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeÉvaluation : 4 sur 5 étoiles4/5 (5794)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreD'EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreÉvaluation : 4 sur 5 étoiles4/5 (1090)

- Never Split the Difference: Negotiating As If Your Life Depended On ItD'EverandNever Split the Difference: Negotiating As If Your Life Depended On ItÉvaluation : 4.5 sur 5 étoiles4.5/5 (838)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceD'EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceÉvaluation : 4 sur 5 étoiles4/5 (894)

- Grit: The Power of Passion and PerseveranceD'EverandGrit: The Power of Passion and PerseveranceÉvaluation : 4 sur 5 étoiles4/5 (587)

- Shoe Dog: A Memoir by the Creator of NikeD'EverandShoe Dog: A Memoir by the Creator of NikeÉvaluation : 4.5 sur 5 étoiles4.5/5 (537)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureD'EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureÉvaluation : 4.5 sur 5 étoiles4.5/5 (474)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersD'EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersÉvaluation : 4.5 sur 5 étoiles4.5/5 (344)

- Her Body and Other Parties: StoriesD'EverandHer Body and Other Parties: StoriesÉvaluation : 4 sur 5 étoiles4/5 (821)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)D'EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Évaluation : 4.5 sur 5 étoiles4.5/5 (119)

- The Emperor of All Maladies: A Biography of CancerD'EverandThe Emperor of All Maladies: A Biography of CancerÉvaluation : 4.5 sur 5 étoiles4.5/5 (271)

- The Little Book of Hygge: Danish Secrets to Happy LivingD'EverandThe Little Book of Hygge: Danish Secrets to Happy LivingÉvaluation : 3.5 sur 5 étoiles3.5/5 (399)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyD'EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyÉvaluation : 3.5 sur 5 étoiles3.5/5 (2219)

- The Yellow House: A Memoir (2019 National Book Award Winner)D'EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Évaluation : 4 sur 5 étoiles4/5 (98)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaD'EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaÉvaluation : 4.5 sur 5 étoiles4.5/5 (265)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryD'EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryÉvaluation : 3.5 sur 5 étoiles3.5/5 (231)

- Team of Rivals: The Political Genius of Abraham LincolnD'EverandTeam of Rivals: The Political Genius of Abraham LincolnÉvaluation : 4.5 sur 5 étoiles4.5/5 (234)

- On Fire: The (Burning) Case for a Green New DealD'EverandOn Fire: The (Burning) Case for a Green New DealÉvaluation : 4 sur 5 étoiles4/5 (73)

- The Unwinding: An Inner History of the New AmericaD'EverandThe Unwinding: An Inner History of the New AmericaÉvaluation : 4 sur 5 étoiles4/5 (45)

- Sub 131Document10 pagesSub 131kjfenPas encore d'évaluation

- Water Treatments: Steam Water Cycle TreatmentDocument2 pagesWater Treatments: Steam Water Cycle TreatmentkjfenPas encore d'évaluation

- Selo 1Document26 pagesSelo 1kjfenPas encore d'évaluation

- 7SA522 CatalogueDocument53 pages7SA522 CataloguePhilip D'cruzPas encore d'évaluation

- Temperature Monitoring: FaizanDocument5 pagesTemperature Monitoring: FaizankjfenPas encore d'évaluation

- 555 Timer Tutorial - How to Build CircuitsDocument1 page555 Timer Tutorial - How to Build CircuitskjfenPas encore d'évaluation

- 7 Ways Signal Noise Can Impact Your Electrical EquipmentDocument5 pages7 Ways Signal Noise Can Impact Your Electrical EquipmentkjfenPas encore d'évaluation

- REG670Document88 pagesREG670Rafael Hoffmann PaludoPas encore d'évaluation

- Load Forecasting and Standardized Load CurvesDocument10 pagesLoad Forecasting and Standardized Load CurveskjfenPas encore d'évaluation

- 74HC193 74HCT193: 14. AbbreviationsDocument2 pages74HC193 74HCT193: 14. AbbreviationskjfenPas encore d'évaluation

- Timer Tutorials 555Document1 pageTimer Tutorials 555kjfenPas encore d'évaluation

- Timer Tutorials 555Document1 pageTimer Tutorials 555kjfenPas encore d'évaluation

- Timer Tutorials 555Document1 pageTimer Tutorials 555kjfenPas encore d'évaluation

- Timer Tutorials 555Document1 pageTimer Tutorials 555kjfenPas encore d'évaluation

- Timer Tutorials 555Document1 pageTimer Tutorials 555kjfenPas encore d'évaluation

- Timer Tutorials 555Document1 pageTimer Tutorials 555kjfenPas encore d'évaluation

- 74HC193 74HCT193: 17. Contact InformationDocument2 pages74HC193 74HCT193: 17. Contact InformationkjfenPas encore d'évaluation

- 74HC193 74HCT193: NXP SemiconductorsDocument2 pages74HC193 74HCT193: NXP SemiconductorskjfenPas encore d'évaluation

- 74HC193 74HCT193: NXP SemiconductorsDocument2 pages74HC193 74HCT193: NXP SemiconductorskjfenPas encore d'évaluation

- 74HC193 74HCT193: NXP SemiconductorsDocument2 pages74HC193 74HCT193: NXP SemiconductorskjfenPas encore d'évaluation

- 74HC193 74HCT193: NXP SemiconductorsDocument2 pages74HC193 74HCT193: NXP SemiconductorskjfenPas encore d'évaluation

- 74HC193 74HCT193: 13. Package OutlineDocument2 pages74HC193 74HCT193: 13. Package OutlinekjfenPas encore d'évaluation

- 74HC193 74HCT193: 10. Dynamic CharacteristicsDocument2 pages74HC193 74HCT193: 10. Dynamic CharacteristicskjfenPas encore d'évaluation

- 74HC HCT193Document2 pages74HC HCT193kjfenPas encore d'évaluation

- 74HC193 74HCT193: 9. Static CharacteristicsDocument2 pages74HC193 74HCT193: 9. Static CharacteristicskjfenPas encore d'évaluation

- 74HC193 74HCT193: 10. Dynamic CharacteristicsDocument2 pages74HC193 74HCT193: 10. Dynamic CharacteristicskjfenPas encore d'évaluation

- 74HC193 74HCT193: NXP SemiconductorsDocument2 pages74HC193 74HCT193: NXP SemiconductorskjfenPas encore d'évaluation

- 74HC193 74HCT193: 5. Pinning InformationDocument2 pages74HC193 74HCT193: 5. Pinning InformationkjfenPas encore d'évaluation

- 74HC193 74HCT193: NXP SemiconductorsDocument2 pages74HC193 74HCT193: NXP SemiconductorskjfenPas encore d'évaluation