Académique Documents

Professionnel Documents

Culture Documents

Adca / Mca (Iii Year) 7t' Term-End Examination December, 2011 Cs-12: Computer Architecture

Transféré par

haider_ali980Description originale:

Titre original

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

Adca / Mca (Iii Year) 7t' Term-End Examination December, 2011 Cs-12: Computer Architecture

Transféré par

haider_ali980Droits d'auteur :

Formats disponibles

No.

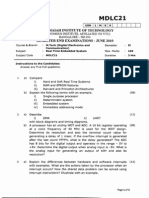

of Printed Pages : 3 ADCA / MCA (III Year) 7t' Term-End Examination December, 2011

I CS-12 I

CS-12 : COMPUTER ARCHITECTURE

Time : 3 hours Maximum Marks : 75

Note : Question no. 1 is compulsory. Answer any three questions from the rest.

1. (a) A 150 MHz processor was used to execute 9 a benchmar2k program with the following instruction and clock cycle counts.

Clock Instruction Instruction Type cycle count count Integer Arithmetic 60, 000 Data Transfer 40, 000 Floating Point 15, 000 Control transfer 8, 000

,--1 C1 Csi CA

Determine the effective CPI, MIPs rate and execution time for this program. CS-12 1 P.T.O.

(b) (c)

(d)

What are the factors limiting the degree of 5 Super Scalar design ? What is multi - threaded processor 8 architecture ? Explain its advantages and disadvantages in comparison to single threaded processors. Explain the architectural distinctions 8 between RISC and CLSC processors. Also, explain the concept of overlapping register windows in the SPARC architecture diagrammatically.

2. (a) Consider the following sequence of code and answer the following questions : : A =D + C S2 : C=E+B S3 : D=A+C S4 : E=F+D S5 : G=E+D S6 : D=A+F S7 : B=G+T (i) Use Bernsteins condition to detect the 5 maximum parallelism embedded in this code. Justify the portion that can be executed in parallel and the remaining portion that must be executed sequentially. (ii) Draw a dependency graph to show 5 all the dependences for the above code. CS-12 2

(b) Describe the differences between super - 5 scalar and VLIW architectures in terms of hardware and software requirements. 3. Explain the following as applied to multiprocessors and multicomputers. (a) A hierarchical cache/bus architecture for 5 designing a scalable multiprocessors. 5 (b) Network partitioning for multicast (c) communication. 5 Discard and Retransmission flow control.

4. (a) Explain the three mechanisms for 9 instruction pipelining, giving an example for each. (b) Explain the effect of block size, set number, 6 associativity and cache size on the performance of set associative cache organisation. 15 5. Compare and contrast the following : (a) Instruction and Trace scheduling (b) NUMA and COMA (c) Coarse gain and Medium grain parallelism

CS-12

Vous aimerez peut-être aussi

- C G192056 Pages:3: Answer All Questions, Each Carries 4 MarksDocument3 pagesC G192056 Pages:3: Answer All Questions, Each Carries 4 MarksCigi ManojPas encore d'évaluation

- Aca Q-BankDocument3 pagesAca Q-BankAyan DasPas encore d'évaluation

- Computer Architecture and OrganizationDocument6 pagesComputer Architecture and OrganizationRahmantic SwatzPas encore d'évaluation

- Embedded System DesignDocument15 pagesEmbedded System DesignKirthi RkPas encore d'évaluation

- CAPP1Document4 pagesCAPP1Navneeth NarayanPas encore d'évaluation

- Question Bank CompleteDocument5 pagesQuestion Bank CompleteSaurabh SenPas encore d'évaluation

- Bca CBCSDocument51 pagesBca CBCSMathan NaganPas encore d'évaluation

- 7th ITDocument6 pages7th ITYashika JindalPas encore d'évaluation

- C G192056 Pages:3: Answer All Questions, Each Carries 4 MarksDocument3 pagesC G192056 Pages:3: Answer All Questions, Each Carries 4 MarksVicPas encore d'évaluation

- 07a80305 ComputerorganizationandarchitectureDocument8 pages07a80305 ComputerorganizationandarchitectureSharanya ThirichinapalliPas encore d'évaluation

- 9A05704 Advanced Computer ArchitectureDocument4 pages9A05704 Advanced Computer ArchitecturesivabharathamurthyPas encore d'évaluation

- Diploma Examination, 2011: 130. Logic and Distributed Control SystemDocument5 pagesDiploma Examination, 2011: 130. Logic and Distributed Control SystemMuthuLakshmi RajendranPas encore d'évaluation

- Question Bank - M5 To M7Document2 pagesQuestion Bank - M5 To M7Pieter MarkerPas encore d'évaluation

- (3hours) : CompulsoryDocument7 pages(3hours) : CompulsorySaima ZainabPas encore d'évaluation

- Nr-Vlsi Technology and DesignDocument2 pagesNr-Vlsi Technology and DesignSudhakar SpartanPas encore d'évaluation

- 07a80402 EmbeddedandrealtimesystemsDocument6 pages07a80402 EmbeddedandrealtimesystemsSharanya ThirichinapalliPas encore d'évaluation

- MCA (Revised) Term-End Examination N-R-R) December, 2013 Mcs-012: Computer Organisation & Assembly Language ProgrammingDocument3 pagesMCA (Revised) Term-End Examination N-R-R) December, 2013 Mcs-012: Computer Organisation & Assembly Language ProgrammingpritywizPas encore d'évaluation

- M. Tech. Semester - I: Distributed Computing (MCSCS 101/1MCS1)Document20 pagesM. Tech. Semester - I: Distributed Computing (MCSCS 101/1MCS1)saurabh1116Pas encore d'évaluation

- Jntu Vlsi Systems DesignDocument5 pagesJntu Vlsi Systems Design9010469071Pas encore d'évaluation

- DDCO UPDATED QUESTION BANKttttDocument4 pagesDDCO UPDATED QUESTION BANKttttbrahmareddy.22isePas encore d'évaluation

- Instructions:: 1692 No of Pages Course CodeDocument2 pagesInstructions:: 1692 No of Pages Course CodePRAGAPas encore d'évaluation

- Computer Architecture Question BankDocument10 pagesComputer Architecture Question BankaniprahalPas encore d'évaluation

- M. Tech. Semester - I: Advanced Computer Architecture (MCSCS102IBMCSCS 902)Document12 pagesM. Tech. Semester - I: Advanced Computer Architecture (MCSCS102IBMCSCS 902)saurabh1116Pas encore d'évaluation

- MCS 012Document118 pagesMCS 012SongYak YamPas encore d'évaluation

- Embedded Systems and Technologies (M. Tech. IAR)Document3 pagesEmbedded Systems and Technologies (M. Tech. IAR)Gupta RanveerPas encore d'évaluation

- MCS-012 MCA (Revised) TR) Term-End Examination cNI June, 2011 0, - Mcs-012: Computer Organisation & Assembly Language ProgrammingDocument3 pagesMCS-012 MCA (Revised) TR) Term-End Examination cNI June, 2011 0, - Mcs-012: Computer Organisation & Assembly Language ProgrammingRajib SahaPas encore d'évaluation

- 12-Mca-Or-Computer OrganizationDocument2 pages12-Mca-Or-Computer OrganizationSRINIVASA RAO GANTAPas encore d'évaluation

- Embedded System DesignDocument2 pagesEmbedded System DesignNipun JainPas encore d'évaluation

- Co Unitwise Questions NewDocument13 pagesCo Unitwise Questions NewSai VenkateshPas encore d'évaluation

- Vlsi QP 1Document6 pagesVlsi QP 1Sailesh PosaniPas encore d'évaluation

- Adv. Computer Architecture CS701 - Jan 011Document2 pagesAdv. Computer Architecture CS701 - Jan 011Sachin Kumar GoyelPas encore d'évaluation

- Adca / Mca (Iii Year) Term-End. Examination June, 2OO7Document4 pagesAdca / Mca (Iii Year) Term-End. Examination June, 2OO7amritanshuuPas encore d'évaluation

- MCS 012Document5 pagesMCS 012S.M. FarhanPas encore d'évaluation

- Computer NetwoksDocument2 pagesComputer NetwoksArijit HembramPas encore d'évaluation

- 2011 Advanced Computer Architecture: CS/B.TECH (CSE) /SEM-4/CS-403/2011Document7 pages2011 Advanced Computer Architecture: CS/B.TECH (CSE) /SEM-4/CS-403/2011Avik MitraPas encore d'évaluation

- Ca Ap9222 PDFDocument4 pagesCa Ap9222 PDFVenkataLakshmi KrishnasamyPas encore d'évaluation

- CS1252 Operating Systems May Jun 2007Document3 pagesCS1252 Operating Systems May Jun 2007aniruthgsabapathyPas encore d'évaluation

- MCSE-011 - D16 - CompressedDocument4 pagesMCSE-011 - D16 - CompressedDeepthireddyPas encore d'évaluation

- Answer All Questions, Each Carries 4 MarksDocument3 pagesAnswer All Questions, Each Carries 4 MarksCigi ManojPas encore d'évaluation

- MCS 012 Previous Year Question Papers by IgnouassignmentguruDocument96 pagesMCS 012 Previous Year Question Papers by IgnouassignmentguruMayank ChoudharyPas encore d'évaluation

- FPGA Based System DesignDocument2 pagesFPGA Based System Designammayi9845_930467904Pas encore d'évaluation

- Computer Organization Architecture RCS 302Document2 pagesComputer Organization Architecture RCS 302yugam sainiPas encore d'évaluation

- Digital Nov 07Document6 pagesDigital Nov 07skssushPas encore d'évaluation

- VI Sem, Jan, Feb 2005Document4 pagesVI Sem, Jan, Feb 2005Veeresh NicolytePas encore d'évaluation

- EC2303 Computer Architecture and Organization QUESTION PAPERDocument4 pagesEC2303 Computer Architecture and Organization QUESTION PAPERJayagopal JaiPas encore d'évaluation

- Indian Institute of Technology, Kharagpur: Mid-Spring Semester 2021-22Document4 pagesIndian Institute of Technology, Kharagpur: Mid-Spring Semester 2021-22Utkarsh PatelPas encore d'évaluation

- CS-68 Bachelor in Computer Applications Term-End Examination June, 2012 Cs-68: Computer NetworksDocument2 pagesCS-68 Bachelor in Computer Applications Term-End Examination June, 2012 Cs-68: Computer Networksr_k_sPas encore d'évaluation

- Time: 03 Hours Maximum Marks: 100: (Autonomous Institution Under VTU) VI Semester B. E. Examinations, May/Jun 14Document3 pagesTime: 03 Hours Maximum Marks: 100: (Autonomous Institution Under VTU) VI Semester B. E. Examinations, May/Jun 14PrateekMandiPas encore d'évaluation

- 21CS34 SIMP Questions - 21SCHEME: Module-1 (Study Any 5 Questions)Document4 pages21CS34 SIMP Questions - 21SCHEME: Module-1 (Study Any 5 Questions)Rohan RPas encore d'évaluation

- Microprocessors (CSE 206) (Makeup)Document2 pagesMicroprocessors (CSE 206) (Makeup)Vishal VimalkumarPas encore d'évaluation

- Pdfjoiner PDFDocument26 pagesPdfjoiner PDFbakosey323Pas encore d'évaluation

- MCS 012june2020Document8 pagesMCS 012june2020kk2760057Pas encore d'évaluation

- Introduction Microprocessors July 2005 OldDocument2 pagesIntroduction Microprocessors July 2005 OldPrasad C MPas encore d'évaluation

- Real Time Embedded Systems M TechDocument2 pagesReal Time Embedded Systems M Techammayi9845_930467904Pas encore d'évaluation

- B. C. A. (Fifth Semester) EXAMINATION, 2016-17: Note: All Questions Have To Be Attempted. Section-ADocument3 pagesB. C. A. (Fifth Semester) EXAMINATION, 2016-17: Note: All Questions Have To Be Attempted. Section-ARajeev GairolaPas encore d'évaluation

- 9A15502 Digital System DesignDocument4 pages9A15502 Digital System Designsivabharathamurthy100% (1)

- 2020 09 14SupplementaryCS405CS405 D Ktu QbankDocument3 pages2020 09 14SupplementaryCS405CS405 D Ktu QbankCigi ManojPas encore d'évaluation

- Evolutionary Algorithms for Mobile Ad Hoc NetworksD'EverandEvolutionary Algorithms for Mobile Ad Hoc NetworksPas encore d'évaluation

- KannadaDocument2 pagesKannadahaider_ali980Pas encore d'évaluation

- Practice DeshaDocument26 pagesPractice Deshahaider_ali980Pas encore d'évaluation

- Placement - 74-1Document25 pagesPlacement - 74-1haider_ali980Pas encore d'évaluation

- WDVP Assignment-Iii: 6. Student RegistrationDocument2 pagesWDVP Assignment-Iii: 6. Student Registrationhaider_ali980Pas encore d'évaluation

- 10IT29 Chetan Gupta Morgan Stanley ResumeDocument6 pages10IT29 Chetan Gupta Morgan Stanley Resumehaider_ali980Pas encore d'évaluation

- Tere Apne Shaher WaleDocument4 pagesTere Apne Shaher Walehaider_ali980Pas encore d'évaluation