Académique Documents

Professionnel Documents

Culture Documents

Funcionamiento PLD - Urigüen

Transféré par

fer6669993Titre original

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

Funcionamiento PLD - Urigüen

Transféré par

fer6669993Droits d'auteur :

Formats disponibles

INGENIERIA ELECTRNICA

CIRCUITOS DIGITALES AVANZADOS Alumnos: Cristian Urigen. Ciclo: Sptimo Grupo 1 Tema: Principio de funcionamiento de los PLD. Mtodos de programacin(ROM, PROM, EEPROM) Cmo funcionan las matrices de conexin. Principios de funcionamiento de un PLD. Un Dispositivo Lgico Programable (PLD) es un componente electrnico usado para construir circuitos digitales reconfigurables. A diferencia de una compuerta lgica que tiene una funcin fija, los PLDs salen de fbrica sin una funcin en especfico, por lo tanto necesitan ser programados o reconfigurados antes de poder ser usados. Los PLDs tienen varias ventajas. La primera es la habilidad de integracin, que permite integrar una gran cantidad de funcionalidad en un solo chip. Los PLDs eliminan el uso de mltiples chips as como la inconveniencia y desconfianza de usar cableado externo. La segunda ventaja es el hecho de poder cambiar el diseo. Muchos PLDs permiten ser reprogramados o reconfigurados. Existen dos ramas principales dentro de los dispositivos lgicos programables, la lgica programable de campo y la de fbrica. El trmino campo en este contexto implica que los dispositivos puedan ser programados en el campo del usuario, mientras que la lgica de fbrica puede ser programada en la misma fbrica donde se construyen, de acuerdo a los requerimientos del cliente. En este caso, la tecnologa de programacin usa procesos irreversibles, por lo que solo es posible hacerlo una vez. [1] Los PLD nos permiten automatizar procedimientos tediosos como tablas de verdad, expresiones booleanas y nos permite controlar interconexiones de compuertas lgicas mediante circuitos fsicos. Para llevar a cabo el funcionamiento de un PLD se debe tomar en cuenta las siguientes especificaciones de diseo [4]: En primer lugar se debe especificar la funcin que el circuito deseado debe realizar [4]. Se debe generar las ecuaciones booleanas que se requieren para implementar esa funcin [4].

En caso de poder simplificar ecuaciones booleanas se debe proceder con lo propuesto [4]. Generar un mapa de fusibles desde las ecuaciones booleanas [4]. Por ltimo se debe proceder a programar el dispositivo seleccionado, tomando en cuenta un chequeo continuo para evitar errores en el proceso de programacin [4].

Mtodos de Programacin (ROM, PROM, EEPROM). ROM

Estas memorias eran programadas mediante la destruccin de una matriz de diodos para realizar el almacenaje de datos, an ms las primeras memorias los datos de la misma deban ser grabados por el fabricante de la memoria con el consecuente costo y la poca seguridad debido a que alguien podra conocer los datos [2]. Las caractersticas fundamentales de las memorias ROM son: 1. Alta densidad: la estructura de la celda bsica es muy sencilla y permite altas integraciones. 2. No voltiles: el contenido de la memoria permanece si se quita la alimentacin. 3. Costo: dado que la programacin se realiza a nivel de mscaras durante el proceso de fabricacin, resultan baratas en grandes tiradas, de modo que el coste de fabricacin se reparte en muchas unidades y el coste unitario es baja. 4. Slo lectura: nicamente son programables a nivel de mscara durante su fabricacin.

Figura 3. Memoria PROM a nivel de circuito [3] PROM

La ROM programable consiste bsicamente en un arreglo de compuertas AND cableadas y un arreglo de compuertas OR. En estos dispositivos tenemos el arreglo de compuertas OR programable; as podemos generar cualquier funcin lgica posible de las variables de

entrada, sin embargo se vuelven poco prcticas cuando se tiene que atender a un gran nmero de entradas, debido a que se duplica el nmero de conexiones fusibles a medida que se agrega una entrada [2].

EEPROM

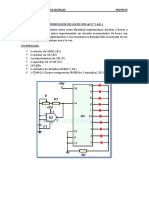

Es una memoria de slo lectura, la cual es programable y borrable electrnicamente, actualmente estas memorias se construyen con transistores de tecnologa MOS (Metal Oxide Silice) y MNOS (Metal Nitride-Oxide Silicon). Las celdas de memoria en las EEPROM son similares a las celdas EPROM y la diferencia bsica se encuentra en la capa aislante alrededor de cada compuesta flotante, la cual es ms delgada y no es fotosensible. Las memorias EEPROM al tener 2 transistores por celda hace que sean de baja densidad y mayor costo, para su programacin requiere de tiempos que oscilan entre 157microsegundos y 625microsegundos [2]. Funcionamiento de las matrices de conexin. Las matrices de interconexin programables PIM permiten unir los pines de entrada/salida a las entradas del bloque lgico o a las salidas de bloque lgico adems de permitir la conexin de entradas/salidas con bloque lgico diferente o incluso a las entradas del mismo bloque lgico la mayora de circuitos CPLD usan una de las dos configuraciones para la conexin entre matrices las cuales son conexiones mediante arreglos o interconexiones mediante multiplexores. La primera opcin se basa en una matriz de filas y columnas con una celda EECMOS en cada interseccin, al igual que en el GAL esta celda puede ser activada para conectar y desconectar la correspondiente fila y columna. Esta conexin permite una total interconexin entre las entradas y salidas de los bloques lgicos sin embargo estas ventajas provocan que se disminuya el desempeo del dispositivo adems de aumentar el consumo de energa y el tamao del componente. En la interconexin mediante multiplexores, existe un multiplexor para cada entrada al bloque lgico, las vas de interconexin programables son conectadas a las entradas son conectadas a las entradas de un nmero fijo de multiplexores por cada bloque lgico. Las entradas de seleccin de estos multiplexores son programadas para permitir que sea seleccionada nicamente una va de la matriz de interconexin por cada multiplexor la cual se prepara hacia el bloque lgico, estos multiplexores no tienen acceso a todas las vas de la matriz porque la rutabilidad se incrementa utilizando multiplexores de mayor tamao, permitiendo as que cualquier combinacin de seales de la matriz de interconexin pueda ser enlazada hacia cualquier bloque lgico sin embargo el uso de grandes multiplexores aumenta el tamao del dispositivo

Figura 2. Arquitectura bsica de los PLD Bibliografa: [1] Serafn Castaeda Cedeo, Dispositivos Lgicos Programables. U.N.A.M [2] Csar Arroyo Cabrera, Memorias programables. Universidad Nacional de Trujillo. [3] Mtodo de programacin EEPROM. [4] Dispositivos Lgicos Programables. IEC. Francisco Javier Torres.

Vous aimerez peut-être aussi

- UF0852 - Instalación y actualización de sistemas operativosD'EverandUF0852 - Instalación y actualización de sistemas operativosÉvaluation : 5 sur 5 étoiles5/5 (1)

- Micro 1Document126 pagesMicro 1Francisco Gomez100% (2)

- G1 ConversoresDocument61 pagesG1 Conversoresfer6669993Pas encore d'évaluation

- 04) Circuitos Integrados Lineales (Sesion 4-5) Amplificadores OperacionalesDocument40 pages04) Circuitos Integrados Lineales (Sesion 4-5) Amplificadores OperacionalesAnonymous LEDlCTPas encore d'évaluation

- Ejemplos de Programación LadderDocument6 pagesEjemplos de Programación Laddercarloshugolety100% (1)

- Bus Industrial Uni-TelwayDocument12 pagesBus Industrial Uni-TelwayHdgo Guerrero OrtizPas encore d'évaluation

- Circuitos 1.8 A 1.24Document8 pagesCircuitos 1.8 A 1.24Isabela VázquezPas encore d'évaluation

- Trabajo Bloque 1Document15 pagesTrabajo Bloque 1jake kawaiiPas encore d'évaluation

- 2.5 Clasificacion de Los PLCDocument10 pages2.5 Clasificacion de Los PLCjavier0% (1)

- PicDocument14 pagesPicxLMx LuNa7iicKzPas encore d'évaluation

- Práctica 2 ISA Ocho EjerciciosDocument6 pagesPráctica 2 ISA Ocho EjerciciosAlexPas encore d'évaluation

- Puertas LogicasDocument27 pagesPuertas LogicasJhojan CLPas encore d'évaluation

- Reporte de Examen V - Encendido de Focos Por ReléDocument21 pagesReporte de Examen V - Encendido de Focos Por ReléOscar Manuel Quiroz De La Vega50% (2)

- Especificaciones Técnicas de Los Tornos ConvencionalesDocument2 pagesEspecificaciones Técnicas de Los Tornos ConvencionalesGIMI2009Pas encore d'évaluation

- 01 Diagrama Escalera LadderDocument20 pages01 Diagrama Escalera LadderMarcoPas encore d'évaluation

- Linea de Tiempo McuDocument2 pagesLinea de Tiempo McuHévy PsicodeliaPas encore d'évaluation

- Reguladores de Voltaje Discretos e IntegradosDocument4 pagesReguladores de Voltaje Discretos e Integradoswilliam.123Pas encore d'évaluation

- Practica Sneu Matic ADocument24 pagesPractica Sneu Matic AAbraham Rodriiguez PerezPas encore d'évaluation

- Eeid - Eeid-510 - Formatoalumnotrabajofinal de ElectronicaDocument9 pagesEeid - Eeid-510 - Formatoalumnotrabajofinal de ElectronicaJean carlos OregonPas encore d'évaluation

- Caracteristicas de Los MicrocontroladoresDocument5 pagesCaracteristicas de Los MicrocontroladoresJavier Liverato100% (1)

- Ejercicios Maxima Transferencia de PotenciaDocument3 pagesEjercicios Maxima Transferencia de PotenciamichelyPas encore d'évaluation

- Reporte Arranque y Paro Con TimmerDocument14 pagesReporte Arranque y Paro Con TimmerClaudio Martinez CastroPas encore d'évaluation

- Micrologix 1000Document3 pagesMicrologix 1000SHOST WIPERPas encore d'évaluation

- PLC Bit, Byte y PalabraDocument2 pagesPLC Bit, Byte y Palabrajassiel233Pas encore d'évaluation

- Secuenciador de Luces Con 4017 y 4011Document6 pagesSecuenciador de Luces Con 4017 y 4011Daniel Steven CondorPas encore d'évaluation

- Reporte 5. Electroneumatica.Document51 pagesReporte 5. Electroneumatica.Abner Martinez100% (1)

- Familias LogicasDocument10 pagesFamilias LogicasroyfantasmaPas encore d'évaluation

- Cuestionario U5 Maquinas ElectricasDocument4 pagesCuestionario U5 Maquinas Electricaserik garciaPas encore d'évaluation

- Práctica 4 (Activación de Un SCR)Document9 pagesPráctica 4 (Activación de Un SCR)JairoPas encore d'évaluation

- Tipos de EncapsuladosDocument6 pagesTipos de EncapsuladoschivisalvaPas encore d'évaluation

- Parametros Del MosfetDocument13 pagesParametros Del MosfetJesus David Zapata Rodriguez50% (2)

- Cuestionario Equipo 2 OptoelectronicaDocument1 pageCuestionario Equipo 2 OptoelectronicaCésar CardenasPas encore d'évaluation

- Acoplamiento de ContadoresDocument9 pagesAcoplamiento de ContadoresAnonymous jv3i8NAPas encore d'évaluation

- Subestaciones eléctricas convertidorasDocument8 pagesSubestaciones eléctricas convertidorasYair Ordoñez CaroPas encore d'évaluation

- Ejercicio 1 Y 2Document25 pagesEjercicio 1 Y 2salvador0% (1)

- 4.1.3 Implementacion de Circuitos Combinacionales y Secuenciales en PLD Rios HernandezDocument3 pages4.1.3 Implementacion de Circuitos Combinacionales y Secuenciales en PLD Rios HernandezJazziel Issui Rios HernandezPas encore d'évaluation

- Ángulos de EulerDocument5 pagesÁngulos de Eulercarlos ballartaPas encore d'évaluation

- Ensayo PLCDocument8 pagesEnsayo PLCCachorro DlPas encore d'évaluation

- Practica de Microcontrolador 16F84Document21 pagesPractica de Microcontrolador 16F84Mario Prot MagañaPas encore d'évaluation

- Programador UniversalDocument37 pagesProgramador Universalvalentina salazarPas encore d'évaluation

- 2 Displays de 7 Segmentos INTRO. Automatizacion ARDUINO Y Proteus PDFDocument5 pages2 Displays de 7 Segmentos INTRO. Automatizacion ARDUINO Y Proteus PDFJovensonPokehPas encore d'évaluation

- Diodos semiconductores: características y modelos equivalentesDocument17 pagesDiodos semiconductores: características y modelos equivalentesIsrael AguilarPas encore d'évaluation

- Display SemaforoDocument5 pagesDisplay SemaforoEstebanPortillo0% (1)

- El CI 555 como temporizadorDocument6 pagesEl CI 555 como temporizadorNicolás F. QuirogaPas encore d'évaluation

- Estructura de Un RobotDocument3 pagesEstructura de Un RobotDaniel CastroPas encore d'évaluation

- Generador de Señal de Reloj Con 7400Document2 pagesGenerador de Señal de Reloj Con 7400LUIS SOTO100% (1)

- Deber de Lengua Alan CominaDocument5 pagesDeber de Lengua Alan CominaElizabeth CominaPas encore d'évaluation

- Newton EulerDocument32 pagesNewton EulerEduardo CoralPas encore d'évaluation

- 1 MicrocontroladoresDocument7 pages1 Microcontroladores1889312 Luis AlejandroPas encore d'évaluation

- Dispositivos PNPN y TiristoresDocument16 pagesDispositivos PNPN y TiristoresDeivid Quinde ConstantePas encore d'évaluation

- Capitulo 1Document48 pagesCapitulo 1ssecaesPas encore d'évaluation

- Tipos de Encapsulados de MicrocontroladoresDocument2 pagesTipos de Encapsulados de MicrocontroladoresDavid Juarez100% (1)

- Comportamiento de Los Transistores BJTDocument11 pagesComportamiento de Los Transistores BJTAlexisTamayoPas encore d'évaluation

- Reporte PLCDocument36 pagesReporte PLCfernando_fernaPas encore d'évaluation

- Manejo de Display de 7 Segmentos y 4 Dígitos MIKROCDocument2 pagesManejo de Display de 7 Segmentos y 4 Dígitos MIKROCArturo ZambranoPas encore d'évaluation

- REPORTE de LA PRÁCTICA - 6 (El Transistor Como Interruptor)Document8 pagesREPORTE de LA PRÁCTICA - 6 (El Transistor Como Interruptor)Lázaro VidalPas encore d'évaluation

- Despacho económico sistema eléctrico DigsilentDocument16 pagesDespacho económico sistema eléctrico DigsilentGabriel Barreda ZegarraPas encore d'évaluation

- Actividad2 Clases y ObjetosDocument7 pagesActividad2 Clases y Objetosdany MartinezPas encore d'évaluation

- Optoacopladores (CD CA)Document10 pagesOptoacopladores (CD CA)Jesús VázquezPas encore d'évaluation

- Dispositivos Lógicos ProgramablesDocument13 pagesDispositivos Lógicos ProgramablesNestor Victoria SantiagoPas encore d'évaluation

- Practica 2 Lab Dispos E-SDocument3 pagesPractica 2 Lab Dispos E-SDio SosaPas encore d'évaluation

- Practica 4Document3 pagesPractica 4fer6669993Pas encore d'évaluation

- Practica 6Document3 pagesPractica 6fer6669993Pas encore d'évaluation

- Principales Sensores de Un Vehículo ModernoDocument6 pagesPrincipales Sensores de Un Vehículo Modernofer6669993Pas encore d'évaluation

- Practica 6Document3 pagesPractica 6fer6669993Pas encore d'évaluation

- Polarización Fija SimulacioseDocument3 pagesPolarización Fija Simulaciosefer6669993Pas encore d'évaluation

- Circuito Generador de Corriente ConstanteDocument7 pagesCircuito Generador de Corriente Constantefer6669993Pas encore d'évaluation

- Ejemplo de AplicaciónDocument1 pageEjemplo de Aplicaciónfer6669993Pas encore d'évaluation

- Polarización Fija SimulacioseDocument3 pagesPolarización Fija Simulaciosefer6669993Pas encore d'évaluation

- Circuito Generador de Corriente ConstanteDocument7 pagesCircuito Generador de Corriente Constantefer6669993Pas encore d'évaluation

- Principales sensores vehículo moderno CTS ECT TPS ACT MAF MAP RPM O2 CKP KS CMP EGRT VVSDocument3 pagesPrincipales sensores vehículo moderno CTS ECT TPS ACT MAF MAP RPM O2 CKP KS CMP EGRT VVSUriel Trinidad PatracaPas encore d'évaluation

- Generador de Corriente ConstanteDocument1 pageGenerador de Corriente Constantefer6669993Pas encore d'évaluation

- Deflexión cuerda vibratoriaDocument2 pagesDeflexión cuerda vibratoriafer6669993Pas encore d'évaluation

- Cuarto Grupo de Preguntas de Ineval PDFDocument41 pagesCuarto Grupo de Preguntas de Ineval PDFamistasPas encore d'évaluation

- Lesiones Del TobilloDocument5 pagesLesiones Del Tobillofer6669993Pas encore d'évaluation

- AlarmaDocument5 pagesAlarmafer6669993Pas encore d'évaluation

- Filtro Iir Conversión de Filtros Analógicos BilinealDocument10 pagesFiltro Iir Conversión de Filtros Analógicos Bilinealfer6669993Pas encore d'évaluation

- Instructivo Permiso FuncionamientoDocument22 pagesInstructivo Permiso Funcionamientoands010Pas encore d'évaluation

- Principales sensores vehículo moderno CTS ECT TPS ACT MAF MAP RPM O2 CKP KS CMP EGRT VVSDocument3 pagesPrincipales sensores vehículo moderno CTS ECT TPS ACT MAF MAP RPM O2 CKP KS CMP EGRT VVSUriel Trinidad PatracaPas encore d'évaluation

- Presentación1 REDESDocument9 pagesPresentación1 REDESfer6669993Pas encore d'évaluation

- EthernetDocument14 pagesEthernetfer6669993Pas encore d'évaluation

- Ethernet IndustrialDocument17 pagesEthernet Industrialfer6669993Pas encore d'évaluation

- Ceraphant TDocument4 pagesCeraphant Tfer6669993Pas encore d'évaluation

- StopDocument4 pagesStopfer6669993Pas encore d'évaluation

- Presentación SCADADocument10 pagesPresentación SCADAfer6669993Pas encore d'évaluation

- Archivo Nuevo1 PDFDocument9 pagesArchivo Nuevo1 PDFfer6669993Pas encore d'évaluation

- P - 1. Nivel CapacitivoDocument13 pagesP - 1. Nivel Capacitivofer6669993Pas encore d'évaluation

- Archivo Nuevo1 PDFDocument9 pagesArchivo Nuevo1 PDFfer6669993Pas encore d'évaluation

- CLC 2Document2 pagesCLC 2fer6669993Pas encore d'évaluation

- AcondicionamientoDocument20 pagesAcondicionamientoAndres Jacob Sanchez JaraPas encore d'évaluation