Académique Documents

Professionnel Documents

Culture Documents

ASC 5 Nivelul Microprogramat

Transféré par

Alis Madalina EneCopyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

ASC 5 Nivelul Microprogramat

Transféré par

Alis Madalina EneDroits d'auteur :

Formats disponibles

5.

NIVELUL MICROPROGRAMAT

Sistemele de calcul sunt implementate folosind diferite concepte care le

apropie de gndirea uman. Se disting astfel mai multe niveluri de programare

ale unui calculator. n acest capitol se va studia nivelul microprogramat.

Functionarea microprocesorului si a oricrui bloc dintr-un sistem cu

microprocesor necesit date si semnale de comand si control. Succesiunea

dorit a evenimentelor din sistem (care conduce la executarea unei sarcini

utile) se produce prin actionarea corect, secvential, a semnalelor de

control, acestea conducnd la transferul corect de date, prelucrarea acestora

si luarea de decizii. n general, ns, datorit multitudinii acestor semnale si

a legturii lor intime cu structura intern a fiecrui bloc nu se lucreaz direct

cu semnale simple ci cu grupuri ale lor care au un efect mai usor de sesizat

din exterior. Astfel de grupuri de semnale sunt numite instruciuni si ele

sunt caracteristice logicii programate.

Din cele mentionate rezult c executarea unei instructiuni

presupune efectuarea ntr-o anumit ordine a unor pasi elementari care se

numesc microoperaii si microinstruciuni. Primele procesoare executau

codul direct la nivel hardware. Executia era destul de rapid (se accesa

direct nivelul 0 din nivelul 2), dar conceptul era lipsit de flexibilitate.

Aceasta se datora imposibilittii adugrii de instructiuni noi.

Fig. 5.1. Structur partial a nivelurilor unui calculator.

223

Practic s-a constatat c pentru executia oricrei instructiuni din setul

microprocesorului se execut o succesiune bine definit de pasi.

Microprogramarea este un concept care formeaz de fapt interfata ntre

limbajul de asamblare si structurile fizice ale procesorului. Microinstructiunile

sunt practic semnalele de comand adresate de unitatea de control ctre unitatea

de executie a procesorului. Aparitia nivelului microprogramat presupune

asocierea fiecrei instructiuni cu o succesiune de microinstructiuni.

5.1. Exemplu de main microprogramat

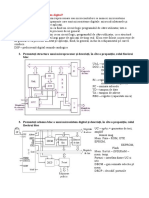

n figura 5.2 se prezint structura unei masini microprogramate.

Fig. 5.2. Structura unei masini microprogramate de tip A (mA).

224

Notatiile folosite n figura 5.2:

R1 R16: 16 registre generale de tip latch, fiecare de 16 biti, care

au functii diferite, registre inaccesibile utilizatorului; ele sunt

utilizate doar de masina microprogramat. Fiecare registru poate

depune date pe magistralele A, B si poate fi ncrcat de pe

magistrala C.

ALU: circuit logic combinational care realizeaz patru operaii

aritmetice i logice selectate de F0 si F1. Cele patru operatii sunt

A+B, AB, A, nonA. La iesire mai sunt disponibili doi biti notati cu

N si Z. Semnificatia lor este:

rezultatul din ALU este negativ N = 1;

rezultatul ALU este zero Z = 1.

registrul shift: este un circuit de deplasare a crui intrare este

legat la iesirea ALU si care poate executa urmtoarele operatii:

deplasare cu un bit la stnga/dreapta;

livrare direct la iesire a cuvntului aflat la intrare (stare

inactiv).

Aceste operatii sunt selectate de liniile de comand S0 si S1.

magistralele A si B sunt legate la ALU prin registrele tampon de

tip latch RTA si RTB (ALU este un circuit logic combinational, iar

intrrile lui trebuie tinute constante pe timpul unei operatii).

Registrele tampon sunt ncrcate prin liniile de comand L0 si L1.

Observaii:

Registrele tampon permit modificarea magistralelor A si B n

timpul unei operatii executate de ctre ALU. Rezult c pot avea

loc operatii ntre registre de tipul R1 R1 + R2, R2 R1 + R2

etc.;

Dac registrele R1 R16 ar fi de tip flip-flop, atunci nu ar mai

fi nevoie de registrele tampon.

RDA, RAD: registre care realizeaz conexiunea cu magistrala de

date, respectiv de adrese. RAD este ncrcat cu date de pe

magistrala B n acelasi timp cu efectuarea unei operatii de ctre

ALU. RDA este ncrcat de pe magistrala C atunci cnd se

activeaz semnalul M1. Semnalele M2 si M3 comand pozitionarea

continutului lui RDA pe magistrala de date (scriere n memorie) si

respectiv nregistrarea datelor de pe magistral n RDA (citire din

memorie). Datele ncrcate n RDA pot fi utilizate la o intrare a

unittii ALU prin semnalul de comand A0 care se aplic

multiplexorului.

225

5.2. Microinstruciunile

n exemplul prezentat anterior, microinstruciunile reprezint setul

de semnale care sunt primite de componentele unittii de executie a masinii

microprogramate. n total sunt 61 de linii de comand, dispuse n nou

grupe functionale, care execut comanda si controlul cii de date a masinii.

Aceste grupe sunt:

16 semnale pentru transferul de date din registrele R1 R16 pe

magistrala A, la un moment dat putnd fi selectat un singur registru

(n figura 5.2 nu au fost reprezentate aceste semnale);

16 semnale pentru transferul de date din registrele R1 R16 pe

magistrala B cu mentiunile anterioare;

16 semnale pentru transferul de date de pe magistrala C ntr-unul

din registrele R1 R16 (nici aceste semnale nu au fost

reprezentate pe schem din motive de spatiu);

dou semnale de comand a ncrcrii registrelor tampon RTA si

RTB, notate n figur cu L0 si L1;

dou semnale care selecteaz operatiile executate de ALU (F0 si

F1);

dou semnale de comand a registrului shift (S0 si S1);

patru semnale de comand a registrelor RDA si RAD (M0, M1, M2

si M3);

dou semnale care indic operatiile de scriere/citire n/din memoria

principal;

un semnal de comand pentru AMUX (A0).

Masina functioneaz secvential, fiind necesar un registru de

comand de 61 biti. Acest numr al semnalelor de comand este prea mare.

S-a ncercat reducerea lui prin selectarea registrelor R1 R16 cu ajutorul

unei linii de comand de 4 biti pentru fiecare magistral. Semnalele se obtin

apoi prin trei decodoare 4/16 care genereaz cele trei grupe de 16 semnale.

n felul acesta se economisesc 3 12 = 36 biti.

Procednd astfel, la fiecare pas trebuie ncrcat un registru. Situatia

nu este mereu avantajoas. De exemplu, este posibil executarea unei

operatii ALU doar pentru setarea semnalelor N si Z. De aceea se utilizeaz

un semnal suplimentar de validare a ncrcrii, VALC. Acesta ia valoarea 1

cnd valideaz ncrcarea si 0 cnd o interzice. VALC este legat de intrarea

de CS (Chip Select) a decodorului. Semnalele M2 si M3 pot informa n

exterior tipul operatiei (citire/scriere din/n memorie). n acest fel se

economisesc nc 2 biti.

226

Semnalele L0 si L1 sunt identice si sunt generate de ceasul intern al

sistemului. n fiecare perioad, L0 si L1 permit stocarea datelor pe

magistralele A si B. n concluzie, nu este necesar specificarea lor n

instructiuni. Rmn 61 36 2 2 + 1 = 22 biti suficienti pentru comanda

cii de date a micromasinii. n structura microinstructiunii vor intra astfel 22

biti de comand plus alti biti descrisi n continuare.

5.2.1. Structura unei microinstruciuni

O microinstructiune cuprinde mai multe prti, numite cmpuri,

fiecare cmp definind o functie proprie. Reprezentarea din figura 5.3 arat

structura unei microinstructiuni.

1 2 2 2 1 1 1 1 1 4 4 4 8

A

M

U

X

C

O

N

D

*

A

L

U

D

E

P

L

R

D

A

R

A

D

R

D

W

R

V

A

L

C

CBA

A

D

D

R

*

Fig. 5.3. Structura unei microinstructiuni (cmpuri si numr de biti alocat); * neprezentat.

Rezult un total de 22 + 2 + 8 = 32 biti. Semnificatia acestor biti este:

AMUX (1 bit) 0 intrare din RTA;

1 intrare din RDA.

ALU (2 biti) 0 A+B;

1 AB;

2 A;

3 nonA.

DEPL (2 biti) 0 fr deplasare;

1 deplasare la dreapta;

2 deplasare la stnga;

3 neutilizat.

RDA (1 bit) indic ncrcarea RDA cu cuvntul de pe magistrala C;

RAD (1 bit) indic ncrcarea RAD cu cuvntul din RTB;

RD (1 bit) indic citirea din memoria central;

WR (1 bit) indic scrierea n memoria central;

VALC (1bit) autorizeaz ncrcarea registrelor generale:

0 interdictie;

1 validare.

ncrcare/depunere de pe magistrala C/pe magistrala A sau B

(semnal pe 3 4 biti).

227

5.2.2. Execuia unei microinstruciuni

O instructiune cuprinde patru subcicluri de executie (este folosit un

ceas cu patru faze):

1. ncrcarea microinstructiunii care trebuie executat ntr-un registru

particular denumit registru microinstruciune RMI;

2. transferul continutului registrelor selectionate pe magistralele A, B

si ncrcarea datelor n RTA si RTB;

3. realizarea operatiilor ALU si ale registrului shift; dac este necesar,

RAD este ncrcat de la iesirea registrului tampon B;

4. ncrcarea datelor de la iesirea registrului shift n registrul

selectionat si/sau n registrul RDA.

Pn acum s-a prezentat calea de date a masinii. n cele ce urmeaz

se va analiza blocul care genereaz semnalele de comand

(microinstructiunile) pentru calea de date.

Schema ceasului si fazele semnalului de ceas sunt reprezentate n

figura 5.4.

Fig. 5.4. Fazele semnalului de ceas.

228

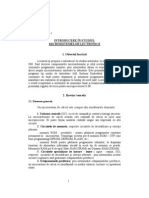

5.2.3. Unitatea de comand

Schema bloc a sistemului microprogramat este prezentat n figura

5.5. Unitatea de comand preia codul n limbaj de asamblare si comand calea

de date prezentat anterior. Componentele sale sunt descrise n continuare.

Memoria de microprogram se mai numeste memorie de comand

(exist ns diferente ntre memoria de program si cea de microprogram).

Memoria de microprogram este o memorie foarte rapid care contine

instructiuni microprogramate. Pentru majoritatea micromasinilor, memoria

de microprogram este de tip read-only; exist si posibilitatea utilizrii

memoriei de tip read-write, ceea ce confer posibilitatea modificrii

dinamice a programului.

Fig. 5.5. Schema bloc a unittii de comand.

n exemplul anterior. microinstructiunile sunt de 32 de biti. Exist

256 de microinstructiuni, ceea ce necesit 8 biti de adres (asa se explic

cmpul ADDR de 8 biti n structura cmpurilor microinstructiunii). Cele

256 de microinstructiuni cer o memorie de 8192 biti (256 instructiuni 32

biti). Fiecare microinstructiune execut dou functii:

controleaz functionarea cii de date;

genereaz adresa pentru microinstructiunea urmtoare.

Asa cum s-a artat, formatul microinstructiunilor contine cmpuri de

control pentru fiecare resurs hardware a masinii.

Secveniatorul de microprogram primeste de pe calea de date

starea curent a acesteia prin bitii de stare (starea este dat de semnalele N si

Z). Secventiatorul de microprogram are rolul de a adresa urmtoarea

Control adres urmtoare

Adres microprogram

Secventiator de

microprogram

Memorie de

microprogram

Calea de date

Stare Control

229

microinstructiune, n functie de starea cii de date si de bitii de control ai

adresei urmtoare, care sunt dati la rndul lor de cmpurile COND si ADDR

din microinstructiune. Prin linia de adres a microprogramului se selecteaz

instructiunea care este depus pe intrarea de control a cii de date.

Astfel, semnificatia cmpului COND este urmtoarea:

COND (2 biti) 0 se execut urmtoarea microinstructiune;

1 salt la adresa specificat de ADDR dac N = 1;

2 salt la adresa specificat de ADDR dac Z = 1;

3 salt neconditionat la ADDR.

Schema general a micromasinii este dat n figura 5.6. Notatiile

folosite sunt urmtoarele:

MCO = microcontor (registru de adresare a memoriei de

microprogram);

INCR = circuit de incrementare (INCR = MCO + 1);

MMUX = multiplexor care lucreaz n concordant cu decizia

provenit de la microsecventiator; el va alege pentru

microinstructiunea urmtoare fie adresa MCO + 1, fie

adresa specificat n ADDR.

Fig. 5.6. Schema bloc a unei micromasini (schema modificat pentru mA).

230

ncrcarea datelor de pe magistrala C ntr-unul din cele 16 registre

generale nu este posibil dect atunci cnd se ndeplinesc urmtoarele conditii:

1. VALC = 1;

2. subciclul curent de ceas este 4 (44 activ);

3. registrul este indicat de cmpul C al microinstructiunii.

5.2.4. Modul de lucru al microsecveniatorului

Ecuatia logic a microsecventiatorului este:

O(s) = DN + SZ + SD,

unde:

O(s) = iesirea microsecventiatorului;

D = bitul dreapta al cmpului COND;

S = bitul stnga al cmpului COND;

N, Z = semnale de stare generate de ALU (negativ si zero).

Cnd O(s) = 1 are loc schimbarea adresei microinstructiunii

urmtoare cu adresa dat de cmpul ADDR din instructiunea curent.

5.3. Microprogramarea orizontal i vertical

Diferenta major ntre aceste dou tehnici de microprogramare este

dat de modul de codare a microinstructiunii.

Se presupune c pentru comanda masinii mA sunt necesare n

semnale. Cnd microinstructiunile contin n biti, cte un bit pentru fiecare

microcomand, ele sunt denumite microinstructiuni n format orizontal.

Exemplu. n cazul micromasinii mA s-ar fi putut renunta la

utilizarea decodoarelor pentru magistralele A, B sau C. De asemenea, ALU

ar fi putut s nu contin un decodor intern pentru cele patru operatii

executate. n acest caz, pentru fiecare ncrcare de pe/pe magistral ar fi fost

nevoie de 16 biti n loc de 4, iar la ALU ar fi fost nevoie de 4 biti n loc de 2

(vezi cmpul ALU n formatul de microinstructiune prezentat).

Deci la una din extremittile formatului microinstructiunilor se afl

formatul orizontal, n care fiecare bit semnific o microcomand. n

consecint, microinstructiunea contine multi biti.

La cealalt extremitate se afl formatul vertical, n care

microinstructiunile contin un numr mic de biti (<< n), ns cmpurile

microinstructiunii sunt puternic codate. Dac n microprogramarea orizontal

231

un microprogram necesit putine instructiuni cu multi biti, n programarea

vertical acelasi microprogram necesit multe instructiuni cu putini biti.

n practic se ntlnesc formate mixte, cum este cel prezentat n

exemplul micromasinii mA, situat ntre cele dou extremitti. Astfel, la

formatul prezentat se ntlnesc cmpuri asociate direct microcomenzilor (de

exemplu, RAD, RDA, AMUX, RD, WR), care au un efect imediat asupra

circuitelor micromasinii. ns se ntlnesc, de asemenea, si cmpuri de biti

codate (de exemplu, ALU, A, B, C), care necesit utilizarea unui decodor

nainte de aplicarea pe circuitele corespunztoare.

5.3.1. Micromaina cu format vertical

Microinstructiunea vertical tipic contine un cmp numit codul

operaiei (care poate fi vzut ca o generalizare a cmpului ALU) si mai

multe cmpuri de operanzi, de exemplu: A, B, C. Pentru a clarifica distinctia

ntre microprogramul orizontal si cel vertical, se va revizui micromasina

mA, utiliznd de aceast dat microinstructiuni verticale. Fiecare nou

microinstructiune va cuprinde trei cmpuri de 4 biti, deci un total de 12 biti

fat de 32 de biti la versiunea precedent.

Primul cmp este codul operatiei (COP) care arat ce trebuie s fac

microinstructiunea. Celelalte cmpuri sunt registrele R1 si R2.

Microinstructiunile de salt regrupeaz registrele R

1

si R

2

pentru a forma un

cmp de 8 biti (fie acesta R).

n tabelul 5.1 este prezentat codul operatiei (fiecare tip de

microinstructiune).

Se observ c fiecare microinstructiune nu realizeaz dect o singur

operatie si c cei 12 biti ai microinstructiunii sunt suficienti pentru a

specifica o operatie la un moment dat. Corespunztor, masina se modific si

rezult micromasina mB, n conformitate cu schema din figura 5.7.

Se constat c la cele dou scheme cile de date sunt identice. n

schimb, la micromasina cu format vertical nu sunt utilizate dect dou

decodoare 4 la 16 pentru R1 si R2 n locul celor trei decodoare A, B, C din

schema anterioar. De asemenea, n schem apar trei elemente noi: blocul

SI, blocul NZ si decodorul COP.

Blocul I contine 16 porti SI care permit cmpului R

1

, dup

traversarea decodorului R

1

, s comande golirea unui registru pe magistrala

A si ncrcarea sa pe magistrala C. Desigur c aceste operatii nu pot fi

simultane. De aici necesitatea portilor SI care determin n timpul

subciclului 4 ncrcarea unui registru cnd aceast operatie este validat de

decodorul COP.

232

Tabelul 5.1

Codul operaiei pentru microinstruciunile n format vertical

Binar Simbol Descriere Operaie

0000 ADD adunare R1 = R1 + R2

0001 AND SI logic R1 = R1 R2

0010 MOVE deplasare R1 = R2

0011 COMPL complement R1 = inv(R2)

0100 SHIFTL deplasare stnga R1 = shiftleft(R2)

0101 SHIFTR deplasare dreapta R1 = shiftright(R2)

0110 GETRDA ncrcare R1 cu RDA R1 = RDA

0111 TEST test registru if R2 < 0 then N = true

if R2 = 0 then Z = true

1000 BEGRD nceput RD RAD = R1; RD

1001 BEGWR nceput WR RAD = R1; RDA = r2; WR

1010 CONRD continuare RD RD

1011 CONWR continuare WR WR

1100 LIBER

1101 NJUMP salt dac N = 1 if N then go to R

1110 ZJUMP salt dac Z = 1 if Z then go to R

1111 UJUMP salt neconditionat go to R

Observaie: R = l6R1 + R2.

Blocul NZ este un registru de 2 biti care nregistreaz semnalele N si

Z la iesirea ALU, cnd aceast nregistrare este ordonat de decodor. Acest

artificiu este utilizat deoarece pe micromasina B nu este realizat dect o

singur operatie n timpul unei microinstructiuni. Astfel, testarea si

utilizarea bitilor N si Z se face doar n microinstructiunea urmtoare, deci

este necesar o pstrare a lor n registru.

Decodorul COP reprezint elementul central al micromasinii.

Acesta analizeaz codul operatiei si precizeaz actiunile care se vor

ntreprinde. Decodorul COP distribuie 13 microcomenzi distincte ctre

blocul SI, microsecventiator, registrul NZ, AMUX, ALU, circuitul shift,

RAD si RDA. Pentru fiecare din cele 16 coduri de operatii posibile trebuie

determinat care dintre cele 13 microcomenzi sunt active (1) si care sunt n

repaus (0).

233

Fig. 5.7. Structura micromasinii cu format vertical (mB).

Rezult astfel un tablou 16 13, prezentat n tabelul 5.2.

Dac se numeroteaz cei patru biti care codeaz microinstructiunea

cu A, B, C si D, atunci se pot obtine, dup minimizare, urmtoarele functii

logice (ideal pentru implementare este un PLA cu 4 intrri si 13 iesiri):

ALUA = ABCD + ABCD + ABCD+ ABCD + ABCD + ABCD +

+ ABCD + ABCD +ABCD + ABCD + ABCD =

= C + AB + AB + AD

ALUB = ABCD + ABCD = ABD

SHIFTA = ABCD

SHIFT B = ABCD

NZ = ABCD + ABCD + ABCD + ABCD + ABCD + ABCD +

+ ABCD + ABCD = A

234

AMUX = ABCD

I = ABCD + ABCD + ABCD + ABCD + ABCD + ABCD +

+ ABCD = AB + AC + AD

RAD = ABCD + ABCD = ABC

RDA = ABCD

RD = ABCD + ABCD = ABD

WR = ABCD + ABCD = ABD

MSA = ABCD + ABCD = ABC

MSB = ABCD + ABCD = ABD

Tabelul 5.2

Corespondena microinstruciuni-microcomenzi la micromaina cu format vertical

in-

struc-

iuni

c

o

m

e

n

z

i

A

L

U

A

A

L

U

B

S

H

I

F

T

A

S

H

I

F

T

B

N

Z

A

M

U

X

S

I

R

A

D

R

D

A

R

D

W

R

M

S

A

M

S

B

0 ADD + +

1 AND + + +

2 MOVE + + +

3 COMPL + + + +

4 SHIFTL + + + +

5 SHIFTR + + + +

6 GETRDA + + + +

7 TEST + +

8 BEGRD + + +

9 BEGWR + + + +

10 CONRD + +

11 CONWR + +

12 LIBER

13 NJUMP + +

14 ZJUMP + +

15 UJUMP + + +

235

5.3.2. Comparaie ntre cele dou microprograme

Micromasina mA are un format mixt, continnd att cmpuri

verticale ct si cmpuri orizontale, pe cnd micromasina mB are un format

vertical.

Exemplu. n cazul n care microprogramul ar fi utilizat pentru

interpretarea unui numr de 23 de tipuri de macroinstructiuni, atunci

microprogramul micromasinii mA ar trebui s aib 79 microinstructiuni a

cte 32 biti, rezultnd 2528 de biti n memoria de microprogram. n schimb,

microprogramul micromasinii mB contine 160 microinstructiuni a 12 biti,

rezultnd n total 1920 de biti. Se obtine astfel un cstig de 24% n

capacitate de memorie, deci o diminuare a costului de implementare pentru

al doilea caz (micromasina mB cu structur vertical).

Inconvenientul major al formatului vertical este dat de numrul

important de microinstructiuni care trebuie executate pentru interpretarea

unei macroinstructiuni. Aceasta se traduce ntr-o diminuare net a vitezei

micromasinii. Din acest motiv, calculatoarele mari si rapide utilizeaz

microprogramarea orizontal. n schimb, masinile mai modeste utilizeaz

microprogramarea vertical pentru simplitate si pret de cost mai mic.

ntr-adevr, microprogramarea vertical permite scrierea usoar a

microprogramului, deoarece fiecare linie de microprogram reprezint o

singur operatie. Microprogramul este mult mai lizibil dect la

microprogramarea orizontal, unde o microinstructiune reprezint operatii

multiple.

n ultimul timp, cnd competitia dintre arhitecturile RISC si CISC a

fost eliminat, se poate spune acelasi lucru si despre formatele vertical si

orizontal pentru microinstructiuni.

5.3.3. Analiza comparativ a sistemelor microprogramate

Microcod vs VLIW (Very Long I nstruction Word) i RISC

Procesoarele proiectate propice, microcodate puternic cu instructiuni

complexe au luat nastere la nceputul anilor 1960 si au continuat pn la

mijlocul anilor 1980. La acel punct, filozofia proiectrii RISC-ului a nceput

s devin mai proeminent. Aceasta a inclus punctele:

Analiz arat c instructiunile complexe sunt folosite rar, ntruct

resursele masinilor necesare lor sunt risipite foarte mult.

Programarea s-a ndeprtat foarte mult de nivelul de asamblare, deci

nu se mai merit s furnizezi instructiuni complexe din motive de

productivitate.

236

Resursele masinilor necesare pentru instructiunile complexe, rar

folosite, sunt utilizate mai bine pentru accelerarea performantei

instructiunilor simple (folosite n mod obisnuit).

Instructiunile complexe microcodate, care necesit multe si diverse

cicluri ceas, sunt dificil de actualizat pentru cresterea performantei.

Seturile de instructiuni simple permit executii directe ale hardware-

ului, evitnd penalizarea performantei a executiei microcodate.

Ar trebui mentionat c exist la fel de bine si puncte-contor:

Instructiunile complexe din implementrile dificil microcodate pot

s nu ia multe extra-resurse ale masinilor (cu exceptia spatiului

microcodului); de exemplu, aceeasi ALU este utilizat des pentru a

calcula adrese efective precum si s calculeze rezultatele operanzilor

actuali.

Instructiunile non-RISC, care implic operanzi directi de memorie,

sunt folosite frecvent de ctre compilatorii moderni, chiar si stivele

de operatii aritmetice (ex. rezultatul memoriei) sunt de obicei

ntrebuintate. Desi asemenea operatii de memorie, de multe ori cu

decodri cu lungimi variate, sunt mai greu de actualizat, este pe

deplin fezabil, exemplificndu-se n mod limpede prin Intel 486,

Cyrix 6x86 etc.

Instructiunile non-RISC ndeplinesc, n mod firesc, mai mult munc

pe instructiune (n medie) si de asemenea de obicei sunt extrem de

codate; asa c permit dimensiuni exterioare mai mici ale aceluiasi

program, iar astfel o utilizare mai bun a memoriilor cache limitate.

Implementrile CISC (Complex Instruction Set Computer) moderne

cel mai remarcabil x86 ndeplinesc cele mai multe instructiuni si

toate modurile de adresare n hardware; microcodul este nc

folosit, pentru cteva instructiuni extrem de complexe sau foarte

speciale (precum CPUID CPU Identification) precum si pentru

housekeeping intern.

Multe procesoare RISC si VLIW sunt proiectate s execute fiecare

instructiune (ct timp este n cache) ntr-un singur ciclu. Acesta este foarte

similar modului n care CPU-urile cu microcod execut o microinstructiune

pe ciclu. Procesoarele VLIW au instructiuni care se comport similar

microcodului orizontal, cu toate c nu au un asemenea control

microgranular asupra hardware-ului precum asigur microcodul.

Instructiunile RISC sunt uneori similare limitatului microcod vertical.

237

5.4. Nanoprogramarea

Pn acum, discutnd despre microprograme, s-a presupus existenta

unei memorii principale (care contine instructiunile nivelului 2) si a unei

memorii de comand (care contine microprogramul).

O a treia memorie, denumit nanomemoria, permite n unele cazuri

o asociere optim ntre microprogramul orizontal si cel vertical Astfel,

nanoprogramarea corespunde unei optimizri statistice a microprogramului,

n cazul n care un set de instructiuni este mai des solicitat. n figura 5.8 este

reprezentat (prin comparatie cu microprogramarea) conceptul de

nanoprogramare.

n cazul a), microprogramul contine n microinstructiuni a cte w biti,

rezultnd capacitatea unei memorii de comand de nw biti. Se presupune c

o analiz detaliat a microprogramului arat c dintre cele 2

w

posibilitti de

reprezentare sunt utilizate doar m << n instructiuni.

n cazul b) s-a construit o nanomemorie de m cuvinte a cte w biti

care contine cele m microinstructiuni mai des utilizate. Atunci fiecare

microinstructiune a microprogramului original poate fi nlocuit n memoria

de comand prin adresa cuvntului din nanomemorie care contine

nanoinstructiunea corespunztoare, rezultnd ltimea cuvntului n memoria

de comand de log

2

m biti.

w log

2

m

n

w

m

a) b)

Fig. 5.8. a) Microprogramare conventional; b) microprogramare si nanoprogramare.

Exemplu. Fie un microprogram de nw = 4096 100 biti cu m = 128

de instructiuni diferite folosite mai frecvent. Rezult o nanomemorie avnd

nanoprogram

micro-

program

microprogram

238

mw = 128 100 biti si o memorie de comand de n log

2

m = 4096 7 biti.

Cstigul fat de microprogramarea conventional este de:

(4096 100) (4096 7) (128 100) = 368 128 biti.

Economia de memorie este realizat n contextul unei reduceri

sensibile de vitez. Datorit faptului c un ciclu de extragere a

microinstructiunii necesit dou accese la memorie (memoria de comand si

nanomemorie), masina nanoprogramat este mai lent dect masina

microprogramat. Din acest considerent, n ultimul timp s-a folosit din ce n

ce mai rar conceptul de nanoprogramare.

5.5. Exemplu de sistem microprogramat AMD

5.5.1. Uniti de execuie integrate

Unitatile de executie se prezinta sub forma unor circuite integrate pe scara

medie/larga. De regula ele sunt structurate transe de biti astfel incat, prin

concatenare si prin utilizarea unor circuite aditionale, se pot construi sisteme de

prelucrare pentru date organizate pe 4, 8, 16, 24, 32, 48 sau 64 de biti. Unittile de

executie integrate s-au comercializat n asociatie cu unittile de comand

corespunztoare si cu o serie de circuite aditionale, formnd ceea ce se cheam

microprocesoare pe transe de biti, microprocesoare bit-slice, microprocesoare

multi-chip etc.

Printre cele mai rspndite familii de microprocesoare bit-slice s-au aflat si

cele produse de compania Advanced Micro Devices, sub numele de AMD 2900.

Unitatea de executie AMD 2901 este organizat pe transe de 4 biti/circuit si este

prevzut cu elementele necesare cuplrii n cascad. Semnalele de comand se

aplic sub forma unor vectori binari la terminalele circuitului, fiind, de regul,

preluate sub controlul unui circuit micro-secventiator integrat (AMD 2909, 2911)

de la o memorie cu continut permanent.

In cele ce urmeaza va fi prezentata unitatea de executie AMD 2901 sub

aspect structural si functional.

5.5.2. Unitatea de execuie AMD 2901

Unitatea de executie AMD 2901 este organizata pe transe de 4 biti/circuit

si este prevazuta cu elementele necesare cuplarii in cascada.

Semnalele de comanda se aplica sub forma unor vectori binari la

terminalele circuitului, fiind, de regula, preluate sub controlul unui circuit micro-

secventiator integrat (AMD 2909, 2911) de la o memorie cu continut permanent.

239

Aceasta solutie se foloseste in cazul unitatilor de comanda microprogramate.

Uneori, pentru a mari viteza de operare, in locul unitatii de comanda

microprogramate se utilizeaza automate conventionale cu porti, bistabile si registre.

Unitatea de executie AMD 2901 dispune de urmatoarele resurse:

- un ansamblu de 16 registre generale de cite 4 biti, organizate sub forma unei memorii

RAM biport, cu doua intrari de adrese, o intrare de date si doua iesiri de date;

- o unitate aritmetica-logica, cu transport anticipat, capabila sa efectueze 3 operatii

aritmetice binare si 5 operatii logice si sa genereze, atit indicatorii de conditii:

depasire, zero, semn, transport (Cn+4), cat si conditiile de propagare (P) si

generare(G) ale transportului, la nivelul intregului circuit;

- un selector de date pentru cele doua intrari ale unitatii aritmeticelogice, care pot

reprezenta combinatii intre iesirile memoriei biport (A,B), o intrare externa de date

(D), constanta "zero" si iesirea unui registru su plimentar-extensie (Q);

- un selector de iesire din circuit, care furnizeaza prin intermediul unor tampoane

TS fie datele de la iesirea A, a memoriei biport, fie datele de la iesirea UAL;

- un registru auxiliar-extensie (Q), care poate fi incarcat fie cu datele de la iesirea

UAL, fie cu propriul sau continut deplasat stanga/dreapta prin intermediul unei

retele logice de deplasare-multiplexor QSHIFT;

- o retea de deplasare-multiplexor RAMSHIFT, plasata pe intrarea B a memoriei

RAM biport.

Indicatorii de conditii trebuie stocati intr-un registru dupa fiecare operatie

efectuata de UAL.

Intrarile R si S ale UAL sunt preluate de la iesirile unui circuit selector

(Selector sursa UAL), care sub controlul semnalelor I0:2, din intrarile D (Date

externe), A, B, 0 si Q, poate furniza combinatiile AB;AD; AQ; A0; DQ; D0; Q0;

BD; BQ; B0. In tabelul 5.3 se prezinta selectia surselor de operanzi pentru UAL.

Tabelul 5.3. Selectia surselor de operanzi pentru UAL

Microcod Sursa

Mnemonica

I

2

I

1

I

0

Codul

octal

R S

AQ

AB

ZQ

ZB

ZA

DA

DQ

DZ

0 0 0

0 0 1

0 1 0

0 1 1

1 0 0

1 0 1

1 1 0

1 1 1

0

1

2

3

4

5

6

7

A Q

A B

0 Q

0 B

0 A

D A

D Q

D Z

Figura 5.9 prezinta schema bloc a circuitului AMD 2901. Unitatea

aritmetica-logica poate efectua sub controlul semnalelor I3:5 trei operatii aritmetice

binare si cinci operatii logice asupra operanzilor aplicati la intrarile R si S.

240

Fig. 5.9. Schema bloc a circuitului AMD 2901.

Intrarea directa D este folosita pentru a introduce date in circuit, in RAM si

in registrul Q. Registrul Q este utilizatin operatiilede inmultire si impartire, ca

extensie sau ca acumulator/registru in unele aplicatii.

9 biti

I

8:6

I

5:3

I

2:0

Destinatie UAL Functie UAL Sursa UAL

8 7 6 5 4 3 2 1 0

Fig. 5.10. Structura vectorului de comanda (Microcodul I

8:0

).

241

Campul "Destinatie UAL" din vectorul de comanda are o semnificatie

complexa prin faptul ca specifica:

- operarea RAM (deplasare/incarcare/inactiv);

- operarea registrului Q (deplasare/incarcare/inactiv);

- conexiunile la RAMSHIFT (RAM0 si RAM3);

- conexiunile la QSHIFT (Q0 si Q3);

- iesirea Y.

Cuvantul (microinstructiunea) de comanda al unitatii de executie va avea

structura din figura 5.11.

23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

I

8

I

7

I

6

I

2

I

1

I

0

C

n

I

5

I

4

I

3

A

3

A

2

A

1

A

0

B

3

B

2

B

1

B

0

C

3

C

2

C

1

C

0

M

U

X

1

Selectie

destinatie

M

U

X

2

Selectie

sursa

Operatie

UAL

Adresa

A

Adresa

B

Adresa

C

Fig. 5.11. Cuvntul de comand al unittii de executie.

Se poate observa ca microinstructiunea care controleaza unitatea de

executie poseda 24 de biti. Bitii 0,..,3 au aparut ca urmare a inglobarii datei in

microinstructiune (microinstructiune cu operand imediat). Campul D se va extinde

in incrementi de 4 biti odata cu extinderea lungimii cuvantului prelucrat de catre

unitatea de executie. Campul Cn este asociat cu transportul in rangul cel mai putin

semnificativ al unitatii de executie, fiind la latitudinea celui care scrie

microprogramul.

5.5.3. Unitatea de comanda integrata. Secventiatorul de microprogram

AMD 2909

Secventiatorul de microprogram AMD 2909 face parte din familia de

circuite AMD2900 si constituie elementul de baza in jurul caruia este organmizata

unitatea de comanda microprogramata.

Dupa cum s-a aratat in paragraful anterior, atat unitatea de executie AMD

2901, cat si circuitele asociate acesteia sunt controlate cu ajutorul unui vector de

comanda constituit din campuri de biti, cu functii bie precizate. Un asemenea

vector controleaza operatii aritmetice elementare, care se pot efectua pe durata unei

perioade de ceas. Vectorul semnalelor de comanda poate fi generat cu ajutorul unui

circuit secvential, in cazul unitatilor de comanda conventionale, sau extras dintr-o

memorie cu continut permanent, in cazul unitatilor de comanda microprogramate.

Operatiile cu caracter complex, printre care se numara si instructiunile

calculatoarelor conventionale, se implementeaza sub forma unor secvente de

vectori de comanda. In sistemele microprogramate aceste secvente sunt stocate

intr-o memorie de control sau memorie de microprograme.

242

Un cuvant al memoriei de control reprezinta un vector de comanda sau o

microinstructiune. Secventiatorul de microprogram, structurat pe transe de cate 4

biti, este destinat generarii adreselor de microinstructiuni si asigurarii inlantuirii

acestora. Secventiatorul, prezentat mai jos, are ca resurse hardware:

- Contorul de MicroProgram (CMP);

- Registrul de Ramificare (RR);

- Indicatorul de Stiva (IS);

- STiVa (STV) cu capacitate de 4 cuvinte x 4 biti;

- INCrementatorul (INC);

- MultipleXorul (MUX) 4 x (4 : 1);

Fig. 5.12. Unitatea de comanda (schema bloc)

Schema bloc a unitatii de comanda va contine, pe langa microsecventiator,

si elementele necesare realizarii unei unitati de comanda:

- Memoria de Microprogram (MM);

- Registrul MicroInstrucriunii (RMI);

- un Comutator de Adrese (CA);

- o memorie de tip PROM.

243

Secventierea microinstructiunilor este realizata prin controlul circuitului

2909 cu ajutorul semnalelor preluate din campurile de control ale

microinstructiunii si de la conditiile externe.

Fig. 5.13. Schema bloc AMD 2909.

Se poate observa, in schema bloc din figura 5.13, faptul ca intrarea R a

microsecventiatorului este preluata direct de la iesirea memoriei de comanda, fara a

mai fi stocat in prealabil in registrul microinstructiunii RMI.

Vous aimerez peut-être aussi

- Proiectarea Microsistemelor DigitaleDocument34 pagesProiectarea Microsistemelor DigitaleIulia Casapu100% (1)

- SCADADocument12 pagesSCADAAdrian FilipPas encore d'évaluation

- L3 Transmisia Seriala UART USARTDocument17 pagesL3 Transmisia Seriala UART USARTAdriana ZestroiuPas encore d'évaluation

- Raportul La Proiectul de AnDocument25 pagesRaportul La Proiectul de AnIon BnPas encore d'évaluation

- Curs z80 NouDocument23 pagesCurs z80 NouBarbieru BarbalataPas encore d'évaluation

- Intel 8080Document15 pagesIntel 8080Maxim MirzencoPas encore d'évaluation

- ArhitecturiDocument9 pagesArhitecturiLucia NegruPas encore d'évaluation

- Carte AMP (93pag)Document93 pagesCarte AMP (93pag)Alex VladPas encore d'évaluation

- Laborator Si Curs APDocument26 pagesLaborator Si Curs APBeatrice FiranPas encore d'évaluation

- Microprocesoare - Z80Document21 pagesMicroprocesoare - Z80Dragos TPas encore d'évaluation

- PMD SubiecteDocument22 pagesPMD SubiecteAdriana PadurePas encore d'évaluation

- Proiect Comunicatii de DateDocument9 pagesProiect Comunicatii de DateTanase AlexandruPas encore d'évaluation

- L6a Masina Microprogramata Tanenbaum Mic-1Document10 pagesL6a Masina Microprogramata Tanenbaum Mic-1Bianca PopescuPas encore d'évaluation

- Indrumar6.1 - Nivel MicroDocument20 pagesIndrumar6.1 - Nivel MicroP Razvan StefanPas encore d'évaluation

- Curs 3 Arhitectura ADSP 2181Document19 pagesCurs 3 Arhitectura ADSP 2181Sanda RuxandraPas encore d'évaluation

- 2 Magistrale PDFDocument14 pages2 Magistrale PDFAndrei VieruPas encore d'évaluation

- Curs AMP - 14Document8 pagesCurs AMP - 14Aurelian MartiniPas encore d'évaluation

- Micro ControllerDocument13 pagesMicro ControllerCatalin LazarPas encore d'évaluation

- SEP - TMS320C10 - Cap13Document21 pagesSEP - TMS320C10 - Cap13Mops LightPas encore d'évaluation

- Arhitectura Calculatoarelor: Capitolul 3 Unitatea Centrală de PrelucrareDocument28 pagesArhitectura Calculatoarelor: Capitolul 3 Unitatea Centrală de PrelucrareMindhunter GamerPas encore d'évaluation

- Programabile 3Document15 pagesProgramabile 3sorin092004Pas encore d'évaluation

- Unitatea de Comanda Si Control PDFDocument20 pagesUnitatea de Comanda Si Control PDFNatalia MadanPas encore d'évaluation

- Divizor Numarator I8253fDocument13 pagesDivizor Numarator I8253fStana AlinPas encore d'évaluation

- Curs 5.12 UCC PDFDocument13 pagesCurs 5.12 UCC PDFBezmanGeorgePas encore d'évaluation

- Curs PIC UriDocument42 pagesCurs PIC UriRadu ConstantinPas encore d'évaluation

- Curs 2 - PrezentareDocument43 pagesCurs 2 - PrezentareCosti AndreiPas encore d'évaluation

- LaboratorSM 1 2 3Document28 pagesLaboratorSM 1 2 3Felice LazarPas encore d'évaluation

- HJGHBNJȘKHJKNNDocument29 pagesHJGHBNJȘKHJKNNCS:GO cFGPas encore d'évaluation

- Caracteristici RISC, UltraSPARC II Si MagistraleDocument9 pagesCaracteristici RISC, UltraSPARC II Si MagistraleRoccoSuasitoPas encore d'évaluation

- Laborator 1Document12 pagesLaborator 1Ceban VladislavPas encore d'évaluation

- Subiecte SI 2012Document6 pagesSubiecte SI 2012Ioana Raluca TiriacPas encore d'évaluation

- CristianAxenie Assembly Programming Course LabDocument403 pagesCristianAxenie Assembly Programming Course LabMu sicPas encore d'évaluation

- Lab.1 MPDocument10 pagesLab.1 MPCristinaPas encore d'évaluation

- UPUS ExamenDocument17 pagesUPUS ExamenAlexandru PiscaPas encore d'évaluation

- Sumatorul SerieDocument13 pagesSumatorul SerieMariana CiceuPas encore d'évaluation

- Informatica IndustrialaDocument32 pagesInformatica Industrialajean4444Pas encore d'évaluation

- Lab 1 MDocument24 pagesLab 1 Mviorica88Pas encore d'évaluation

- Mostra Subiecte Examen PSMDocument6 pagesMostra Subiecte Examen PSMCriss FanyPas encore d'évaluation

- Curs 6 - Numararea Evenimentelor Si Masurarea Intervalelor de TimpDocument27 pagesCurs 6 - Numararea Evenimentelor Si Masurarea Intervalelor de TimpDHM1305Pas encore d'évaluation

- Microcontrolerul Pic 16F84Document19 pagesMicrocontrolerul Pic 16F84Cat RosePas encore d'évaluation

- Lab 3. Placa de Achiziţie Date Multiplexoare - Circuite de Eşantionare-Memorare - Convertoare Analog-Numerice Şi Numeric-AnalogicDocument17 pagesLab 3. Placa de Achiziţie Date Multiplexoare - Circuite de Eşantionare-Memorare - Convertoare Analog-Numerice Şi Numeric-AnalogicRoxana ElenaPas encore d'évaluation

- Multiplicarea Cu Acumulare: 1) Procesoare DSP Operatii Efectuate de Unitatea CentralaDocument2 pagesMultiplicarea Cu Acumulare: 1) Procesoare DSP Operatii Efectuate de Unitatea CentralaCirnaROPas encore d'évaluation

- MCU Lab2Document8 pagesMCU Lab2Petru G.Pas encore d'évaluation

- Pic 16f84Document33 pagesPic 16f84Valentin BodnarescuPas encore d'évaluation

- Programarea Microcontrolerelor Pic 16f84Document20 pagesProgramarea Microcontrolerelor Pic 16f84Alex AndruPas encore d'évaluation

- AOC 3 FundamenteUCPDocument40 pagesAOC 3 FundamenteUCPSergio_SmileroPas encore d'évaluation

- Controller UlDocument16 pagesController UlnicuboyPas encore d'évaluation

- Microprocesoare 13Document17 pagesMicroprocesoare 13neacsu92Pas encore d'évaluation

- Rezolvari PSMDocument15 pagesRezolvari PSMCretz CristiPas encore d'évaluation

- Proiect de Curs MIDocument17 pagesProiect de Curs MIZgherea MihaiPas encore d'évaluation

- MPA Subiecte 8 La 13Document7 pagesMPA Subiecte 8 La 13Adrian MasPas encore d'évaluation

- Cap 1 - APBDocument45 pagesCap 1 - APBAnonymous vMqh2CkPas encore d'évaluation

- SMC Subiecte RezolvateDocument30 pagesSMC Subiecte Rezolvateandy tudoreanuPas encore d'évaluation

- Raport La Proiectul de An - Exemplu Cu StergeriDocument26 pagesRaport La Proiectul de An - Exemplu Cu StergeriAlina AxentiPas encore d'évaluation