Académique Documents

Professionnel Documents

Culture Documents

Aula Sistdigfim Al

Transféré par

Romeu Corradi JúniorCopyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

Aula Sistdigfim Al

Transféré par

Romeu Corradi JúniorDroits d'auteur :

Formats disponibles

TDM I - SISTEMAS DIGITAIS

CIRCUITOS LGICOS

SISTEMAS E SUBSISTEMAS DIGITAIS

MICROELETRONICA

+

=

MOTIVAO

MOTIVAO

TDM I - SISTEMAS DIGITAIS

CIRCUITOS LGICOS

SISTEMAS E SUBSISTEMAS DIGITAIS

MICROELETRONICA

SISTEMAS OPERACIONAIS

+

=

MOTIVAO

TDM I - SISTEMAS DIGITAIS

CIRCUITOS LGICOS

SISTEMAS E SUBSISTEMAS DIGITAIS

MICROELETRONICA

SISTEMAS OPERACIONAIS

REDES

+

=

TDM I - SISTEMAS DIGITAIS

CIRCUITOS LOGICOS

+ =

PROJETO DE SISTEMAS

COMBINACIONAIS E SEQUENCIAIS

SIMPLES

TDM I - SISTEMAS DIGITAIS

SISTEMAS DIGITAIS

Combinacionais e Sequenciais

nfase em Automao

PROJETO DE CIRCUITOS

COMPLEXOS ?

EMENTA

TDM I - SISTEMAS DIGITAIS

MODULOS COMBINACIONAIS FIXOS

MODULOS COMBINACIONAIS ARITMTICOS FIXOS

REPRESENTAO NUMRICA BINRIA EM PONTO FIXO

ARITMTICA BINRIA EM PONTO FIXO

MODULOS SEQUENCIAIS FIXOS

PROJETOS DE SISTEMAS DIGITAIS

SUBSISTEMA DE CONTROLE

BIBLIOGRAFIA

TDM I - SISTEMAS DIGITAIS

INTRODUO AOS SISTEMAS DIGITAIS

MILOS ERCEGOVAC, TOMAS LANG, JAIME MORENO

BOOKMAN

PRINCIPLES OF DIGITAL DESIGN

DANIEL D. GAJSKI

PRENTICE HALL

SISTEMAS DIGITAIS FUNDAMENTOS E APLICAES

T. L. FLOYD

BOOKMAN

Apostilas no site:

www.corradi.junior.nom.br

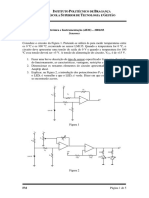

EXERCICIO 1

(CIRC. LOGICOS)

TDM I - SISTEMAS DIGITAIS

EXPRESSES DE CHAVEAMENTO E

CIRCUITO

OBS: ESTA ESPECIFICAO TAMBEM

PODERIA SER ATENDIDA POR UM PROJETO

BASEADO EM MODULOS FIXOS, MODULOS

PROGRAMAVEIS E EM

MICROCOMPUTADOR

EM UM PROGRAMA DE PERGUNTAS E RESPOSTAS, O APRESENTADOR FAZ UMA

PERGUNTA PARA 3 PARTICIPANTES. AQUELE QUE SOUBER A RESPOSTA,

PRESSIONA UM BOTO COLOCADO A SUA FRENTE, QUE, POR SUA VEZ, FAZ COM

QUE UM LED ASSOCIADO AO BOTO SEJA ACESO, CASO NENHUM OUTRO

CANDIDATO TENHA, PREVIAMENTE, PRESSIONADO O SEU CORRESPONDENTE

BOTO. O LED DEVE FICAR ACESO AT QUE O APRESENTADOR PRESSIONE UM

BOTO DE RESET.

CASO HAJA BOTES PRESSIONADOS SIMULTANEAMENTE A PRIORIDADE DEVE SER

: BOTO 1 , DEPOIS, BOTO 2 E, FINALMENTE BOTO 3.

PROJETE UM CIRCUITO QUE ATENDA AS ESPECIFICAES ACIMA, USANDO

PORTAS LOGICAS E FLIP-FLOPs TIPO D COM PRESET E CLEAR, SABENDO QUE : OS

LEDs DEVEM SER ACESOS EM NIVEL 0; O CIRCUITO DEVE SER SINCRONO;

APENAS O BOTO DO APRESENTADOR ASSINCRONO; DEVE EXISTIR UM FLIP-

FLOP POR CANDIDATO E O CLOCK NO PODE SER DESABILITADO.

SISTEMAS DIGITAIS

PROJETO DE SISTEMAS

COMBINACIONAIS E SEQUENCIAIS

SIMPLES

CIRCUITOS INTEGRADOS

DISPONIVEIS

PROJETO DE SISTEMAS

COMBINACIONAIS E SEQUENCIAIS

COMPLEXOS

SISTEMAS DIGITAIS

MODULOS COMBINACIONAIS FIXOS

DECODIFICADORES

CODIFICADORES

CODIFICADORES DE PRIORIDADE

MULTIPLEXADORES

DEMULTIPLEXADORES

DESLOCADORES

SISTEMAS DIGITAIS

DECODIFICADORES

X

O

Y

0

X

1

Y

1

X

2

Y

2

. .

. .

X

N-1

Y

N-1

.

.

E Y

2

N

-1

ESPECIFICAO

ENTRADAS: X : X = (X

N-1

,......,X

0

) X

J

e {0,1}

E : E e {0,1}

SAIDAS : Y : Y = (Y

2

N

-1

,......,Y

0

) Y

J

e {0,1}

FUNO : Y

I

= 1 SE (X=I) E (E=1)

Y

I

= 0 CASO CONTRARIIO

N-1

EM QUE: X = X

J

2

J

E I = 0,1...,2

N

1

J= 0

REDES DECODIFICADORAS

SISTEMAS DIGITAIS

DECODIFICAO

COINCIDENTE

REDES DECODIFICADORAS

SISTEMAS DIGITAIS

E

E

DECODIFICAO

EM ARVORE

VANTAGEM ?

DESVANTAGEM ?

EXERCICIO 2

SISTEMAS DIGITAIS

GND

0

1

2

31

CHAVE

ROTATIVA

VCC

32

0 1 2 31

.....

EXERCICIO 2 CONTINUAO

SISTEMAS DIGITAIS

GND

0

1

2

31

CHAVE

ROTATIVA

VCC

BLOCO

CODIFICADOR

BLOCO

DECODIFICADOR

5

?

PROJETE O BLOCO DECOFICADOR ACIMA, USANDO

CIs 74LS138 E USE DECODIFICAO EM ARVORE

IO #O0

I1 #O1

I2 #O2

#E .

#E .

E #O7

74LS138

.....

CODIFICADOR

SISTEMAS DIGITAIS

X

0

Y

0

X

1

Y

1

X

2

Y2

. .

. .

X

N-1

Y

N-1

X

2

N

-1

E A

ESPECIFICAO

ENTRADAS: X : X = (X

2

N

-1

,......,X

0

) X

J

e {0,1}

E : E e {0,1}

SAIDAS : Y : Y = (Y

N-1

,......,Y

0

) Y

J

e {0,1}

A : A e {0,1}

FUNO : Y = I SE (X

I

=1) E (E=1)

Y = 0 CASO CONTRARIO

A = 1 SE (ALGUM X

I

= 1) E (E =1)

A = 0 CASO CONTRARIO

N-1

EM QUE: Y = Y

J

2

J

E I = 0,1...,2

N

1

J= 0

EXERCICIO 3

SISTEMAS DIGITAIS

GND

0

1

2

31

CHAVE

ROTATIVA

VCC

BLOCO

CODIFICADOR

BLOCO

DECODIFICADOR

5

?

PROJETE O BLOCO COFICADOR ACIMA, USANDO

CIs DO TIPO DESENHADO AO LADO

IO O0

I1 O1

I2 O2

I3 .

I4 .

I5

I6

I7

E A

CODIFICADOR

.....

EXERCICIO 4

SISTEMAS DIGITAIS

PROJETE UM SISTEMA COMBINACIONAL QUE TENHA UMA

ENTRADA X DE 3 BITS, REPRESENTANDO OS DIGITOS DE

0 A 7 E UMA SAIDA Y DE 3 BITS REPRESENTANDO O

MESMO CONJUNTO DE NUMEROS, SABENDO QUE A

FUNO DO SISTEMA Y = (3X) MOD 8.

OBS: USO OBRIGATORIO DE DECOD. E CODIFIC.

CODIFICADOR DE PRIORIDADE

SISTEMAS DIGITAIS

X

0

Y

0

X

1

Y

1

X

2

Y2

. .

. .

X

N-1

Y

N-1

X

2

N

-1

E A

ESPECIFICAO

ENTRADAS: X : X = (X

2

N

-1

,......,X

0

) X

J

e {0,1}

E : E e {0,1}

SAIDAS : Y : Y = (Y

N-1

,......,Y

0

) Y

J

e {0,1}

A : A e {0,1}

FUNO : Y = I SE (X

I

=1) E (X

K

= 0 , K < I) E (E=1)

Y = 0 CASO CONTRARIO

A = 1 SE (ALGUM X

I

= 1) E (E =1)

A = 0 CASO CONTRARIO

N-1

EM QUE: Y = Y

J

2

J

E I = 0,1...,2

N

1

J= 0

EXERCICIO 5

SISTEMAS DIGITAIS

PROJETE UM SISTEMA COMBINACIONAL QUE INDIQUE

QUANTOS DESLOCAMENTOS PARA ESQUERDA DEVEMOS

EFETUAR EM UM VETOR DE 8 BITS DE MODO QUE O BIT

MAIS A ESQUERDA SEJA 1(NORMALIZAO PARA

ESQUERDA).

OBS: USE O CI ABAIXO.

IO O0

I1 O1

I2 O2

I3 .

I4 .

I5

I6

I7

E A

CODIFICADOR

DE PRIORIDADE

MULTIPLEXADOR

SISTEMAS DIGITAIS

X

0

X

1

X

2

.

.

X

N-1

Z

X

2

N

-1

E S

N-1

.....S

1

S

0

ESPECIFICAO

ENTRADAS: X : X = (X

2

N

-1

,......,X

0

) X

J

e {0,1}

S : S = (S

N-1

,......,S

0

) S

J

e {0,1}

E : E e {0,1}

SAIDAS : Z : Z e {0,1}

FUNO : Z = X

S

SE (E=1)

Z = 0 CASO CONTRARIO

N-1

EM QUE: S = S

J

2

J

E I,J = 0,1...,2

N

1

J= 0

EXERCICIO 6

SISTEMAS DIGITAIS

PROJETE UM SISTEMA COMBINACIONAL PERMITA A

ESPIONAR ,POR MEIO DE UM PAINEL DE CHAVES, 4

LINHAS DE COMUNICAO

?

L0

L1

L2

L3

EXERCICIO 7

SISTEMAS DIGITAIS

PROJETE UM SISTEMA DIGITAL PARA IMPLEMENTAR A

FUNO (ABCD)= CONJUNTO-UM (1,3,4,9,14,15)

DEMULTIPLEXADOR

SISTEMAS DIGITAIS

YO

Y1

Y2

.

.

X YN-1

Y2

N

-1

E

SN-1 .....S1S0

ESPECIFICAO

ENTRADAS: X : X e {0,1}

E : E e {0,1}

S : S = (S

N-1

,......,S

0

) S

J

e {0,1}

SAIDAS : Y : Y = (Y

2

N

-1

,......,Y

0

) Y

J

e {0,1}

FUNO : Y

I

= X SE (I = S) E (E = 1)

Y

I

=0 CASO CONTRARIIO

N-1

EM QUE: S = S

J

2

J

E I,J = 0,1...,2

N

1

J= 0

DESLOCADOR P

SISTEMAS DIGITAIS

X-P

X-P+1

.

XO YO

X1 Y1

X2 Y2

. .

. .

XN-1 YN-1

XN

XN+1 .

.

XN+P-1

E

D

S

USO:MULT/DIV POTENCIA DE 2 ALINHAMENTO DE VETORES

ESPECIFICAO

ENTRADAS: X : X = (X

N+p -1

,..,X

N

....,X

0

...X

-P

) X

J

e {0,1}

E : E e {0,1}

S : S e { P,...,0 }

D : D e {0,1} D=0: ESQUERDA D=1: DIREITA

SAIDAS : Y : Y = (Y

N-1

,......,Y

0

) Y

J

e {0,1}

FUNO : Y

I

= X

I-S

SE (D=0) E (E = 1)

Y

I

= X

I+S

SE (D=1) E (E = 1)

Y

I

= 0

SE (E = 0)

USO:

-MULTIPLICAO/DIVISO

POTENCIA DE 2

-ALINHAMENTO DE

VETORES

EXERCICIO 8

SISTEMAS DIGITAIS

PROJETE UM SISTEMA DIGITAL QUE NORMALIZE O

VETOR DO EXERCICIO 5

EXERCICIO 9

SISTEMAS DIGITAIS

DOIS SD USAM CODIGOS NO CONVENCIONAIS PARA

REPRESENTAR NUMEROS INTEIROS ENTRE 0 E 15 DA

SEGUINTE MANEIRA:

O SIST. A REPRESENTA UM NUMERO INTEIRO N COMO

P = 3N MOD 16.

O SIST. B REPRESENTA UM NUMERO INTEIRO N COMO

Q = 7N MOD 16.

PROJETE UM CIRCUITO QUE REALIZE A CONVERSO DE

CODIGO DO SISTEMA A PARA O SISTEMA B USANDO 2

MUXs DE 8 ENTRADAS E UM XOR DE 2 ENTRADAS

MODULOS COMBINACIONAIS

ARITMETICOS FIXOS

SISTEMAS DIGITAIS

NUMERO

BINARIO

NUMERO

HEXADECIMAL

NUMERO

DECIMAL

10011101 9D 157

NUMERO

DECIMAL

NUMERO

HEXADECIMAL

NUMERO

BINARIO

183 B7 10110111

1 x 2

7

+ 1 x 2

4

+ 1 x 2

3

+ 1 x 2

2

+ 1 x 2

0

= 128 + 16 + 8 + 4 + 1 = 157

9 x 16

1

+ 13 x 16

0

= 157

183/16

7 11/16

B 0

MODULOS COMBINACIONAIS

ARITMETICOS FIXOS

SISTEMAS DIGITAIS

SOMADOR

+

N

Y X

Z

C

IN

C

OUT

X = X

I

.2

I

I=0

N-1

NUMERO INTEIRO

DE O A 2

N

-1

RELACIONAMENTO ENTRADA E SAIDA

X + Y+ C

IN

= 2

N

C

OUT

+ Z

IDEM PARA Y E Z

MODULOS COMBINACIONAIS

ARITMETICOS FIXOS

SISTEMAS DIGITAIS

SOMADOR

ESPECIFICAO

ENTRADAS: X : X = (X

2

N

-1

,......,X

0

) X

J

e {0,1}

Y : Y = (Y

N-1

,......,Y

0

) Y

J

e {0,1}

C

IN

: C

IN

e {0,1}

SAIDAS : Z : Z = (Z

N-1

,......,Z

0

) Z

J

e {0,1}

C

OUT

: C

OUT

e {0,1}

FUNES : Z = (X + Y + C

IN

) MOD 2

N

C

OUT

= 1 SE (X + Y + C

IN

) 2

N

C

OUT

= 0 CASO CONTRARIO

MODULOS COMBINACIONAIS

ARITMETICOS FIXOS

SISTEMAS DIGITAIS

SOMADOR DE 1 BIT

+

1

X

I

C

I

C

I+1

Y

I

Z

I

FUNES

Z

I

= X

I

Y

I

C

I

C

I+1

= X

I

. Y

I

+ (X

I

Y

I

) .C

I

G

I

P

I

Z

I

= P

I

C

I

C

I+1

= G

I

+ P

I

.C

I

1

1

1

1

G: GERA CARRY

P: PROPAGA CARRY

MODULOS COMBINACIONAIS

ARITMETICOS FIXOS

SISTEMAS DIGITAIS

IMPLEMENTAO DO SOMADOR DE 1 BIT

X

I

Y

I

C

I

G

I

Z

I C

I+1

SOMADOR

COMPLETO

FUNES

G

I

= X

I

. Y

I

P

I

= (X

I

Y

I

)

Z

I

= P

I

C

I

C

I+1

= G

I

+ P

I

.C

I

SOMADOR QUANDO NO

SE TEM CARRY DE

ENTRADA

P

I

MEIO

SOMADOR

MODULOS COMBINACIONAIS

ARITMETICOS FIXOS

SISTEMAS DIGITAIS

MODULO SOMADOR DE N BITs COM

CARRY PROPAGADO

+

X

N-1

C

N

Y

N-1

Z

N-1

+

X

0

C

N-1

C

0

C

1

Z

0

SOMADDOR

DE 1 BIT

Y

0

MODULOS COMBINACIONAIS

ARITMETICOS FIXOS

SISTEMAS DIGITAIS

RETARDO DO MODULO SOMADOR

C

I+1

= G

I

+ P

I

.C

I

E RETARDO DE QQ GATE

1

O

MODULO: C1= G0 +P0.C0 RETARDO: 3

2

O

MODULO: C2= G1 +P1.C1 RETARDO: 3 + 2 = 5

3

O

MODULO: C3= G2 +P2.C2 RETARDO: 5 + 2 = 7

4

O

MODULO: C4= G3+P3.C3 RETARDO: 7 + 2 = 9

..............................................................................................

N

O

MODULO: CN= GN-1 +PN-1.C1 RETARDO: (2N+1)

MODULOS COMBINACIONAIS

ARITMETICOS FIXOS

SISTEMAS DIGITAIS

PROJETO DE UM NOVO MODULO SOMADOR COM

RETARDO MENOR

C

I+1

= G

I

+ P

I

.C

I

E RETARDO DE QQ GATE

1

O

MODULO: C1= G0 +P0.C0 RETARDO: 3

2

O

MODULO: C2= G1 +P1.C1 = G1+ P1(G0 +P0C0) = G1 +P1G0 +P1P0C0 RETARDO: 3

3

O

MODULO: C3= G2 + G1G2 + G0P1P2 + P0P1P2C0 RETARDO: 3

4

O

MODULO: C4= G3 + G2P3 + G1P2 P3 + POP1P2P3C0 RETARDO: 3

..............................................................................................

N

O

MODULO: .............. RETARDO: 3

G P

MODULOS COMBINACIONAIS

ARITMETICOS FIXOS

SISTEMAS DIGITAIS

MODULO SOMADOR DE TRANSPORTE DE CARRY

ANTECIPADO (EXEMPLO COM 4 BITS)

X0 Y0 C0

G0 P0 S0

X1 Y1 C1

G1 P1 S1

X2 Y2 C2

G2 P2 S2

X3 Y3 C3

G3 P3 S3

C4 G3 P3 C3 G2 P2 C2 G1 P1 C1 G0P0

G P GERADOR DE CARRY ANTECIPADO C0

MODULOS COMBINACIONAIS

ARITMETICOS FIXOS

NUMEROS NO FORMATO BCD

BINARIO BCD

0000 0000

0001 0001

0010 0010

0011 0011

0100 0100

0101 0101

0110 0110

0111 0111

BINARIO BCD

1000 1000

1001 1001

1010 10000

1011 10001

1100 10010

1101 10011

1110 10100

1111 10101

+ 6

5 1

MODULOS COMBINACIONAIS

ARITMETICOS FIXOS

SISTEMAS DIGITAIS

SOMADOR BCD

X3 X2 X1 X0 Y3 Y2 Y1 Y0

COUT

Z3 Z2 Z1 Z0 CIN

+

X Y

Z

ESPECIFICAO

ENTRADAS E SAIDA

X 9 Y 9 Z 9

FUNES

1 SE X + Y + CIN > 9

COUT =

0 CASO CONTRARIO

X + Y + CIN SE (X + Y + CIN 9) E COUT=0

Z = X + Y + CIN + 6 SE (X + Y + CIN > 9) E COUT=0 COUT=1

X + Y + CIN + 6 SE (X + Y + CIN 9) E COUT=1

MODULOS COMBINACIONAIS

ARITMETICOS FIXOS

SISTEMAS DIGITAIS

EXEMPLO DE SOMA BCD

0100 4

+

0011 3

0 0111 7

0101 5

+

0111 7

0 1100 C

+ 0110

1 0010 12

1001 9

+

1000 8

1 0001 1

+ 0110

1 0111 17

MODULOS COMBINACIONAIS

ARITMETICOS FIXOS

SISTEMAS DIGITAIS

SUBTRATOR

-

N

Y X

Z

B

IN

B

OUT

X = X

I

.2

I

I=0

N-1

NUMERO INTEIRO

DE O A 2

N

-1

RELACIONAMENTO ENTRADA E SAIDA

X - Y- B

IN

= Z

- 2

N

B

OUT

IDEM PARA Y E Z

MODULOS COMBINACIONAIS

ARITMETICOS FIXOS

SISTEMAS DIGITAIS

EXEMPLO DE SUBTRAO

1111 15

-

0111 7

0 1000 8

0101 5

-

0111 7

-2

-------------------

10101 21

-

0111 7

1 1110 14

14 16 = - 2

NO SE PODE REPRESENTAR

UM NUMERO

NEGATIVO,QUANDO SE

TRABALHA COM NUMEROS

POSITIVOS SEM SINAL

EMPRESTIMO

(BORROW)

MODULOS COMBINACIONAIS

ARITMETICOS FIXOS

SISTEMAS DIGITAIS

SUBTRATOR

ESPECIFICAO

ENTRADAS: X : X = (X

n-1

,......,X

0

) X

J

e {0,1}

Y : Y = (Y

N-1

,......,Y

0

) Y

J

e {0,1}

B

IN

: B

IN

e {0,1}

SAIDAS : Z : Z = (Z

N-1

,......,Z

0

) Z

J

e {0,1}

B

OUT

: B

OUT

e {0,1}

FUNES : Z = (X - Y - B

IN

) SE (X - Y - B

IN

) 0

Z = (X - Y - B

IN

) + 2

N

SE (X - Y - B

IN

) < 0

B

OUT

= 1 SE (X - Y - B

IN

) < 0

B

OUT

= 0 CASO CONTRARIO

MODULOS COMBINACIONAIS

ARITMETICOS FIXOS

SISTEMAS DIGITAIS

SUBTRATOR DE 1 BIT

-

1

X

I

B

I

B

I+1

Y

I

Z

I

FUNES

Z

I

= X

I

+ Y

I

+ B

I

B

I+1

= X

I

. Y

I

+ (X

I

+ Y

I

) .B

I

G

I

P

I

Z

I

= P

I

+ B

I

B

I+1

= G

I

+ P

I

.B

I

REPRESENTAO E OPERAES COM NUMERO

INTEIROS COM SINAL

SISTEMAS DIGITAIS

SISTEMA : SINAL/MAGNITUDE

NUMERO INTEIRO X REPRESENTADO COMO (XS,XM)

XS XM

SINAL

(1 BIT)

0 +

1 -

MAGNITUDE

(JBITS)

BIT + SIGNIFICATIVO

DO VETOR

REPRESENTAO E OPERAES COM NUMERO

INTEIROS COM SINAL

SISTEMAS DIGITAIS

REPRESENTAO DE NUMEROS DE N BITS

( 1 BIT DE SINAL E N-1 BITS DE MAGNITUDE )

- (2

N-1

1) X (2

N-1

1)

N = 8

- (2

7

1) X 2

7

1

- 127 X 127

ADIO COM NUMEROS EM SINAL E MAGNITUDE

SISTEMAS DIGITAIS

+ > - < + < - > - -

SOM SUB

+ +

+

SOM SUB

+

SOM SUB

-

SOM

-

SUB

A SUBTRAO ANALOGA

COMPLEMENTO A 2

SISTEMAS DIGITAIS

PARA AGILIZAR AS OPERAES

FOI CRIADO O SISTEMA COMPLEMENTO A 2

NUMERO INTEIRO X REPRESENTADO POR:

X SE X 0 X

X

R

=

2

N

- |X| SE X < 0 C2(X)

NUMERO DE BITS DO VETOR

EXEMPLO DE NUMERO EM COMPLEMENTO A 2

SISTEMAS DIGITAIS

N=8

X= 7

X= -7 C2(7) = 2

8

7 = 249

X=7 0 0 0 0 0 1 1 1

X= -7 1 1 1 1 1 0 0 1

REPRESENTAO DOS NUMEROS COM 8 BITS, EM

COMPLEMENTO A 2

SISTEMAS DIGITAIS

127 0 1 1 1 1 1 1 1

126 0 1 1 1 1 1 1 0

125 0 1 1 1 1 1 0 1

124 0 1 1 1 1 1 0 0

.

2 0 0 0 0 0 0 1 0

1 0 0 0 0 0 0 0 1

0 0 0 0 0 0 0 0 0

-1 1 1 1 1 1 1 1 1

-2 1 1 1 1 1 1 1 0

.

-126 1 0 0 0 0 0 1 0

-127 1 0 0 0 0 0 0 1

-128 1 0 0 0 0 0 0 0

-

+

_ _ _ _ _ _ _ _

_ _ _ _ _ _ _ _

7 6 5 4 3 2 1 0

0 0 0 0 0 0 0 0

1

X

C2(X)

+

BITS

2

N

8 BITS

0

ADIO EM COMPLEMENTO A 2

SISTEMAS DIGITAIS

X Y

SOM

X + Y

X C2(Y)

SOM

X -Y

2

N

- Y

1

2

N

C2(X) (Y)

SOM

Y - X

2

N

- X

1

2

N

C2(X) C2(Y)

SOM

-(X + Y)

2

N

- X

10

2

N+1

2

N

- Y

COUT

SUBTRAO EM COMPLEMENTO A 2

SISTEMAS DIGITAIS

X Y

SOM

X - Y

X C2(Y)

SOM

X +Y

Y

C2(X) (Y)

SOM

-X - Y

2

N

- X

10

2

N+1

C2(X) C2(Y)

SOM

-X + Y

2

N

- X

1

2

N

Y

C2

2

N

- Y

1

2

N

DC2

C2

2

N

- Y

DC2

NO SE USA MAIS O SUBTRATOR

2

N

- Y

C2 DC2

COMPLEMENTA DESCOMPLEMENTA

=

EXERCICIO: BLOCO PARA

COMPLEMENTAR E BLOCO PARA

DESCOMPLEMENTAR

MOSTRE QUE PARA COMPLEMENTAR A 2,

OU DESCOMPLEMENTAR, UM VETOR DE 8

BITS, BASTA INVERTER OS BITS DO

VETOR E SOMAR 1

SOLUO DO EXERCICIO

X + C2(X) = 2

N

X + #X = 2

N

- 1

C2(X) = #X + 1

X + C2(X) = 2

N

C2(X) + #C2(X) = 2

N

- 1

X = #C2(X) + 1

SOMADOR/SUBTRATOR P/ COMPLEMENTO A 2

SISTEMAS DIGITAIS

X Y

C2

1 0

MUX

+

0 SOMA

1 SUBTR.

COMPLEMENTADOR

SISTEMAS DIGITAIS

X + C2(X) = 2

N

X + #X = 2

N

1

C2(X) = #X + 1

X Y

1 0

MUX

+

0 SOMA

1 SUBTR.

CIN

ESTOURO EM COMPLEMENTO A 2

(OVERFLOW)

SISTEMAS DIGITAIS

ADIO:

OS 2 OPERANDOS SO POSITIVOS OU NEGATIVOS

0

0

+

BIT N-2

CARRY =1 P/ ESTOURAR

COUT=0 1

COUT

-1

= 1

1

1

BIT N-2

+

CARRY =0 P/ ESTOURAR

COUT

-1

= 0 0

COUT=1

P/ OCORRER OVERFLOW

1. NUMEROS COM MESMO SINAL

2. APS A OPERAO, O BIT DE

SINAL FICA INVERTIDO

OU

COUT XOR COUT

-1

=1

SUBTRAO:

RACIOCINIO

ANALOGO

ESTOURO EM COMPLEMENTO A 2

(OVERFLOW)

SISTEMAS DIGITAIS

EXEMPLOS

(+ 126) + (+126) VAI GERAR OVERFLOW

01111110

01111110

___________

C

OUT-1

= 1

(- 126) + (-126) VAI GERAR OVERFLOW

10000010

10000010

___________

C

OUT-1

= 0

+

SUBTRAO DE NUMEROS SEM SINAL

EM SOMADOR/SUBTRATOR C2

SISTEMAS DIGITAIS SISTEMAS DIGITAIS

X + C2(X) = 2

N

X + #X = 2

N

1

C2(X) = #X + 1

X Y

1 0

MUX

+

1 SUBTR.

CIN

0 0

#Y

X + #Y +1 = X + 2

N

- Y

COUT

1

X-Y

COUT

2

N

(2

N

+X) -Y

COUT

0

X <Y -> EMPRESTIMO

DE 2

N

( BORROW)

OK

BORROW = # COUT

INTERPRETAO DO

RESULTADO

SOMADOR/SUBTRATOR C2

SISTEMAS DIGITAIS SISTEMAS DIGITAIS

1 0

MUX

+

CIN

COUT

0 SOMA

1 SUBTR.

1

0

COUT

OV

COUT

-1

Y X

Z

FLAGS DE STATUS

SISTEMAS DIGITAIS

1 0

MUX

+

CIN

COUT

1

0

COUT

OV

COUT

-1

Y X

Q D

CLK

Q D

CLK FC

OV

FLAGS

Z

EXEMPLO

SISTEMAS DIGITAIS

NUMEROS S/SINAL

AL: 00001010 (10)

BL: 10001111 (143)

AL BL - > AL + #BL +1 =

01111011 (123) BO -> CY=1

123 256 = -133

-133

NUMEROS C/SINAL

AL: 00001010 (10)

BL: 10001111 (-113)

AL BL - > AL + #BL +1 =

:01111011 (123) OV=0

+123

EXERCICIO 10

SISTEMAS DIGITAIS

1. COMPLETE

A SEGUINTE

TABELA

NUMERO

INTEIRO COM

SINAL

NUMERO

INTEIRO SEM

SINAL

VETOR DE

BITS

COMPLEMENTO A 2,

VETOR COM 7 BITS

-37

COMPLEMENTO A 2,

VETOR COM 8 BITS

205

COMPLEMENTO A 2,

VETOR COM 5BITS

11011

COMPLEMENTO A 2,

VETOR COM 8 BITS

9

SINAL-MAGNITUDE ,

VETOR COM 5BITS

11011

EXERCICIO 10

SISTEMAS DIGITAIS

2. A representao de numeros inteiros pode ser generalizada

para a representao de numeros de ponto fixo. Ou seja , o

ponto binario , o qual se presume que para os numeros inteiros

esteja a direita do digito menos significativo , pode ser colocado

entre 2 digitos quaisquer. Para o vetor de bits x = (X6, X5,..., Xo)

e um ponto binario entre os bits X4 e X3, determine o numero

x

maximo

mais positivo e o numero x

minimo

mais negativo e mostre

a sua representacao em vetor de bits correspondente.

a. no sistema sinal e magnitude

b. no sistema complemento de 2

EXERCICIO 10

SISTEMAS DIGITAIS

3. Para os pares seguintes de vetores x e y de 8 bits representando numeros

inteiros no sistema COMPLEMENTO A 2 ,obtenha os vetores de bits z e d que

representam z = x + y e d=x-y ,respectivamente.

Verifique se obteve o resultado correto.

X: 01011011 y: 00100111

X: 10101010 y: 10100000

4. Para os pares seguintes de vetores x e y de 8 bits representando numeros

inteiros no sistema SEM SINAL ,obtenha os vetores de bits z e d que

representam z = x + y e d=x-y ,respectivamente.

Verifique se obteve o resultado correto.

X: 01011011 y: 00100111

X: 10101010 y: 10100000

EXERCICIO 10

SISTEMAS DIGITAIS

5. PROJETAR UM SUBTRATOR BCD USANDO O MODULO SOMADOR/SUBTRATOR

6. A EXTENSO DE FAIXA EXECUTADA QUANDO NECESSARIO REPRESENTAR

O VALOR X POR UM VETOR DE M BITS , DADA SUA REPRESENTAO POR UM

VETOR DE BITS DE N<M BITS. OU SEJA, Z=X E Z=(Zm-l,Zm-2,...ZO) , X=(Xn-l,Xn-

2,...XO)

NO SISTEMA DE COMPLEMENTO A 2 , A EXTENSAO DE FAIXA IMPLEMENTADA

POR :

Xn-1 para i = m-l,...n

Zi =

Xi para i= n-l,..0

PROVE QUE ESTA IMPLEMENTAO CORRETA

MODULOS COMBINACIONAIS

ARITMETICOS FIXOS

SISTEMAS DIGITAIS

SOMADOR

SUBTRATOR

UNIDADE ARITMETICA

UNIDADE ARITMETICA LOGICA

COMPARADOR

MULTIPLICADOR

DIVISOR

MODULOS COMBINACIONAIS

ARITMETICOS FIXOS

SISTEMAS DIGITAIS

UNIDADE ARITMETICA

AU

X Y

Z

F

CIN

COUT

OV

ZERO

SINAL

N

3

COUT : CARRY OU BORROW

OV : OVERFLOW

ZERO : SE Z = 0

SINAL : SINAL DE Z

EXEMPLO DE FUNES :

SOMA

SOMA C/CIN

SUBRATAO

INCREMENTO DE X

TROCA DE SINAL DE X

STATUS DA AU

MODULOS COMBINACIONAIS

ARITMETICOS FIXOS

SISTEMAS DIGITAIS

UNIDADE ARITMETICA

AU

X Y

Z

F

CIN

COUT

OV

ZERO

SINAL

N

3

ESPECIFICAO

ENTRADAS:

X =(X

N-1

,...X

0

) X

I

e {0,1}

Y =(X

N-1

,...X

0

) X

I

e {0,1}

CIN e {0,1}

F = (F

2

,F

1

,F

0

) F

I

e {0,1}

SAIDAS:

Z =(Z

N-1

,...Z

0

) Z

I

e {0,1}

COUT,SGN,ZERO,OV e {0,1}

FUNES

F OPERAO

001 ADD Z = X + Y

011 SUB Z = X - Y

101 ADDC Z = X + Y + CIN

110 CS Z = - X

010 INC Z = X + 1

SGN =1 SE Z< 0, 0 CASO

CONTRARIO

ZERO =1 SE Z=0, 0 CASO

CONTRARIO

OV =1 SE Z ESTOURAR, 0 CASO

CONTRARIO (N

O

C / SINAL)

COUT =1 SE Z ESTOURAR, 0 CASO

CONTRARIO (N

O

S / SINAL)

MODULOS COMBINACIONAIS

ARITMETICOS FIXOS

SISTEMAS DIGITAIS

PROJETO DA UNIDADE ARITMETICA

MODULOS BASICOS PARA O PROJETO

K

MUX

0 1

+

CIN

COUT

C0UT-1

COMPL

MODULOS COMBINACIONAIS

ARITMETICOS FIXOS

SISTEMAS DIGITAIS

UNIDADE ARITMETICA

PROJETO

COMPL X COMPL Y

Kx

MUX

0 1

000.....00

Kmx

+

COUT

C0UT-1

C0

SGN

ZERO

MUX

1 0

OV

COUT

X Y

Z

F1= Ky

F2.F1= Kx

F0= Kmx

F1+ F2F0CIN = C0

F1.F0 = K2mx

F2 F1 F0 C

IN

XS

YS

FUNES

F2 F1 F0 OPERAO

0 0 1 ADD Z =X + Y

0 1 1 SUB Z = X - Y

1 0 1 ADDC Z = X + Y + CIN

1 1 0 CS Z = - X

0 1 0 INC Z = X + 1

1

0

MODULOS COMBINACIONAIS

ARITMETICOS FIXOS

SISTEMAS DIGITAIS

UNIDADE ARITMETICA LOGICA

ALU

X Y

Z

COUT

OV

ZERO

SINAL

N

3

FUNES

F OPERAO

001 ADD Z = X + Y

011 SUB Z = X - Y

101 ADDC Z = X + Y + CIN

110 CS Z = - X

010 INC Z = X + 1

000 AND Z = X.Y

100 OR Z = X + Y

111 XOR Z = X Y

CIN

F

MODULOS COMBINACIONAIS

ARITMETICOS FIXOS

SISTEMAS DIGITAIS

OV COUT

X

Y

F1= Ky

F2.F1= Kx

F0= Kmx

F1+ F2F0CIN = C0

F1.F0 = K2mx

K3mx1

K3mx

F2 F1 F0 C

IN

UNIDADE ARITMETICA LOGICA (PROJETO)

AU

MUX

0 1 2 3

Z

SGN

AU

ZERO

ALU

S1

S0

FLAGS DE STATUS ADICIONAIS

SISTEMAS DIGITAIS

Q D

CLK

Q D

CLK

Q D

CLK

ZERO

SGN

PARIDADE

Z C/ N

O

PAR DE 1s -> FP = 1

(PARIDADE PAR)

Z C/ N

O

IMPAR DE 1s -> FP = 0

(PARIDADE IMPAR)

EXEMPLO

SISTEMAS DIGITAIS

SINAL EM NIVEL O -> +

RESULTADO = ZERO

PARIDADE PAR

MODULOS COMBINACIONAIS

ARITMETICOS FIXOS

SISTEMAS DIGITAIS

COMPARADORES (NUMEROS SEM SINAL)

G

OUT

G

IN

E

OUT

E

IN

S

OUT

S

IN

X Y

EXERCICIO 11

SISTEMAS DIGITAIS

COMPARE 2 VETORES DE 8 BITS USANDO

COMPARADORES DE 4 BITS

MODULOS COMBINACIONAIS

ARITMETICOS FIXOS

SISTEMAS DIGITAIS

MULTIPLICADOR PARA NUMEROS S/SINAL

X Y

x

Z

N

M

N + M

ESPECIFICAO

ENTRADAS:

X : X = (X

n-1

,......,X

0

) X

J

e {0,1}

Y : Y = (Y

M-1

,......,Y

0

) Y

J

e {0,1}

SAIDAS :

Z : Z = (Z

N+M-1

,......,Z

0

) Z

J

e {0,1}

FUNO :

Z = X.Y

MODULOS COMBINACIONAIS

ARITMETICOS FIXOS

SISTEMAS DIGITAIS

MULTIPLICADOR PARA NUMEROS S/SINAL

IMPLEMENTAO

Z = X . Y

M-1 M-1

Z = X . ( Y

I

2

I

) = ( XY

I

2

I

)

I=0 I=0

XY

I

= 0 SE Y

I

= 0

XY

I

= X SE Y

I

= 1

IMPLEMENTADO POR

ANDs

DESLOCAMENTO DE I

POSIES PARA A

ESQUERDA

MODULOS COMBINACIONAIS

ARITMETICOS FIXOS

SISTEMAS DIGITAIS

MULTIPLICADOR PARA NUMEROS S/SINAL

X Y

4

3

X3Y0 X2Y0 X1Y0 X0Y0

X3Y1 X2Y1 X1Y1 X0Y1

X3Y2 X2Y2 X1Y2 X0Y2

+

Z

7

SISTEMAS DIGITAIS

MULTIPLICADOR PARA NUMEROS S/SINAL

(IMPLEMENTAO)

Z

Y

7

3

+

MODULOS COMBINACIONAIS

ARITMETICOS FIXOS

X3Y0 X2Y0 X1Y0 X0Y0

X3Y1 X2Y1 X1Y1 X0Y1

X3Y2 X2Y2 X1Y2 X0Y2

BLOCO

AND/SOMADOR

COM 3 ENTRADAS

E 2 SAIDAS

X

4

MODULOS COMBINACIONAIS

ARITMETICOS FIXOS

SISTEMAS DIGITAIS

SISTEMAS DIGITAIS

DIVISOR PARA NUMEROS S/SINAL

EX

N

N/2

N/2

X

Y

Z R

ESPECIFICAO

ENTRADAS:

X =(X

N-1

,...X

0

) X

I

e {0,1}

Y =(X

N/2-1

,...X

0

) X

I

e {0,1}

SAIDAS:

Z =(Z

N/2-1

,...Z

0

) Z

I

e {0,1}

R =(R

N/2-1

,...R

0

) R

I

e {0,1}

EX e {0,1}

FUNES:

Z = X/Y

R = X MOD Y

EX =1 (se Z

N-1

+ Z

N-2

+ Z

N-3

+... + Z

N/2

=1)

MODULOS COMBINACIONAIS

ARITMETICOS FIXOS

OU

DIVISOR

N/2

MODULOS COMBINACIONAIS

ARITMETICOS FIXOS

SISTEMAS DIGITAIS

IMPLEMENTAO

X7 X6 X5 X4 X3 X2 X1 X0 Y3 Y2 Y1Y0

X7

Y3Y2Y1Y0

- B

X6

1 0

Z7

Y3Y2Y1Y0

- B

X5

Z6

1 0

- B

1 0

Z5

Y3Y2Y1Y0

X4

Y3Y2YY0

- B

Z5

1 0

X3

MODULOS ARITMETICOS FIXOS

X4

X3

X6 X5

SISTEMAS DIGITAIS

Y3Y2Y1Y0

- B

X2

1 0

Z3

Y3Y2Y1Y0

- B

X1

Z2

1 0

- B

1 0

Z1

Y3Y2Y1Y0

X0

Y3Y2Y1Y0

- B

Z0

1 0

R3 R2 R1R0

Z7Z6Z5Z4 Z3Z2Z1Z0

EX

MODULOS ARITMETICOS FIXOS

X2 X1

X0

SISTEMAS DIGITAIS

EXEMPLO

10001010 0111

X

Y

Z _ _ _ _ R

10001010 0111

0_ _ _

X

Y

Z _ _ _ _ R

<

_ _ _ _ _ _ _ _

_ _ _ _

10001010 0111

00 _ _

X

Y

Z _ _ _ _ R

<

_ _ _ _

MODULOS ARITMETICOS FIXOS

SISTEMAS DIGITAIS

10001010 0111

X

Y

Z _ _ _ _ R

10001010 0111

0001

X

Y

Z

0001

R

>

000_ _ _ _ _

_ _ _ _

MODULOS ARITMETICOS FIXOS

<

0111

-

10001010 0111

0001

X

Y

Z

0001

R

<

0 _ _ _

0111

-

1

SISTEMAS DIGITAIS

MODULOS ARITMETICOS FIXOS

10001010 0111

0001

X

Y

Z

0001

<

00 _ _

0111

-

R

10

10001010 0111

0001

X

Y

Z

0001

>

001 _

0111

R

101

0 111

0 110

-

10001010 0111

0001

X

Y

Z

0001

>

0011

0111

101

0 111

0 1100

SISTEMAS DIGITAIS

MODULOS ARITMETICOS FIXOS

-

-

0111

-

0101 R

5

19 VERIFICAO

19 x 7 +5 = 138

138

7

# 0 -> EXCEO

SISTEMAS DIGITAIS

MODULOS ARITMETICOS FIXOS

0700H = 1792

1792/02 = 896 > 255 -> ESTOURO

SISTEMAS DIGITAIS

MODULOS ARITMETICOS FIXOS

25

RESTO QUOCIENTE

0700H -> 1792

30H -> 48

25H -> 37

10H -> 16

1792 / 48 = 37 R 16

10

SISTEMAS DIGITAIS

EXERCICIO 11A

PREENCHA A TABELA ABAIXO:

SOMA FC FO FS FZ FP

SOMA

SUB

SUB

MUL

MUL

DIV

DIV

SEM

SINAL

COM

SINAL

SEM

SINAL

COM

SINAL

SEM

SINAL

COM

SINAL

SEM

SINAL

COM

SINAL

10101010 01010101

BINARIO DECIMAL

SISTEMAS DIGITAIS

EXERCICIO 11B

PREENCHA A TABELA ABAIXO

FC FO FS FZ FP

AND

OR

XOR

10101010 01010101

SISTEMAS DIGITAIS

ARITMETICA EM PONTO FLUTUANTE

REPRESENTAO BINARIA EM PONTO FLUTUANTE

_ . _ _ _ _ _ _ _ ...... _ _ _ 2

_ _ _ _ _ _ _ _ ...... _ _ _

SINAL DO

NUMERO

PONTO

BINARIO

MANTISSA

SINAL DO EXPOENTE

EXPOENTE

SISTEMAS DIGITAIS

ARITMETICA EM PONTO FLUTUANTE

COMO REPRESENTAR + 5 EM PONTO FLUTUANTE ?

MANTISSA : 9 BITS ( INCLUINDO O BIT DE SINAL)

EXPOENTE : 6 BITS ( INCLUINDO O BIT DE SINAL)

0.00000101 2

001000

+ +

0.00001010 2

000111

+ +

0.00010100 2

000110

+ +

0.10100000 2

000011

+ +

.........................................

OU

OU

OU

QUAL A MELHOR

REPRESENTAO ?

NO TEM COMPL A 2

EM PT. FLUTUANTE

SISTEMAS DIGITAIS

ARITMETICA EM PONTO FLUTUANTE

COMO REPRESENTAR +0,25 EM PONTO FLUTUANTE ?

MANTISSA : 9 BITS ( INCLUINDO O BIT DE SINAL)

EXPOENTE : 6 BITS ( INCLUINDO O BIT DE SINAL)

0.01000000 2

000000

0.10000000 2

100001

OU QUAL A MELHOR

REPRESENTAO ?

0,25 = 1 / 4 = 1 / 2

2

+ +

+

-

SISTEMAS DIGITAIS

ARITMETICA EM PONTO FLUTUANTE

MULTIPLICAO: (+ 5 X + 5) EM PONTO FLUTUANTE ?

0.00000101 2

001000

0.00000101 2

001000

X

0.00000000 00011001 2

010000

OU

0.00000001 11001000 2

001100

OU

0.11001000 00000000 2

000101

MELHOR REPRESENTAO

SISTEMAS DIGITAIS

ARITMETICA EM PONTO FLUTUANTE

FORMATO NORMALIZADO

_ . 1 _ _ _ _ _ _ ..... _ _ 2

_ _ _ _ _ _ _ ...... _ _ _

SINAL DO NUMERO

MANTISSA

SINAL DO EXPOENTE

EXPOENTE

FORMATO NORMALIZADO REAL

_ 1. _ _ _ _ _ _ ..... _ _ 2

_ _ _ _ _ _ _ _ ...... _ _ _

SEMPRE EXISTEM, NO NECESSITAM SER

ARMAZENADOS NA MEMORIA

ARMAZENAMENTO NA MEMORIA

SINAL DO N

O

| EXPOENTE C/SINAL| MANTISSA

SISTEMAS DIGITAIS

ARITMETICA EM PONTO FLUTUANTE

COMO REPRESENTAR + 5 EM PONTO FLUTUANTE NO

FORMATO NORMALIZADO ?

01.01000000 2

000010

+

+

ARMAZENAMENTO NA MEMORIA

0| 000010| 01000000

SINAL

EXPOENTE MANTISSA

SISTEMAS DIGITAIS

ARITMETICA EM PONTO FLUTUANTE

COMPARAO ENTRE 2 NUMEROS EM PONTO FLUTUANTE

SINAL N

O

| SINAL EXP| EXPOENTE|MANTISSA

SINAL N

O

| SINAL EXP| EXPOENTE|MANTISSA

1 2 3

4

SISTEMAS DIGITAIS

ARITMETICA EM PONTO FLUTUANTE

MODIFICAO NO EXPOENTE PARA FACILITAR A

COMPARAO ENTRE 2 NUMEROS EM PONTO FLUTUANTE

+31

+0

-0

- 30

62

31

1

0

63

-31

+31

+31

+ PESO

APS A MODIFICAO, OS EXPOENTES SO POSITIVOS

USADOS

MAIS

ADIANTE

PESO =31

SISTEMAS DIGITAIS

ARITMETICA EM PONTO FLUTUANTE

COMPARAO ENTRE 2 NUMEROS EM PONTO FLUTUANTE,

EXPOENTES COM PESO

SINALN

O

| EXPOENTE|MANTISSA

SINALN

O

| EXPOENTE|MANTISSA

1

2

SISTEMAS DIGITAIS

ARITMETICA EM PONTO FLUTUANTE

REPRESENTAO DE + 5 EM PONTO FLUTUANTE NO

FORMATO NORMALIZADO SEM PESO

01.01000000 2

000010

+ +

ARMAZENAMENTO NA MEMORIA

0| 100001| 01000000

REPRESENTAO DE + 5 EM PONTO FLUTUANTE NO

FORMATO NORMALIZADO COM PESO

01.01000000 2

100001

+

+ 31

SISTEMAS DIGITAIS

ARITMETICA EM PONTO FLUTUANTE

INTERVALOS DE REPRESENTAO DOS NUMEROS

0 +

-

MAIOR

VALOR

(MODULO)

MAIOR

VALOR

(MODULO)

MENOR

VALOR

(MODULO)

MENOR

VALOR

(MODULO)

OVERFLOW

OVERFLOW

UNDERFLOW

01.111111112

111110

01.000000002

000001

C/ PESO C/ PESO

SISTEMAS DIGITAIS

ARITMETICA EM PONTO FLUTUANTE

01.000000002

100010

01.000000002

000001- 100010 + 011111

EXEMPLO DE GERAO DE UNDERFLOW

01.000000002

000001

=

1 - 34 + 31 = - 2

UNDERFLOW

PARA OS CASOS DE UNDERFLOW SO PERMITIDOS NUMEROS

NO NORMALIZADOS COM EXPOENTE ZERO

00.010000002

000000

/2

+2

REPRESENTAO DO ZERO :

00.000000002

000000

0

/2

SISTEMAS DIGITAIS

ARITMETICA EM PONTO FLUTUANTE

01.000000002

111110

01.000000002

111110 +111110 - 011111

EXEMPLO DE GERAO DE OVERFLOW

01.000000002

111110

=

62 + 62 - 31 = + 93

OVERFLOW

X

REPRESENTAO DO OVERFLOW ( INFINITO):

00.000000002

111111

63

SISTEMAS DIGITAIS

ARITMETICA EM PONTO FLUTUANTE

PADRO IEEE 754

PRECISO SIMPLES

(-1)

S

X ( 1 + M) X 2

E

IMPLICITO

(NO PRECISA

SER

ARMAZENADO)

S|EXPONTE|MANTISSA

1 | 8 BITS | 23 BITS 32 BITS

PESO: 127

PRECISO DUPLA

(-1)

S

X ( 1 + M) X 2

E

IMPLICITO

(NO PRECISA

SER

ARMAZENADO)

S|EXPONTE|MANTISSA

1 | 11 BITS | 52 BITS 64 BITS

PESO: 1023

SISTEMAS DIGITAIS

ARITMETICA EM PONTO FLUTUANTE

REPRESENTAO DE -0,75 NO PADRO IEEE 754,

PRECISO SIMPLES

- 0,75 = - 3 / 4 -> - 0.112

0

-> - 1.1 X 2

-1

1|01111110|10000000000000000000000

31 30................ 23 22 0

+ 127

QUAL O NUMERO QUE O VETOR BINARIO EST REPRESENTANDO

EM PRECISO SIMPLES ?

1|10000001|01000000000000000000000

-

129 127 = 2

1 1/4

- 1,25 X 2

2

= -5

SISTEMAS DIGITAIS

ADIO EM PONTO FLUTUANTE

S M

E

S M

E

+

S M

S M

E

+

00..0

E

E

M S

NORMALIZAO

OVERFLOW ?

UNDERFLOW ?

EXCEO

OBS: ARREDONDAR A MANTISSA

PODE DESNORMALIZAR

SISTEMAS DIGITAIS

EXEMPLO ADIO EM PONTO

FLUTUANTE

1.001

1.001

+

10.010

NORMALIZAR

1.001

0.010

-

0.111

NORMALIZAR

DEPOIS DE IGUALADOS OS EXPOENTES...

SISTEMAS DIGITAIS

ADIO EM PONTO FLUTUANTE

HARDWARE PARA SOMA EM PONTOFLUTUANTE

S| EXP|MANTISSA S| EXP|MANTISSA

UA EX -

MUX

C

MUX MUX

DESL. DIR.

UA MANT +

MUX

MUX

DIR/ESQ

INC/DEC

COMPARAO DE

EXPOENTES

DESLOCAMENTO DIREITA

DO MENOR NUMERO

SOMA

NORMALIZAO

SISTEMAS DIGITAIS

ADIO EM PONTO FLUTUANTE

HARDWARE PARA SOMA EM PONTOFLUTUANTE (CONTINUAO)

UAMANT +

DIR/ESQ

INC/DEC

NORMALIZAO

MUX

MUX

C

HARD. DE ARREDONDAMENTO

S| EXPOENTE| MANTISSA

ARREDONDAMENTO

REPETIDO

DO SLIDE

ANTERIOR

SISTEMAS DIGITAIS

MULTIPLICAO EM PONTO

FLUTUANTE

S M

X

E

M

NORMALIZAO

OVERFLOW ?

UNDERFLOW ?

EXCEO

OBS: ARREDONDAR A MANTISSA

PODE DESNORMALIZAR

E

E

S M

P + -

S

SISTEMAS DIGITAIS

EX. DE MULTIPLICAO DE

MANTISSAS EM PONTO FLUTUANTE

1.001

1.001

X

1001

0000

0000

1001

1.010001

1.100

1.100

X

1100

0000

1100

0000

10.010000

NORMALIZAR

SISTEMAS DIGITAIS

TIPOS NUMERICOS NO PADRO IEEE

NUMERO |SINAL |EXPOENTE | MANTISSA

NORMALIZADO|+/- |0 < ... < 11..111 | QUALQUER = 0

NO NORMAL |+/- | 0 | QUALQUER = 0

ZERO |+/- | 0 | 0

INFINITO |+/- | 111............11 | 0

NaN |+/- |111 ...........11 | QUALQUER = 0

GERAO DE NaN : / , - , 0/0

SISTEMAS DIGITAIS

EXERCICIO 12

1. CONVERTA OS SEGUINTES NUMEROS PARA O FORMATO IEEE 754 ,

USANDO A PRECISAO SIMPLES. FORNEA O VETOR RESULTADO

COMPACTADO COM 8 DIGITOS HEXADECIMAIS

A. 9 B. 5/32 C.-5/32 D. 6,125

2. CONVERTA OS SEGUINTES NUMEROS, EXPRESSOS NO FORMATO

IEEE754 , PRECISAO SIMPLES , COMPACTADOS EM HEXADECIMAL, PARA

DECIMAL

A. 42E48000 B. 3F880000 C. C7F00000

3. SOME OS NUMEROS 3EE00000H E 3D800000H EXPRESSOS NO

FORMATO IEEE 754 , PRECISAO SIMPLES. O RESULTADO

NORMALIZADO DEVE SER FORNECIDO COMPACTADO EM HEXADECIMAL.

4. MULTIPLIQUE OS NUMEROS ACIMA

5. DIVIDA OS NUMEROS ACIMA

SISTEMAS DIGITAIS

EXERCICIO 12

6, UM PROGRAMA CALCULA REQ PELA EXPRESSAO R

EQ

=1/ ( 1/R1 +I/ R2 + 1/R3 )

SABENDO QUE R1=R2 = R3 = 0, E QUE OS NUMEROS ESTAO NO FORMATO IEEE

754 , PRECISAO SIMPLES , QUAIS SAO OS NUMEROS( NO FORMATO ACIMA)

UTILIZADOS E GERADOS PARA CALCULAR R

EQ

?

7. MOSTRE QUE A CONVERSO DE UM NUMERO FRACIONARIO DECIMAL EM

BINARIO ENVOLVE REPETIDAS MULTIPLICAES POR 2. A CADA PASSO, A PARTE

FRACIONARIA DO NUMERO DECIMAL MULTIPLICADA POR 2. O DIGITO A

ESQUERDA DA VIRGULA DECIMAL SER 0 OU 1 E CONTRIBUIR PARA A

CORRESPONDENTE PARTE BINARIA, COMEANDO PELO BIT MAIS SIGNIFICATIVO.

A PARTE FRACIONARIA DO PRODUTO USADA COMO MULTIPLICANDO NO

PROXIMO PASSO.

CONVERTA 0,5125 PARA O FORMATO IEEE 754, PRECISO SIMPLES.

SISTEMAS DIGITAIS

MODULOS SEQUENCIAIS FIXOS

REGISTRADOR

REGISTRADOR DE DESLOCAMENTO

CONTADOR

SISTEMAS DIGITAIS

REGISTRADORES

USO: ARMAZENAMENTO DE ESTADOS EM MAQUINAS SEQUENCIAIS

LD

CLK

CLR

REG

X

Z

N

ENTRADAS:

X =(X

N-1

,...X

0

) X

I

e {0,1}

LD, CLK, CLR e {0,1}

ESTADO:

S=(S

N-1

,...S

0

) S

I

e {0,1}

SAIDAS:

Z =(Z

N-1

,...Z

0

) Z

I

e {0,1}

FUNES

ESTAD0

S(T +1) = X(T) SE LD(T) =1 E CLR (T) =0

= S(T) SE LD(T) =0 E CLR (T) =0

= 0 SE CLR(T) = 1

SAIDA

Z(T) = S(T)

ESPECIFICAO

SISTEMAS DIGITAIS

IMPLEMENTAO DO BIT I DO REGISTRADOR

D Q

CLK

CLR

LD

0 1

X I

Z I

CLK

CLR

REGISTRADORES

SISTEMAS DIGITAIS

EXERCICIO 13

PROJETE UM SISTEMA COM A ESPECIFICAO

ABAIXO, USANDO:

1. FLIP-FLOPs TIPO D

2. REGISTRADORES

0

A =0

1

A =1

A =0

3

A =1

A =0

2

A =1

A =0

A=1

SISTEMAS DIGITAIS

EXERCICIO 13 SOLUO

S1S0 S1

+

A=0 A=1

0 0 0 0

0 1 0

1

1 1 1

1

1 0 1

0

S1S0 S0

+

A=0 A=1

0 0 0 1

0 1 1

1

1 1 1

0

1 0 0

0

S1

+

= S1. #A + S0.A S0

+

= S0. #A + #S1.A

SISTEMAS DIGITAIS

EXERCICIO 13 SOLUO

S1

+

= S1. #A + S0.A

S0

+

= S0. #A + #S1.A

IMPLEMENTAO COM FLIP-FLOPs

D Q

CLK

#Q

D Q

CLK

#Q

S1

+

S0

+

S1

S0

A

O

R

O

R

SISTEMAS DIGITAIS

EXERCICIO 13 SOLUO

S1

+

= S1. #A + S0.A

S0

+

= S0. #A + #S1.A

IMPLEMENTAO COM REGISTRADOR

LD X1 X0

CLK

CLR Z1 Z0

A

CLK

CLR

REG

SISTEMAS DIGITAIS

REGISTRADORES DE DESLOCAMENTO

USO: TRANSFERENCIA SERIAL DE BITS

XR XL

CLK

CTRL

REG

X

Z

N

ENTRADAS:

X =(X

N-1

,...X

0

) X

I

e {0,1}

XR, XL ,CLK e {0,1}

CTRL e {CARGA,ESQUERDA, DIR,NADA}

ESTADO:

S=(S

N-1

,...S

0

) S

I

e {0,1}

SAIDAS:

Z =(Z

N-1

,...Z

0

) Z

I

e {0,1}

FUNES

ESTAD0

S(T +1) =S(T) SE CTRL = NADA

= X(T) SE CTRL = CARGA

= (S

N-2

,...S

0

,

,

XL) SE CTRL = ESQ.

= (XR,S

N-1

, ...S

1

) SE CTLR = DIR

SAIDA

Z(T) = S(T)

ESPECIFICAO

2

SISTEMAS DIGITAIS

D Q

CLK

X I

Z I

REGISTRADORES DE

DESLOCAMENTO(IMPLEMENTAO BIT I)

D Q

CLK

IMPLEMENTAO

D Q

CLK

3 2 1 0

S1

S0

CTRL1

CTRL0

CTRL1 CTRLO

0 0 NADA

0 1 ESQ

1 0 DIR

1 1 CARGA

SISTEMAS DIGITAIS

EXERCICIO 14

1. PROJETE UM SISTEMA COM A SEGUINTE ESPECIFICAO:

ENTRADA: X(T) ,SAIDA: Y(T) FUNO: X(T).X(T-8) =1

2. PROJETE UM SISTEMA COM A SEGUINTE ESPECIFICAO:

ENTRADA: X(T) ,SAIDA: Y(T)

FUNO: X(T-8,T)) = 011101101

SISTEMAS DIGITAIS

INTERCONEXO ENTRE REGISTRADORES

VIA BARRAMENTO DE DADOS

#LD X

#OE REG

CLK Z

CONTROLE

DE ALTA

IMPEDANCIA

DBO

DB7

DB: DATA BUS

8

SISTEMAS DIGITAIS

CONTROLE DE ALTA IMPEDANCIA

VCC

GND #OE

CI

VCC

GND #OE

CI

VCC

GND #OE

CI

VCC

GND #OE

CI

GND

NIVEL

1

GND

NIVEL

0

VCC

NIVEL

Z

3

O

ESTADO

ALTA

IMPEDANCIA

ESTAGIO DE

SAIDA

SISTEMAS DIGITAIS

INTERCONEXO ENTRE REGISTRADORES

VIA BARRAMENTO DE DADOS

#LD X

#OE REGA

CLK

Z

#LD X

#OE REGB

CLK

Z

#LD X

#OE REGC

CLK

Z

N BITS

REPRESENTAO SIMPLIFICADA

SISTEMAS DIGITAIS

INTERCONEXO ENTRE REGISTRADORES

VIA BARRAMENTO DE DADOS

#LD X

#OE REGA

CLK

Z

#LD X

#OE REGB

CLK

Z

#LD X

#OE REGC

CLK

Z

N BITS

REPRESENTAO SIMPLIFICADA (METODO REUNIO DE LINHAS)

SISTEMAS DIGITAIS

INTERCONEXO ENTRE REGISTRADORES

VIA BARRAMENTO DE DADOS

ESTADO DOS SINAIS PARA TRANSFERIR O CONTEUDO DO REG A PARA O REG C

# LDA| # LDB| #LDC| #OEA| #OEB|# OEC

1 1 0 0 1 1

A TRANSFERENCIA OCORRE NA TRANSIO DO CLOCK

DIAGR DE TEMPO DOS SINAIS NA TRANSFERENCIA DO DADO 1011 DO REG A PARA O

REG C

CLK

#LDC

#OEA

DB3

DB2

DB1

DB0

... ...

... ...

...

...

...

...

0

1

1

1

CLK

#LDC

DB3

#OEA

...

...

1011

DB0

SISTEMAS DIGITAIS

INTERCONEXO ENTRE REGISTRADORES

VIA BARRAMENTO DE DADOS

#LD

#OE REG

CLK X/Z

CONTROLE

DE ALTA

IMPEDANCIA

REGISTRADOR

BIDIRECIONAL

SISTEMAS DIGITAIS

INTERCONEXO ENTRE REGISTRADORES

VIA BARRAMENTO DE DADOS

#LD

#OE REG

CLK X/Z

CONTROLE

DE ALTA

IMPEDANCIA

REGISTRADOR

BIDIRECIONAL

REPRESENTAO SIMPLIFICADA

SISTEMAS DIGITAIS

INTERCONEXO ENTRE REGISTRADORES

VIA BARRAMENTO DE DADOS

#LD

#OE REG

CLK X/Z

CONTROLE

DE ALTA

IMPEDANCIA

REGISTRADOR

BIDIRECIONAL

REPRESENTAO SIMPLIFICADA

METODO REUNIAO DAS LINHAS

SISTEMAS DIGITAIS

EXERCICIO 15

1. OS REG`s A, B, C ESTO INICIALMENTE CARREGADOS COM 1011,1000,0111.

OS SINAIS DA FIG. SO ENTO APLICADOS AOS REGISTRADORES.

A. DETERMINE O CONTEUDO DE CADA REG NOS INSTANTES T1,T2,T3,T4

B. DESCREVA O QUE ACONTECERIA SE #LDA =0 QUANDO O TERCEIRO PULSO

DE CLOCK OCORESSE.

A B C

T3 T1 T2 T4

CLK

#0EA

#0EB

#0EC

#LDA

#LDB

#LDC

C. DESENHE O SINAL EM DB3

SISTEMAS DIGITAIS

EXERCICIO 15 CONTINUAO

2.A FIG. MOSTRA 2 DISPOSITIVOS EXTRAS QUE FORAM CONECTADOS AO BUS

DE DADOS. UM DELES UM CONJUNTO DE CHAVES COM BUFFERS, QUE

PODEM SER USADAS PARA ENTRADA DE DADOS MANUAL EM QQ DOS

REGs DO BUS. O OUTRO UM REG DE SAIDA QUE UTILIZADO PARA

ARMAZENAR QQ DADO QUE ESTEJA NO BUS DURANTE UMA

TRANSFERENCIA DE DADOS E APRESENT-LO A UM CONJUNTO DE LEDS.

A. SUPONHA QUE TODOS OS REGs

CONTENHAM 0000.FAA UM RESUMO

DA SEQUENCIA DE OPERAES

NECESSARIAS PARA CARREGAR OS REG`S

COM OS SEGUINTES DADOS, PELAS CHAVES:

A: 1011 B: 0001 C: 1110

B. QUAL SER O ESTADO DOS LEDS NO

FINAL DESTA SEQUENCIA ?

A B C

CLK

D Q

D Q

D Q

D Q

VCC

#ESW GND

VCC

CH0

CH3

CH1

CH2

CLK

L3

L2

L1

L0

SISTEMAS DIGITAIS

EXERCICIO 15 CONTINUAO

A B C

CLK

D Q

D Q

D Q

D Q

VCC

#ESW GND

VCC

CH0

CH3

CH1

CH2

CLK

L3

L2

L1

L0

A1 #O

3

A0 #O

2

#E #O

1

#O

0

A1 #O

3

A0 #O

2

#E #O

1

#O

0

DEC. DUAL

GND

GND

OS1

OS0

IS1

IS0

#ESW

#OEC

#OEB

#OEA

#LDC

#LDB

#LDA

T0 T1 T2 T3

OS1

OS0

IS1

IS0

CLK

3. SUPONDO QUE

TODOS OS REG`s

ESTO COM 0000 NO

INSTANTE TO E AS

CHAVES ESTO NA

POSIO MOSTRADA

NA FIGURA

A. QUAL O CONTEUDO

DE CADA REG. EM

T1, T2 E T3 ?

B. PODE OCORRER

CONTENO DE

BARRAMENTO NESTE

CIRCUITO ? EXPLIQUE

Lj: LED

SISTEMAS DIGITAIS

EXERCICIO 16

UMA MEMORIA CONTEM VARIOS REGISTRADORES, UMA VIA CODIFICADA PARA

SELECIONAR UM REGISTRADOR, UMA VIA BIDIRECIONAL PARA LEITURA OU

ESCRITA DE DADOS, UM SINAL DE COMANDO DE LEITURA , UM SINAL DE

COMANDO DE ESCRITA E UM SINAL DE SELEO DE MEMORIA, CONFORME

MOSTRADO NA FIG. ABAIXO:

REG1

....

REGN-1

REG0

J

B. END

2

J

= N

B. DADOS

B. DADOS

#RD

#CS

#WR

SISTEMAS DIGITAIS

EXERCICIO 16 - CONTINUAO

1. PROJETE UMA MEMORIA 8 x 8 ( OITO REGISTRADORES OITO

ENDEREOS OITO POSIES CADA UMA COM OITO BITS), USANDO OS

COMPONENTES ABAIXO:

I0 00

I1 01

I2 O2

I3 O3

I4 04

I5 05

I6 O6

I7 O7

STB

#OE

LATCH

STB #OE Q O

0 0 Q Q

0 1 Q Z

1 0 I I

1 1 I Z

I

O

Q

3

S

I0 #00

I1 #01

I2 #O2

#O3

#04

#05

#O6

#O7

#E

DECOD.

I

SISTEMAS DIGITAIS

EXERCICIO 16 - CONTINUAO

2. PROJETE UM MODULO DE MEMORIA 16 x 8,

USANDO MEMORIAS 8 x 8 :

3. PROJETE UM MODULO DE MEMORIA 8 x 16,

USANDO MEMORIAS 8 x 8 :

USO MAIS COMUM: CONTAR EVENTOS

REG

SISTEMAS DIGITAIS

CONTADOR MODULO P

CNT

| CLK

CLR TC

REG

Z

ENTRADAS:

CNT, CLR,CLK e {0,1}

ESTADO:

S: = S

e {0,1,2 ...P-1}

SAIDAS:

Z: = Z

e {0,1,2 ...P-1}

TC e {0,1}

FUNES

ESTAD0

S(T +1) =(S(T)+ CNT) MOD P SE CLR =0

S(T +1) = 0 SE CLR =1

SAIDA

Z(T) = S(T)

TC(T) = 1 SE S(T) = P-1 , CNT=1 E CLR =0

= 0 CASO CONTRARIO

ESPECIFICAO

CONTAGEM TERMINAL

ASSINCRONO

SISTEMAS DIGITAIS

CONTADOR MODULO P

TIPOS DE CONTADORES

COM RELAO A CONTAGEM

UP : CONTAR P/ CIMA

DOWN : CONTAR P/ BAIXO

UP / DOWN : CONTAR P/ CIMA E P / BAIXO

( NECESSITA DE SINAL DE CONTROLE ADICIONAL)

COM RELAO AO CODIGO

BINARIO

BCD

ANEL

SISTEMAS DIGITAIS

CONTADOR

MODULO P

ESTADO |BINARIO | BCD | ANEL

0 |0000 |0000 |00000001

1 |0001 |0001 |00000010

2 |0010 |0010 |00000100

3 |0011 |0011 |00001000

4 |0100 |0100 |00010000

5 |0101 |0101 |00100000

6 |0110 |0110 |01000000

7 |0111 |0111 |10000000

8 |1000 |1000 |

9 |1001 |1001 |

10 |1010

11 |1011

12 |1100

13 |1101

14 |1110

15 |1111

REG

SISTEMAS DIGITAIS

CONTADOR BINARIO COM ENTRADA

PARALELA, MODULO 16

CNT I3 I2 I1 I0

| CLK

CLR TC

LD O3 O2 O1 O0

REG

Z

ENTRADAS:

I : I = (I3,I2,I1,I0) I

J

{0,1} I e {0,1 ...15}

LD, CNT, CLR,CLK e {0,1}

ESTADO:

S : S = (S3,S2,S1,S0) S

J

{ 0,1} S e {0,1...15}

SAIDAS:

Z : Z = (Z3,Z2,Z1,Z0) Z

J

{0,1} Z e {0,1...15}

TC e {0,1}

FUNES

ESTAD0

S(T +1) =(S(T )+ CNT) MOD16 SE LD = 0

S(T +1) = I SE LD = 1

S(T +1) = 0 SE CLR = 1

S(T +1) = S(T) CASO CONTRARIO

ESPECIFICAO

I

SAIDA

Z(T) = S(T)

TC(T) = 1 SE S(T) = 15 E CNT = 1,CLR=0

= 0 CASO CONTRARIO

LD E CNT, SE

ATIVADOS AO MESMO

TEMPO, PREVALECE

O LD

SISTEMAS DIGITAIS

CONTADOR MODULO K (2 s k s 16)

CNT I3 I2 I1 I0

| CLK

CLR TC

LD O3 O2 O1 O0

EX: CONTADOR MODULO 12 USANDO CONTADOR MODULO 16

0 0 0 0

TC

NO USADA

SISTEMAS DIGITAIS

DIVISOR DE FREQUENCIA MODULO K

(2 s k s 16)

CNT I3 I2 I1 I0

| CLK

CLR TC

LD O3 O2 O1 O0

EX: DIVISOR DE FREQUENCIA MODULO 9 USANDO CONTADOR

MODULO 16

0 1 1 1 (16- 9)

X

Z

X

Z

7 8 9 10 11 12 13 14 15 7 8 9 10 11 12 13 14 15

FreqZ = FreqX / 9

1

0

SISTEMAS DIGITAIS

CONTADOR USO COMUM

CONTADOR DE EVENTOS

DOWN CLR

| CLK CONTADOR

UP

COMPARADOR

Eout Sout

NUMERO MAXIMO

DE ESPAOS

LOTADO VAGAS

SISTEMAS DIGITAIS

CONTADOR - USO COMUM

CONTROLAR UMA SEQUENCIA FIXA DE AES EM UM

SISTEMA DIGITAL

DECODIFIC.

0

1

2

3

4

5

CONTADOR

MODULO 6

| CLK

SEQUENCIA DE AES

0 ZERAR REGISTRADORES

1 ENTRADA A

2 ENTRADA B

3 COMPUTAR

4 COMPUTAR

5 SAIDA C

OR

ZERAR

ENTR. A

ENTR. B

COMPUTAR

SAIDA C

SISTEMAS DIGITAIS

CONTADOR - USO COMUM

GERAR SINAIS DE TEMPO

DECOD.

0

1

2

3

4

5

6

7

CONTADOR

MODULO 6

| CLK

S Q

| CLK

R #Q

TS0

S Q

| CLK

R #Q

TS1

S Q

| CLK

R #Q

TS2

ESTADO

TS0

TS1

TS2

7 0 2 1 3 4 5 6 7 0

MESMA FREQUENCIA

FASES DIFERENTES

FF SR

SINCRONO

SISTEMAS DIGITAIS

CONTADOR USO COMUM

GERAR SINAIS DE TEMPO

CONTADOR S0

MODULO 4

| CLK S1

CLK0

CLK

CLK0

CLK2

CLK4

AND

AND

CLK2

CLK4

FREQUENCIAS

DIFERENTES

0 1 2 3

SISTEMAS DIGITAIS

CONTADOR - USO NO CONVENCIONAL

CONTADOR USADO COMO REGISTRADOR DE ESTADO NA

IMPLEMENTAO DE UMA MAQUINA SEQUENCIAL

2 3

4

CNT = 1 LD = 0

CNT = 0 LD = 0

CNT = 0 LD = 1

CNT CONTADOR

LD

CLK

2 3 4

SISTEMAS DIGITAIS

EXERCICIO 17

PROJETAR A MAQUINA SEQUENCIAL ESPECIFICADA ABAIXO,

USANDO CONTADOR MODULO 16 , QUATRO MUX`s 8 x 1 E

INVERSORES

S0

S1

S2

S3 S4

S5

S6

#a/0

a/0

_ /0

_ /0

#b/1

b/0

c/0 #c/0

_ /0

#b/0

b/0

SISTEMAS DIGITAIS

EXERCICIO 17 SOLUO

S0

S1

S3

S4

S2

S5

S6

CNT I

3

I

2

I

1

I

0

CLK CONTADOR

LD O

3

O

2

O

1

O

0

#O

2

#O

1

#O

0

#O

2

#O

1

O

0

#O

2

O

1

#O

0

#O

2

O

1

O

0

O

2

#O

1

#O

0

O

2

#O

1

O

0

O

2

O

1

#O

0

CNT = #O

2

#O

1

#O

0

a + #O

2

#O

1

O

0

+ #O

2

O

1

#O

0

+

#O

2

O

1

O

0

b + O

2

#O

1

#O

0

#c + O

2

#O

1

O

0

LD = O

2

#O

1

#O

0

c + O

2

O

1

#O

0

I2 I1 I0 SAIDA

O

2

O

1

#O

0

b 0 0 0 #O

2

O

1

O

0

#b 1

O

2

#O

1

#O

0

c 0 0 1

O

2

O

1

#O

0

#b 0 0 1

SISTEMAS DIGITAIS

EXERCICIO 17 - SOLUO

S2

S1

S0

O2

O1

O0

0 1 2 3 4 5 6 7

a 1 1 b #c 1 0 0 0 0 0 0 c 0 1 0

CNT

LD

0 1 2 3 4 5 6 7

0 0 0 0 c 0#b 0

0 1 2 3 4 5 6 7

0 0 0#b 0 0 0 0

0 1 2 3 4 5 6 7

I0

SAIDA

O1

O0

O2

O0

O0

O1

O2

O1

O2

BIT MAIS SIGNIFICATIVO

SISTEMAS DIGITAIS

EXERCICIO 18

1. A FIG. MOSTRA COMO UM MUX PODE SER UTILIZADO PARA GERAR

FORMAS DE ONDA LOGICA COM QQ PADRO DESEJADO. O PADRO

PROGRAMADO USANDO CHAVES ON-OFF E UM CONTADOR.

DESENHE A FORMA DE ONDA Z PARA A POSIO DAS CHAVES DA FIGURA.

SUBSTITUA O CONTADOR MODULO 8 POR UM CONTADOR MODULO 16 E CONECTE O

BIT MSB DO CONTADOR NA ENTRADA #E DO MUX. DESENHE A FORMA DE

ONDA EM Z

CONTADOR

MODULO 8

| CLK

CLK

Z

I7 I6 I5 I4 I3 I2 I1 I0

#E

VCC

GND

SISTEMAS DIGITAIS

EXERCICIO 18 CONTINUAO

2. MOSTRE COMO CONECTAR 2 CIS, DO TIPO ABAIXO, PARA FORMAR

UM CONTADOR DE 8 BITS QUE DIVIDE A FREQUENCIA DO CLOCK POR

100. UTILIZE A SAIDA #TCD DE UM ESTAGIO COMO CLOCK DO

SEGUNDO ESTAGIO. ( ESPECIFICAO: O CONTADOR DEVE SER DOWN E

DEVE SER CARREGADO QUANDO AMBOS OS ESTAGIOS ESTIVEREM

SIMULTANEAMENTE EM SUAS CONTAGENS FINAIS)

#PL P0 P1 P2 P3

| CPU #TCU

| CPD #TCD

MR Q0 Q1 Q2 Q3

PL :carga paralela

CPU : clock para contagem UP

CPD:clock para cont agem DOWN

MR : master reset

MONOESTAVEL

Q

MONO ESTAVEL

|CLK #Q

VCC

R

C

T ~ RC

CLR

D #Q

|CLK Q

GND

VCC

Vref

VCC

A

B

S

COMPARADOR ANALOGICO

A=B -> S =1

A = B -> S =0

SISTEMAS DIGITAIS

SISTEMAS DIGITAIS

EXERCICIO 18 CONTINUAO

3. A FIG. MOSTRA COMO UM CONTADOR DECRESCENTE COM CARGA PODE SER USADO EM UM

CIRCUITO TEMPORIZADOR PROGRAMAVEL. A FREQ. DO CLOCK DE ENTRADA DE 1HZ. AS

CHAVES S1 AT S4 SO USADA PARA AJUSTAR O CONTADOR PARA UMA CONTAGEM INICIAL,

QUANDO UM PULSO APLICADO A #PL. A OPERAO DO TEMPORIZADOR INICIADA

PRESSIONANDO-SE O BOTO DE INICIO. O FFZ USADO PARA ELIMINAR OS EFEITOS DA

TREPIDAO (BOUNCE) DO CONTATO DO BOTO INICIO. O MONO USADO PARA FORNECER UM

PULSO BEM ESTREITO PARA #PL. A SAIDA DO FFX TER UMA FORMA DE ONDA QUE VAI PARA

NIVEL 1 POR UM NUMERO DE SEGUNDOS IGUAL AO NUMERO PRESENTE NAS CHAVES.

VCC

GND

MR P3 P2 P1 P0 |CPU

CONTADOR DOWN |CPD

#PL #TCD

1HZ

J

K

X

+CLK

#CLR

J

Z +CLK

#SET K

VCC

GND

GND

VCC

BOTO

INICIO

#Y MONO | CLK

Tp = 100 NS

ASSINCRONO

SISTEMAS DIGITAIS

EXERCICIO 18 CONTINUAO

A. ADMITA QUE TODOS OS FF`S E CONTADOR ESTO NO ESTADO

0. ANALISE E EXPLIQUE A OPERAO DO CIRCUITO,

MOSTRANDO AS FORMAS DE ONDA, PARA O CASO DAS

CHAVES PROGRAMADAS COM O NUMERO 4. NO DEIXE DE

EXPLICAR A FUNO DO FFX.

B. POR QUE A SAIDA DO TEMPORIZADOR NO PODE SER

TOMADA DA SAIDA DE #TCD?

C. POR QUE A CHAVE DE INICIO NO PODE SER USADA PARA

DISPARAR O MONO DIRETAMENTE?

D. O QUE ACONTECERIA SE CHAVE INICIO FOSSE MANTIDA

ACIONADA POR UM LONGO PERIODO? INCLUA A LOGICA

NECESSARIA PARA GARANTIR QUE A MANUTENO DO

ACIONAMENTO DA CHAVE INICIO NO V AFETAR A

OPERAO DO TEMPORIZADOR.

SISTEMAS DIGITAIS

CONTADOR JOHNSON

CONTADOR EM ANEL COM 3 BITS

D Q D Q D Q

CONTAGEM

100

010

001

100

010

001

CONTADOR EM JOHNSON COM 3 BITS

D Q D Q

D # Q

Q

CONTAGEM

100

110

111

011

001

000

CLK

Q

CLK

Q

SISTEMAS DIGITAIS

EXERCICIO 19

1. DETERMINE A FREQUENCIA DOS PULSOS NOS PONTOS W,X,Y,Z

NO CIRCUITO ABAIXO:

CONTADOR

EM ANEL

DE 16BITS

160KHZ

W

CONTADOR

PARALELO

DE 4 BITS

X CONTADOR

DE

PULSAO

MODULO 25

Y

CONTADOR

JOHNSON

DE 4 BITS

Z

2. MODIFIQUE O CIRCUITO DA FIGURA ABAIXO PARA GERAR UMA FORMA DE

CONTROLE QUE VAI PARA NIVEL 0 DESDE T20 AT T24. A MODIFICAO NO

REQUER LOGICA ADICIONAL.

CONTADOR UP + +CLK

Q2 Q1 Q0

CONTADOR UP + +CLK

Q2 Q1 Q0

A2 A1 A0 DECOD. E2 #E1 #E0

#O7 #O6 #O5 #O4 # O3 #O2 #O1 #O0

SAIDA

T0 T1 T2 ....

CONTADORES ZERADOS

SISTEMAS DIGITAIS

FREQUENCIMETRO

267

CLEAR

1S

0,1S

0,01S

INT.

AMOSTR.

FX

CLR

CONTADOR | CLK

DECODIFICADOR

CONTROLE DO

DISPLAY

FREQUENCIA DESCONHECIDA FX

PULSO DE AMOSTRAGEM PX

FX

PX

CLEAR

Z

Z

PAINEL

PLACA

SISTEMAS DIGITAIS

FREQUENCIMETRO

PARA A FREQUENCIA, DESCONHECIDA PELO FREQUENCIMETRO, DE 3792 PULSOS

POR SEGUNDO, DETERMINE A SAIDA DO CONTADOR APS O INTERVALO DE

AMOSTRAGEM DE:

A. 1s B. 0,1s C. 0,01s

___________________________________________________________________________________________

OBS:

FX = 2,4HZ

1 2

1 2 3

1s

CONTAGEM

CONTAGEM

0,4s

SISTEMAS DIGITAIS

FREQUENCIMETRO

INTERVALO DE AMOSTRAGEM

CLK

100KHZ

DIV10 DIV10 DIV10 DIV10 DIV10

10KHZ 1KHZ 100HZ 1HZ 10HZ

1

2

3

4

5

6

1s

0,1s

10ms 1ms

100us

10us

Q J

+CLK

#Q K

PX

CHAVE DE SELEO PARA

INTERVALO DE AMOSTRAGEM

VCC

VCC

CLK

TEMPO DE AMOSTRAGEM

SISTEMAS DIGITAIS

EXERCICIO 19-A:FREQUENCIMETRO

INTERVALO DE AMOSTRAGEM

ADMITA QUE O CONTADOR CONSTRUIDO COM 3 CONTADORES BCD EM

CASCATA, COM OS RESPECTIVOS DISPLAYS. SE A FREQUENCIA DESCONHECIDA

ESTIVER ENTRE 1KHZ E 10KHZ, QUAL A MELHOR ESCOLHA PARA A POSIO

DA CHAVE.

DISPLAY

1s 0,1s 10mS

1ms 100us 10us

MENOR FREQ.

MAIOR FREQ.

1KHZ -> 1ms

10KHZ -> 100us

SISTEMAS DIGITAIS

FREQUENCIMETRO (CLEAR AUTOMATICO)

267

CLEAR

1S

0,1S

0,01S

INT.

AMOSTR.

CLR |CLK

CONTADOR

DECODIFICADOR

CONTR. DISPLAY

Q J

+CLK

#Q K

VCC

VCC

Q J

+CLK

#Q K

VCC

VCC

MONO

Q |CLK

SISTEMAS DIGITAIS

FREQUENCIMETRO (CLEAR AUTOMATICO)

FORMAS DE ONDA

Q

+CLK

Q

+CLK

Q

|CLK

CONTADOR

CLEAR

CLK

CONTADOR

ZERADO

CONTADOR

CONTANDO

CONTADOR PARADO

DISPLAY EXIBINDO A FREQUENCIA

SISTEMAS DIGITAIS

FREQUENCIMETRO (CLEAR AUTOMATICO)

COMO O DISPLAY EST CONECTADO DIRETAMENTE NAS SAIDAS DO CONTADOR, O

DISPLAY MOSTRAR A OPERAO DE RESET E A CONTAGEM. ISTO TORNA MUITO

DIFICIL A LEITURA DO DISPLAY PARA DETERMINAR A FREQUENCIA DESCONHECIDA,

EXCETO PARA INTERVALOS DE AMOSTRAGEM LENTOS.

ESTE PROBLEMA PODE SER RESOLVIDODA SEGUINTE MANEIRA:

CLR |CLK

CONTADOR

DECODIFICADOR

DISPLAY

Q J

+CLK

#Q K

VCC

VCC

Q J

+CLK

#Q K

VCC

VCC

MONO

Q |CLK

REG +CLK

SISTEMAS DIGITAIS

FREQUENCIMETRO (CLEAR AUTOMATICO)

FORMAS DE ONDA

Q

+CLK

Q

+CLK

Q

|CLK

CONTADOR

CLEAR

CLK

CONTADOR

ZERADO

CONTADOR

CONTANDO

DISPLAY EXIBINDO

SOMENTE A FREQUENCIA

+ CLK REG

SISTEMAS DIGITAIS

DISPOSITIVOS DO TIPO PADRO

COMBINACIONAIS

DECODIFICADOR

CODIFICADOR

MULTIPLEXADOR

DEMULTIPLEXADOR

DESLOCADOR-P

SOMADOR

SUBTRATOR

UNID. ARITMETICA E LOGICA

COMPARADOR

SEQUENCIAIS

REGISTRADOR

REGISTRADOR DE DESLOCAMENTO

CONTADOR

PLD

SISTEMAS DIGITAIS

DISPOSITIVOS LOGICOS PROGRAMAVEIS

FF

G G

FF

FF

FF G

FF

G

SE AS

CONEXES

PUDEREM SER

ABERTAS ESTE

DISPOSITIVO

PROGRAMAVEL

FF: FLIP-FLOP

G: GATE

PLD

SISTEMAS DIGITAIS

DISPOSITIVOS LOGICOS PROGRAMAVEIS

CONEXO

FUSIVEL

ELETRONICO

CHAVE

ELETRONICA

PROGRAMAVEL UMA NICA

VEZ

PROGRAMAVEL DIVERSAS

VEZES

CORRENTE

FLIP- FLOP

SISTEMAS DIGITAIS

DISPOSITIVOS LOGICOS PROGRAMAVEIS

PROGRAMAO DO PLD

PELO FABRICANTE

PELO PROJETISTA

SISTEMAS DIGITAIS

DISPOSITIVOS LOGICOS PROGRAMAVEIS

IDEIA BASICA DE PROGRAMAO DE PLD COMBINACIONAL

COM 3 ENTRADAS E UMA SAIDA

A

B

C

F

#A#B#C

#A#B C

#A B #C

#A B C

A#B#C

A#B C

A B #C

A B C

+

SELECIONAR QUAIS TERMOS VO FAZER PARTE DO OU, PARA

QUE QQ FUNO POSSA SER IMPLEMENTADA

SISTEMAS DIGITAIS

DISPOSITIVOS LOGICOS PROGRAMAVEIS

TIPOS DE PLDs

PLA

PAL

ROM

PSA

PROGRAMABLE ARRAY LOGIC

PROGRAMABLE LOGIC ARRAY

READ ONLY MEMORY

PROGRAMABLE SEQUENCIAL ARRAY

FIELD PROGRAMABLE GATE ARRAY

SPLD

CPLD

SPLDs AGRUPADAS

FPGA

PLA(MATRIZ LOGICA PROGRAMAVEL)

SISTEMAS DIGITAIS

PLA

MATRIZ

DE

AND

MATRIZ

DE OR

ESCOLHA DOS

TERMOS DA

FUNO

ESCOLHA DAS

COMBINAES DE

TERMOS PARA

GERAR AS

FUNES DE SAIDA

SAIDAS

PLA (MATRIZ LOGICA PROGRAMAVEL)

SISTEMAS DIGITAIS

1

2

K

1

XN-1 X1 X0

YK-1 Y1 Y0

1

2

R

MATRIZ

AND

MATRIZ

OR

...

...

.

.

CONEXO

PROGRAMAVEL:

PODE SER

DESFEITA

1

.

2

.

K

PLA CIRCUITOS BASICOS

SISTEMAS DIGITAIS

VCC

GND

A

VCC

GND

S

A B S

0 0 1

0 1 0

1 0 0

1 1 0

S = #(A + B)

INVERSOR

VCC

GND

VCC

GND

BUFFER NO INVERSOR

NOR

B

GND

S = (#A . #B)

PLA (MATRIZ LOGICA PROGRAMAVEL)

SISTEMAS DIGITAIS

XI

CIRCUITO CIRCUITO

XI

CIRCUITO

XI XI

CIRCUITO

< ATRASO

MELHOR

CONFIGURAO

PLA (MATRIZ LOGICA PROGRAMAVEL)

SISTEMAS DIGITAIS

ESPECIFICAO

ENTRADA

X = (X

N-1

,...,X

0

) X

I

e {0,1}

SAIDA

Z = (Z

K-1

,...,Z

0

) Z

I

e {0,1}

FUNO

IMPLEMENTAO DE K (N

O

DE ORs) FUNES DE

CHAVEAMENTO COM NO MAXIMO R (N

O

DE AND`S) TERMOS,

SENDO QUE R < 2

N

.

XN-1

1

PLA (MATRIZ LOGICA PROGRAMAVEL)

SISTEMAS DIGITAIS

XN-1

GND

GND

XN-2

GND

GND

VCC

1

2

3

4

1

XN-2

1 2 3 4

PLA (MATRIZ LOGICA PROGRAMAVEL)

SISTEMAS DIGITAIS

GND

GND

GND

GND

VCC

1

2

3

4

1

XN-2

XN-1

XN-1 XN-2 S

0 0 0

0 1 0

1 0 0

1 1 1

S = X

N-1

.X

N-2

2 E 4 ABERTOS

SISTEMAS DIGITAIS

XN-1

GND

GND

GND

GND

1

2

3

4

1

XN-2

XN-1

XN-1 XN-2 S

0 0 0

0 1 0

1 0 1

1 1 0

S = X

N-1

.#X

N-2

PLA

2 E 3 ABERTOS

VCC

SISTEMAS DIGITAIS

XN-1

GND

GND

GND

GND

1

2

3

4

1

XN-2

XN-1

XN-1 XN-2 S

0 0 0

0 1 1

1 0 0

1 1 0

S = #X

N-1

.X

N-2

PLA

1 E 4 ABERTOS

VCC

SISTEMAS DIGITAIS

XN-1

GND

GND

GND

GND

1

2

3

4

1

XN-2

XN-1

XN-1 XN-2 S

0 0 1

0 1 0

1 0 0

1 1 0

S = #X

N-1

.#X

N-2

PLA

1 E 3 ABERTOS

VCC

1

PLA (MATRIZ LOGICA PROGRAMAVEL)

SISTEMAS DIGITAIS

GND

GND

GND

VCC

1

2

R

PARA AND1 OR AND2 , 3 ABERTO

PARA AND1 OR ANDR , 2 ABERTO

1

2

R

1

R 2

GND

VCC

YK-1

YK-1

......

YK2

PLA (MATRIZ LOGICA PROGRAMAVEL)

SISTEMAS DIGITAIS

1

2

2

1

A B C

F2 F1 F0

1

2

3

MATRIZ

AND

MATRIZ

OR

.

.

CONEXO

1

.

2

.

K

EXEMPLO: F2 = A#BC + AB#C

F0 = A#B

SEM CONEXO

EXERCICIO 20

SISTEMAS DIGITAIS

1

2

1

D3 D1 D0

G3

1

2

4

MATRIZ

AND

MATRIZ

OR

.

.

1

IMPLEMENTAR UM CONVERSOR DE CODIGO BCD-GRAY

D2

3

D

0

1

2

3

4

5

6

7

8

9

G

0

1

3

2

6

7

5

4

C

D

G2 G1 G0

4

5

6

EXERCICIO 20 - SOLUO

SISTEMAS DIGITAIS

D

0

1

2

3

4

5

6

7

8

9

G

0

1

3

2

6

7

5

4

C

D

3210

0000

0001

0010

0011

0100

0101

0110

0111

1000

1001

3210

0000

0001

0011

0010

0110

0111

0101

0100

1100

1101

G3 = D3

G2 = D3 + D2

G1 = D2#D1 + #D2D1

G0 = D1#D0 + #D1D0

EXERCICIO 20 SOLUO

SISTEMAS DIGITAIS

1

2

1

D3 D1 D0

G3

1

2

4

MATRIZ

AND

MATRIZ

OR

.

.

D2

3

SOLUO PICTORICA: MOSTRAR OS TERMOS E OS ANDS

ENVOLVIDOS PARA A GERAO DAS FUNES

G3 =D3

G2 = D3 + D2

G1 = #D2D1 + D2#D1

G0 = #D1D0 + D1#D0

5

6

G2 G1 G0

PAL (MATRIZ LOGICA PROGRAMAVEL)

SISTEMAS DIGITAIS

1

1

2

4

MATRIZ

AND

.

.

1

I

Z0

R

XN-1 X1 X0 XN-2

..

ZK-1

.

.

1

2

K

.

.

PROGRAMAVEL

GND

ZJ