Académique Documents

Professionnel Documents

Culture Documents

FPGA Design With Verilog

Transféré par

machnik14866240 évaluation0% ont trouvé ce document utile (0 vote)

143 vues2 pagesThis document discusses FPGA design using Verilog. It covers FPGA architecture and design flow, including concepts like lookup tables and CLBs. It also discusses designing with Verilog HDL, including modules, data types, gates, and behavioral/structural modeling. Additionally, it addresses RTL design using Verilog, including finite state machines and asynchronous state machines. Finally, it describes a lab session that involves simulating and synthesizing a serial transmitter design and pedestrian crossing control project using Verilog.

Description originale:

FPGA DESIGN WITH VERILOG

Copyright

© © All Rights Reserved

Formats disponibles

PDF, TXT ou lisez en ligne sur Scribd

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentThis document discusses FPGA design using Verilog. It covers FPGA architecture and design flow, including concepts like lookup tables and CLBs. It also discusses designing with Verilog HDL, including modules, data types, gates, and behavioral/structural modeling. Additionally, it addresses RTL design using Verilog, including finite state machines and asynchronous state machines. Finally, it describes a lab session that involves simulating and synthesizing a serial transmitter design and pedestrian crossing control project using Verilog.

Droits d'auteur :

© All Rights Reserved

Formats disponibles

Téléchargez comme PDF, TXT ou lisez en ligne sur Scribd

0 évaluation0% ont trouvé ce document utile (0 vote)

143 vues2 pagesFPGA Design With Verilog

Transféré par

machnik1486624This document discusses FPGA design using Verilog. It covers FPGA architecture and design flow, including concepts like lookup tables and CLBs. It also discusses designing with Verilog HDL, including modules, data types, gates, and behavioral/structural modeling. Additionally, it addresses RTL design using Verilog, including finite state machines and asynchronous state machines. Finally, it describes a lab session that involves simulating and synthesizing a serial transmitter design and pedestrian crossing control project using Verilog.

Droits d'auteur :

© All Rights Reserved

Formats disponibles

Téléchargez comme PDF, TXT ou lisez en ligne sur Scribd

Vous êtes sur la page 1sur 2

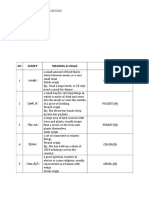

FPGA Design with Verilog

a) FPGA Architecture and Design flow

Concept of programmable hardware

Difference between FPGA and CPLD

Architecture of FPGA

Look up table concept

Programmable routing

CLBs

Input/output blocks

Xilinx XC4000/Spartan architecture

Application of FPGA

FPGA design flow Xilinx(ISE)

Design capture

Synthesis/STA

Timing constraints/ Pin constraints

How to fix timing issues

Care about for clocks

Drive strengths/IO

Report analysis

Place and route

Bit map generation

Bitmap download methods

b) Designing using Verilog-HDL

The module

Nets and Networks of modules

Basic Data Types

Primitive Gates Specifying Time Delays

The Continuous Assignment Statement

Operators and Expressions

Data flow modelling

Structural modelling

Behavioural Descriptions -The Sequential Block

Describing Combinational Logic

Describing Sequential Logic

Design Verification using Test-fixtures

c) RTL level design using verilog

FSM

ASM

RTL Level Design for Serial Transmitter Using verilog-HDL

d) Lab Session

Simulation

Simulation of serial transmitter and analysing wave forms

Project

Concepts of Pedestrian crossing control

Designing of Pedestrian crossing control using verilog HDL

Simulation of Pedestrian crossing control

Synthesis of Pedestrian crossing control

Pre-Requisites:

Digital Design concepts

Basic Concepts of C programming

Vous aimerez peut-être aussi

- Intro To FPGA Design Using MATLAB and Simulink PublishedDocument31 pagesIntro To FPGA Design Using MATLAB and Simulink PublishedelectrocarbonPas encore d'évaluation

- Sandeepalani Course of 16 WeeksDocument3 pagesSandeepalani Course of 16 WeeksNitesh JadhavPas encore d'évaluation

- Vlsi ProjectsDocument2 pagesVlsi ProjectsnewvlsiprojectsPas encore d'évaluation

- Asic and Fpga DesignDocument24 pagesAsic and Fpga DesignGiri ReddyPas encore d'évaluation

- Program in VLSIDocument3 pagesProgram in VLSIVamshi KrishnaPas encore d'évaluation

- Handout STD Cell DesignDocument25 pagesHandout STD Cell DesignHacraloPas encore d'évaluation

- Cdac Vlsi Course StructureDocument2 pagesCdac Vlsi Course Structuresureshr_42Pas encore d'évaluation

- Vlsi/Fpga Design and Test CAD Tool Flow in Mentor GraphicsDocument20 pagesVlsi/Fpga Design and Test CAD Tool Flow in Mentor GraphicsaltisinPas encore d'évaluation

- A SicDocument3 pagesA SicSumit Singh ThakurPas encore d'évaluation

- Dependent Sources, Passive ElementsDocument3 pagesDependent Sources, Passive ElementsSridhar ChandrasekarPas encore d'évaluation

- Introduction To FPGADocument29 pagesIntroduction To FPGAMohan Babu APas encore d'évaluation

- slide thiết kế hệ thốngDocument391 pagesslide thiết kế hệ thốngNguyễn Tấn ĐịnhPas encore d'évaluation

- Chapter 01 Introduction-1Document96 pagesChapter 01 Introduction-1Thanh Diện NguyễnPas encore d'évaluation

- How Does FPGA Work: OutlineDocument17 pagesHow Does FPGA Work: OutlinehariharankalyanPas encore d'évaluation

- Vector 22 MayDocument5 pagesVector 22 MayVenky YadavPas encore d'évaluation

- Vlsi Ieee Project Topics: View PapersDocument6 pagesVlsi Ieee Project Topics: View PapersEr Shivam GuptaPas encore d'évaluation

- Vlsi Design FlowDocument7 pagesVlsi Design FlowAster RevPas encore d'évaluation

- Books-Download - HTML: Programming FundamentalDocument4 pagesBooks-Download - HTML: Programming Fundamentalyupsup9Pas encore d'évaluation

- ASIC Design FlowDocument16 pagesASIC Design FlowPeter ChenPas encore d'évaluation

- Chapter - 01 Course IntroductionDocument94 pagesChapter - 01 Course IntroductionNguyen Yen NhiPas encore d'évaluation

- Vlsi ManualDocument110 pagesVlsi ManualSam Joel.DPas encore d'évaluation

- Padmaja ResumeDocument4 pagesPadmaja Resumepadmajakavuri2000Pas encore d'évaluation

- Lecture 3 - Design FlowDocument18 pagesLecture 3 - Design Flowkumarkankipati19100% (1)

- ECE448 Lecture15 ASIC DesignDocument17 pagesECE448 Lecture15 ASIC DesignSunil PandeyPas encore d'évaluation

- VLSI ListDocument3 pagesVLSI List22kishor1111Pas encore d'évaluation

- Semi Custom Vlsi DesignDocument25 pagesSemi Custom Vlsi DesignPraveen KumarPas encore d'évaluation

- QP M Tech 4th Sem 21 VASDDocument2 pagesQP M Tech 4th Sem 21 VASDAshadur RahamanPas encore d'évaluation

- IEEE Titles and Research & Development Projects For Students ofDocument11 pagesIEEE Titles and Research & Development Projects For Students ofvijaykannamallaPas encore d'évaluation

- Chapter - 01 Course IntroductionDocument94 pagesChapter - 01 Course IntroductionNguyễn Thị Diễm ThúyPas encore d'évaluation

- Flexible Tools For Interactive Model-Based Control Design and SimulationDocument55 pagesFlexible Tools For Interactive Model-Based Control Design and SimulationArun KumarPas encore d'évaluation

- Eee646 Fpga-based-system-Design Ela 2.00 Ac29Document2 pagesEee646 Fpga-based-system-Design Ela 2.00 Ac29Ranjith M KumarPas encore d'évaluation

- FPGA-Arch CPLD Design April2012Document112 pagesFPGA-Arch CPLD Design April2012Moazzam HussainPas encore d'évaluation

- Types of SimulationDocument3 pagesTypes of Simulationhumtum_shri573667% (3)

- VLSI Lab ManualDocument83 pagesVLSI Lab ManualSri SandhiyaPas encore d'évaluation

- Analog and Digital VLSI Design: Lecture 2: VLSI Design Flow & Challenges in VLSI DesignDocument8 pagesAnalog and Digital VLSI Design: Lecture 2: VLSI Design Flow & Challenges in VLSI DesignAmandeep GuptaPas encore d'évaluation

- Vlsi 161217161739 PDFDocument29 pagesVlsi 161217161739 PDFkondalarao79Pas encore d'évaluation

- 2 ND Sem Course WorkDocument2 pages2 ND Sem Course WorkMmkpss Sriram Sista MmkpssPas encore d'évaluation

- Nelson s09Document47 pagesNelson s09YUE shenPas encore d'évaluation

- System Design and Modeling With SimulinkDocument0 pageSystem Design and Modeling With SimulinkSharmila ChowdhuriPas encore d'évaluation

- Nikhil B. ShahDocument2 pagesNikhil B. ShahnikhilshahbPas encore d'évaluation

- Ravi Sharma ResDocument2 pagesRavi Sharma ResSunny ModiPas encore d'évaluation

- Lecture 3 - Design FlowDocument14 pagesLecture 3 - Design FlowramukajarrPas encore d'évaluation

- VLSI Design - EDA TOOLS PDFDocument83 pagesVLSI Design - EDA TOOLS PDFprathap_somaPas encore d'évaluation

- Fpga Introduction 20190626aDocument26 pagesFpga Introduction 20190626atulasiPas encore d'évaluation

- Definition:: Field-Programmable Gate ArrayDocument6 pagesDefinition:: Field-Programmable Gate ArrayyaduyadavendraPas encore d'évaluation

- ASIC Layout - 2 Standard Cell FlowDocument25 pagesASIC Layout - 2 Standard Cell Flowdiva9jobsPas encore d'évaluation

- 6 CosynthesisDocument50 pages6 CosynthesisRaghu RamPas encore d'évaluation

- A Framework For The Design of High Speed Fir Filters On FpgasDocument4 pagesA Framework For The Design of High Speed Fir Filters On Fpgasamit1411narkhedePas encore d'évaluation

- Technical Content Reference - ResumeDocument8 pagesTechnical Content Reference - ResumeKiransai ReddyPas encore d'évaluation

- ASIC Layout - 2 Standard Cell Flow PDFDocument28 pagesASIC Layout - 2 Standard Cell Flow PDFEsakkiPonniahPas encore d'évaluation

- FPGA (Xilinx & Altera)Document1 pageFPGA (Xilinx & Altera)Bala SgPas encore d'évaluation

- Asic Design Flow: Submitted To:-Submitted By: - Manju K. Chattopadhyay Purvi Medawala 14MTES11Document18 pagesAsic Design Flow: Submitted To:-Submitted By: - Manju K. Chattopadhyay Purvi Medawala 14MTES11CLARITY UDTPas encore d'évaluation

- Vlsi Ic Design FlowDocument20 pagesVlsi Ic Design FlowrajanarendrasaiPas encore d'évaluation

- Input Files RequiredDocument3 pagesInput Files RequiredsrajecePas encore d'évaluation

- 8.programmable Asic Design SoftwareDocument21 pages8.programmable Asic Design Softwaresalinsweety50% (2)

- Ap7202-Asic and FpgaDocument10 pagesAp7202-Asic and FpgaJayapalPas encore d'évaluation

- Sem1 EmbbededDocument9 pagesSem1 Embbededvishwanath cPas encore d'évaluation

- Embedded Software Design and Programming of Multiprocessor System-on-Chip: Simulink and System C Case StudiesD'EverandEmbedded Software Design and Programming of Multiprocessor System-on-Chip: Simulink and System C Case StudiesPas encore d'évaluation

- Python Quick ReferenceDocument1 pagePython Quick Referencemachnik14866240% (1)

- Finxter WorldsMostDensePythonCheatSheetDocument1 pageFinxter WorldsMostDensePythonCheatSheetmachnik1486624Pas encore d'évaluation

- All Interfaces in FPMDocument1 pageAll Interfaces in FPMmachnik1486624Pas encore d'évaluation

- Sardar Vallabhbhai Patel SpeechDocument1 pageSardar Vallabhbhai Patel Speechmachnik14866240% (1)

- Sri Dakshinamurthy Stotram - Hindupedia, The Hindu EncyclopediaDocument7 pagesSri Dakshinamurthy Stotram - Hindupedia, The Hindu Encyclopediamachnik1486624Pas encore d'évaluation

- Cat1 Segmentals PDFDocument1 pageCat1 Segmentals PDFmachnik1486624Pas encore d'évaluation

- NO Script Meaning & Usage WordDocument2 pagesNO Script Meaning & Usage Wordmachnik1486624Pas encore d'évaluation

- RTO Work For KarnatakaDocument5 pagesRTO Work For Karnatakamachnik1486624Pas encore d'évaluation

- ABAP Object Oriented Approach For Reports - RedesignDocument4 pagesABAP Object Oriented Approach For Reports - Redesignmachnik1486624Pas encore d'évaluation

- FNA Practice Materials Cat 1Document6 pagesFNA Practice Materials Cat 1machnik1486624Pas encore d'évaluation

- Tamil LearningDocument13 pagesTamil Learningmachnik1486624Pas encore d'évaluation

- Procedure For Displaying The Flight ModelDocument1 pageProcedure For Displaying The Flight Modelmachnik1486624Pas encore d'évaluation

- From Bangalore To Ooty! - Team-BHPDocument17 pagesFrom Bangalore To Ooty! - Team-BHPmachnik1486624Pas encore d'évaluation

- 1.FPGA Design Flow Processes PropertiesDocument5 pages1.FPGA Design Flow Processes Propertiesmachnik1486624Pas encore d'évaluation

- DSP Lab Sample Viva QuestionsDocument5 pagesDSP Lab Sample Viva Questionsmachnik1486624Pas encore d'évaluation

- Modelling Latches and FlipflopsDocument9 pagesModelling Latches and Flipflopsmachnik1486624Pas encore d'évaluation