Académique Documents

Professionnel Documents

Culture Documents

Subject: Analog and Mixed Signal Ic Design: Resistance

Transféré par

chandravinita0 évaluation0% ont trouvé ce document utile (0 vote)

16 vues2 pagesI test paper of Analog & Mixed signal IC Design

Titre original

AMS 2015I

Copyright

© © All Rights Reserved

Formats disponibles

DOCX, PDF, TXT ou lisez en ligne sur Scribd

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentI test paper of Analog & Mixed signal IC Design

Droits d'auteur :

© All Rights Reserved

Formats disponibles

Téléchargez comme DOCX, PDF, TXT ou lisez en ligne sur Scribd

0 évaluation0% ont trouvé ce document utile (0 vote)

16 vues2 pagesSubject: Analog and Mixed Signal Ic Design: Resistance

Transféré par

chandravinitaI test paper of Analog & Mixed signal IC Design

Droits d'auteur :

© All Rights Reserved

Formats disponibles

Téléchargez comme DOCX, PDF, TXT ou lisez en ligne sur Scribd

Vous êtes sur la page 1sur 2

BANASTHALI VIDYAPITH

I PERIODICAL TEST-2015

CLASS: M.TECH II SEM. VLSI DESIGN

SUBJECT: ANALOG AND MIXED SIGNAL IC DESIGN

NUMBER OF STUDENTS = 66

NOTE: Attempt all questions. Assume missing data, if any suitably. Write specific answers,

unnecessary long answer can deduct your marks.

MAX. MARKS: 10

TIME: 1:30 Hrs.

Q.1. Attempt all parts (2X2).

(a) In the case of mismatch between the MOSFETs used to design the simple current mirror, show that

the relationship between input and output current is given by the expression:

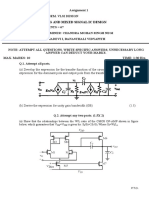

(b) Describe the small signal model for the circuit shown in Fig. 1 below. Also calculate output

resistance.

ISS

Fig. 1

Fig. 2

Fig. 3

Q.2. Attempt any two parts. (1.5X 2)

(a) Discuss small signal model of Wilson current mirror and obtain the expression for its output

resistance.

(b) Find the small signal output resistance and differential voltage gain, v o/vid, of the circuit in Fig. 2

(shown above). Assume all transistors have a W/L of 10m/1m, KN =110A/V2, KP =50A/V2, N

=0.04V-1,P =0.05V-1, VT0=0.7 V, and ISS=10A.

(c) Calculate the output resistance and the minimum output voltage, while maintaining all devices in

saturation, for the circuit shown in Fig.3 above. Assume that IOUT is actually 10A. You can use the

value of various model parameters given in the question 2 (b) above. Dimensions are in micrometer.

********************

Vous aimerez peut-être aussi

- MOS Integrated Circuit DesignD'EverandMOS Integrated Circuit DesignE. WolfendalePas encore d'évaluation

- Subject: Analog and Mixed Signal Ic DesignDocument3 pagesSubject: Analog and Mixed Signal Ic DesignchandravinitaPas encore d'évaluation

- Subject: Analog and Mixed Signal Ic DesignDocument2 pagesSubject: Analog and Mixed Signal Ic DesignchandravinitaPas encore d'évaluation

- MELZG632 Analog IC Design MidSem Make-Up 1573297948961Document3 pagesMELZG632 Analog IC Design MidSem Make-Up 1573297948961VEMURI RAVI TEJAPas encore d'évaluation

- Integrated Circuits Nec 501 PDFDocument2 pagesIntegrated Circuits Nec 501 PDFSaurabhPas encore d'évaluation

- Sura Group of Institutions, Lucknow: Q-2.2 Determine The Following For The Given NetworkDocument2 pagesSura Group of Institutions, Lucknow: Q-2.2 Determine The Following For The Given NetworkSaurabh SinghPas encore d'évaluation

- Vlsi Design: Time: 3 Hours Total Marks: 100Document4 pagesVlsi Design: Time: 3 Hours Total Marks: 100Shivani VarshneyPas encore d'évaluation

- Final Fall 2020Document2 pagesFinal Fall 2020Zeyad AymanPas encore d'évaluation

- Final Fall 2020Document2 pagesFinal Fall 2020Zeyad AymanPas encore d'évaluation

- Answer KeyDocument5 pagesAnswer Keyjaferkhan pPas encore d'évaluation

- SECTION - A (20 Marks Each) : Dayananda Sagar College of Engineering Department of Eie I Internal TestDocument1 pageSECTION - A (20 Marks Each) : Dayananda Sagar College of Engineering Department of Eie I Internal TestKrushnasamy SuramaniyanPas encore d'évaluation

- Analog - RF VLSI Design (ECE 503) (Makeup) PDFDocument2 pagesAnalog - RF VLSI Design (ECE 503) (Makeup) PDFRahul PinnamaneniPas encore d'évaluation

- R09-Cmos Analog and Mixed Signal DesignDocument1 pageR09-Cmos Analog and Mixed Signal DesignbalashyamuPas encore d'évaluation

- Lab Report 1: Diode I-V CharacteristicsDocument3 pagesLab Report 1: Diode I-V CharacteristicsIslam Fathy FaragPas encore d'évaluation

- Set - A Beee QPDocument2 pagesSet - A Beee QPThiaga RajanPas encore d'évaluation

- Answer All Questions: 4 Semester - B.E. / B.Tech Second Internal Test - March 2013Document1 pageAnswer All Questions: 4 Semester - B.E. / B.Tech Second Internal Test - March 2013BIBIN CHIDAMBARANATHANPas encore d'évaluation

- IIUM Electronics ECE 1312/ECE 1231 Final Exam Sem 1 (2012 - 2013)Document8 pagesIIUM Electronics ECE 1312/ECE 1231 Final Exam Sem 1 (2012 - 2013)Ridhwan Asri100% (1)

- Assignment No. 6Document3 pagesAssignment No. 6aditya nagrajanPas encore d'évaluation

- Main Paper EC-306Document2 pagesMain Paper EC-306Sachin PalPas encore d'évaluation

- Main Paper EC-306Document2 pagesMain Paper EC-306Sachin PalPas encore d'évaluation

- Main Paper EC-306Document2 pagesMain Paper EC-306Sachin PalPas encore d'évaluation

- Main Paper EC-306Document2 pagesMain Paper EC-306Sachin PalPas encore d'évaluation

- Ryerson University EE 8502 Analog CMOS Integrated Circuits Final ExaminationDocument7 pagesRyerson University EE 8502 Analog CMOS Integrated Circuits Final ExaminationooohlalalaPas encore d'évaluation

- Q Paper 09ec61 May June 2012Document2 pagesQ Paper 09ec61 May June 2012Bhaskar MishraPas encore d'évaluation

- Notes: (No. of Printed Pages-4) ES201 Enrol. No. (ET) End Semester Examination Nov.-Dec., 2016Document6 pagesNotes: (No. of Printed Pages-4) ES201 Enrol. No. (ET) End Semester Examination Nov.-Dec., 2016Ryash ShahPas encore d'évaluation

- NR-221103 - Digital Circuits Design and ApplictionDocument5 pagesNR-221103 - Digital Circuits Design and ApplictionSrinivasa Rao G100% (1)

- R09-Cmos Analog and Mixed Signal DesignDocument2 pagesR09-Cmos Analog and Mixed Signal DesignbalashyamuPas encore d'évaluation

- Sri Vellappally Natesan College of Engineering: Series Test-Ii March 2016 08.825: Microwave Device and Circuits (T)Document1 pageSri Vellappally Natesan College of Engineering: Series Test-Ii March 2016 08.825: Microwave Device and Circuits (T)anupvasuPas encore d'évaluation

- EXAM Phys Elec II 2016 SolutionsDocument10 pagesEXAM Phys Elec II 2016 SolutionsThulasizwe PhethaPas encore d'évaluation

- E3-238: Analog VLSI Circuits Lab 2: InstructionsDocument4 pagesE3-238: Analog VLSI Circuits Lab 2: InstructionsR SHARMAPas encore d'évaluation

- Electronic Measurement - Instrumentation Rec403Document2 pagesElectronic Measurement - Instrumentation Rec403Brahmanand SinghPas encore d'évaluation

- ENEL2EEH1 - Electrical & Electronic EngineeringDocument7 pagesENEL2EEH1 - Electrical & Electronic EngineeringqanaqPas encore d'évaluation

- B1 Ece2002 50030 50290 50369Document4 pagesB1 Ece2002 50030 50290 50369NanduPas encore d'évaluation

- (Common For Both) Low Power Vlsi DesignDocument2 pages(Common For Both) Low Power Vlsi DesignSaranya RamaswamyPas encore d'évaluation

- Exp 3Document5 pagesExp 3MariaPas encore d'évaluation

- Btech Oe 3 Sem Analog Electronics Koe037 2022Document3 pagesBtech Oe 3 Sem Analog Electronics Koe037 2022Vishal Kumar SharmaPas encore d'évaluation

- Second Series Oct 27Document1 pageSecond Series Oct 27sambhudharmadevanPas encore d'évaluation

- Ee141 hw6 sp10Document3 pagesEe141 hw6 sp10Brenda PalmerPas encore d'évaluation

- Basics of Electrical and ElectronicsDocument11 pagesBasics of Electrical and ElectronicsannpotterPas encore d'évaluation

- Basic Electronics Rec201 1Document4 pagesBasic Electronics Rec201 1ranveeryadav3710Pas encore d'évaluation

- AnnaunivqpDocument2 pagesAnnaunivqpShankarPas encore d'évaluation

- EE115C - Digital Electronic Circuits Homework #6: Due Monday, Feb 25, 4pmDocument3 pagesEE115C - Digital Electronic Circuits Homework #6: Due Monday, Feb 25, 4pmShobhit GargPas encore d'évaluation

- B. Tech: Roll NoDocument5 pagesB. Tech: Roll NoRavindra KumarPas encore d'évaluation

- BMS College of Engineering, Bangalore-560019: December 2015 Semester End Main ExaminationsDocument3 pagesBMS College of Engineering, Bangalore-560019: December 2015 Semester End Main ExaminationsrameshPas encore d'évaluation

- 15A04301 Electronic Devices and CircuitsDocument1 page15A04301 Electronic Devices and CircuitsSivaprasad ReddyPas encore d'évaluation

- Eee312 Eee282 Lab7 Spring2015Document6 pagesEee312 Eee282 Lab7 Spring2015vognarPas encore d'évaluation

- 18EC42 First IA Test Q-PaperDocument2 pages18EC42 First IA Test Q-PapersharanbasappaPas encore d'évaluation

- Model Question Paper (CBCS) With Effect From 2015-16 15ELN15/25Document2 pagesModel Question Paper (CBCS) With Effect From 2015-16 15ELN15/25Suresh AkkolePas encore d'évaluation

- Analog & Mixed Mode VLSI Design EC604Document2 pagesAnalog & Mixed Mode VLSI Design EC604Sean AguilarPas encore d'évaluation

- Physics Paper 1-Spm 2010Document9 pagesPhysics Paper 1-Spm 2010Phy LabPas encore d'évaluation

- Electrical, Digital and Industrial Circuits: IT IL IcDocument4 pagesElectrical, Digital and Industrial Circuits: IT IL IcNGOUNEPas encore d'évaluation

- 06CS32 May - June 2010Document2 pages06CS32 May - June 2010Rafael BarriosPas encore d'évaluation

- Anallysis and Design of Analog Integrated Circuits QuestionsDocument5 pagesAnallysis and Design of Analog Integrated Circuits QuestionsshankarPas encore d'évaluation

- TED (15) - 3021 Reg. No: Electrical & Electronics EngineeringDocument3 pagesTED (15) - 3021 Reg. No: Electrical & Electronics EngineeringMuhd Shabeeb APas encore d'évaluation

- TED (21) 2031 QPDocument3 pagesTED (21) 2031 QPSreekanth KuPas encore d'évaluation

- Self Biased Cascode CM PDFDocument7 pagesSelf Biased Cascode CM PDFDhaval ShuklaPas encore d'évaluation

- Elec1041y 1 2007 2 PDFDocument7 pagesElec1041y 1 2007 2 PDFchetsPas encore d'évaluation

- Fundamentals of Electronics 1: Electronic Components and Elementary FunctionsD'EverandFundamentals of Electronics 1: Electronic Components and Elementary FunctionsPas encore d'évaluation

- Electromagnetic Compatibility (EMC) Design and Test Case AnalysisD'EverandElectromagnetic Compatibility (EMC) Design and Test Case AnalysisPas encore d'évaluation

- CLASS: B.TECH. VI SEM. (Electronics & Instrumentation)Document2 pagesCLASS: B.TECH. VI SEM. (Electronics & Instrumentation)chandravinitaPas encore d'évaluation

- CLASS: B.TECH. V SEM. (Electronics & Communication)Document3 pagesCLASS: B.TECH. V SEM. (Electronics & Communication)chandravinitaPas encore d'évaluation

- Guidelines For Preparation of Project Report: (Prescribed Format and Specification) 1. GeneralDocument11 pagesGuidelines For Preparation of Project Report: (Prescribed Format and Specification) 1. GeneralchandravinitaPas encore d'évaluation

- Experiment List: M.Tech. II Sem. (VLSI) Analog & Mixed Signal IC Design LabDocument1 pageExperiment List: M.Tech. II Sem. (VLSI) Analog & Mixed Signal IC Design LabchandravinitaPas encore d'évaluation

- Manual For Preparation of Project ReportDocument8 pagesManual For Preparation of Project ReportchandravinitaPas encore d'évaluation

- AMS Design Lab ProblemsDocument1 pageAMS Design Lab ProblemschandravinitaPas encore d'évaluation

- INEC PaperDocument1 pageINEC PaperchandravinitaPas encore d'évaluation

- Department of Electronics (AIM & ACT) Banasthali University Notice CompositeDocument2 pagesDepartment of Electronics (AIM & ACT) Banasthali University Notice CompositechandravinitaPas encore d'évaluation

- Nano ElectronicsDocument1 pageNano Electronicschandravinita100% (1)

- Syllabus For PHDFDocument2 pagesSyllabus For PHDFchandravinitaPas encore d'évaluation

- Philip Larkin Is One of BritainDocument7 pagesPhilip Larkin Is One of Britainchandravinita100% (1)

- Analog PracticalDocument1 pageAnalog PracticalchandravinitaPas encore d'évaluation

- Course Description ECE 5364 - Electronic Circuit DesignDocument3 pagesCourse Description ECE 5364 - Electronic Circuit DesignchandravinitaPas encore d'évaluation

- Quantum Computing 1Document6 pagesQuantum Computing 1chandravinitaPas encore d'évaluation

- BTechEEE Syllabus - 08.09.09Document31 pagesBTechEEE Syllabus - 08.09.09Ankita VijayvergiyaPas encore d'évaluation