Académique Documents

Professionnel Documents

Culture Documents

Flip Flops

Transféré par

hariharankalyanTitre original

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

Flip Flops

Transféré par

hariharankalyanDroits d'auteur :

Formats disponibles

ECE 733 Class Notes

Latches and Flip-Flops

Dr. Paul D. Franzon

Outline

Design Goals

Basic Latches and Flip-flops

Optimizing Timing

Single Sided Designs

Differential Designs

Some comparisons

References

Dally & Poulton, Chapters 4, 12.1

Kang & Leblecici, Chs 8-9

Bernstein, Ch. 5

2012, Dr. Paul D. Franzon, www.ece.ncsu.edu/erl/faculty/paulf.html

ECE 733 Class Notes

Objectives and Motivation

Objectives:

Understand design goals and tradeoffs in flip-flops and how they are

measured

Be able to describe operation of a wide range of flips and recognize how the

roles of individual transistors determine operation

Motivation

Most complex high-speed digital circuit

Constrains performance of logic and I/O

2012, Dr. Paul D. Franzon, www.ece.ncsu.edu/erl/faculty/paulf.html

ECE 733 Class Notes

Revision

Ck

Ck

D-Latch:

level-sensitive

Tracks data while clock high

Stores data while clock low

D-Flip-flop

edge-sensitive

Stores data on clock edge

tSetUp

thold

tclock-Q

taperture

Ck

D

tSetUp

thold

tclock-Q

taperture

tD-Q

2012, Dr. Paul D. Franzon, www.ece.ncsu.edu/erl/faculty/paulf.html

ECE 733 Class Notes

Edge-Triggered Flip-Flops

Created from latches:

Two styles:

2012, Dr. Paul D. Franzon, www.ece.ncsu.edu/erl/faculty/paulf.html

ECE 733 Class Notes

Goals of Flip-Flop Design

Timing and Clock Speed:

tclock tck Q max tlog ic max t setup t skew max

Logic

clock

skew

Goal:

Minimize tDQ=tCk-Q + tsetup

2012, Dr. Paul D. Franzon, www.ece.ncsu.edu/erl/faculty/paulf.html

ECE 733 Class Notes

Goals

Timing Closure:

Ability to withstand max-min process and

temperature variations depends on how

much of the clock-period is taken up by

setup and hold times

Goal:

Register

Q1

D1

Comb

Logic

Constrains maximum taperture = tsetup+thold

clock

Register

D2

tLogic-delay

+/-tskew

Q2

clock

tset-up

thold tskew

tskew

clock

D2

tck-Q-max + tlogic-max tck-Q-min-tlogic-min

2012, Dr. Paul D. Franzon, www.ece.ncsu.edu/erl/faculty/paulf.html

ECE 733 Class Notes

Goals of flip-flop design

Timing Related:

To get fastest clock period:

Minimize tD-Q

=t_su + t_ck-Q

soft clock edge

NOT (or reduce) propagate clock skew to Q

Removes or reduces impact of tskew on clock period

clock

D

skew

clock

skew

Q

Note : Latches have this property for signals that arrive after clock

rising edge!

Incorporate logic into flip-flop

And remove from before/after flip-flop

2012, Dr. Paul D. Franzon, www.ece.ncsu.edu/erl/faculty/paulf.html

ECE 733 Class Notes

Goals of Flip-Flop Design

Timing Related:

Be able to drive good loads

Typical fan-out: 2-8 FO4 inputs (50 200 fF in 0.18 m)

Minimum susceptibility to clock slope (edge rate)

Most FFs have an max rise/fall time specification

2012, Dr. Paul D. Franzon, www.ece.ncsu.edu/erl/faculty/paulf.html

ECE 733 Class Notes

Goals of Flip-Flop Design

Power Related

Minimize internal power

Minimize clock load

Note : Speed-power tradeoff

Can design to minimize Power.Delay or Energy.Delay Product

Measured in fJ gives minimum energy per transition (and energy-delay

product for constant fclock)

Bit Error Rate Related

Minimize suceptibility to:

Noise on clocks or signals (e.g. due to crosstalk)

Clock edge rate variations

Charge-sharing failures

Charge leakage failures, including alpha particle strikes

Power & ground noise

Other

Facilitate test and debug (Be static & scannable)

2012, Dr. Paul D. Franzon, www.ece.ncsu.edu/erl/faculty/paulf.html

ECE 733 Class Notes

Flip-Flop Basics

Generic Flip-Flop:

Sampler

Static:

storage

Output

Dynamic:

etc.

Sampling Stage:

Must ensure input is sampled for both high and low D

Fastest if no DC path from Vdd to Gnd during sampling

Output Stage:

Drives load without disrupting stored state

2012, Dr. Paul D. Franzon, www.ece.ncsu.edu/erl/faculty/paulf.html

10

ECE 733 Class Notes

Basic Bistable Static Storage Element

V1

Cross-coupled inverter pair

V2

V1

V1

V3

V3

V1

V2

Stable operating point

Inverter loaded with

itself:

Regenerative feedback

Unstable (high gain)

Stable operating point

V2

V1

Qualitative View:

Energy

V2

V2

2012, Dr. Paul D. Franzon, www.ece.ncsu.edu/erl/faculty/paulf.html

11

ECE 733 Class Notes

Noise Margin

Add noise at one input:

V2

V1

Assume nominal V2 =1

V1

Vn

V1

Size of boxes

determine NMs

V1

Small Vn

V2

High gain no longer stable

V2

Unity gain

Large Vn

2012, Dr. Paul D. Franzon, www.ece.ncsu.edu/erl/faculty/paulf.html

V2

12

ECE 733 Class Notes

Can replace

INV with logic

Basic Latches

To store a logic level (change state):

Must overcome the potential hill

between two stable states

Some Methods:

Use Transmission gates to break feedback

path

D-latch

Break supply current path (RS latch)

Reset/Set

D latch:

Clk

D

clk

Q

S

2012, Dr. Paul D. Franzon, www.ece.ncsu.edu/erl/faculty/paulf.html

NOR RS latch

13

ECE 733 Class Notes

Latch Basics

Other Methods To Change State:

Directly over-powering regenerative

feedback in storage cell

Must generate a negative noise margin

by the write (clk=high)

In this case:

Sizes p1, p2 = 2 m / 0.35 m

Sizes n3, n4 = 3 m / 0.35 m

Sizes n1, n2, n5, n6 = 5 m / 0.35 m

provides sufficient write margin

p2

p1

D

n1

n3

n4

n5

D

clk

clk

n2

n6

V1

RH inverter (D=0)

LH inverter (D=1)

Negative Voltage Margin

Write

V2

2012, Dr. Paul D. Franzon, www.ece.ncsu.edu/erl/faculty/paulf.html

14

ECE 733 Class Notes

Revision: Flip-flop Design Goals

Timing:

t clock t ck Q max t log ic max t setup max t skew max

Logic

clock

skew

Goals :

Minimize tDQ = tclock-Q + tSU

Constrain upper limt for taperture = tsetup + thold

2012, Dr. Paul D. Franzon, www.ece.ncsu.edu/erl/faculty/paulf.html

15

ECE 733 Class Notes

Timing

Tradeoff between tclock-Q and tsu / thold:

tclock-Q

thold

tSU

Why?

D

clk

clock

D

Q

Q

X

Smaller tSU VX smaller

-Amplification Voltage growth exponential with time

VQe-t/

Amplifier delay increases exponentially with decreasing

tSU

(I.E. with smaller Vx)

Q metastable during amplification

Q

2012, Dr. Paul D. Franzon, www.ece.ncsu.edu/erl/faculty/paulf.html

16

ECE 733 Class Notes

Doing this in Project

Illustrate for D: 0 1 transition:

Conservative tsu:

Aggressive tsu:

Failure:

Clock

D

Q

tsu tck-Q

One point on

curve on previous page

tsu tck-Q

Another point

<tsu

Failure!

NOT a valid tsu

Reminder: Goal most likely to minimize tDQ, not tsu

2012, Dr. Paul D. Franzon, www.ece.ncsu.edu/erl/faculty/paulf.html

17

ECE 733 Class Notes

Project Characterization

T_hold

Failure:

Good:

Ck

Ck

Q

<thold

Failure!

NOT a valid thold

thold

Good! (NO change in Q due to D)

thold

2012, Dr. Paul D. Franzon, www.ece.ncsu.edu/erl/faculty/paulf.html

18

ECE 733 Class Notes

Timing

Objective : Minimize tD-Q = tSU + tclock-Q

Often results in negative setup time

tSU

clock

D

Q

Forbidden

400

tD-Q

tclock-Q

tD-Q

(ps)

350

300

250

-60 -40 -20 0 20 40 60 80

e.g. strong-ARM flip-flop

2012, Dr. Paul D. Franzon, www.ece.ncsu.edu/erl/faculty/paulf.html

tSU(ps)

19

ECE 733 Class Notes

Other Timing Parameters

tSU

clock

D

400

350

Forbidden

Hold

Hold period:

300

Hold period

(no transitions

allowed)

250

-80 -60 -40 -20 0 20 40 60 80 tSU(ps)

2012, Dr. Paul D. Franzon, www.ece.ncsu.edu/erl/faculty/paulf.html

20

ECE 733 Class Notes

Other Timing Parameters

Effect of clock edge rate

Flip-flop timing can be sensitive to clock edge rate (slope)

Can cause race-through in Master-Slave

e.g. pass-gate FF:

D

clk

Vinv

Vt

clk

Vt

T2 open

T1 open

Q

Q

T1

Clk

T2

Clk

Problem if T2 open longer than Tinv-delay past this time

2012, Dr. Paul D. Franzon, www.ece.ncsu.edu/erl/faculty/paulf.html

21

ECE 733 Class Notes

Latches Flip-Flops Characterized

Single-Sided

C2MOS

TSPC

Transmission Gate

Double-Sided (complementary or differential)

DCVS

Single Transistor Clock

Hybrid Latch Flip-flop

Semi Dynamic Flip-flop

Sense Amp Flip Flop

K6 Flip Flop

Comparisons

2012, Dr. Paul D. Franzon, www.ece.ncsu.edu/erl/faculty/paulf.html

22

ECE 733 Class Notes

Common Questions

How is the signal sampled on the clock 0 1 transition?

What determines:

tsetup ?

thold ?

tck-Q ?

How is the data stored?

What prevents false transitions from occuring when

D changes after thold ?

When clock goes low ?

2012, Dr. Paul D. Franzon, www.ece.ncsu.edu/erl/faculty/paulf.html

23

ECE 733 Class Notes

C2MOS Flip-Flop

Edge triggered Master-Slave device:

Samples while clk Low

Tri-state inverter

Samples while clk High

Clock Buffer

Regenerate when clock high

2012, Dr. Paul D. Franzon, www.ece.ncsu.edu/erl/faculty/paulf.html

24

ECE 733 Class Notes

C2MOS Operation

Track (ck = 0)

=on

Tracking input

Recycling previous value

Track (ck 1)

Holding sampled value

Sampling input

2012, Dr. Paul D. Franzon, www.ece.ncsu.edu/erl/faculty/paulf.html

25

ECE 733 Class Notes

Timing

What determines t_setup and t_hold?

clk

ckb

ck

tsu

D can not change during this interval

t_hold

What determines t_clock-Q?

Clock buffer delay + delay through second tri-state buffer

2012, Dr. Paul D. Franzon, www.ece.ncsu.edu/erl/faculty/paulf.html

26

ECE 733 Class Notes

True Single Phase Clocked (TSPC) Latches & Flip-Flops

Based on the following dynamic latches:

Transparent while clock high:

clk

D

clk

clk

D

clk

SN

When clock low:

PP

SP

PP

Note : Only clock is needed, not clock or a second clock phase

True single phase lowest skew in distribution

Make latches and flip-flops by mixing stages.

(Source : Yuang and Svenson)

2012, Dr. Paul D. Franzon, www.ece.ncsu.edu/erl/faculty/paulf.html

27

ECE 733 Class Notes

TSPC Flip Flops

Example:

Positive edge triggered static-input flip flop

SP + SP + SN + SN

D

clk

b

a

Observation:

SP stage simply inverts a while clk lo

Not needed if Q OK..

Note, nodes a, b, Q float for part of clock

period

Watch for inadvertant charge sharing

Note can put logic in PU and PD chains

clk

2012, Dr. Paul D. Franzon, www.ece.ncsu.edu/erl/faculty/paulf.html

28

ECE 733 Class Notes

Operation

D=0, clk=0

ck 1

1

clk

x1

clk

Note: a/b floats high or low (x0, x1)

D1, clk=1 (Q should not change)

x0

clk

2012, Dr. Paul D. Franzon, www.ece.ncsu.edu/erl/faculty/paulf.html

29

ECE 733 Class Notes

Operation

D=1, clk=0

ck 1

1

x1

clk

clk

Note: a/b floats high or low (x0, x1)

D0, clk=1 (Q should not change)

D

x1

x0

clk

2012, Dr. Paul D. Franzon, www.ece.ncsu.edu/erl/faculty/paulf.html

30

ECE 733 Class Notes

TSPC Issues

Timing:

tclock-Q is very quick

Must have logic between stages to prevent hold violation

Can be sensitive to clock slope (next page)

Has floating nodes during evaluate

Very high clock load

2012, Dr. Paul D. Franzon, www.ece.ncsu.edu/erl/faculty/paulf.html

31

ECE 733 Class Notes

Clock Slope

Example : Sensitivity of TSPC flip-flop:

p2

D

a

p1

n1

clk

Possible failure:

D remains high

a low when clock low

clock

b

Q

p1 off

before p2 on

Possible Fixes :

p1 & p2

On

Reduce Wn1; enforce clock slope rules

2012, Dr. Paul D. Franzon, www.ece.ncsu.edu/erl/faculty/paulf.html

32

ECE 733 Class Notes

Transmission Gate Master-Slave

PowerPC 603

Clock Load

High

Power

Low

low power feedback

Positive setup

TG delay determines t_su

INV(s) + TG gate determines t_ck-Q

(first INV only matters if tsu very small)

Q buffer makes timing less sensitive to load variations

2012, Dr. Paul D. Franzon, www.ece.ncsu.edu/erl/faculty/paulf.html

33

ECE 733 Class Notes

Differential Latches and Flip Flops

i.e. Requires both D and D

Conventional Latches and Master-Slave Designs

DCVS

True Single Phase Clocked Latch

DSTC and SSTC

Pulse-triggered Latches:

HLFF

DSFF

SAFF

ETL

2012, Dr. Paul D. Franzon, www.ece.ncsu.edu/erl/faculty/paulf.html

34

ECE 733 Class Notes

Differential Cascode Voltage Switch

Q

Variants:

Static RAM style Latch

p2

p1

Operation explained earlier

Transparent when clk hi

n3

n1

n5

n4

clk

n2

Simple DCVS:

Latch or flip-flop?

Dynamic or static?

Latch

p1

Dynamic

Susceptibility to charge sharing can be

reduced by placing inverters on Q and

Q

p2

D

n1

n5

D

clk

clk

n2

2012, Dr. Paul D. Franzon, www.ece.ncsu.edu/erl/faculty/paulf.html

n6

35

ECE 733 Class Notes

DCVS

Combine to make Master-Slave Flip-flop

Better than single-sided flip-flops

Fewer gates than C2MOS

Fully static storage

Smaller clock load

Complementary faster operation

clk

p5

p2

p1

Q

p3

p4

n3

n1

D

n6

n7

n4

n5

D

clk

n2

2012, Dr. Paul D. Franzon, www.ece.ncsu.edu/erl/faculty/paulf.html

36

ECE 733 Class Notes

Operation

Clock = low:

clk

Master turned on

One of n1 or n5 turned on

n1 or n5 overpowers latch

p2

p1

p4

p3

Clock high

p5

n1

D

n7

n6

n3

n5

n4

D

clk

n2

Master

Slave

After thold, what prevents a false transition?

If D changes, can NOT result in the off n1 or n5 turning ON, as no PU path in

master

D changing can only result in the on transistor turning OFF: OK as latch has

already stored new value

2012, Dr. Paul D. Franzon, www.ece.ncsu.edu/erl/faculty/paulf.html

37

ECE 733 Class Notes

Operation

Ck=0; D=1

clk

p5

p1

p2

Q

p4

p3

n3 n4

n1

n6

n7

n5

clk

n2

Master

Slave

2012, Dr. Paul D. Franzon, www.ece.ncsu.edu/erl/faculty/paulf.html

38

ECE 733 Class Notes

Operation

Ck1; D=1

clk

p5

Float Hi

p1

p2

Q

p4

p3

n3 n4

n1

Q Q=0

n6

n7

n5

clk

n2

Master

Slave

2012, Dr. Paul D. Franzon, www.ece.ncsu.edu/erl/faculty/paulf.html

39

ECE 733 Class Notes

Operation

Ck=1; D0

(expect to see no transition)

clk

p5

p1

p2

Q

p4

p3

n3 n4

n1

D

n6 off

Q Q=0

n6

n7

n5 off

n5

clk

n2

Master

2012, Dr. Paul D. Franzon, www.ece.ncsu.edu/erl/faculty/paulf.html

Slave

40

ECE 733 Class Notes

DCVS

clk

Variant : Ratio insensitive Latch

p4

Removes need to overcome X-coupled D

latch to change state

Especially hard to overcome nFETs in

X-coupled inverters

Reduces sensitivity to process

variations

p5, p4 ensures Vdd/Gnd path broken

when changing stored state

p3 ties the on p1 or p2 to Vdd when

clock is low and latch is holding its

outputs

e.g. 0 held:

D has not changed:

p3

p5

p2

p1

Q

n3

n1

n4

D

Q

n5

clk

1

D has changed:

n2

Vdd path

2012, Dr. Paul D. Franzon, www.ece.ncsu.edu/erl/faculty/paulf.html

41

ECE 733 Class Notes

Operation

Ck=0; D=1

Ck1; D=1

clk

clk

p4

HI

p3

p2

p1

Q

n3

n1

n4

p4

p5

D

Q

n5

HI

p3

p5

p2

p1

Q

n3

n1

n4

D

Q

Q=1

n5

clk

clk

n2

n2

P3 OFF allows latch state to change easilly

2012, Dr. Paul D. Franzon, www.ece.ncsu.edu/erl/faculty/paulf.html

42

ECE 733 Class Notes

Operation

Ck0; D=1 (latch event)

Ck=0; D0 (expect no change)

clk

clk

p4

HI

p3

p2

p1

Q

n3

n1

n4

HI

p4

p5

D

Q

n5

Q=1

p3

p5

p2

p1

Q

n3

n1

n4

D

Q

Q=1

n5

clk

clk

n2

n2

P3 ON means latch data is preserved

2012, Dr. Paul D. Franzon, www.ece.ncsu.edu/erl/faculty/paulf.html

43

ECE 733 Class Notes

DCVS latch with pre-charge

Add pre-charge to increase speed:

Simple Latched Dual Rail Domino structure:

latch pair

clk

clk

Q

Q

D

D

clk

clk

clk

Q

Q

A

B

clk

Dynamic D latch with pre-charge

D latch with merged logic

2012, Dr. Paul D. Franzon, www.ece.ncsu.edu/erl/faculty/paulf.html

44

ECE 733 Class Notes

Single Transistor Clocked MS latches

Yuan & Svensson 97

p3

p1

p5

p4

p5

p2

p3

n1

n9

p2

n3

n10

p4

n4

n4

n5

n6

n8

n2

n1

(Dynamic)

p6

Small clock load; charge sharing issues

2012, Dr. Paul D. Franzon, www.ece.ncsu.edu/erl/faculty/paulf.html

n2

n3

(Semi-static)

Min. sizes. Ensures static

operation if D changes while

clk high.

45

ECE 733 Class Notes

operation

Ck=0; D=1

Ck1; D=1

p1

p1

p4

p4

p5

p5

p2

p2

p3

p3

n3

n3

n1

n2

n1

2012, Dr. Paul D. Franzon, www.ece.ncsu.edu/erl/faculty/paulf.html

n2

46

ECE 733 Class Notes

Operation

Ck=1; D->0

p1

p4

p5

p2

p3

n3

n1

n2

2012, Dr. Paul D. Franzon, www.ece.ncsu.edu/erl/faculty/paulf.html

47

ECE 733 Class Notes

Operation

Ck=0; D=1

Ck1; D=1

p3

p3

p5

p5

p6

Hi

n9

p2

Lo

n4

n1

n5

n2

n9

n10

p2

p4

n6

n4

n3

n1

2012, Dr. Paul D. Franzon, www.ece.ncsu.edu/erl/faculty/paulf.html

n10

p4

Lo

n8

p6

n5

n2

n6

n8

n3

48

ECE 733 Class Notes

Operation

Ck=1; D 0

p3

p5

Lo

p2

p6

n9

n10

p4

INV and nFETs it drives

help discharge floating node

n4

n1

2012, Dr. Paul D. Franzon, www.ece.ncsu.edu/erl/faculty/paulf.html

n5

n2

n6

n8

n3

49

ECE 733 Class Notes

Pulse-triggered Latch

Principle of Operation:

Hybrid Latch Flip-Flop (HLFF) (AMD, K6, Portovi, 1996)

Clocked Transistors

p1

p3

p2

X pre-charged (clock low)

Pulse samples D onto X

n3

p4

n6

Storage

n5

n2

n1

Master

2012, Dr. Paul D. Franzon, www.ece.ncsu.edu/erl/faculty/paulf.html

n4

Slave

50

ECE 733 Class Notes

HLFF

Operation:

Absorbs skew

Fully static (retains Q)

Negative setup

Allows cycle stealing

Can add logic

thold c.f. tD-Q

Precharge

(clock low)

Precharge

(clock high)

p1

p3

p2

n1

p4

n4

Storage

n2

n3

D high

2012, Dr. Paul D. Franzon, www.ece.ncsu.edu/erl/faculty/paulf.html

n5

n6

D low

51

ECE 733 Class Notes

HLFF Operation

Basic Structure

Precharge dynamic inverter master

Clock-evaluate inverter slave

Clock Low

Precharge X

Clock High

n1 on; n3 on for 3 INV delay

D high X low p4 pulls Q hi

D low X charge shared with n1_S; p2

turn on, pulling X high

After thold

p1

n1

n2

n3

p2

X

p3

p4

n4

n5

n6

tsu:

Can be negative

Criteria:

p3 (weak) turns on starts pulling X

As long as n2 turns on while n1, n3 Hi

high to help precharge

thold

D : Hi Lo : n2 off : no change as n3 off

Determined by:

D : Lo Hi : n2 on : no change as n3 off

and p3 keeps X high

time n3 on after optimal tsu point

2012, Dr. Paul D. Franzon, www.ece.ncsu.edu/erl/faculty/paulf.html

52

ECE 733 Class Notes

Operation

Ck=0; D=1

Ck1; D=1

p1

p2

p3

p1

p4

p2

p3

p4

Q=1

X

n1

n4

n1

n4

n2

n5

n2

n5

n3

n6

n3

n6

= turning off

= turning on

Critical path larger transistors

2012, Dr. Paul D. Franzon, www.ece.ncsu.edu/erl/faculty/paulf.html

53

ECE 733 Class Notes

Operation

Ck=1; X precharges

p1

n1

Ck=1; D0

p2

p3

p4

Q=1

n4

p2weak

p3

p1

n1

p4

Q=1

n4

n2

n5

n2

n5

n3

n6

n3

n6

Precharge helps defines size of weak pull-up

2012, Dr. Paul D. Franzon, www.ece.ncsu.edu/erl/faculty/paulf.html

54

ECE 733 Class Notes

Operation

Ck=0; D=0

Ck1; D=0

p1

n1

p2

p3

p4

p2weak

p3

p1

n4

n1

p4

Q=0

n4

n2

n5

n2

n5

n3

n6

n3

n6

Easier transition than 01.

Tsu determined by time for RHS sampler to replace role of LHS sampler if D=1

At clock going high, and then changes to 0 during pulse

2012, Dr. Paul D. Franzon, www.ece.ncsu.edu/erl/faculty/paulf.html

55

ECE 733 Class Notes

Operation

Ck=1; X precharges

p1

n1

Ck=1; D1

weak p3 reduces dip in X, as a result of

charge-sharing through n2, making

sure p4 does not turn on

p2

p3

p4

Q=1

p1

n5

n3

n6

p2

p3

Q=1

p4

n4

n2

weak

n1

n4

n2

n5

n3

n6

Helps defines size of weak pull-up

2012, Dr. Paul D. Franzon, www.ece.ncsu.edu/erl/faculty/paulf.html

56

ECE 733 Class Notes

HLFF Waveforms

charge share X to nfet n1

p1

p2

p3

p4

n1

n4

n2

n5

n3

n6

Weak p3 pulling X high

2012, Dr. Paul D. Franzon, www.ece.ncsu.edu/erl/faculty/paulf.html

57

ECE 733 Class Notes

Semi-Dynamic Flip Flop

Sun UltraSparc, Klass, VLSI Circuits 98

p1

p2

n1

n4

n2

n5

n3

2012, Dr. Paul D. Franzon, www.ece.ncsu.edu/erl/faculty/paulf.html

58

ECE 733 Class Notes

SDFF

Operation

p1

X

N1

n1

p2

n4

n2

n5

n3

Clk = low :

X precharged to

Clk hi :

D=0 :

1, N1 is ON

X stays high, N1 on then off, Q pulled down; 0 stored

After thold if D 1:

D=1:

N1 is off : No change

X goes low, leaving N1 on. Pulls Q high

After thold if D 0:

No P/G connection on LHS X latched low by X-coupled inverters)

2012, Dr. Paul D. Franzon, www.ece.ncsu.edu/erl/faculty/paulf.html

59

ECE 733 Class Notes

Operation

Ck=0; D=1

Ck1; D=1

p1

p1

1

n1

n3

1 0

p2

Q=1

n1

1

n2

p2

n4

n2

n5

0 1

n4

n5

n3

Defines critical path

Tsu: 3 nfets on long enough for 10 transistion

2012, Dr. Paul D. Franzon, www.ece.ncsu.edu/erl/faculty/paulf.html

60

ECE 733 Class Notes

Operation

Ck=1; D0

D=1; Ck0

p1

0

n1

1

n2

p2

Q=1

p1

0 1

n1

n4

1

n2

n5

p2

Q=1

n4

n5

n3

n3

Q does not change

2012, Dr. Paul D. Franzon, www.ece.ncsu.edu/erl/faculty/paulf.html

61

ECE 733 Class Notes

Operation

Ck=0; D=0

Ck1; D=0

p1

1

n1

1

n2

p1

p2

n4

n1 10

n5

n2

n3

0 1

p2

Q=0

n4

n5

n3

If D went high while Delayed ck

nFET is turning off, a different Q could result

(i.e. tsu could be negative, and the action

In LHS pull down chain defines tsu)

2012, Dr. Paul D. Franzon, www.ece.ncsu.edu/erl/faculty/paulf.html

62

ECE 733 Class Notes

Operation

Ck=1; D1

Ck0

p1

1

n1

0

n2

p2

1

n4

Q=0

p1

1

n1

n2

n5

n3

1

0

p2

Q=0

1

n4

n5

n3

Because top left nFET turned

off, Q does not change

2012, Dr. Paul D. Franzon, www.ece.ncsu.edu/erl/faculty/paulf.html

63

ECE 733 Class Notes

SDFF Timing Waveforms

2012, Dr. Paul D. Franzon, www.ece.ncsu.edu/erl/faculty/paulf.html

64

ECE 733 Class Notes

Sense Amp Flip Flop

Matsui, et.al. 1994, DEC Alpha 21264; StrongArm

110

Clocked T

DiffAmp

Storage

First stage : Sense Amp

Precharged to Hi when clk=0

p2, p3 :

Off

n3, n4 :

On

Clk 1

Diff Amp amplfies change in D

p2 or p3 turn on, latching value onto

storage cell

S or R go low

Role of N5

Keeps both INVs grounded even if D

changes

If D changes after thold

N5 reduces swing onto INVs

Strength of N5? Weak

SR latch

Ideal for low-swing inputs

2012, Dr. Paul D. Franzon, www.ece.ncsu.edu/erl/faculty/paulf.html

65

ECE 733 Class Notes

Operation

Ck=0; D=1

Ck1; D=1

0

1

Data stored in latch at top center

2012, Dr. Paul D. Franzon, www.ece.ncsu.edu/erl/faculty/paulf.html

66

ECE 733 Class Notes

Operation

Ck=1; D0

Ck0; D=1

2

0

0 4

0

1

Mn5 prevents change in latch

0 4

RS latch unaffected as S, R = 1

2012, Dr. Paul D. Franzon, www.ece.ncsu.edu/erl/faculty/paulf.html

67

ECE 733 Class Notes

SAFF Timing

Ck->1

N2 not on long enough to pull down

2 long enough to start turning N3 off.

Once N3 is enough, D-> 1 will no longer work

tsu

tforbidden

N3 is sufficiently off to prevent full transition

but on enough to start one

Tck-Q

N6-N1-N3 pulls 1 down

S->0

Delay in SR latch

2012, Dr. Paul D. Franzon, www.ece.ncsu.edu/erl/faculty/paulf.html

68

ECE 733 Class Notes

SAFF

2012, Dr. Paul D. Franzon, www.ece.ncsu.edu/erl/faculty/paulf.html

69

ECE 733 Class Notes

2012, Dr. Paul D. Franzon, www.ece.ncsu.edu/erl/faculty/paulf.html

70

ECE 733 Class Notes

Modified SAFF

2012, Dr. Paul D. Franzon, www.ece.ncsu.edu/erl/faculty/paulf.html

71

ECE 733 Class Notes

K6 ETL

p1

p2

p3

n1

p4

n3

n2

2012, Dr. Paul D. Franzon, www.ece.ncsu.edu/erl/faculty/paulf.html

n4

72

ECE 733 Class Notes

Operation

Clock Low:

p1

p3

n1

n2

p2

Nothing

p4

Clock Hi

n3

n4

Pulsed output!

-Must ensure output pulse

is sufficiently wide

D or Db sampled onto Q or Qb

by clock pulse

An input of NOR 1

rst Lo, 3 INV delays later

q, qb Hi

rst off

Self reset, Why?

Reduces clock load

2012, Dr. Paul D. Franzon, www.ece.ncsu.edu/erl/faculty/paulf.html

73

ECE 733 Class Notes

Flip Flop Comparison

2012, Dr. Paul D. Franzon, www.ece.ncsu.edu/erl/faculty/paulf.html

74

ECE 733 Class Notes

StrongArm

K6

Sense

Amp

SDFF

2012, Dr. Paul D. Franzon, www.ece.ncsu.edu/erl/faculty/paulf.html

75

ECE 733 Class Notes

HLFF

PowerPC

C2MOS

2012, Dr. Paul D. Franzon, www.ece.ncsu.edu/erl/faculty/paulf.html

76

ECE 733 Class Notes

Delay Comparison

2012, Dr. Paul D. Franzon, www.ece.ncsu.edu/erl/faculty/paulf.html

77

ECE 733 Class Notes

Power Delay Product

2012, Dr. Paul D. Franzon, www.ece.ncsu.edu/erl/faculty/paulf.html

78

ECE 733 Class Notes

Clock Power Consumption

2012, Dr. Paul D. Franzon, www.ece.ncsu.edu/erl/faculty/paulf.html

79

ECE 733 Class Notes

General Characteristics

2012, Dr. Paul D. Franzon, www.ece.ncsu.edu/erl/faculty/paulf.html

80

ECE 733 Class Notes

Reduced Clock Swing FlipFlop

Goal : Reduce clock power

Clock 20% - 40% of overall chip power

2012, Dr. Paul D. Franzon, www.ece.ncsu.edu/erl/faculty/paulf.html

81

ECE 733 Class Notes

Low Swing Double-Edge Triggered Flip-Flop

2012, Dr. Paul D. Franzon, www.ece.ncsu.edu/erl/faculty/paulf.html

82

ECE 733 Class Notes

Flip Flop Design Summary

In high performance circuits, what are some of the goals of Flip-Flop design?

Fast total tD-Q = tsu + tclk-Q

Minimum Power consumption

(internal + clock load)

Capture tradeoff:

-Power Delay product

(=Energy.Delay at constant fclk)

Narrow aperture time (tSU+thold )

Minimize sensitivity to clock slope; charge sharing; crosstalk; Vdd/Gnd noise

What design characteristics tend to produce the best flip-flops?

Use latch concepts in FFs; esp. pulsed clocked latches

- gives narrow aperture WITH negative tSU

Strive for reduced node swings

2012, Dr. Paul D. Franzon, www.ece.ncsu.edu/erl/faculty/paulf.html

83

Vous aimerez peut-être aussi

- Latches and Flip-FlopsDocument83 pagesLatches and Flip-FlopsDavidPas encore d'évaluation

- Timing Design in Digital Systems: Dr. Paul D. FranzonDocument38 pagesTiming Design in Digital Systems: Dr. Paul D. FranzonAmanViraniPas encore d'évaluation

- Dynamic Combinational Circuits: Dr. Paul D. FranzonDocument16 pagesDynamic Combinational Circuits: Dr. Paul D. FranzonqwertyPas encore d'évaluation

- Timing Design in Digital Systems: Dr. Paul D. FranzonDocument24 pagesTiming Design in Digital Systems: Dr. Paul D. FranzonMaheshPas encore d'évaluation

- Low Power Design: Dr. Paul D. FranzonDocument16 pagesLow Power Design: Dr. Paul D. FranzonBruno SilvaPas encore d'évaluation

- Low Power Design Techniques and StrategiesDocument14 pagesLow Power Design Techniques and Strategiessibint_2Pas encore d'évaluation

- Introduction to Classical and State Variable Control DesignDocument8 pagesIntroduction to Classical and State Variable Control Designcsunshine852Pas encore d'évaluation

- Thesis Online ChulaDocument7 pagesThesis Online Chulaangelagibbsdurham100% (2)

- Lec20 PDFDocument49 pagesLec20 PDFMustafa Rashik HasnainPas encore d'évaluation

- CMOS Logic StructuresDocument23 pagesCMOS Logic StructuressuprabhuPas encore d'évaluation

- Synthesizable Verilog: Dr. Paul D. FranzonDocument16 pagesSynthesizable Verilog: Dr. Paul D. FranzonVishnu ChilamakuruPas encore d'évaluation

- CAM HandoutsDocument45 pagesCAM Handoutsyashar2500Pas encore d'évaluation

- Literature Review Water Level IndicatorDocument8 pagesLiterature Review Water Level Indicatorea3c5mfq100% (1)

- SET-1: Answer To The Interview QuestionsDocument9 pagesSET-1: Answer To The Interview QuestionsÆshok IncreĐible KingPas encore d'évaluation

- Protocol Engineering: Bayu ErfiantoDocument36 pagesProtocol Engineering: Bayu ErfiantoRakaPramudyaRiptaningMurtiPas encore d'évaluation

- ComparatorDocument42 pagesComparatoramta1Pas encore d'évaluation

- Analysis and Construction of a Positive-Edge Triggered D Flip Flop CircuitDocument1 pageAnalysis and Construction of a Positive-Edge Triggered D Flip Flop CircuitKim Alexis MirasolPas encore d'évaluation

- Verilog I: Dr. Paul D. FranzonDocument29 pagesVerilog I: Dr. Paul D. Franzonshakya balPas encore d'évaluation

- Advanced Technologies Development Center Microelectronics & Nanotechology laboratory Design Kit Development Project TeamDocument21 pagesAdvanced Technologies Development Center Microelectronics & Nanotechology laboratory Design Kit Development Project TeamAmel ChPas encore d'évaluation

- Cmos01 1upDocument13 pagesCmos01 1upKritika NimeshPas encore d'évaluation

- Clock Skew ThesisDocument5 pagesClock Skew ThesisJody Sullivan100% (2)

- Understanding Timing in The Back-End Design Flow: Vlsi Ii: Design of Very Large Scale Integration CircuitsDocument23 pagesUnderstanding Timing in The Back-End Design Flow: Vlsi Ii: Design of Very Large Scale Integration CircuitsSiam HasanPas encore d'évaluation

- Research Paper On PipeliningDocument5 pagesResearch Paper On Pipeliningojfhsiukg100% (1)

- Basics of Timing AnalysisDocument70 pagesBasics of Timing AnalysisBharath DesareddyPas encore d'évaluation

- Deterministic Planning II & Probabilistic Planning IDocument53 pagesDeterministic Planning II & Probabilistic Planning IeviroyerPas encore d'évaluation

- Paterson 3 RD Open Foam WorkshopDocument24 pagesPaterson 3 RD Open Foam WorkshopGonzalo SáezPas encore d'évaluation

- Msu Thesis SubmissionDocument5 pagesMsu Thesis Submissionannabarrettdesmoines100% (2)

- E2 Lab Manual Spring 22Document68 pagesE2 Lab Manual Spring 22Rabia JadoonPas encore d'évaluation

- 7 CLK Tree SynthesisDocument64 pages7 CLK Tree Synthesisdharma_panga8217100% (1)

- DFTDocument14 pagesDFTRahulPas encore d'évaluation

- Pipelining Hazards LectureDocument42 pagesPipelining Hazards LectureRida AmjadPas encore d'évaluation

- LECTURE - 22 Basics of Real Basics of Real - Time Time Scheduling SchedulingDocument24 pagesLECTURE - 22 Basics of Real Basics of Real - Time Time Scheduling SchedulingUsman IftikharPas encore d'évaluation

- Analog Electronic Circuits and System 3e Gary Ford Carl ArftDocument134 pagesAnalog Electronic Circuits and System 3e Gary Ford Carl ArftTrevor CooperPas encore d'évaluation

- (Lec 17) Timing Analysis at The Logic LevelDocument29 pages(Lec 17) Timing Analysis at The Logic LevelBhuvin GowdaPas encore d'évaluation

- HRY-312 Computer Organization Introduction To PipeliningDocument30 pagesHRY-312 Computer Organization Introduction To Pipelininggami2Pas encore d'évaluation

- Reservoir Flood Routing2Document58 pagesReservoir Flood Routing2TibesoPas encore d'évaluation

- Delay BufferDocument29 pagesDelay BufferSathish Kumar JujjavarapuPas encore d'évaluation

- Lecture #32 Registers, Counters EtcDocument21 pagesLecture #32 Registers, Counters EtcRajan GoyalPas encore d'évaluation

- Design of Enhanced Hybrid Flip-Flop With Embedded Logic ModuleDocument6 pagesDesign of Enhanced Hybrid Flip-Flop With Embedded Logic ModuleInternational Journal of Application or Innovation in Engineering & ManagementPas encore d'évaluation

- TimingAnalysis Presentation v1 1Document70 pagesTimingAnalysis Presentation v1 1priyanka HundekarPas encore d'évaluation

- EE520 ASIC Design PDFDocument44 pagesEE520 ASIC Design PDFthiendoan_bkPas encore d'évaluation

- Laboratory ManualDocument67 pagesLaboratory ManualMitchell CifuentesPas encore d'évaluation

- R1Document28 pagesR1K VadlamaniPas encore d'évaluation

- Check ValveDocument83 pagesCheck Valvechu42Pas encore d'évaluation

- W04C - ETA Example-SeparatorDocument14 pagesW04C - ETA Example-SeparatorHasna Shintia PutriPas encore d'évaluation

- Liquip Monitor For Overfill and Grounding: Data Sheet Part N°: Pd501 Series TitleDocument3 pagesLiquip Monitor For Overfill and Grounding: Data Sheet Part N°: Pd501 Series TitleAbegail BernabePas encore d'évaluation

- Vlsi Interview Questions 2Document15 pagesVlsi Interview Questions 2Ganessh Balaji100% (1)

- BTH Master Thesis Software EngineeringDocument6 pagesBTH Master Thesis Software Engineeringdwsdzrcq100% (2)

- Research Paper On Full AdderDocument8 pagesResearch Paper On Full Adderhyz0tiwezif3100% (1)

- Timing Issues in FPGA Synchronous Circuit Design: ECE 428 Programmable ASIC DesignDocument33 pagesTiming Issues in FPGA Synchronous Circuit Design: ECE 428 Programmable ASIC DesignVarun KondagunturiPas encore d'évaluation

- 10-Print EC8261 CIRCUITS AND DEVICES LABORATORY ManualDocument49 pages10-Print EC8261 CIRCUITS AND DEVICES LABORATORY ManualBenPas encore d'évaluation

- Teaching Design While Constructing A 100-Watt Audio AmplifierDocument3 pagesTeaching Design While Constructing A 100-Watt Audio Amplifierungabo bungaPas encore d'évaluation

- Silvaco PDFDocument33 pagesSilvaco PDFkumarguptavPas encore d'évaluation

- Lecture 1 AnalogDocument13 pagesLecture 1 AnalogKishorePas encore d'évaluation

- CMOS Sequential Circuit Design Lec.-1Document22 pagesCMOS Sequential Circuit Design Lec.-1Parag ParandkarPas encore d'évaluation

- Dphil Thesis StructureDocument4 pagesDphil Thesis Structuretracydolittlesalem100% (2)

- Arduino Measurements in Science: Advanced Techniques and Data ProjectsD'EverandArduino Measurements in Science: Advanced Techniques and Data ProjectsPas encore d'évaluation

- Engineering the CMOS Library: Enhancing Digital Design Kits for Competitive SiliconD'EverandEngineering the CMOS Library: Enhancing Digital Design Kits for Competitive SiliconÉvaluation : 1 sur 5 étoiles1/5 (1)

- January - 2013 - 2013 CSEC MathsDocument6 pagesJanuary - 2013 - 2013 CSEC MathsRishi GopiePas encore d'évaluation

- Physics 2010 P2Document17 pagesPhysics 2010 P2Rishi Gopie100% (1)

- Physics 2003 P3Document5 pagesPhysics 2003 P3Rishi GopiePas encore d'évaluation

- Physics 2002 P3Document7 pagesPhysics 2002 P3Rishi GopiePas encore d'évaluation

- Physics 2006 P2Document12 pagesPhysics 2006 P2Rishi GopiePas encore d'évaluation

- Orm TP 221 8: Secon Ary Education Certificate Examina T ONDocument12 pagesOrm TP 221 8: Secon Ary Education Certificate Examina T ONRishi GopiePas encore d'évaluation

- Physics 2005 January P3Document7 pagesPhysics 2005 January P3Rishi GopiePas encore d'évaluation

- Physics 2008 P2Document11 pagesPhysics 2008 P2Rishi Gopie100% (3)

- CAPE Pure Mathematics SyllabusDocument139 pagesCAPE Pure Mathematics SyllabusDarnell Gracen100% (1)

- Physics 2003 P2Document14 pagesPhysics 2003 P2Rishi GopiePas encore d'évaluation

- Physics 1999 P2Document12 pagesPhysics 1999 P2Rishi GopiePas encore d'évaluation

- Physics 2000 P3Document5 pagesPhysics 2000 P3Rishi GopiePas encore d'évaluation

- Class 1 UnitsDocument8 pagesClass 1 UnitsRishi GopiePas encore d'évaluation

- Physics 2005 January P3Document7 pagesPhysics 2005 January P3Rishi GopiePas encore d'évaluation

- Binary AddersDocument23 pagesBinary Addersrajendra.rajuPas encore d'évaluation

- Chapter9 LatchesFlip FlopsAndTimersDocument27 pagesChapter9 LatchesFlip FlopsAndTimersRishi GopiePas encore d'évaluation

- Lecture Notes For Digital ElectronicsDocument43 pagesLecture Notes For Digital ElectronicsShruti GuptaPas encore d'évaluation

- Binary Adder 2Document5 pagesBinary Adder 2Rishi GopiePas encore d'évaluation

- Binary Adder 2Document5 pagesBinary Adder 2Rishi GopiePas encore d'évaluation

- Broadband Powerline Communication SystemDocument193 pagesBroadband Powerline Communication SystemBibhudutta PandaPas encore d'évaluation

- Chapter 30 Nuclear EnergyDocument14 pagesChapter 30 Nuclear EnergyRishi GopiePas encore d'évaluation

- 2G Cellular Networks GSM and IS95: A ComparisonDocument67 pages2G Cellular Networks GSM and IS95: A ComparisonRishi GopiePas encore d'évaluation

- Cie o Level Physics Syllabus For Year 2012Document46 pagesCie o Level Physics Syllabus For Year 2012Sakib Ex-rccPas encore d'évaluation

- Homework 5Document5 pagesHomework 5Ishan JawaPas encore d'évaluation

- Digital Logic Design fundamentalsDocument24 pagesDigital Logic Design fundamentalsFaraz KhanPas encore d'évaluation

- ANURAG GROUP OF INSTITUTIONS, Venktapur (V), Ghatkesar (M), Ranga Reddy (Dist.), A.P, INDIADocument8 pagesANURAG GROUP OF INSTITUTIONS, Venktapur (V), Ghatkesar (M), Ranga Reddy (Dist.), A.P, INDIAM Madan GopalPas encore d'évaluation

- Simulation and Synthesis Techniques For Asynchronous FIFO DesignDocument24 pagesSimulation and Synthesis Techniques For Asynchronous FIFO DesignKavyashreeMPas encore d'évaluation

- Converting PIC To Freescale Motorola HC08Document9 pagesConverting PIC To Freescale Motorola HC08hc_iePas encore d'évaluation

- Anna University CS2354 Advanced Computer Architecture Question PaperDocument2 pagesAnna University CS2354 Advanced Computer Architecture Question PaperpraveenaprabhuPas encore d'évaluation

- How To Avoid Lock Out ConditionDocument3 pagesHow To Avoid Lock Out ConditionSiva Guru100% (1)

- Chapter - 3 MOSFET AmplifiersDocument41 pagesChapter - 3 MOSFET AmplifiersNguyễn Phước Định TườngPas encore d'évaluation

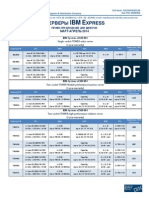

- Servers IBM Express - PromoDocument9 pagesServers IBM Express - PromogicuasemPas encore d'évaluation

- Computer Organization - Functional Units of A ComputerDocument31 pagesComputer Organization - Functional Units of A ComputerKiruthiga PrabakaranPas encore d'évaluation

- Sample Design of Half Adder Is Used To Explain The Design FlowDocument12 pagesSample Design of Half Adder Is Used To Explain The Design FlowSyam SandeepPas encore d'évaluation

- Projectos FPGA en Orcad 9Document8 pagesProjectos FPGA en Orcad 9Mario Sanchez DuartePas encore d'évaluation

- Static CMOS Inverter DC CharacteristicsDocument1 pageStatic CMOS Inverter DC CharacteristicsCarlos SaavedraPas encore d'évaluation

- Assignment 1 2020coaDocument5 pagesAssignment 1 2020coaAmit ChinaraPas encore d'évaluation

- FinFET FDSOIDocument15 pagesFinFET FDSOIsamiularefin2000Pas encore d'évaluation

- Pin Xcm001 ADocument4 pagesPin Xcm001 AadthvqsPas encore d'évaluation

- Using The Serial Peripheral Interface (SPI) Module On 68HC (9) 08 MicrocontrollersDocument8 pagesUsing The Serial Peripheral Interface (SPI) Module On 68HC (9) 08 MicrocontrollersJackson Dias RochaPas encore d'évaluation

- MicroprocessorsDocument25 pagesMicroprocessorsthereader94Pas encore d'évaluation

- El382 Microprocessors and Digital Control Systems 2019 1Document8 pagesEl382 Microprocessors and Digital Control Systems 2019 1Michael BOATEYPas encore d'évaluation

- Abit - M621 Schematics: Title Sheet ModifyDocument33 pagesAbit - M621 Schematics: Title Sheet Modify775i945GZ100% (1)

- Intel Desktop Board D945GNT/D945GTP Product Guide: Order NumberDocument74 pagesIntel Desktop Board D945GNT/D945GTP Product Guide: Order Numberkevint28Pas encore d'évaluation

- Hard Disk DriveDocument31 pagesHard Disk DrivePrincess Anne Vela OlayvarPas encore d'évaluation

- Atpg For Scan Chain Latches and FlipflopsDocument6 pagesAtpg For Scan Chain Latches and FlipflopsMaksi HutapeaPas encore d'évaluation

- M925 V.9.1 BDocument62 pagesM925 V.9.1 Bericgb86% (7)

- Unit-1 - DC & AC Circuits PDFDocument60 pagesUnit-1 - DC & AC Circuits PDFSaravanan T Y100% (5)

- N68C-GS FXDocument54 pagesN68C-GS FXEfren de la CruzPas encore d'évaluation

- HT1621 PDFDocument20 pagesHT1621 PDFJose Luis Mata LedesmaPas encore d'évaluation

- MramDocument15 pagesMramVeerendra VermaPas encore d'évaluation

- Lab Manual DLD LabDocument113 pagesLab Manual DLD Labqudratullah ehsan0% (1)

- Asynchronous Sequential Circuits DesignDocument33 pagesAsynchronous Sequential Circuits DesignPei Xin CheongPas encore d'évaluation