Académique Documents

Professionnel Documents

Culture Documents

Data Sheet

Transféré par

ΠΑΝΑΓΙΩΤΗΣΠΑΝΑΓΟΣCopyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

Data Sheet

Transféré par

ΠΑΝΑΓΙΩΤΗΣΠΑΝΑΓΟΣDroits d'auteur :

Formats disponibles

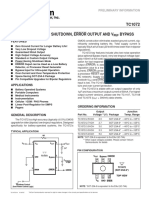

54ABT/74ABT373

Octal Transparent Latch with TRI-STATE Outputs

Y

General Description

The ABT373 consists of eight latches with TRI-STATE outputs for bus organized system applications. The flip-flops

appear transparent to the data when Latch Enable (LE) is

HIGH. When LE is LOW, the data that meets the setup

times is latched. Data appears on the bus when the Output

Enable (OE) is LOW. When OE is HIGH the bus output is in

the high impedance state.

Features

Y

Y

Y

Y

Y

Y

TRI-STATE outputs for bus interfacing

Output sink capability of 64 mA, source capability of

32 mA

Commercial

Military

Guaranteed output skew

Guaranteed multiple output switching specifications

Output switching specified for both 50 pF and 250 pF

loads

Guaranteed simultaneous switching, noise level and

dynamic threshold performance

Guaranteed latchup protection

High impedance glitch free bus loading during entire

power up and power down

Nondestructive hot insertion capability

Standard Military Drawing (SMD) 5962-9321801

Package

Number

Package Description

20-Lead (0.300 Wide) Molded Small Outline, JEDEC

74ABT373CSC (Note 1)

M20B

74ABT373CSJ (Note 1)

M20D

20-Lead (0.300 Wide) Molded Small Outline, EIAJ

74ABT373CPC

N20B

20-Lead (0.300 Wide) Molded Dual-In-Line

54ABT373J/883

J20A

20-Lead Ceramic Dual-In-Line

MSA20

20-Lead Molded Shrink Small Outline, EIAJ Type II

54ABT373W/883

W20A

20-Lead Cerpack

54ABT373E/883

E20A

20-Lead Ceramic Leadless Chip Carrier, Type C

MTC20

20-Lead Molded Thin Shrink Small Outline, JEDEC

74ABT373CMSA (Note 1)

74ABT373CMTC (Notes 1, 2)

Note 1: Devices also available in 13 reel. Use suffix e SCX, SJX, MSAX, and MTCX.

Note 2: Contact factory for package availability.

Connection Diagrams

Pin Assignment

for DIP, SOIC, SSOP and Flatpak

Pin Assignment

for LCC

Pin Names

D0 D7

LE

OE

O0 O7

Description

Data Inputs

Latch Enable Input

(Active HIGH)

Output Enable Input

(Active LOW)

TRI-STATE Latch

Outputs

TL/F/11547 2

TL/F/115471

TRI-STATE is a registered trademark of National Semiconductor Corporation.

C1995 National Semiconductor Corporation

TL/F/11547

RRD-B30M115/Printed in U. S. A.

54ABT/74ABT373 Octal Transparent Latch with TRI-STATE Outputs

September 1995

Physical Dimensions inches (millimeters) (Continued)

20-Lead Small Outline Integrated Circuit EIAJ (SJ)

NS Package Number M20D

20-Lead Plastic EIAJ SSOP (MSA)

NS Package Number MSA20

14

Vous aimerez peut-être aussi

- Data SheetDocument8 pagesData SheetΠΑΝΑΓΙΩΤΗΣΠΑΝΑΓΟΣPas encore d'évaluation

- Data SheetDocument16 pagesData SheetΠΑΝΑΓΙΩΤΗΣΠΑΝΑΓΟΣPas encore d'évaluation

- Types MC and MCN Multilayer RF Capacitors High-Frequency OptionsDocument9 pagesTypes MC and MCN Multilayer RF Capacitors High-Frequency OptionsΠΑΝΑΓΙΩΤΗΣΠΑΝΑΓΟΣPas encore d'évaluation

- Types MC and MCN Multilayer RF Capacitors High-Frequency OptionsDocument9 pagesTypes MC and MCN Multilayer RF Capacitors High-Frequency OptionsΠΑΝΑΓΙΩΤΗΣΠΑΝΑΓΟΣPas encore d'évaluation

- 3.3 V Ecl/Pecl/Hstl/Lvds: ÷2/4, ÷4/5/6 Clock Generation ChipDocument12 pages3.3 V Ecl/Pecl/Hstl/Lvds: ÷2/4, ÷4/5/6 Clock Generation ChipΠΑΝΑΓΙΩΤΗΣΠΑΝΑΓΟΣPas encore d'évaluation

- Data Sheet 1Document17 pagesData Sheet 1ΠΑΝΑΓΙΩΤΗΣΠΑΝΑΓΟΣPas encore d'évaluation

- Axial Leads/Spinguard: General DescriptionDocument6 pagesAxial Leads/Spinguard: General DescriptionΠΑΝΑΓΙΩΤΗΣΠΑΝΑΓΟΣPas encore d'évaluation

- Data SheetDocument19 pagesData SheetΠΑΝΑΓΙΩΤΗΣΠΑΝΑΓΟΣPas encore d'évaluation

- Data SheetDocument9 pagesData SheetΠΑΝΑΓΙΩΤΗΣΠΑΝΑΓΟΣPas encore d'évaluation

- Data SheetDocument6 pagesData SheetΠΑΝΑΓΙΩΤΗΣΠΑΝΑΓΟΣPas encore d'évaluation

- Data SheetDocument12 pagesData SheetΠΑΝΑΓΙΩΤΗΣΠΑΝΑΓΟΣPas encore d'évaluation

- Datasheet TL082 PDFDocument11 pagesDatasheet TL082 PDFJavier RenanPas encore d'évaluation

- VN0610LL FET Transistor: N Channel - EnhancementDocument4 pagesVN0610LL FET Transistor: N Channel - EnhancementΠΑΝΑΓΙΩΤΗΣΠΑΝΑΓΟΣPas encore d'évaluation

- LM1117Document21 pagesLM1117dipankaborahPas encore d'évaluation

- TC1072 50ma Cmos Ldo With Shutdown, Error Output and V BypassDocument12 pagesTC1072 50ma Cmos Ldo With Shutdown, Error Output and V BypassΠΑΝΑΓΙΩΤΗΣΠΑΝΑΓΟΣPas encore d'évaluation

- AX97 Series: SMD Power InductorsDocument3 pagesAX97 Series: SMD Power InductorsΠΑΝΑΓΙΩΤΗΣΠΑΝΑΓΟΣPas encore d'évaluation

- CD 4023Document12 pagesCD 4023giorgio19741Pas encore d'évaluation

- Patented : SM6S10 Thru SM6S36ADocument5 pagesPatented : SM6S10 Thru SM6S36AΠΑΝΑΓΙΩΤΗΣΠΑΝΑΓΟΣPas encore d'évaluation

- Data SheetDocument4 pagesData SheetΠΑΝΑΓΙΩΤΗΣΠΑΝΑΓΟΣPas encore d'évaluation

- DMTH6004SPS: 60V 175°C N-Channel Enhancement Mode Mosfet PowerdiDocument7 pagesDMTH6004SPS: 60V 175°C N-Channel Enhancement Mode Mosfet PowerdiΠΑΝΑΓΙΩΤΗΣΠΑΝΑΓΟΣPas encore d'évaluation

- 54ACT283 4-Bit Binary Full Adder With Fast Carry: General Description FeaturesDocument8 pages54ACT283 4-Bit Binary Full Adder With Fast Carry: General Description FeaturesΠΑΝΑΓΙΩΤΗΣΠΑΝΑΓΟΣPas encore d'évaluation

- Data SheetDocument16 pagesData SheetΠΑΝΑΓΙΩΤΗΣΠΑΝΑΓΟΣPas encore d'évaluation

- Wall Plug Ins Electrical SpecsDocument1 pageWall Plug Ins Electrical SpecsΠΑΝΑΓΙΩΤΗΣΠΑΝΑΓΟΣPas encore d'évaluation

- Data SheetDocument4 pagesData SheetΠΑΝΑΓΙΩΤΗΣΠΑΝΑΓΟΣPas encore d'évaluation

- 8K Microwire Compatible Serial EEPROM: 93AA76A/B/C, 93LC76A/B/C, 93C76A/B/CDocument26 pages8K Microwire Compatible Serial EEPROM: 93AA76A/B/C, 93LC76A/B/C, 93C76A/B/CΠΑΝΑΓΙΩΤΗΣΠΑΝΑΓΟΣ100% (1)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeD'EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeÉvaluation : 4 sur 5 étoiles4/5 (5783)

- The Yellow House: A Memoir (2019 National Book Award Winner)D'EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Évaluation : 4 sur 5 étoiles4/5 (98)

- Never Split the Difference: Negotiating As If Your Life Depended On ItD'EverandNever Split the Difference: Negotiating As If Your Life Depended On ItÉvaluation : 4.5 sur 5 étoiles4.5/5 (838)

- Shoe Dog: A Memoir by the Creator of NikeD'EverandShoe Dog: A Memoir by the Creator of NikeÉvaluation : 4.5 sur 5 étoiles4.5/5 (537)

- The Emperor of All Maladies: A Biography of CancerD'EverandThe Emperor of All Maladies: A Biography of CancerÉvaluation : 4.5 sur 5 étoiles4.5/5 (271)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceD'EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceÉvaluation : 4 sur 5 étoiles4/5 (890)

- The Little Book of Hygge: Danish Secrets to Happy LivingD'EverandThe Little Book of Hygge: Danish Secrets to Happy LivingÉvaluation : 3.5 sur 5 étoiles3.5/5 (399)

- Team of Rivals: The Political Genius of Abraham LincolnD'EverandTeam of Rivals: The Political Genius of Abraham LincolnÉvaluation : 4.5 sur 5 étoiles4.5/5 (234)

- Grit: The Power of Passion and PerseveranceD'EverandGrit: The Power of Passion and PerseveranceÉvaluation : 4 sur 5 étoiles4/5 (587)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaD'EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaÉvaluation : 4.5 sur 5 étoiles4.5/5 (265)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryD'EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryÉvaluation : 3.5 sur 5 étoiles3.5/5 (231)

- On Fire: The (Burning) Case for a Green New DealD'EverandOn Fire: The (Burning) Case for a Green New DealÉvaluation : 4 sur 5 étoiles4/5 (72)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureD'EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureÉvaluation : 4.5 sur 5 étoiles4.5/5 (474)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersD'EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersÉvaluation : 4.5 sur 5 étoiles4.5/5 (344)

- The Unwinding: An Inner History of the New AmericaD'EverandThe Unwinding: An Inner History of the New AmericaÉvaluation : 4 sur 5 étoiles4/5 (45)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyD'EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyÉvaluation : 3.5 sur 5 étoiles3.5/5 (2219)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreD'EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreÉvaluation : 4 sur 5 étoiles4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)D'EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Évaluation : 4.5 sur 5 étoiles4.5/5 (119)

- Her Body and Other Parties: StoriesD'EverandHer Body and Other Parties: StoriesÉvaluation : 4 sur 5 étoiles4/5 (821)