Académique Documents

Professionnel Documents

Culture Documents

MAC Instruction Sequence Steps Exam Questions

Transféré par

nizobellDescription originale:

Titre original

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

MAC Instruction Sequence Steps Exam Questions

Transféré par

nizobellDroits d'auteur :

Formats disponibles

1

Instructions: ANSWER ALL QUESTIONS in the answer booklets provided. If you make any

assumptions, clearly state them in your answer booklet.

Materials Allowed: Course textbook, course lecture notes, ENCS approved electronic

calculators.

Location: H539-1

Time: 19:00-22:00

Question 1: [20 points]

The multiply-and-accumulate operation nds use in many digital signal applications. Digital

signal processors often include a dedicated instruction as part of their instructions sets which

perform the operation. Consider the following three address instruction:

MAC

source1,source2,source3/destination

This instruction will perform the operation:

source3/destination<=(source1xsource2)+source3/destination

In other words, the MAC (the mnemonic for multiply-and-accumulate) instruction

multiplies

the two specied source operands and adds to result to the third source which also acts as

the nal

destination.

(a) Identify all the addressing modes used in the following instruction:

MAC

#NUM,(R0)+,R1

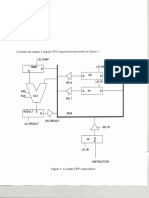

(b) The sequence of control steps to perform an instruction fetch using the single-bus

internal

CPU organization shown in Figure 1 are:

T0: BUS <= PC, MAR <= BUS, sel_temp = 1, F = ADD, ld_result = 1.

T1: READ = 1, MDR <= data_out from memory (this implies ld_mdr = 1 and sel_mdr =

1),

BUS <= RESULT, PC <= BUS.

T2: BUS <= MDR, IR <= BUS.

In the above, we assume that main memory will respond (for a READ or a WRITE) within

one

clock cycle.

(i) What advantage does the multiplexer at the input of the MDR offer in terms of program

execution speed?

(ii) Rewrite the sequence of control steps needed to perform an instruction fetch given that

the

MDR multiplexer is NOT present (i.e. the MDR is loaded directly from the bus). What

modications would be required to the existing bus organization to accommodate this change?

(c) Give the sequence of control steps to execute the MAC#NUM,(R0)+,R1instruction.

Assume the existence of the MDR multiplexer when answering this question. You may

assume

that the instruction occupies one main memory location and that the ALU is capable of

performing a multiply operation.

BUS

ld_ir

ld_temp

TEMP

IR

en_ir

ld_pc

PC

"1"

0

en_pc

ld_r0

sel_temp

R0

en_r0

F=

R1

ALU

.

.

Rn

ld_result

RESULT

MAR

en_res

0

MDR

1

SP

address

MEMORY

data_in

R

data_out

W

Figure 1: A single-bus internal CPU organization.

sel_mdr

Question 2: [20 points]

Consider the following Intel 80x86 assembly language program:

section.data

numberdb5

answerdb1

section.bss

;putUNINITIALIZEDdatahereusing

section.text

global_start

_start:

movesi,number

keith:moveax,0

moval,[esi]

movdl,al

movbl,2

loopy:divbl;ax/blwithquotient inal andremainder inah

andax,1111111100000000b

cmpax,0

jethere

incbl

cmpbl,dl

jedone

moveax,0;restorethenumberbackinto

moval,[esi];ax

jmploopy

there:movbyte[answer],0

done:

moveax,1;Thesystemcallforexit(sys_exit)

movebx,0;Exitwithreturncodeof0(noerror)

int80h

(a) State in a few short, clear and concise English sentences the action performed by this

program.

An example of a correct method of expressing an answer would

be:

This program removes all vowels from the null-terminated ASCII string stored commencing

at

memory location number. Vowels are replaced with the blank character. Furthermore, any

ASCII

characters corresponding to the digits 0, 1, 2. ... 9 are replaced with their 9s

complement

Of course, this is meant merely as an example. The program performs something

value and will appear in inverse video when displayed on a VGA monitor.

else.

(b) What values will be stored in memory location answerif the program is run with value

5

and then value 6stored in memory location number?

Question 3: [20 points]

(a) Consider a small 8 x 3-bit random access memory which makes use of the binary

storage cell

illustrated in Figure 2. The basic storage cell employs an AND gate at its output as opposed

to

using a tri-state buffer.

select

data input

data output

Read/Write

Figure 2: Block diagram of a binary storage cell.

(i) How many binary storage cells would be needed to construct the random access

memory?

(ii) Show the internal construction of the random access memory assuming a 1-dimensional

address decoding technique is employed. When drawing your diagram, make use of the

block

diagram of the binary storage cell and any other hardware components required. Use

A2A1A0

for the address lines (line A2 is the most signicant address bit) , d2d1d0 for the input data

lines

(d2 is the most signicant data bit), dout2dout1dout0 for the output data lines, R/W for the

read/

write

line and

enable

for a

the

enable of theaddress

memory.

Your drawing

MUSTUse

be clear

andlines

legible

(iii) Repeat

part(ii)

using

2-dimensional

decoding

technique.

address

and

A2A1

indicate

all row

signal

names.and address line A0 to perform column decoding. In the interest of

to perform

decoding

diagram clarity, it is not necessary to show the connections used for the data input signals, nor

the R/

W signal. It is also sufcient to merely show the hardware and the signal interconnections

necessary to generate the dout0 output data line. As in part (ii) your drawing MUST be clear and

legible.

(iv) Explain in words (or with the aid of a small diagram) what would change in part (ii) and

part (iii) if binary storage cells with tri-state output capability were employed in the

construction

of the RAM.

(b) Which of the following give the correct number of SRAM chips of size 1 048 576 locations

with 8 bits per location, and the size of the address decoder needed to build a SRAM

memory system with a total capacity of 8 589 934 000 locations with 32 bits per location using a 1D

organization?

Hint:

220=1048576=1Mega

(210)(220)=230=1073741000=1Giga

(23)(210)(220)=233=8589934000=8Giga

(i) 8 192 chips with a 32 -to- 8 589 934 000 address decoder.

(ii) 32 768 chips with a 32 -to- 8 589 934 000 address decoder.

(iii) 32 768 chips with a 13 -to- 8192 address decoder.

(iv) Not even Keith has enough money to buy the necessary amount of SRAM chips in

order to

construct this memory system.

Question 4: [20 points]

(a) The use of a FRAME POINTER register within a CPU allows for a subroutine to:

(i) point to the next element to be popped from the

stack.

(ii) point to the bottom of the stack

(iii) access any passed parameters pushed onto the stack by the calling routine and to

access any

local variables in the stack.

(iv) obtain the address of the next instruction to be

executed.

(v) point to itself during a recursive call.

Indicate your answer by choosing one of the above 5

choices.

(b) Express the decimal number 3.1415926(pi to 7 decimal place accuracy) in IEEE-754

32

bit format.

(c) Given the following word (one word = 2 bytes) sized data 0xABCD( expressed in

hexadecimal) show how the data would be stored in a byte-sized main memory for a CPU which uses

high

byte followed by low byte versus a machine which stores words in low byte followed by high

byte order.

(d) ROM is volatile. TRUE or FALSE?

(e) A ROM can be re-programmed after it has been manufactured. TRUE or

FALSE?

Question 5: [20 points]

Consider a small block-set-associative cache memory with a total of 4 different sets. Each

set

consists of two blocks. Each block contains 4 locations. Main memory consists of a total of

512

different locations. Answer the following questions for this cache-main memory

(a) Give the format of a main memory address in the form

organization.

of :

TTTT

SSS WWW

Be sure to specify the number of bits required in each eld of the main memory

address.

(b) How many different main memory blocks maps onto each cache

set?

(c) To which cache set does main memory address (12F)16map

onto ?

(d) Assume that the tags of the main memory blocks currently residing in cache set 2

are:

00000and 10010.

Indicate whether a cache hit or a cache miss occurs if the CPU generates the following 4

main

memory addresses (all addresses are specied in hexadecimal notation) :

008

00B

12A

1F8

(e) If the block in cache set 2 with tag = 10010is chosen as the victim block in the case

of a

cache miss, in which main memory block does this cache block reside in?

Vous aimerez peut-être aussi

- Gulf Business - September 2010Document84 pagesGulf Business - September 2010motivatepublishingPas encore d'évaluation

- What's - July 2010 - Abu DhabiDocument116 pagesWhat's - July 2010 - Abu DhabimotivatepublishingPas encore d'évaluation

- Workstation Precision m4400 BrochureDocument2 pagesWorkstation Precision m4400 BrochurestopsherenowPas encore d'évaluation

- All Digital Hub Pricelist with Contact Details and ProductsDocument3 pagesAll Digital Hub Pricelist with Contact Details and ProductsOdlanorSontsa100% (1)

- Calista Luxury Resort VIP Concept All InclusiveDocument12 pagesCalista Luxury Resort VIP Concept All InclusiveChristopher HenryPas encore d'évaluation

- DALI Explorer User ManualDocument4 pagesDALI Explorer User ManualfarshathPas encore d'évaluation

- Major Telecom Vendors and Subcons in KSADocument2 pagesMajor Telecom Vendors and Subcons in KSAMuhammad Awais AshfaqPas encore d'évaluation

- Dahua Price ListDocument18 pagesDahua Price ListTufail Khan100% (1)

- Cardinal 225 Tech ManualDocument116 pagesCardinal 225 Tech ManualaswinraveendranPas encore d'évaluation

- CSB0028Document2 pagesCSB0028chinnaPas encore d'évaluation

- 2023 WASH Cluster Partner Operational Precence JuneDocument2 pages2023 WASH Cluster Partner Operational Precence JuneResilient GemePas encore d'évaluation

- Jobs in UAE (With Salaries) - Indeed - Ae PDFDocument1 pageJobs in UAE (With Salaries) - Indeed - Ae PDFAshish SharmaPas encore d'évaluation

- Nasscom Industry ReportDocument120 pagesNasscom Industry ReportShekhar AnandPas encore d'évaluation

- Trujet Media Kit 2017 18Document7 pagesTrujet Media Kit 2017 18సాయి కశ్యప్100% (1)

- DancomechDocument2 pagesDancomechTakrimi IsmailPas encore d'évaluation

- Hotels CdoDocument5 pagesHotels Cdojane_rockets100% (1)

- CNC, CNC Router Table, CNC Plan, CNC PlanıDocument54 pagesCNC, CNC Router Table, CNC Plan, CNC Planıduranigne100% (9)

- Apple Accessory ProtocolDocument9 pagesApple Accessory ProtocolGino MarchalPas encore d'évaluation

- User AgentDocument2 pagesUser AgenthuongPas encore d'évaluation

- Hotels in SeychellesDocument20 pagesHotels in SeychellesMak KhanPas encore d'évaluation

- Hotel MapDocument1 pageHotel MapNazura PatelPas encore d'évaluation

- Hadef & Partners Welcome To DubaiDocument11 pagesHadef & Partners Welcome To Dubaimeforall84Pas encore d'évaluation

- Answer Model Cs303 Systemsoftware November2018Document43 pagesAnswer Model Cs303 Systemsoftware November2018Nova DileepPas encore d'évaluation

- DM 810Document5 pagesDM 810andersonbheringPas encore d'évaluation

- Cable Headend-Hub TechnologiesDocument251 pagesCable Headend-Hub Technologiesaltobruno100% (1)

- Apm30h Tmc11h Ibbs Installation GuideDocument41 pagesApm30h Tmc11h Ibbs Installation GuidePompi Edw PortiPas encore d'évaluation

- Etisilat and Du Eco ProjectDocument22 pagesEtisilat and Du Eco ProjectSiddharth ShahPas encore d'évaluation

- Land AreaDocument1 pageLand AreaprOPas encore d'évaluation

- Fragmentation PDFDocument6 pagesFragmentation PDFDibyendu PaulPas encore d'évaluation

- Technical Brief Avaya DMCC Application NotesDocument2 pagesTechnical Brief Avaya DMCC Application Notesrandom54321Pas encore d'évaluation

- Dubai Internet CityDocument11 pagesDubai Internet Citytvsameel7208100% (1)

- 100127068Document29 pages100127068karthidevPas encore d'évaluation

- ATC200-LITE-USB Teletilt Control System Computer Interface Setup 639559Document2 pagesATC200-LITE-USB Teletilt Control System Computer Interface Setup 639559Jw Gibson100% (1)

- Mideast Africa OfficesDocument15 pagesMideast Africa OfficesSajal AroraPas encore d'évaluation

- Installing and Activating Autodesk 2016Document10 pagesInstalling and Activating Autodesk 2016Sabin CodreanuPas encore d'évaluation

- Recruiting and Allied Agencies in UAEDocument8 pagesRecruiting and Allied Agencies in UAEAboobackerEriyadanPas encore d'évaluation

- Subnettibg & Vlsm QUESTIONS مع الاجوبة والشرحDocument7 pagesSubnettibg & Vlsm QUESTIONS مع الاجوبة والشرحZizou ZazouPas encore d'évaluation

- India Information Technology ReportDocument43 pagesIndia Information Technology Reportprateeksri10Pas encore d'évaluation

- List of Local Organization With Disclaimer - 145 PDFDocument2 pagesList of Local Organization With Disclaimer - 145 PDFAyaz Ahmed KhanPas encore d'évaluation

- Instruction Manual For RTN 620 (HW MW)Document37 pagesInstruction Manual For RTN 620 (HW MW)ПашаЖируха100% (1)

- Jtag To Sb5101 Install All Sb5101 Working Bin Stock Haxorware & Ambit 250 2mb Full Flash !!! Tested ! ! !Document6 pagesJtag To Sb5101 Install All Sb5101 Working Bin Stock Haxorware & Ambit 250 2mb Full Flash !!! Tested ! ! !narakas171Pas encore d'évaluation

- Seafarer'S Application Form: Present PermanentDocument5 pagesSeafarer'S Application Form: Present PermanentJean BalaticoPas encore d'évaluation

- G LI 002 BTS3006C Hardware Structure 20070403 A 1.0Document72 pagesG LI 002 BTS3006C Hardware Structure 20070403 A 1.0naveedalishaPas encore d'évaluation

- EIST Unlocked Example Rev 1.1aDocument14 pagesEIST Unlocked Example Rev 1.1aSonny LabielPas encore d'évaluation

- VDA Company Profile 2021 ENDocument31 pagesVDA Company Profile 2021 ENluong phamPas encore d'évaluation

- List of Chemanol Accredited Hotels in GCCDocument3 pagesList of Chemanol Accredited Hotels in GCCManoj0% (1)

- Dubai Senior Technician Muhammad Dilshad resumeDocument1 pageDubai Senior Technician Muhammad Dilshad resumeAzhar HussainPas encore d'évaluation

- The DB9-USB Family of UART Converter Modules: DatasheetDocument26 pagesThe DB9-USB Family of UART Converter Modules: DatasheetScoundrel BytePas encore d'évaluation

- HP Pavilion TX1000 SchematicsDocument36 pagesHP Pavilion TX1000 Schematicsmeng798651100% (1)

- MCU-200 Ruggedized Data SheetDocument2 pagesMCU-200 Ruggedized Data Sheet송민호Pas encore d'évaluation

- Eal30 La-2691Document53 pagesEal30 La-2691anon_184197599100% (1)

- Curriculum Vitae - Doc - JIJO PHILIPDocument4 pagesCurriculum Vitae - Doc - JIJO PHILIPIndia_JIPHPas encore d'évaluation

- 0438Document9 pages0438Ahmed BilalPas encore d'évaluation

- TCS TeleTech Oracle issue tracking reportDocument12 310 pagesTCS TeleTech Oracle issue tracking reportSoorav MlicPas encore d'évaluation

- MCS 012Document4 pagesMCS 012rajatkumar.codingPas encore d'évaluation

- Solutions To Set 8Document18 pagesSolutions To Set 8kitana_sectPas encore d'évaluation

- Amazon Online Assessment 2021 QuestionsDocument12 pagesAmazon Online Assessment 2021 QuestionsCoder Coder0% (2)

- CAO Set 8Document8 pagesCAO Set 8Vilayat AliPas encore d'évaluation

- MCS-012 - Computer Organisation and AssemblyDocument4 pagesMCS-012 - Computer Organisation and AssemblyLataPuthranPas encore d'évaluation

- B.E./B.Tech. DEGREE EXAMINATION Computer Architecture QuestionsDocument3 pagesB.E./B.Tech. DEGREE EXAMINATION Computer Architecture QuestionssamueljamespeterPas encore d'évaluation

- SOEN 344 6 Design PatternsDocument70 pagesSOEN 344 6 Design PatternsnizobellPas encore d'évaluation

- Lecture 6A - Genetic PedigreesDocument43 pagesLecture 6A - Genetic Pedigreesnizobell50% (2)

- SOEN 344-7 - Design PatternsDocument67 pagesSOEN 344-7 - Design PatternsnizobellPas encore d'évaluation

- SOEN 344 5 Design PatternsDocument70 pagesSOEN 344 5 Design PatternsnizobellPas encore d'évaluation

- Lecture 5 - How Genes Are Transmitted From Generation To GenerationIIDocument30 pagesLecture 5 - How Genes Are Transmitted From Generation To GenerationIInizobellPas encore d'évaluation

- Lecture 1112 - DNA and ReplicationDocument50 pagesLecture 1112 - DNA and ReplicationnizobellPas encore d'évaluation

- SOEN 344-3a - Design PatternsDocument54 pagesSOEN 344-3a - Design PatternsnizobellPas encore d'évaluation

- SOEN 344-4-Design PatternsDocument61 pagesSOEN 344-4-Design PatternsnizobellPas encore d'évaluation

- SOEN 344-3b-Design PatternsDocument28 pagesSOEN 344-3b-Design PatternsnizobellPas encore d'évaluation

- Understanding Chromosomal AbnormalitiesDocument43 pagesUnderstanding Chromosomal AbnormalitiesnizobellPas encore d'évaluation

- Lecture 8 - Genetics of ComplexTraits IIDocument47 pagesLecture 8 - Genetics of ComplexTraits IInizobellPas encore d'évaluation

- A4 Abinader F2013Document11 pagesA4 Abinader F2013nizobellPas encore d'évaluation

- Genes: How Traits Are InheritedDocument36 pagesGenes: How Traits Are InheritednizobellPas encore d'évaluation

- Lecture 7 - Genetics of Complex TraitsDocument36 pagesLecture 7 - Genetics of Complex TraitsnizobellPas encore d'évaluation

- Sex and Development: Ronnee Yashon Michael CummingsDocument27 pagesSex and Development: Ronnee Yashon Michael CummingsnizobellPas encore d'évaluation

- Lecture 1A - Chapter 1 Course Introduction, Why Project ManagementDocument14 pagesLecture 1A - Chapter 1 Course Introduction, Why Project ManagementnizobellPas encore d'évaluation

- Chemistry Formula SheetDocument10 pagesChemistry Formula Sheetfghtrpltf16Pas encore d'évaluation

- A2 Abinader F2013 0Document8 pagesA2 Abinader F2013 0nizobellPas encore d'évaluation

- Comp228 Notes 6Document29 pagesComp228 Notes 6nizobellPas encore d'évaluation

- Chem205Lec51-AMT F2011Document13 pagesChem205Lec51-AMT F2011nizobellPas encore d'évaluation

- Engr213midterm II Fall2015 SolutionsDocument8 pagesEngr213midterm II Fall2015 SolutionsnizobellPas encore d'évaluation

- Comp228 Notes 5b PDFDocument45 pagesComp228 Notes 5b PDFnizobellPas encore d'évaluation

- Comp228 Notes 5a PDFDocument21 pagesComp228 Notes 5a PDFnizobellPas encore d'évaluation

- Comp228 Notes 4 PDFDocument29 pagesComp228 Notes 4 PDFnizobellPas encore d'évaluation

- Assignment #1 F13 PDFDocument3 pagesAssignment #1 F13 PDFnizobellPas encore d'évaluation

- Introduction to SQL Server EnvironmentDocument12 pagesIntroduction to SQL Server EnvironmentCassie CutiePas encore d'évaluation

- Number: 200-301 Passing Score: 800 Time Limit: 120 Min File Version: 0Document11 pagesNumber: 200-301 Passing Score: 800 Time Limit: 120 Min File Version: 0Geekware PeruPas encore d'évaluation

- Answer : Find Missing Element in List of ArrayDocument3 pagesAnswer : Find Missing Element in List of Arraymadhavi uPas encore d'évaluation

- RSFactoryTalk SE & Microsoft SQL Server - PLCSDocument3 pagesRSFactoryTalk SE & Microsoft SQL Server - PLCSrodriggoguedesPas encore d'évaluation

- Practical File Grade 12Document13 pagesPractical File Grade 12azeeemkhaan3830Pas encore d'évaluation

- Created by .. Shatakshi RDocument23 pagesCreated by .. Shatakshi RShatakshi RampurePas encore d'évaluation

- Full Download Ebook Ebook PDF Modern Database Management 12th Edition PDFDocument41 pagesFull Download Ebook Ebook PDF Modern Database Management 12th Edition PDFjoe.imhof180100% (33)

- Node JsDocument3 pagesNode Jspreda andreiPas encore d'évaluation

- LB - ImagesDocument4 pagesLB - ImagesCode on MindPas encore d'évaluation

- Discovery Data CollectionDocument269 pagesDiscovery Data Collectionsubbu1228Pas encore d'évaluation

- Setup Log 2014-05-27 #004Document9 pagesSetup Log 2014-05-27 #004adfhdafhPas encore d'évaluation

- Parity Release Notes - V7.0.0 General AvailabilityDocument18 pagesParity Release Notes - V7.0.0 General AvailabilityHenry100% (1)

- Lesson 6 - Hibernate Queries and RelationshipDocument70 pagesLesson 6 - Hibernate Queries and RelationshipNaveen KumarPas encore d'évaluation

- ENSC 351: Real-Time and Embedded Systems: Craig Scratchley, Spring 2014 Multipart Project Part 2ADocument3 pagesENSC 351: Real-Time and Embedded Systems: Craig Scratchley, Spring 2014 Multipart Project Part 2ARobert HoPas encore d'évaluation

- Oled - I2C: ManualDocument8 pagesOled - I2C: Manualsloko2Pas encore d'évaluation

- PHP Variables: PHP Variable: Declaring String, Integer, and FloatDocument16 pagesPHP Variables: PHP Variable: Declaring String, Integer, and Floatpaula.garzarodriguez.23Pas encore d'évaluation

- 840Dsl Ncvar PLC Sig Lists Man 1218 en-USDocument1 722 pages840Dsl Ncvar PLC Sig Lists Man 1218 en-USeusofisoPas encore d'évaluation

- Instruction Set 8086Document63 pagesInstruction Set 8086Kavitha SubramaniamPas encore d'évaluation

- Dvp-Es2 Ss2 Sa2 Sx2-Program o en 20110302Document609 pagesDvp-Es2 Ss2 Sa2 Sx2-Program o en 20110302puskyboyPas encore d'évaluation

- SAP Directory Structure for UNIX SystemsDocument10 pagesSAP Directory Structure for UNIX SystemsDevender5194Pas encore d'évaluation

- Linux Interview QDocument9 pagesLinux Interview QAbdullah AdelPas encore d'évaluation

- This Is Cloud Data ManagementDocument2 pagesThis Is Cloud Data ManagementRayanPas encore d'évaluation

- SemaphoreDocument29 pagesSemaphoreSaranya ThangarajPas encore d'évaluation

- Radix Sort AlgorithmDocument10 pagesRadix Sort AlgorithmNithin ChandyPas encore d'évaluation

- Learning Life Cycle ManagementDocument21 pagesLearning Life Cycle ManagementjessyhamidPas encore d'évaluation

- Computer Structure - MemoryDocument61 pagesComputer Structure - MemoryLotso Chik100% (1)

- User Guide For KPI ReporterDocument61 pagesUser Guide For KPI ReporterAnh DaoPas encore d'évaluation

- Apache HTTP Server Main Configuration FileDocument15 pagesApache HTTP Server Main Configuration FileĐình KhangPas encore d'évaluation

- Learn Oracle Weblogic Server 12C Administration: For Middleware AdministratorsDocument81 pagesLearn Oracle Weblogic Server 12C Administration: For Middleware AdministratorspradeepPas encore d'évaluation

- The Advantages of Client/Server ComputingDocument5 pagesThe Advantages of Client/Server ComputingPuspala ManojkumarPas encore d'évaluation