Académique Documents

Professionnel Documents

Culture Documents

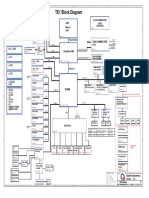

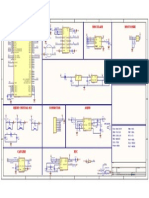

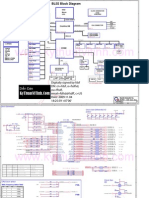

Schematic Content: Altera Cyclone II FPGA Starter Board

Transféré par

Albert Ponic NinyehDescription originale:

Titre original

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

Schematic Content: Altera Cyclone II FPGA Starter Board

Transféré par

Albert Ponic NinyehDroits d'auteur :

Formats disponibles

5 4 3 2 1

Altera Cyclone II FPGA Starter Board

D

SCHEMATIC CONTENT PAGE D

TOP COVER PAGE , TOP 01 ~ 03

AUDIO WM8731 04 ~ 04

DISPLAY VGA , 7SEGMENT ,LED 05 ~ 07

EP2C20 EP2C20 BANK1..BANK8 , POWER , CONFIG 08 ~ 12

INPUT CLOCK , PS2 , RS232 , KEY , SWITCH , CONNECT 13 ~ 17

MEMORY SRAM , DRAM , FLASH , SD CARD 18 ~ 19

POWER POWER 20 ~ 20

C

BLASTER USB BLASTER 21 ~ 21 C

B B

A A

Title

Altera Cyclone II Starter Board

Size Document Number Rev

B COVER PAGE 1.1A

Date: Tuesday, October 03, 2006 Sheet 1 of 21

5 4 3 2 1

5 4 3 2 1

DC USB LINE LINE MIC VGA RS232 PS2

7.5V BLASTER IN OUT IN OUTPUT KEYBORAD

D D

WM8731 4BIT RGB

GPIO_0

GPIO_1

FT245

M3128

C C

EP2C20

EPCS4

SD CARD

SDRAM SRAM FLASH

B B

EXT CLK

HEX3

HEX2

HEX1

HEX0

LED17

LED16

LED15

LED14

LED13

LED12

LED11

LED10

LED9

LED8

LED7

LED6

LED5

LED4

LED3

LED2

LED1

LED0

KEY3

KEY2

KEY1

KEY0

A A

SW9

SW8

SW7

SW6

SW5

SW4

SW3

SW2

SW1

SW0

Title

Altera Cyclone II Starter Board

Size Document Number Rev

B PLACEMENT 1.1A

Date: Tuesday, October 03, 2006 Sheet 2 of 21

5 4 3 2 1

5 4 3 2 1

EP2S35 EP2C20

AUDIO PAGE 4

AUD_BCLK AUD_ADCDAT

AUD_DACDAT AUD_BCLK AUD_ADCDAT AUD_ADCDAT PWR PAGE 20

AUD_ADCLRCK AUD_DACDAT AUD_ADCDAT

AUD_DACLRCK AUD_ADCLRCK AUD_BCLK 24MHZ

AUD_DACLRCK AUD_DACDAT AUD_BCLK 24MHZ

D I2C_SCLK I2C_SDAT AUD_ADCLRCK AUD_DACDAT DATA0 D

AUD_XCK I2C_SCLK I2C_SDAT AUD_DACLRCK AUD_ADCLRCK DATA0

AUD_XCK AUD_DACLRCK DCLK

I2C_SDAT DCLK ASDO

I2C_SCLK I2C_SDAT ASDO NCSO

AUD_XCK I2C_SCLK NCSO NCE

AUD_XCK NCE

NCONFIG

DISPLAY PAGE 5-6 HEX0_D[0..6] NCONFIG CONF_DONE

HEX1_D[0..6] HEX0_D[0..6] CONF_DONE NSTATUS USB BLASTER PAGE 21

HEX0_D[0..6] HEX2_D[0..6] HEX1_D[0..6] NSTATUS

HEX1_D[0..6] HEX0_D[0..6] HEX3_D[0..6] HEX2_D[0..6] TCK DATA0 24MHZ

HEX2_D[0..6] HEX1_D[0..6] HEX3_D[0..6] TCK TDI DATA0 24MHZ

HEX3_D[0..6] HEX2_D[0..6] VGA_R[0..3] TDI TDO DCLK

HEX3_D[0..6] VGA_G[0..3] VGA_R[0..3] TDO TMS DCLK ASDO

VGA_R[0..3] VGA_B[0..3] VGA_G[0..3] TMS ASDO NCSO

VGA_G[0..3] VGA_R[0..3] VGA_VSYNC VGA_B[0..3] LINK_D0 NCSO NCE

VGA_B[0..3] VGA_G[0..3] VGA_HSYNC VGA_VSYNC LINK_D0 LINK_D1 NCE

VGA_VSYNC VGA_B[0..3] VGA_HSYNC LINK_D1 LINK_D2 TDO NCONFIG

VGA_HSYNC VGA_VSYNC LED[0..17] LINK_D2 LINK_D3 TDO NCONFIG CONF_DONE

VGA_HSYNC LED[0..17] LINK_D3 CONF_DONE NSTATUS

LED[0..17] NSTATUS

LED[0..17] UART_RXD TCK

UART_TXD UART_RXD TCK TDI

C UART_TXD TDI C

TMS

27MHZ TMS

50MHZ 27MHZ LINK_D0

EXT_CLOCK 50MHZ LINK_D0 LINK_D1

INPUT IN/OUT EXT_CLOCK LINK_D3 LINK_D1 LINK_D2

PS2_DAT LINK_D3 LINK_D2

UART_TXD UART_RXD PS2_CLK PS2_DAT

UART_TXD UART_RXD PS2_CLK

PS2_CLK 27MHZ KEY[0..3]

PS2_DAT PS2_CLK 27MHZ 50MHZ SW[0..2] KEY[0..3]

PS2_DAT 50MHZ EXT_CLOCK SW[3..6] SW[0..2]

GPIO_B[0..35] EXT_CLOCK SW[7..9] SW[3..6]

GPIO_B[0..35] KEY[0..3] SW[7..9]

GPIO_B[36..71] KEY[0..3] SW[0..9] GPIO_B[0..71]

GPIO_B[36..71] SW[0..9] GPIO_B[0..71]

FLASH_D[0..7]

FLASH_RESET FLASH_D[0..7]

FLASH_WE FLASH_RESET

FLASH_CE FLASH_WE

MEMORY PAGE 18-19 FLASH_OE FLASH_CE

FLASH_A[0..21] FLASH_OE

FLASH_RESET FLASH_A[0..21]

B B

FLASH_WE FLASH_RESET DRAM_D[0..15]

FLASH_CE FLASH_WE DRAM_CLK DRAM_D[0..15]

FLASH_OE FLASH_CE DRAM_CKE DRAM_CLK

FLASH_A[0..21] FLASH_OE FLASH_D[0..7] DRAM_CS DRAM_CKE

FLASH_A[0..21] FLASH_D[0..7] DRAM_WE DRAM_CS

DRAM_CLK DRAM_CAS DRAM_WE

DRAM_CKE DRAM_CLK DRAM_RAS DRAM_CAS

DRAM_CS DRAM_CKE DRAM_LDQM DRAM_RAS

DRAM_WE DRAM_CS DRAM_UDQM DRAM_LDQM

DRAM_CAS DRAM_WE DRAM_BA0 DRAM_UDQM

DRAM_RAS DRAM_CAS DRAM_BA1 DRAM_BA0

DRAM_LDQM DRAM_RAS DRAM_A[0..11] DRAM_BA1

DRAM_UDQM DRAM_LDQM DRAM_A[0..11]

DRAM_BA0 DRAM_UDQM SRAM_D[0..15]

DRAM_BA1 DRAM_BA0 SRAM_WE SRAM_D[0..15]

DRAM_A[0..11] DRAM_BA1 DRAM_D[0..15] SRAM_CE SRAM_WE

DRAM_A[0..11] DRAM_D[0..15] SRAM_OE SRAM_CE

SRAM_WE SRAM_LB SRAM_OE

SRAM_CE SRAM_WE SRAM_UB SRAM_LB

SRAM_OE SRAM_CE SRAM_A[0..17] SRAM_UB

SRAM_LB SRAM_OE SRAM_A[0..17]

SRAM_UB SRAM_LB SD_DAT

SRAM_A[0..17] SRAM_UB SRAM_D[0..15] SD_CLK SD_DAT

A

SRAM_A[0..17] SRAM_D[0..15] SD_CMD SD_CLK A

SD_CLK SD_DAT3 SD_CMD

SD_CMD SD_CLK SD_DAT3

SD_DAT3 SD_CMD SD_DAT

SD_DAT3 SD_DAT

Title

Altera Cyclone II Starter Board

Size Document Number Rev

B TOP LEVEL 1.1A

Date: Tuesday, October 03, 2006 Sheet 3 of 21

5 4 3 2 1

5 4 3 2 1

J2 LINEIN

VCC33 VCC33 C1

R1 4.7K

GND

NCR

NCL

1U

L

R2 R3 C2

R4 4.7K

5

2

4

1

3

D D

2K 2K 1U

I2C_SCLK

I2C_SDAT R5 R6

4.7K 4.7K

I2C ADDRESS READ IS 0x34 AGND

I2C ADDRESS WRITE IS 0x35

AGND AGND

I2C_SDAT J1 MICIN

I2C_SCLK R7 330

GND

NCR

NCL

R

L

C3

28

27

26

25

24

23

22

U1 R8 680

5

2

4

1

3

1U

SDIN

SCLK

CSB

MODE

LLINEIN

RLINEIN

MICIN

C C

TC21

1 21 100U/6V

XTI/MCLK MBIAS

2 XTO VMID 20

3 19 C5 R9 AGND

A_VCC33 DCVDD AGND

4 WM8731 18

DGND AVDD A_VCC33

5 17 1000P 47K

DBVDD ROUT J3 LINEOUT

6 CLKOUT LOUT 16

7 BCLK HPGND 15

DACLRCK

ADCLRCK

GND

NCR

RHPOUT

NCL

DACDAT

ADCDAT

LHPOUT

AGND AGND

HPVDD

L

AGND

5

2

4

1

3

8

9

10

11

12

13

14

TC22

B B

100U/6V

AUD_XCK

A_VCC33

AUD_BCLK

AUD_DACDAT TC23 AGND

AUD_DACLRCK

AUD_ADCDAT 100U/6V

AUD_ADCLRCK

R10 R11

A_VCC33

47K 47K

BC1 BC2 BC3 BC4

AGND AGND

R12 0 0.1U 0.1U 0.1U 0.1U

A A

AGND

AGND Title

Altera Cyclone II Starter Board

Size Document Number Rev

A AUDIO 1.1A

Date: Tuesday, October 03, 2006 Sheet 4 of 21

5 4 3 2 1

5 4 3 2 1

RN1

5 4

6 3 VGA_R0

J4

7 2 VGA_R1

D D

1 R R 8 1 VGA_R2

6 2 G VGA_R3

11 1 3 B 2K

4 RN2

5 GND 1 8

6 RG 2 7

7 BG 3 6

8 GG 4 5

9

10 GND 1K

11

12

13 HS RN3

10 14 VS 5 4

15 5 15 6 3 VGA_G0

7 2 VGA_G1

8 1 VGA_G2

17

16

C VGA VGA_G3 C

G 2K

RN4

1 8

2 7

3 6

4 5

1K

RN5

5 4

6 3 VGA_B0

7 2 VGA_B1

8 1 VGA_B2

VGA_R[0..3] VGA_B3

B B

VGA_G[0..3] 2K

VGA_B[0..3] B RN6

VGA_HSYNC 1 8

VGA_VSYNC 2 7

3 6

4 5

1K

H R13 120 VGA_HSYNC

V R14 120 VGA_VSYNC

A A

Title

Altera Cyclone II Starter Board

Size Document Number Rev

A VGA 1.1A

Date: Tuesday, October 03, 2006 Sheet 5 of 21

5 4 3 2 1

5 4 3 2 1

HEX0_D0 1 8 A0

HEX0_D1 2 7 B0 HEX0_D[0..6]

HEX0_D2 3 6 C0 HEX1_D[0..6]

HEX0_D3 4 5 D0 HEX2_D[0..6]

HEX3_D[0..6]

RN7 1K

D D

HEX0_D4 1 8 E0

HEX0_D5 2 7 F0

HEX0_D6 3 6 G0 HEX0 HEX1

HEX1_D0 4 5 A1 10 A 10 A

RN8 1K A0 9 B A1 9 B

B0 VCC33 B1 VCC33

C0 8 C C1 8 C

HEX1_D1 1 8 B1 D0 D1

HEX1_D2 2 7 C1 5 D 1 5 D 1

HEX1_D3 3 6 D1

HEX1_D4 4 5 E1 4 E 6 4 E 6

RN9 1K E0 2 F E1 2 F

F0 F1

C G0 3 G G1 3 G C

HEX1_D5 1 8 F1

HEX1_D6 2 7 G1 7 DP 7 DP

HEX2_D0 3 6 A2

HEX2_D1 4 5 B2 7Segment Display 7Segment Display

RN10 1K

HEX2_D2 1 8 C2 HEX2 HEX3

HEX2_D3 2 7 D2 10 A 10 A

HEX2_D4 3 6 E2

HEX2_D5 4 5 F2 A2 9 B A3 9 B

B2 VCC33 B3 VCC33

RN11 1K C2 8 C C3 8 C

D2 D3

5 D 1 5 D 1

HEX2_D6 1 8 G2

B B

HEX3_D0 2 7 A3 4 E 6 4 E 6

HEX3_D1 3 6 B3

HEX3_D2 4 5 C3 E2 2 F E3 2 F

F2 F3

RN12 1K G2 3 G G3 3 G

7 DP 7 DP

HEX3_D3 1 8 D3

HEX3_D4 2 7 E3 7Segment Display 7Segment Display

HEX3_D5 3 6 F3

HEX3_D6 4 5 G3

RN13 1K

A A

Title

Altera Cyclone II Starter Board

Size Document Number Rev

A 7 SEGMENT 1.1A

Date: Tuesday, October 03, 2006 Sheet 6 of 21

5 4 3 2 1

5 4 3 2 1

LEDR0 LEDR

LED[0..17]

RN15

LEDR1 LEDR

LED0 1 8

LED1 2 7

LED2 3 6 LEDR2 LEDR

D D

LED3 4 5

LEDR3 LEDR

330

LEDR4 LEDR

RN16

LEDR5 LEDR

LED4 1 8

LED5 2 7

LED6 3 6 LEDR6 LEDR

LED7 4 5

LEDR7 LEDR

330

C C

LEDR8 LEDR

RN17

LED8 1 8

LED9 2 7 LEDR9 LEDR

3 6

4 5

330 LEDG0 LEDG

RN18

LEDG1 LEDG

LED10 1 8

LED11 2 7

B B

LED12 3 6 LEDG2 LEDG

LED13 4 5

LEDG3 LEDG

330

LEDG4 LEDG

RN19

LEDG5 LEDG

LED14 1 8

LED15 2 7

LED16 3 6 LEDG6 LEDG

LED17 4 5

A LEDG7 LEDG A

330

Title

Altera Cyclone II Starter Board

Size Document Number Rev

A LED 1.1A

Date: Tuesday, October 03, 2006 Sheet 7 of 21

5 4 3 2 1

5 4 3 2 1

D D

HEX0_D[0..6]

DRAM_D[0..15] HEX1_D[0..6]

DRAM_A[0..11] HEX2_D[0..6]

SW[7..9] HEX3_D[0..6]

U2A U2B

DRAM_A3 Y4 HEX0_D0 J2

DRAM_A2 LVDS0n HEX0_D1 LVDS16n

Y3 LVDS0p J1 LVDS16p

DRAM_A0 W4 HEX0_D2 H2

DRAM_A10 LVDS1n HEX0_D3 LVDS17n

W3 LVDS1p H1 LVDS17p

DRAM_D7 Y2 HEX0_D4 F2

DRAM_D6 LVDS2n HEX0_D5 LVDS18n

Y1 LVDS2p F1 LVDS18p

DRAM_D5 W2 HEX0_D6 E2

DRAM_D4 LVDS3n HEX1_D0 LVDS19n

W1 LVDS3p E1 LVDS19p

DRAM_CS T6 HEX1_D1 H6

DRAM_RAS LVDS4n HEX1_D2 LVDS20n

C T5 LVDS4p H5 LVDS20p

C

DRAM_D3 V2 HEX1_D3 H4

DRAM_D2 LVDS5n HEX1_D4 LVDS21n

V1 LVDS5p G3 LVDS21p

DRAM_A4 R6 HEX1_D5 D2

DRAM_A5 LVDS6n HEX1_D6 LVDS22n

R5 LVDS6p D1 LVDS22p

DRAM_D1 U2 HEX2_D0 G5

DRAM_D0 LVDS7n HEX2_D1 LVDS23n

U1 LVDS7p G6 LVDS23p

DRAM_D15 T2

BANK1 HEX2_D2 C2

BANK2

DRAM_D14 LVDS8n HEX2_D3 LVDS24n

T1 LVDS8p C1 LVDS24p

DRAM_D13 R2 HEX2_D5 E4

DRAM_D12 LVDS9n HEX2_D4 LVDS25n

R1 LVDS9p E3 LVDS25p

DRAM_A6 P6 N6 DRAM_A11 HEX3_D6 D4 F3 HEX3_D5

DRAM_A7 LVDS10n IO1_0 DRAM_CAS HEX2_D6 LVDS26n IO2_0 HEX3_D3

P5 LVDS10p IO1_1 T3 D3 LVDS26p IO2_1 J4

DRAM_LDQM R7 W5 DRAM_A1 L8 HEX3_D4

DRAM_WE LVDS11n IO1_2 IO2_2

R8 LVDS11p

DRAM_A9 N4 P3 DRAM_A8 F4 HEX3_D0

DRAM_CKE LVDS12n VREFB1N0 DRAM_BA0 VREFB2N0

B

N3 LVDS12p VREFB1N1 U3 VREFB2N1 H3 B

DRAM_D11 P2

DRAM_D10 LVDS13n SW7 SW9

P1 LVDS13p CLK3/LVDSCLK1n M2 CLK1/LVDSCLK0n L2

DRAM_D9 N2 M1 SW8 L1 50MHZ

DRAM_D8 LVDS14n CLK2/LVDSCLK1p CLK0/LVDSCLK0p

N1 LVDS14p

M6 V4 DRAM_BA1 D6 HEX3_D2

DRAM_UDQM LVDS15n PLL1_OUTn DRAM_CLK PLL3_OUTn HEX3_D1

M5 LVDS15p PLL1_OUTp U4 PLL3_OUTp D5

CYCLONE II EP2C20 CYCLONE II EP2C20

A A

Title

Altera Cyclone II Starter Board

Size Document Number Rev

A EP2C20 BANK1 AND BANK 2 1.1A

Date: Tuesday, October 03, 2006 Sheet 8 of 21

5 4 3 2 1

5 4 3 2 1

VGA_R[0..3]

D D

VGA_G[0..3] GPIO_B[0..15]

VGA_B[0..3] GPIO_B[36..51]

U2C U2D

I2C_SDAT B3 H11 GPIO_B1 B13 B20 GPIO_B15

I2C_SCLK LVDS27n/DEV_CLRn LVDS42n GPIO_B0 LVDS45n LVDS60n GPIO_B14

A3 LVDS27p LVDS42p G11 A13 LVDS45p LVDS60p A20

AUD_XCK B4 E11 GPIO_B3 B14 C18 GPIO_B51

AUD_BCLK LVDS28n LVDS43n VGA_B1 GPIO_B2 LVDS46n LVDS61n GPIO_B50

A4 LVDS28p LVDS43p D11 A14 LVDS46p LVDS61p C17

AUD_DACDAT B5 B11 VGA_VSYNC GPIO_B44 F12

AUD_DACLRCK LVDS29n LVDS44n VGA_HSYNC UART_TXD LVDS47n

A5 LVDS29p LVDS44p A11 G12 LVDS47p

AUD_ADCDAT B6

AUD_ADCLRCK LVDS30n GPIO_B5

A6 LVDS30p B15 LVDS48n

G7 GPIO_B4 A15

LVDS31n GPIO_B7 LVDS48p

H7 LVDS31p B16 LVDS49n

GPIO_B6 A16

UART_RXD LVDS49p

F8 LVDS32n F14 LVDS50n

C G8 GPIO_B45 F13 C

LINK_D1 LVDS32p GPIO_B40 LVDS50p

D8 LVDS33n E14 LVDS51n

VGA_R1 C9 GPIO_B47 D14

LVDS33p GPIO_B9 LVDS51p

F9 LVDS34n B17 LVDS52n

LINK_D0 GPIO_B8

VGA_R3

E8

B7

LVDS34p BANK3 GPIO_B39

A17

G15

LVDS52p BANK4

VGA_R2 LVDS35n GPIO_B42 LVDS53n

A7 LVDS35p F15 LVDS53p

VGA_G0 B8 GPIO_B48 D15

VGA_G3 LVDS36n GPIO_B46 LVDS54n

A8 LVDS36p C14 LVDS54p

E9 D7 LINK_D3 GPIO_B38 H14

VGA_R0 LVDS37n IO3_0 PS2_DAT LVDS55n GPIO_B36

D9 LVDS37p IO3_1 E7 J14 LVDS55p IO4_0 H12

H10 H8 H13 GPIO_B37

LVDS38n IO3_2 GPIO_B49 IO4_1

H9 LVDS38p D16 LVDS56n

VGA_G2 B9 C10 VGA_G1 GPIO_B41 E15 C16

VGA_B0 LVDS39n VREFB3N0 LINK_D2 GPIO_B43 LVDS56p VREFB4N0

A9 LVDS39p VREFB3N1 C7 G16 LVDS57n VREFB4N1 C13

PS2_CLK H15

27MHZ GPIO_B11 LVDS57p 24MHZ

F11 LVDS40n CLK10/LVDSCLK5n D12 B18 LVDS58n CLK8/LVDSCLK4n B12

F10 E12 GPIO_B10 A18 A12

B

VGA_B3 LVDS40p CLK11/LVDSCLK5p GPIO_B13 LVDS58p CLK9/LVDSCLK4p B

B10 LVDS41n B19 LVDS59n

VGA_B2 A10 GPIO_B12 A19

LVDS41p LVDS59p

CYCLONE II EP2C20 CYCLONE II EP2C20

A A

Title

Altera Cyclone II Starter Board

Size Document Number Rev

A EP2C35 BANK3 AND BANK 4 1.1A

Date: Tuesday, October 03, 2006 Sheet 9 of 21

5 4 3 2 1

5 4 3 2 1

SW[0..2]

GPIO_B[16..35] LED[0..17]

D D

GPIO_B[52..71] KEY[0..3]

U2E U2F

GPIO_B54 D19 L19 GPIO_B34 M19

GPIO_B55 LVDS62n LVDS77n GPIO_B35 LVDS78n

D20 LVDS62p LVDS77p L18 M18 LVDS78p

GPIO_B52 C19 GPIO_B67 N21

GPIO_B53 LVDS63n GPIO_B66 LVDS79n

C20 LVDS63p N22 LVDS79p

GPIO_B16 C21 GPIO_B68 P15

GPIO_B17 LVDS64n GPIO_B69 LVDS80n

C22 LVDS64p N15 LVDS80p

GPIO_B56 E20 KEY1 R21

GPIO_B57 LVDS65n KEY0 LVDS81n

F20 LVDS65p R22 LVDS81p

GPIO_B62 G17 KEY3 T21

GPIO_B61 LVDS66n KEY2 LVDS82n

G18 LVDS66p T22 LVDS82p

GPIO_B18 D21 GPIO_B70 P17

GPIO_B19 LVDS67n GPIO_B71 LVDS83n

D22 LVDS67p P18 LVDS83p

C GPIO_B20 E21 LED8 R18 C

GPIO_B21 LVDS68n LED1 LVDS84n

E22 LVDS68p R19 LVDS84p

GPIO_B65 H18 LED11 U21

GPIO_B63 LVDS69n LED10 LVDS85n

GPIO_B22

H17 LVDS69p LED13

U22 LVDS85p BANK6

GPIO_B23

F21

F22

LVDS70n BANK5 LED12

V21

V22

LVDS86n

GPIO_B24 LVDS70p LED17 LVDS86p

G21 LVDS71n Y21 LVDS87n

GPIO_B25 G22 LED16 Y22

LVDS71p LVDS87p

J17 LVDS72n

H16 LED15 W21 R17 LED9

LVDS72p GPIO_B64 LED14 LVDS88n IO6_0 LED6

IO5_0 J15 W22 LVDS88p IO6_1 Y18

GPIO_B30 J19 LED2 U19

GPIO_B32 LVDS73n GPIO_B60 SD_CLK LVDS89n LED0

J18 LVDS73p VREFB5N0 G20 V20 LVDS89p VREFB6N0 R20

GPIO_B31 J20 K20 GPIO_B33 LED3 Y19 U20 SD_DAT3

LVDS74n VREFB5N1 SD_CMD LVDS90n VREFB6N1

H19 LVDS74p Y20 LVDS90p

GPIO_B26 J21 L21 SW1 LED5 V19 M21 EXT_CLOCK

GPIO_B27 LVDS75n CLK5/LVDSCLK2n SW0 SD_DAT LVDS91n/INIT_DONE CLK7/LVDSCLK3n SW2

J22 LVDS75p CLK4/LVDSCLK2p L22 W20 LVDS91p/nCEO CLK6/LVDSCLK3p M22

GPIO_B28 K21

B

GPIO_B29 LVDS76n GPIO_B59 LED7 B

K22 LVDS76p PLL2_OUTn E18 PLL4_OUTn U18

E19 GPIO_B58 T18 LED4

PLL2_OUTp PLL4_OUTp

CYCLONE II EP2C20 CYCLONE II EP2C20

A A

Title

Altera Cyclone II Starter Board

Size Document Number Rev

A EP2C20 BANK5 AND BANK 6 1.1A

Date: Tuesday, October 03, 2006 Sheet 10 of 21

5 4 3 2 1

5 4 3 2 1

FLASH_A[0..21]

D D

FLASH_D[0..7] SRAM_D[0..15]

SW[3..6] SRAM_A[0..17]

U2G U2H

FLASH_A17 AA20 AA13 FLASH_A13 SRAM_A6 AA11 AA5 SRAM_A4

FLASH_A0 LVDS92n LVDS107n FLASH_A14 SRAM_A7 LVDS109n LVDS124n SRAM_CE

AB20 LVDS92p LVDS107p AB13 AB11 LVDS109p LVDS124p AB5

FLASH_D7 AA19 AA12 FLASH_A15 SRAM_WE AA10 Y6 SRAM_A16

FLASH_D6 LVDS93n LVDS108n FLASH_A16 SRAM_A5 LVDS110n LVDS125n SRAM_A17

AB19 LVDS93p LVDS108p AB12 AB10 LVDS110p LVDS125p Y5

W16 SRAM_A8 V11 AA4 SRAM_A2

LVDS94n SRAM_A9 LVDS111n LVDS126n SRAM_A3

Y17 LVDS94p W11 LVDS111p LVDS126p AB4

FLASH_A6 V15 AA3 SRAM_A0

FLASH_A5 LVDS95n SRAM_A10 LVDS127n SRAM_A1

U15 LVDS95p R11 LVDS112n LVDS127p AB3

SRAM_A11 T11

SRAM_D6 LVDS112p

T16 LVDS96n AA9 LVDS113n

R16 SRAM_D7 AB9

FLASH_D5 LVDS96p SRAM_D4 LVDS113p

AA18 LVDS97n AA8 LVDS114n

C FLASH_D4 AB18 SRAM_D5 AB8 C

FLASH_A3 LVDS97p SRAM_D12 LVDS114p

R15 LVDS98n R9 LVDS115n

FLASH_A8 R14 SRAM_A14 R10

FLASH_A7 LVDS98p SRAM_A13 LVDS115p

W15 LVDS99n U10 LVDS116n

FLASH_WE SRAM_D11

FLASH_A4

Y14 LVDS99p SRAM_D9

U9 LVDS116p BANK8

FLASH_A18

T15

U14

LVDS100n BANK7 SRAM_D8

W9

Y9

LVDS117n

FLASH_D3 LVDS100p SRAM_D2 LVDS117p

AA17 LVDS101n AA7 LVDS118n

FLASH_D2 AB17 SRAM_D3 AB7

FLASH_A19 LVDS101p FLASH_A10 SRAM_D10 LVDS118p

V14 LVDS102n IO7_0 R12 V9 LVDS119n

FLASH_RESET W14 R13 FLASH_A21 SRAM_D13 W8

FLASH_D1 LVDS102p IO7_1 SRAM_UB LVDS119p SRAM_D15

AA16 LVDS103n W7 LVDS120n IO8_0 U8

FLASH_D0 AB16 Y16 FLASH_A2 SRAM_D14 V8

LVDS103p VREFB7N0 FLASH_A9 LVDS120p SRAM_A12

VREFB7N1 Y13 VREFB8N0 Y10

FLASH_OE AA15 SRAM_D0 AA6 Y7 SRAM_LB

FLASH_CE LVDS104n SW3 SRAM_D1 LVDS121n VREFB8N1

AB15 LVDS104p CLK12/LVDSCLK6n V12 AB6 LVDS121p

FLASH_A1 AA14 W12 SW4 P8 U12 SW5

FLASH_A12 LVDS105n CLK13/LVDSCLK6p LVDS122n CLK14/LVDSCLK7n SW6

B

AB14 LVDS105p P9 LVDS122p CLK15/LVDSCLK7p U11 B

FLASH_A20 U13 SRAM_A15 T7

FLASH_A11 LVDS106n SRAM_OE LVDS123n

T12 LVDS106p T8 LVDS123p

CYCLONE II EP2C20 CYCLONE II EP2C20

A A

Title

Altera Cyclone II Starter Board

Size Document Number Rev

A EP2C20 BANK7 AND BANK 8 1.1A

Date: Tuesday, October 03, 2006 Sheet 11 of 21

5 4 3 2 1

5 4 3 2 1

VCCIO VCCINT

VCCIO

D D

AA22

AB21

W17

M20

M14

AA1

G14

G19

AB2

C11

D17

C12

N14

E10

E13

A21

B22

P16

Y12

V13

Y11

V10

K14

P10

P11

P12

P13

T19

T14

L20

L14

J16

J10

J11

J12

J13

W6

M3

M9

G9

C6

N9

P7

B1

A2

K9

T4

T9

L3

L9

J7

U2I BC13 BC14 BC15 BC16 BC17 BC18

VCCIO1

VCCIO1

VCCIO1

VCCIO1

VCCIO2

VCCIO2

VCCIO2

VCCIO3

VCCIO3

VCCIO3

VCCIO3

VCCIO3

VCCIO4

VCCIO4

VCCIO4

VCCIO4

VCCIO4

VCCIO5

VCCIO5

VCCIO5

VCCIO5

VCCIO6

VCCIO6

VCCIO6

VCCIO6

VCCIO7

VCCIO7

VCCIO7

VCCIO7

VCCIO7

VCCIO8

VCCIO8

VCCIO8

VCCIO8

VCCIO8

VCCINT

VCCINT

VCCINT

VCCINT

VCCINT

VCCINT

VCCINT

VCCINT

VCCINT

VCCINT

VCCINT

VCCINT

VCCINT

VCCINT

VCCINT

VCCINT

0.1U 0.1U 0.1U 0.1U 0.1U 0.1U

G1 VCCINT

NC0

G2 NC1

H21 U6 VCCIO

NC2 VCCD_PLL1

H22 NC3 VCCD_PLL2 F17

J3 NC4 VCCD_PLL3 E5

J5 NC5 VCCD_PLL4 U17

J6 BC19 BC20 BC21 BC22 BC23 BC24 BC25 BC26

NC6

J8 NC7 VCCA_PLL1 U7

J9 F16 0.1U 0.1U 0.1U 0.1U 0.1U 0.1U 0.1U 0.1U

NC8 VCCA_PLL2

K8 NC9 VCCA_PLL3 E6

K15 NC10 VCCA_PLL4 U16

K17 NC11

K18 NC12

L7 VCC33

NC13

L15 NC14

L16 NC15

C L17

M7

NC16 Power and GND BC27 BC28 BC29 BC30 BC31 BC32

C

NC17

M8 NC18 GNDA_PLL1 V7

M15 E16 0.1U 0.1U 0.1U 0.1U 0.1U 0.1U

NC19 GNDA_PLL2

M16 NC20 GNDA_PLL3 F7

N5 NC21 GNDA_PLL4 V16

N8 NC22

P4 NC23 GND_PLL1 V5

P14 U5 VCC33

NC24 GND_PLL1

P19 NC25 GND_PLL2 E17

P20 NC26 GND_PLL2 F18

P21 NC27 GND_PLL3 F5

P22 F6 BC33 BC34 BC35 BC36 BC37 BC38

NC28 GND_PLL3

R4 NC29 GND_PLL4 V18

W18 T17 0.1U 0.1U 0.1U 0.1U 0.1U 0.1U

NC30 GND_PLL4

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

CYCLONE II EP2C20 VCCINT

A1

A22

B2

B21

C5

C8

C15

D10

D13

D18

F19

G4

G10

G13

H20

K3

K7

K10

K11

K12

K13

K16

K19

L10

L11

L12

L13

M4

M10

M11

M12

M13

N7

N10

N11

N12

N13

N16

N19

R3

T10

T13

T20

V3

V6

V17

W10

W13

W19

Y8

Y15

AA2

AA21

AB1

AB22

BC5 BC6 BC7 BC8 BC9 BC10 BC11 BC12

B B

0.1U 0.1U 0.1U 0.1U 0.1U 0.1U 0.1U 0.1U

U2J

VCCINT VCCIO

ASDO C4 C15 C16 C17 C18 C19 C20 C21 C22

NCSO ASDO

C3 nCSO

TDI K5 1U 1U 1U 1U 1U 1U 1U 1U

TCK TDI

K2 TCK

TMS K6

TDO TMS

L5 TDO

DCLK L6

DATA0 DCLK

NCONFIG

K4

L4

DATA0 Crotrol Signal

NCE nCONFIG

K1 nCE

CONF_DONE N18

NSTATUS CONF_DONE

N20 nSTATUS

M17 MSEL0

N17 MSEL1

A A

CYCLONE II EP2C20 Title

Altera Cyclone II Starter Board

Size Document Number Rev

B EP2C20 POWER AND CONFIG 1.1A

Date: Tuesday, October 03, 2006 Sheet 12 of 21

5 4 3 2 1

5 4 3 2 1

D D

VCC33

BC41 Y1

1 EN VCC 4

0.1U

2 3 EXT_CLOCK

GND OUT

50MHZ

50MHZ

C C

J5

VCC33

EXT CLOCK

R15

BC45 Y2

1 4 1K

0.1U EN VCC

2 GND OUT 3

27MHZ

B B

27MHZ

A A

Title

Altera Cyclone II Starter Board

Size Document Number Rev

A CLOCK 1.1A

Date: Tuesday, October 03, 2006 Sheet 13 of 21

5 4 3 2 1

5 4 3 2 1

RN20

UART_RXD 1 8 RXD

D D

2 7

3 6

RXD LEDR 4 5

10

11

TXD LEDG U4 J6

330

VCC33 13 R1IN R1OUT 12 1

8 R2IN R2OUT 9 6

UART_TXD 11 14 2

T1IN T1OUT

10 T2IN T2OUT 7 7

C6 3

1 C+ 8

1U 3 4

C1-

4 C2+ VCC 16 VCC33 9

C7 5 15 5

C2- GND

2 V+

1U 6 RS232

V-

C MAX232 C

C8 C9

1U 1U VCC33

BC42

0.1U

VCC5 VCC5

R16 R17

2K 2K

PS2_DAT R18 120

B B

PS2_CLK R19 120

J7

VCC5 TOP

DAT1

2 8 6

3

GND3

D1 D2 VCC5

BC46 CLK 6 5 3

BAT54S BAT54S

8

0.1U 2 1

1

VCC33 VCC33 PS2

9

10

11

A A

Title

Altera Cyclone II Starter Board

Size Document Number Rev

A PS2 AND RS232 1.1A

Date: Tuesday, October 03, 2006 Sheet 14 of 21

5 4 3 2 1

5 4 3 2 1

KEY[0..3]

D D

SW[0..9]

RN21

1 8 VCC33

2 7

3 6

4 5

100K U5

10 GND RN22

KEYIN0 9 11 8 1 KEY0

KEYIN1 A8 B8 KEY1

8 A7 B7 12 7 2

KEYIN2 7 13 6 3 KEY2

KEYIN3 A6 B6 KEY3

C 6 A5 B5 14 5 4 C

5 A4 B4 15

KEY0 KEY1 KEY2 KEY3 4 16

C10 C11 C12 C13 A3 B3 120

4 3 4 3 4 3 4 3 3 A2 B2 17

2 A1 B1 18

1 2 1 2 1 2 1 2 1U 1U 1U 1U

OE 19

PBSW PBSW PBSW PBSW VCC33 1 20

DIR VCC VCC33

74HC245

SW0 SW1 SW2 SW3 SW4 SW5 SW6 SW7

4 GND 4 GND 4 GND 4 GND 4 GND 4 GND 4 GND 4 GND

1 VCC33 1 VCC33 1 VCC33 1 VCC33 1 VCC33 1 VCC33 1 VCC33 1 VCC33

2 SW0 2 SW1 2 SW2 2 SW3 2 SW4 2 SW5 2 SW6 2 SW7

3 GND 3 GND 3 GND 3 GND 3 GND 3 GND 3 GND 3 GND

B B

5 GND 5 GND 5 GND 5 GND 5 GND 5 GND 5 GND 5 GND

DPDT SW DPDT SW DPDT SW DPDT SW DPDT SW DPDT SW DPDT SW DPDT SW

VCC33

SW8 SW9

4 GND 4 GND

1 VCC33 1 VCC33

2 SW8 2 SW9 BC43 BC44

3 GND 3 GND

5 GND 5 GND 0.1U 0.1U

DPDT SW DPDT SW

A A

Title

Altera Cyclone II Starter Board

Size Document Number Rev

A KEY AND SWITCH 1.1A

Date: Tuesday, October 03, 2006 Sheet 15 of 21

5 4 3 2 1

5 4 3 2 1

GPIO_B[0..35]

D D

RN23 RN24 RN25

GPIO_B0 1 8 IO_A0 GPIO_B4 1 8 IO_A4 GPIO_B8 1 8 IO_A8

GPIO_B1 2 7 IO_A1 GPIO_B5 2 7 IO_A5 GPIO_B9 2 7 IO_A9

GPIO_B2 3 6 IO_A2 GPIO_B6 3 6 IO_A6 GPIO_B10 3 6 IO_A10

GPIO_B3 4 5 IO_A3 GPIO_B7 4 5 IO_A7 GPIO_B11 4 5 IO_A11

47 47 47

RN26 RN27 RN28

GPIO_B12 1 8 IO_A12 GPIO_B16 1 8 IO_A16 GPIO_B20 1 8 IO_A20

GPIO_B13 2 7 IO_A13 GPIO_B17 2 7 IO_A17 GPIO_B21 2 7 IO_A21

GPIO_B14 3 6 IO_A14 GPIO_B18 3 6 IO_A18 GPIO_B22 3 6 IO_A22

GPIO_B15 4 5 IO_A15 GPIO_B19 4 5 IO_A19 GPIO_B23 4 5 IO_A23

C C

47 47 47

RN29 RN30 RN31

GPIO_B24 1 8 IO_A24 GPIO_B28 1 8 IO_A28 GPIO_B32 1 8 IO_A32

GPIO_B25 2 7 IO_A25 GPIO_B29 2 7 IO_A29 GPIO_B33 2 7 IO_A33

GPIO_B26 3 6 IO_A26 GPIO_B30 3 6 IO_A30 GPIO_B34 3 6 IO_A34

GPIO_B27 4 5 IO_A27 GPIO_B31 4 5 IO_A31 GPIO_B35 4 5 IO_A35

47 47 47

(GPIO 0)

JP1

IO_A0 IO_A1

IO_A2 1 2 IO_A3

B

IO_A4 3 4 IO_A5 B

IO_A6 5 6 IO_A7

IO_A8 7 8 IO_A9

9 10

VCC5 11 12

IO_A10 IO_A11

IO_A12 13 14 IO_A13

IO_A14 15 16 IO_A15

IO_A16 17 18 IO_A17

IO_A18 19 20 IO_A19

IO_A20 21 22 IO_A21

IO_A22 23 24 IO_A23

IO_A24 25 26 IO_A25

27 28

VCC33 29 30

IO_A26 IO_A27

IO_A28 31 32 IO_A29

IO_A30 33 34 IO_A31

IO_A32 35 36 IO_A33

IO_A34 37 38 IO_A35

A A

39 40

BOX Header 2X20M Title

Altera Cyclone II Starter Board

Size Document Number Rev

A CONNECT A 1.1A

Date: Tuesday, October 03, 2006 Sheet 16 of 21

5 4 3 2 1

5 4 3 2 1

GPIO_B[36..71]

D RN32 RN33 RN34 D

GPIO_B36 1 8 IO_B0 GPIO_B40 1 8 IO_B4 GPIO_B44 1 8 IO_B8

GPIO_B37 2 7 IO_B1 GPIO_B41 2 7 IO_B5 GPIO_B45 2 7 IO_B9

GPIO_B38 3 6 IO_B2 GPIO_B42 3 6 IO_B6 GPIO_B46 3 6 IO_B10

GPIO_B39 4 5 IO_B3 GPIO_B43 4 5 IO_B7 GPIO_B47 4 5 IO_B11

47 47 47

RN35 RN36 RN37

GPIO_B48 1 8 IO_B12 GPIO_B52 1 8 IO_B16 GPIO_B56 1 8 IO_B20

GPIO_B49 2 7 IO_B13 GPIO_B53 2 7 IO_B17 GPIO_B57 2 7 IO_B21

GPIO_B50 3 6 IO_B14 GPIO_B54 3 6 IO_B18 GPIO_B58 3 6 IO_B22

GPIO_B51 4 5 IO_B15 GPIO_B55 4 5 IO_B19 GPIO_B59 4 5 IO_B23

47 47 47

RN38 RN39 RN40

C GPIO_B60 1 8 IO_B24 GPIO_B64 1 8 IO_B28 GPIO_B68 1 8 IO_B32 C

GPIO_B61 2 7 IO_B25 GPIO_B65 2 7 IO_B29 GPIO_B69 2 7 IO_B33

GPIO_B62 3 6 IO_B26 GPIO_B66 3 6 IO_B30 GPIO_B70 3 6 IO_B34

GPIO_B63 4 5 IO_B27 GPIO_B67 4 5 IO_B31 GPIO_B71 4 5 IO_B35

47 47 47

(GPIO 1)

JP2

IO_B0 IO_B1

IO_B2 1 2 IO_B3

IO_B4 3 4 IO_B5

IO_B6 5 6 IO_B7

IO_B8 7 8 IO_B9

B 9 10 B

VCC5 11 12

IO_B10 IO_B11

IO_B12 13 14 IO_B13

IO_B14 15 16 IO_B15

IO_B16 17 18 IO_B17

IO_B18 19 20 IO_B19

IO_B20 21 22 IO_B21

IO_B22 23 24 IO_B23

IO_B24 25 26 IO_B25

27 28

VCC33 29 30

IO_B26 IO_B27

IO_B28 31 32 IO_B29

IO_B30 33 34 IO_B31

IO_B32 35 36 IO_B33

IO_B34 37 38 IO_B35

39 40

BOX Header 2X20M

A A

Title

Altera Cyclone II Starter Board

Size Document Number Rev

A CONNECT B 1.1A

Date: Tuesday, October 03, 2006 Sheet 17 of 21

5 4 3 2 1

5 4 3 2 1

R_VCC33 R_VCC33

D D

DRAM_D[0..15] SRAM_D[0..15]

DRAM_A[0..11] SRAM_A[0..17]

14

27

43

49

11

33

U7

3

9

U6

SRAM_A0 1

VDD

VDD

VDD

VDDQ

VDDQ

VDDQ

VDDQ

VCC

VCC

SRAM_A1 A0

2 A1

DRAM_A0 23 2 DRAM_D0 SRAM_A2 3

DRAM_A1 A0 D0 DRAM_D1 SRAM_A3 A2

24 A1 D1 4 4 A3

DRAM_A2 25 5 DRAM_D2 SRAM_A4 5 7 SRAM_D0

DRAM_A3 A2 D2 DRAM_D3 SRAM_A5 A4 D0 SRAM_D1

26 A3 D3 7 18 A5 D1 8

DRAM_A4 29 8 DRAM_D4 SRAM_A6 19 9 SRAM_D2

DRAM_A5 A4 D4 DRAM_D5 SRAM_A7 A6 D2 SRAM_D3

30 A5 D5 10 20 A7 D3 10

DRAM_A6 31 11 DRAM_D6 SRAM_A8 21 13 SRAM_D4

DRAM_A7 A6 D6 DRAM_D7 SRAM_A9 A8 D4 SRAM_D5

32 A7 D7 13 22 A9 D5 14

DRAM_A8 33 42 DRAM_D8 SRAM_A10 23 15 SRAM_D6

DRAM_A9 A8 D8 DRAM_D9 SRAM_A11 A10 D6 SRAM_D7

C 34 A9 D9 44 24 A11 D7 16 C

DRAM_A10 22 45 DRAM_D10 SRAM_A12 25 29 SRAM_D8

DRAM_A11 A10 D10 DRAM_D11 SRAM_A13 A12 D8 SRAM_D9

35 A11 D11 47 26 A13 D9 30

36 48 DRAM_D12 SRAM_A14 27 31 SRAM_D10

DRAM_CLK A12 D12 DRAM_D13 SRAM_A15 A14 D10 SRAM_D11

38 CLK D13 50 42 A15 D11 32

DRAM_CKE 37 51 DRAM_D14 SRAM_A16 43 35 SRAM_D12

DRAM_LDQM CKE D14 DRAM_D15 SRAM_A17 A16 D12 SRAM_D13

15 LDQM D15 53 44 A17 D13 36

DRAM_UDQM 39 28 37 SRAM_D14

UDQM A18 D14 SRAM_D15

SRAM 256Kx16 D15 38

DRAM_WE 16 SDRAM 1Mx16x4 SRAM_CE 6

DRAM_CAS nWE SRAM_OE nCE

17 nCAS 41 nOE

DRAM_RAS 18 SRAM_WE 17

DRAM_CS nRAS SRAM_LB nWE

19 39

GND

GND

DRAM_BA0 nCS SRAM_UB nLB

20 BA0 40 nUB

DRAM_BA1 21 40

BA1 NC

VSSQ

VSSQ

VSSQ

VSSQ

VSS

VSS

VSS

12

34

B B

28

41

54

6

12

46

52

SRAM_CE R20 4.7K

R_VCC33

DRAM_CS R21 4.7K

R_VCC33

BC47 BC48 BC49 BC50 BC51 BC52 BC53 BC54

A A

0.1U 0.1U 0.1U 0.1U 0.1U 0.1U 0.1U 0.1U

Title

Altera Cyclone II Starter Board

Size Document Number Rev

A SDRAM AND SRAM 1.1A

Date: Tuesday, October 03, 2006 Sheet 18 of 21

5 4 3 2 1

5 4 3 2 1

D D

FLASH_D[0..7]

FLASH_A[0..21]

U9

U8 FLASH_A0 45

FLASH_A1 DQ15/A-1

25 A0 VCC 37 F_VCC33

9 DAT2 FLASH_A2 24

SD_DAT3 FLASH_A3 A1

1 DAT3 23

SD_CMD FLASH_A4 A2 FLASH_D0

2 CMD 22 29

R22 4.7K FLASH_A5 A3 DQ0 FLASH_D1

C

F_VCC33 3 VSS 21 31 C

F_VCC33 FLASH_A6 A4 DQ1 FLASH_D2

4 VCC 20 33

SD_CLK FLASH_A7 A5 DQ2 FLASH_D3

5 CLK 19 35

FLASH_A8 A6 DQ3 FLASH_D4

6 VSS 18 38

SD_DAT FLASH_A9 A7 DQ4 FLASH_D5

7 DAT0 8 40

R23 4.7K FLASH_A10 A8 DQ5 FLASH_D6

F_VCC33 8 DAT1 7 42

FLASH_A11 A9 DQ6 FLASH_D7

6 A10 DQ7 44

10 SW0 FLASH_A12 5 30

FLASH_A13 A11 DQ8

11 SW1 4 32

FLASH_A14 A12 DQ9

3 A13 DQ10 34

FLASH_A15 2 36

SD FLASH_A16 A14 DQ11

1 39

12

13

14

15

FLASH_A17 A15 DQ12

48 A16 DQ13 41

FLASH_A18 17 43

FLASH_A19 A17 DQ14

16 A18

FLASH_A20 9

F_VCC33 FLASH_A21 A19

10 A20

B

13 A21FLASH 4Mx8 B

FLASH_WE 11

FLASH_RESET WE#

12 RESET#

BC55 BC56 BC57 14

R24 4.7K WP#ACC

F_VCC33 15 RY/BY#

0.1U 0.1U 0.1U FLASH_CE 26

FLASH_OE CE#

28 OE# VSS 27

47 BYTE# VSS 46

A A

Title

Altera Cyclone II Starter Board

Size Document Number Rev

A FLASH AND SD 1.1A

Date: Tuesday, October 03, 2006 Sheet 19 of 21

5 4 3 2 1

5 4 3 2 1

D3

SW11

1

D4 5 SS14 5V0

6 VCC5

VCC5

J8 SS14 4 U10 D5

1 D6 2 1 3

INPUT OUTPUT

2 USB5V 3

D SS14 D

3

GND

SS14 USB5V POWER SW

DC_7.5V D7

TC1 TC2 BC59 LM7805-0.8A BC60 TC3 TC4

4

SS14 BC58 TC5 TC6 100U/16V 100U/16V 0.1U 0.1U 100U/16V 100U/16V

D8

0.1U 100U/16V 100U/16V U18 D11

1 INPUT OUTPUT 3

SS14

SS14

GND

LM7805-0.8A

4

3V3

VCC33

VCC33

U17 LM1117-3.3-0.8A

VCC5 3 4

ADJ/GND

INPUT VOUT

R28

TC7 BC64 TC8 TC19 TC9

C C

120

1

100U/6V 0.1U 100U/6V 100U/6V 100U/6V VCC33 F_VCC33 VCC33 R_VCC33 VCC33 A_VCC33

R25 0 R26 0 R27 0

POWER

LEDB

BC61 TC10 BC62 TC11 BC63 TC12

0.1U 100U/6V 0.1U 100U/6V 0.1U 100U/6V

1V2 VCC12 VCCINT VCC33 VCCIO

VCC33 VCC12 VCC12

U11 LM1117-1.2-0.8A R29 0 R30 0

3 4

ADJ/GND

INPUT VOUT

B TC16 BC65 TC17 C4 R31 TC14 TC13 TC18 TC15 B

1

100U/6V 0.1U 100U/6V 1U 330 100U/6V 100U/6V 100U/6V 100U/6V

GND1 GND2 GND3 GND4 MH1 MH2 MH3 MH4 MH5 MH6

GND GND GND GND GND GND GND GND GND GND FID1 FID2 FID3 FID4 FID5 FID6

FIDUCIAL FIDUCIAL FIDUCIAL FIDUCIAL FIDUCIAL FIDUCIAL

A A

Title

Altera Cyclone II Starter Board

Size Document Number Rev

B POWER 1.1A

Date: Tuesday, October 03, 2006 Sheet 20 of 21

5 4 3 2 1

5 4 3 2 1

24MHZ

R32 330 FP3V

PWRON

USBON

USB5V

L1 BEAD BC68 BC69

USB5V

BC70 BC71 BC72 0.1U 0.1U

100

L2 BEAD

13

30

26

99

98

97

96

95

94

93

92

91

90

89

88

87

86

85

84

83

82

81

80

79

78

77

76

3

0.1U 0.1U 0.1U U12 FP3V U13

BC73

VCCIO

IO-A2

IO-A3

IO-A4

IO-A5

IO-A6

GNDIO

IO-A7

IO-A8

IO-A9

INPUT/OE2/GCLK2

INPUT/GCLRn

INPUT/OE1

INPUT/GCLK1

IO-H8

IO-H7

IO-H6

VCCIO

IO-H5

IO-H4

IO-H3

GNDIO

IO-H2

IO-H1

AVCC

VCC

VCC

VCCINT

GNDINT

D D

0.1U 6 25 ULED 1 75

3V3OUT D0 6MHZ IO-A1 IO-H0

D1 24 2 IO-A0 GNDIO 74

23 3 73 ISPTDO RN41

J9 USB TYPE B R33 1.5K D2 ISPTDI VCCIO TDO FPTDI LINK_D0

5 RSTOUT# D3 22 4 TDI IO-G7 72 1 8

3 USB_DP 21 UD0 5 71 FPNCSO 2 7 LINK_D1

D+ D-

USB_DM R34 22 D4 UD1 IO-B8 IO-G6 FPTCK LINK_D2

2 7 USBDP D5 20 6 IO-B7 IO-G5 70 3 6

19 UD2 7 69 FPNST 4 5 LINK_D3

R35 22 D6 UD3 IO-B6 IO-G4

1 8 USBDM D7 18 8 IO-B5 IO-G3 68

GND VBUS 4 UD4 9 67 120

IO-B4 IO-G2

3

3

UD5 10 66

IO-B3 VCCIO FP3V

D9 D10 27 16 GND 11 65

XTIN RD# UD6 GNDIO GNDIO TDO

BAT54S BAT54S 15 12 64

5

WR UD7 IO-B2 IO-G1 TCK

28 XTOUT TXE# 14 13 IO-B1 IO-G0 63

12 14 EPM3128AT 62 ISPTCK

1

2

R36 100K nRESET RXF# ISPTMS IO-B0 TCK TMS

USB5V 4 RESET# 15 TMS IO-F7 61

16 60 TDI

USB5V USB5V IO-C8 IO-F6

17 IO-C7 GNDIO 59

2 EEDATA 18 VCCIO IO-F5 58

1 19 57 TRGDCLK

6MHZ R37 22 EESK IO-C6 IO-F4 TRGASDO

32 EECS SI/WU 11 20 IO-C5 IO-F3 56

31 10 21 55 TRGNCS

TEST PWREN# IO-C4 IO-F2

AGND

C14 URD 22 54 TRGNST

GND

GND

UWR IO-C3 IO-F1

C 23 IO-C2 GNDIO 53 C

47P TXE 24 52

IO-C1 IO-F0

GNDINT

FT245BM RXF

VCCINT

25 51

GNDIO

GNDIO

GNDIO

VCCIO

29

9

17

IO-C0 VCCIO

IO-D8

IO-D7

IO-D6

IO-D5

IO-D4

IO-D3

IO-D2

IO-D1

IO-D0

IO-E0

IO-E1

IO-E2

IO-E3

IO-E4

IO-E5

IO-E6

IO-E7

IO-E8

IO-E9

USB5V USB3V LOAD

R38 120 ULED

FP3V

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

U14 LM1117-3.3-0.8A

3 4 LEDB

ADJ/GND

INPUT VOUT

FP3V

BC74 TC20 BC75 BC76 BC77 TRGOE

USB5V

RN42

0.1U 100U/6V 0.1U 0.1U 0.1U U15

1

8 1 EEPCS 1 8

EEPCLK 2 CS VCC

7 2 CLK NC 7

R39 1.5K 6 3 EEPDI 3 6 BC78

EEPDO 4 DI ORG

5 4 DO GND 5

0.1U

CONF_DONE R49 10K VCC33 93LC46B

NSTATUS R50 10K 120

B Q2 8550 Q3 8550 B

RN44

RN43 10K JP3

VCC33 FP3V USB3V FP3V

NCONFIG 5 4 VCC33 8 1 EEPDI ISPTCK

ISPTDO 1 2

6 3 7 2 3 4 USB3V

TCK 7 2 6 3 ISPTMS EEPCLK

USB3V 5 6 USB5V

NCE 8 1 5 4 EEPDO EEPCS VCC5

ISPTDI 7 8 R40 R41 R42 R43

9 10

RN45 10K SW12 10K CPLD ISP 1K 10K 1K 10K

4 5 VCC33 4 R44 R45

TDI 3 6 1 NCE VCC5 PWRON USBON

TMS 2 7 2 VCC33 4.7K 4.7K

TDO 1 8 3 TRGOE R46 1.5K U16

5 TRGNCS 1 8 VCC33 BC79 Q1 Q4

TRGNST nCS VCC VCC33 8050 8050

2 DATA VCC 7

SW-Slide VCC33 3 6 TRGDCLK 0.1U

RN46 120 GND VCC DCLK TRGASDO R47 R48

4 GND ASDI 5

DCLK 8 1 TRGDCLK RUN/PROG

ASDO 7 2 TRGASDO EPCS4 1K 1K

NCSO 6 3 TRGNCS FP3V

DATA0 5 4 TRGNST

LINK_D0

LINK_D1 Y3 BC80 FP3V

A LINK_D2 4 1 A

LINK_D3 VCC EN 0.1U

24MHZ 3 2

OUT GND BC81 BC82 BC83 BC84 BC85 BC86

24MHZ

0.1U 0.1U 0.1U 0.1U 0.1U 0.1U Title

Altera Cyclone II Starter Board

Size Document Number Rev

B USB BLASTER 1.1A

Date: Tuesday, October 03, 2006 Sheet 21 of 21

5 4 3 2 1

Vous aimerez peut-être aussi

- CCTV Surveillance: Video Practices and TechnologyD'EverandCCTV Surveillance: Video Practices and TechnologyÉvaluation : 4 sur 5 étoiles4/5 (1)

- DE0 ReleaseDocument19 pagesDE0 Releasedoniz30Pas encore d'évaluation

- LAB-X1 SchematicDocument2 pagesLAB-X1 SchematicRenato MirandaPas encore d'évaluation

- Labx 1 SCHDocument2 pagesLabx 1 SCHercervantesPas encore d'évaluation

- Advanced Raspberry Pi: Raspbian Linux and GPIO IntegrationD'EverandAdvanced Raspberry Pi: Raspbian Linux and GPIO IntegrationPas encore d'évaluation

- P+5V P+5V: Power On MuteDocument8 pagesP+5V P+5V: Power On MuteuyrikPas encore d'évaluation

- Beginning STM32: Developing with FreeRTOS, libopencm3 and GCCD'EverandBeginning STM32: Developing with FreeRTOS, libopencm3 and GCCPas encore d'évaluation

- MCD Demo2 Manual enDocument33 pagesMCD Demo2 Manual enmario_villarreal_110% (1)

- Physics and Technology of Crystalline Oxide Semiconductor CAAC-IGZO: Application to LSID'EverandPhysics and Technology of Crystalline Oxide Semiconductor CAAC-IGZO: Application to LSIPas encore d'évaluation

- Spock: Power Serial I/ODocument5 pagesSpock: Power Serial I/OSanyi Ocsai100% (2)

- CECL08D Datasheet Mp3-PlayerDocument1 pageCECL08D Datasheet Mp3-PlayerGlauber CostaPas encore d'évaluation

- Isp C v5Document2 pagesIsp C v5Francis TaisantPas encore d'évaluation

- M300 U400Document38 pagesM300 U400Sebastian FrancisPas encore d'évaluation

- rqqhfwlrqvehwzhhq5) Dqg%%0Rgxohv: &&67Hfkqlfdo'Rfxphqwdwlrq 6Fkhpdwlfv/D/Rxwv') Ybd 1$0Document9 pagesrqqhfwlrqvehwzhhq5) Dqg%%0Rgxohv: &&67Hfkqlfdo'Rfxphqwdwlrq 6Fkhpdwlfv/D/Rxwv') Ybd 1$0anjirponselPas encore d'évaluation

- High-Performance GM LS-Series Cylinder Head GuideD'EverandHigh-Performance GM LS-Series Cylinder Head GuideÉvaluation : 4.5 sur 5 étoiles4.5/5 (2)

- OV7670 + AL422B (FIFO) Camera Module (V2.0) SchematicDocument1 pageOV7670 + AL422B (FIFO) Camera Module (V2.0) SchematicMuhammad Alfiansyah100% (3)

- Exploring Arduino: Tools and Techniques for Engineering WizardryD'EverandExploring Arduino: Tools and Techniques for Engineering WizardryÉvaluation : 4.5 sur 5 étoiles4.5/5 (5)

- Hws 13642Document3 pagesHws 13642dhieward100% (2)

- Exploring BeagleBone: Tools and Techniques for Building with Embedded LinuxD'EverandExploring BeagleBone: Tools and Techniques for Building with Embedded LinuxÉvaluation : 4 sur 5 étoiles4/5 (2)

- PS2134 64 Schematic Kingston DTDocument3 pagesPS2134 64 Schematic Kingston DTluis_may22Pas encore d'évaluation

- LG r480 - Quanta Ql3 Preso-II - Rev 1a PDFDocument39 pagesLG r480 - Quanta Ql3 Preso-II - Rev 1a PDFJosé Da Silva MataPas encore d'évaluation

- 8051 Microcontroller: An Applications Based IntroductionD'Everand8051 Microcontroller: An Applications Based IntroductionÉvaluation : 5 sur 5 étoiles5/5 (6)

- PE4H VER24 SchematicDocument2 pagesPE4H VER24 SchematicB Huerta MuñozPas encore d'évaluation

- Semiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsD'EverandSemiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsPas encore d'évaluation

- Cpu Logic DiagramDocument0 pageCpu Logic DiagramMauricio RaúlPas encore d'évaluation

- Noblex - RCD - 138Document8 pagesNoblex - RCD - 138pablo190381Pas encore d'évaluation

- LCR Metar - Sve ShemeDocument7 pagesLCR Metar - Sve ShemeKarlo MužinićPas encore d'évaluation

- ®MCI Electronics WWW - Olimex.cl: 3V3 3V3 RssiDocument1 page®MCI Electronics WWW - Olimex.cl: 3V3 3V3 Rssiefx8100% (1)

- Complete PCB Design Using OrCAD Capture and PCB EditorD'EverandComplete PCB Design Using OrCAD Capture and PCB EditorÉvaluation : 5 sur 5 étoiles5/5 (1)

- Acer Aspire 7741 7741z 7741g 7741zg Emachines G730g Wistron JE70-CP Rev - 1M SCHDocument67 pagesAcer Aspire 7741 7741z 7741g 7741zg Emachines G730g Wistron JE70-CP Rev - 1M SCHWilgen GarciaPas encore d'évaluation

- Engineering Service Revenues World Summary: Market Values & Financials by CountryD'EverandEngineering Service Revenues World Summary: Market Values & Financials by CountryPas encore d'évaluation

- Toshiba Satellite M300 M305 Quanta TE1 Laptop SchematicsDocument40 pagesToshiba Satellite M300 M305 Quanta TE1 Laptop SchematicsErick RodriguezPas encore d'évaluation

- 07 Schematic Diagram EDocument6 pages07 Schematic Diagram EGiovanni Mendoza100% (1)

- Can Bus SCHDocument1 pageCan Bus SCHhoangdai100% (3)

- Packard-Bell Easynote Ml65 Vesurio Pb5 Pb6 Quanta Pb5 Pb6 Rev 1a SCHDocument35 pagesPackard-Bell Easynote Ml65 Vesurio Pb5 Pb6 Quanta Pb5 Pb6 Rev 1a SCHAloui ZakariaPas encore d'évaluation

- Acer 5553g M B Quanta Zr8 - Da0zr8mb8e0Document49 pagesAcer 5553g M B Quanta Zr8 - Da0zr8mb8e0tuner12Pas encore d'évaluation

- Acer I5 47501306462469980Document67 pagesAcer I5 47501306462469980fdsaq12Pas encore d'évaluation

- TF 117 Circuit DiagramDocument9 pagesTF 117 Circuit DiagramFrancis TaisantPas encore d'évaluation

- Abit - M621 Schematics: Title Sheet ModifyDocument33 pagesAbit - M621 Schematics: Title Sheet Modify775i945GZ100% (1)

- 8I845PE PRO Rev.1.01 SCHDocument38 pages8I845PE PRO Rev.1.01 SCHJurgita GecienePas encore d'évaluation

- HP Envy 15 (Quanta SP7)Document42 pagesHP Envy 15 (Quanta SP7)efeln1Pas encore d'évaluation

- Toshiba Satellite A300Document37 pagesToshiba Satellite A300Nagy József100% (1)

- Scheme HP Compaq Cq61 Quanta Op8Document40 pagesScheme HP Compaq Cq61 Quanta Op8Alija SirotanovićPas encore d'évaluation

- Q9T4 FP91G Interface BDDocument5 pagesQ9T4 FP91G Interface BDax63naPas encore d'évaluation

- Schematic DiagramDocument13 pagesSchematic DiagramSas WajiPas encore d'évaluation

- DELL VOSTRO-3500 Winery15 PDFDocument91 pagesDELL VOSTRO-3500 Winery15 PDFronaldovieiraPas encore d'évaluation

- Wistron JV50-PU Rev SB PDFDocument61 pagesWistron JV50-PU Rev SB PDFalbugPas encore d'évaluation

- Helio Board SCH v1.22Document26 pagesHelio Board SCH v1.22nanostallmannPas encore d'évaluation

- HP Pavilion Dv6 Quanta Ut3 Ut5 Rev PV SCHDocument43 pagesHP Pavilion Dv6 Quanta Ut3 Ut5 Rev PV SCHOtto OctavianPas encore d'évaluation

- HP Pavilion Dv6000 Dv6500 Dv6600 Dv6700 Dv9000 Dv9500 - DA0AT3MB8F0 - QUANTA AT3 - SC (Intel) - Rev 1ADocument48 pagesHP Pavilion Dv6000 Dv6500 Dv6600 Dv6700 Dv9000 Dv9500 - DA0AT3MB8F0 - QUANTA AT3 - SC (Intel) - Rev 1Agbouret0% (1)

- Perancangan Crushing Plant Batu Andesit Di PT Nurmuda Cahaya Desa Batujajar Timur Kecamatan Batujajar Kabupaten Bandung Barat Provinsi Jawa BaratDocument8 pagesPerancangan Crushing Plant Batu Andesit Di PT Nurmuda Cahaya Desa Batujajar Timur Kecamatan Batujajar Kabupaten Bandung Barat Provinsi Jawa BaratSutan AdityaPas encore d'évaluation

- Fire Protection in BuildingsDocument2 pagesFire Protection in BuildingsJames Carl AriesPas encore d'évaluation

- Module 2 MANA ECON PDFDocument5 pagesModule 2 MANA ECON PDFMeian De JesusPas encore d'évaluation

- Sample - SOFTWARE REQUIREMENT SPECIFICATIONDocument20 pagesSample - SOFTWARE REQUIREMENT SPECIFICATIONMandula AbeyrathnaPas encore d'évaluation

- Quiz 140322224412 Phpapp02Document26 pagesQuiz 140322224412 Phpapp02Muhammad Mubeen Iqbal PuriPas encore d'évaluation

- PMP Assesment TestDocument17 pagesPMP Assesment Testwilliam collinsPas encore d'évaluation

- Cable To Metal Surface, Cathodic - CAHAAW3Document2 pagesCable To Metal Surface, Cathodic - CAHAAW3lhanx2Pas encore d'évaluation

- Congenital Cardiac Disease: A Guide To Evaluation, Treatment and Anesthetic ManagementDocument87 pagesCongenital Cardiac Disease: A Guide To Evaluation, Treatment and Anesthetic ManagementJZPas encore d'évaluation

- Government College of Nursing Jodhpur: Practice Teaching On-Probability Sampling TechniqueDocument11 pagesGovernment College of Nursing Jodhpur: Practice Teaching On-Probability Sampling TechniquepriyankaPas encore d'évaluation

- Man and Historical ActionDocument4 pagesMan and Historical Actionmama.sb415Pas encore d'évaluation

- 1 in 8.5 60KG PSC Sleepers TurnoutDocument9 pages1 in 8.5 60KG PSC Sleepers Turnoutrailway maintenancePas encore d'évaluation

- Rana2 Compliment As Social StrategyDocument12 pagesRana2 Compliment As Social StrategyRanaPas encore d'évaluation

- postedcontentadminuploadsFAQs20for20Organization PDFDocument10 pagespostedcontentadminuploadsFAQs20for20Organization PDFMohd Adil AliPas encore d'évaluation

- Cloud Comp PPT 1Document12 pagesCloud Comp PPT 1Kanishk MehtaPas encore d'évaluation

- Biblical World ViewDocument15 pagesBiblical World ViewHARI KRISHAN PALPas encore d'évaluation

- Review On AlgebraDocument29 pagesReview On AlgebraGraziela GutierrezPas encore d'évaluation

- Dwnload Full Principles of Economics 7th Edition Frank Solutions Manual PDFDocument35 pagesDwnload Full Principles of Economics 7th Edition Frank Solutions Manual PDFmirthafoucault100% (8)

- India TeenagersDocument3 pagesIndia TeenagersPaul Babu ThundathilPas encore d'évaluation

- Brand Strategy - in B2BDocument6 pagesBrand Strategy - in B2BKrishan SahuPas encore d'évaluation

- Desktop 9 QA Prep Guide PDFDocument15 pagesDesktop 9 QA Prep Guide PDFPikine LebelgePas encore d'évaluation

- Pathology of LiverDocument15 pagesPathology of Liverערין גבאריןPas encore d'évaluation

- Case Study 2Document5 pagesCase Study 2api-247285537100% (1)

- QSP 04bDocument35 pagesQSP 04bakrastogi94843Pas encore d'évaluation

- Thesis PaperDocument53 pagesThesis PaperAnonymous AOOrehGZAS100% (1)

- Cyber Briefing Series - Paper 2 - FinalDocument24 pagesCyber Briefing Series - Paper 2 - FinalMapacheYorkPas encore d'évaluation

- Amount of Casien in Diff Samples of Milk (U)Document15 pagesAmount of Casien in Diff Samples of Milk (U)VijayPas encore d'évaluation

- Close Enough To Touch by Victoria Dahl - Chapter SamplerDocument23 pagesClose Enough To Touch by Victoria Dahl - Chapter SamplerHarlequinAustraliaPas encore d'évaluation

- Phytotherapy On CancerDocument21 pagesPhytotherapy On CancerSiddhendu Bhattacharjee100% (1)

- Design of Penstock: Reference Code:IS 11639 (Part 2)Document4 pagesDesign of Penstock: Reference Code:IS 11639 (Part 2)sunchitk100% (3)

- In Flight Fuel Management and Declaring MINIMUM MAYDAY FUEL-1.0Document21 pagesIn Flight Fuel Management and Declaring MINIMUM MAYDAY FUEL-1.0dahiya1988Pas encore d'évaluation