Académique Documents

Professionnel Documents

Culture Documents

Vl9251 Testing of Vlsi Circuits

Transféré par

Velmurugan Subbiah ParvathyDescription originale:

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

Vl9251 Testing of Vlsi Circuits

Transféré par

Velmurugan Subbiah ParvathyDroits d'auteur :

Formats disponibles

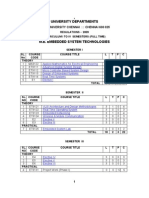

VL9251 TESTING OF VLSI CIRCUITS LTPC 3003 UNIT I BASICS OF TESTING AND FAULT MODELLING 9 Introduction to testing Faults

s in Digital Circuits Modelling of faults Logical Fault Models Fault detection Fault Location Fault dominance Logic simulation Types of simulation Delay models Gate Level Event driven simulation. UNIT II TEST GENERATION FOR COMBINATIONAL AND SEQUENTIAL CIRCUITS 9 Test generation for combinational logic circuits Testable combinational logic circuit design Test generation for sequential circuits design of testable sequential circuits. UNIT III DESIGN FOR TESTABILITY 9 Design for Testability Ad-hoc design generic scan based design classical scan based design system level DFT approaches. UNIT IV SELF TEST AND TEST ALGORITHMS 9 Built-In self Test test pattern generation for BIST Circular BIST BIST Architectures Testable Memory Design Test Algorithms Test generation for Embedded RAMs. UNIT V FAULT DIAGNOSIS 9 Logical Level Diagnosis Diagnosis by UUT reduction Fault Diagnosis for Combinational Circuits Self-checking design System Level Diagnosis. Total: 45 REFERENCES:

1. M.Abramovici, M.A.Breuer and A.D. Friedman, Digital systems and Testable Design, Jaico Publishing House,2002. 2. P.K. Lala, Digital Circuit Testing and Testability, Academic Press, 2002. 3. M.L.Bushnell and V.D.Agrawal, Essentials of Electronic Testing for Digital, Memory and Mixed-Signal VLSI Circuits, Kluwer Academic Publishers, 2002. 4. A.L.Crouch, Design Test for Digital ICs and Embedded Core Systems, Prentice Hall International, 2002.

Vous aimerez peut-être aussi

- Digital Circuit Testing: A Guide to DFT and Other TechniquesD'EverandDigital Circuit Testing: A Guide to DFT and Other TechniquesPas encore d'évaluation

- Electronic Design Automation: Synthesis, Verification, and TestD'EverandElectronic Design Automation: Synthesis, Verification, and TestPas encore d'évaluation

- TVC SyllabusDocument1 pageTVC Syllabuskalai555Pas encore d'évaluation

- 13ec571 PDFDocument1 page13ec571 PDFsushPas encore d'évaluation

- Syllabus 3rd Semester Me Vlsi DesignDocument3 pagesSyllabus 3rd Semester Me Vlsi DesignSHARANYAPas encore d'évaluation

- Ap7102 Adsd SyllabiDocument6 pagesAp7102 Adsd SyllabishankarPas encore d'évaluation

- Course Work SyllabusDocument4 pagesCourse Work SyllabusKiruba KaranPas encore d'évaluation

- Ap7102 AdsdDocument5 pagesAp7102 AdsdshankarPas encore d'évaluation

- Ece5029 Vlsi-Testing-And-Testability TH 1.1 47 Ece5029Document2 pagesEce5029 Vlsi-Testing-And-Testability TH 1.1 47 Ece5029Chandan MalleshPas encore d'évaluation

- M E EmbeddedSystemTechnologiesDocument31 pagesM E EmbeddedSystemTechnologiesRohini BabuPas encore d'évaluation

- M.E. Vlsi Design: Anna University of Technology Madurai MADURAI - 625002 Regulations 2010 Curriculam & SyllabiDocument34 pagesM.E. Vlsi Design: Anna University of Technology Madurai MADURAI - 625002 Regulations 2010 Curriculam & SyllabikumaranrajPas encore d'évaluation

- Vlsi Design PDFDocument22 pagesVlsi Design PDFKishore KumarPas encore d'évaluation

- Advanced Digital System DesignDocument1 pageAdvanced Digital System Designarunecetheboss0% (3)

- EC6302 - de - SyllabusDocument2 pagesEC6302 - de - SyllabusNava KrishnanPas encore d'évaluation

- Vlsi System DesignDocument12 pagesVlsi System DesignMahender GoudPas encore d'évaluation

- Digital System DesignDocument2 pagesDigital System DesignYaswanthPas encore d'évaluation

- M.E.embedded System TechnologiesDocument32 pagesM.E.embedded System TechnologiesSri RamPas encore d'évaluation

- Vlsi DesignDocument12 pagesVlsi DesignTanveer AhmedPas encore d'évaluation

- Cse I PDFDocument22 pagesCse I PDFannamyemPas encore d'évaluation

- SyllabusDocument3 pagesSyllabusSushanth RajkumarPas encore d'évaluation

- VLSIDocument28 pagesVLSISurendhar SekarPas encore d'évaluation

- Syl PDFDocument1 pageSyl PDFNivithaPas encore d'évaluation

- EC8095 SyllabusDocument2 pagesEC8095 Syllabusjames RPas encore d'évaluation

- De SyllabusDocument2 pagesDe SyllabusKarthikeyan_Go_9525Pas encore d'évaluation

- Vlsi Mtech 1st - Year - Jntu Kakinada SyllabusDocument8 pagesVlsi Mtech 1st - Year - Jntu Kakinada Syllabustele203Pas encore d'évaluation

- Regulation - 2009: Affiliated Institutions Anna University, ChennaiDocument27 pagesRegulation - 2009: Affiliated Institutions Anna University, ChennaiYogeswaran SundarrajPas encore d'évaluation

- La Verificacion de Sistemas DigitalesDocument19 pagesLa Verificacion de Sistemas DigitalesinghectorrPas encore d'évaluation

- Physical Design of Vlsi CircuitsDocument1 pagePhysical Design of Vlsi CircuitsNatheswaranPas encore d'évaluation

- R 2008 M.E. Embedded System Tech SyllabusDocument26 pagesR 2008 M.E. Embedded System Tech Syllabuslee_ganeshPas encore d'évaluation

- Design For TestabilityDocument26 pagesDesign For TestabilityDenise NelsonPas encore d'évaluation

- Vlsi Mtech Jntu Kakinada SyllabusDocument11 pagesVlsi Mtech Jntu Kakinada Syllabusaditya414Pas encore d'évaluation

- VVC SyllabusDocument1 pageVVC SyllabusRamesh MallaiPas encore d'évaluation

- EmbeddedDocument9 pagesEmbeddedNanc Joy100% (1)

- Vlsi Mtech Jntu Kakinada II Sem SyllabusDocument16 pagesVlsi Mtech Jntu Kakinada II Sem Syllabusrv prasad50% (2)

- Cad VlsiDocument1 pageCad VlsiAnil MarturiPas encore d'évaluation

- VLSI, VLSI System & VLSI System DesignDocument26 pagesVLSI, VLSI System & VLSI System Designrohit_sreerama4040Pas encore d'évaluation

- M.E. (Embedded System Technologies)Document37 pagesM.E. (Embedded System Technologies)Priya DarshiniPas encore d'évaluation

- M Tech VLSI Design SyllabusDocument46 pagesM Tech VLSI Design SyllabusVirupakshi MadhurimaPas encore d'évaluation

- I M.Tech - IT (Full Time) (11-13)Document8 pagesI M.Tech - IT (Full Time) (11-13)Balaji PaulrajPas encore d'évaluation

- Embedded System TechnologiesDocument37 pagesEmbedded System TechnologiesjayaprahasPas encore d'évaluation

- Regulations - 2009: Affiliated Institutions Anna University, ChennaiDocument10 pagesRegulations - 2009: Affiliated Institutions Anna University, Chennaisri_vas00074013Pas encore d'évaluation

- Vlsi Vlsid Vlsisd Vlsi Me Ece PDFDocument18 pagesVlsi Vlsid Vlsisd Vlsi Me Ece PDFramanaidu1Pas encore d'évaluation

- ME VLSI SyllabusDocument33 pagesME VLSI Syllabusps0208Pas encore d'évaluation

- New Trends in Observer-Based Control: An Introduction to Design Approaches and Engineering ApplicationsD'EverandNew Trends in Observer-Based Control: An Introduction to Design Approaches and Engineering ApplicationsOlfa BoubakerPas encore d'évaluation

- On-Chip Communication Architectures: System on Chip InterconnectD'EverandOn-Chip Communication Architectures: System on Chip InterconnectPas encore d'évaluation

- Multimedia Services in Wireless Internet: Modeling and AnalysisD'EverandMultimedia Services in Wireless Internet: Modeling and AnalysisPas encore d'évaluation

- Object-Oriented Simulation with Hierarchical, Modular Models: Intelligent Agents and Endomorphic SystemsD'EverandObject-Oriented Simulation with Hierarchical, Modular Models: Intelligent Agents and Endomorphic SystemsÉvaluation : 1 sur 5 étoiles1/5 (1)

- Fault Tolerant & Fault Testable Hardware DesignD'EverandFault Tolerant & Fault Testable Hardware DesignÉvaluation : 5 sur 5 étoiles5/5 (2)

- System-on-Chip Test Architectures: Nanometer Design for TestabilityD'EverandSystem-on-Chip Test Architectures: Nanometer Design for TestabilityPas encore d'évaluation

- Advanced Penetration Testing for Highly-Secured Environments - Second EditionD'EverandAdvanced Penetration Testing for Highly-Secured Environments - Second EditionPas encore d'évaluation

- Wireless Personal Area Networks: Performance, Interconnection and Security with IEEE 802.15.4D'EverandWireless Personal Area Networks: Performance, Interconnection and Security with IEEE 802.15.4Pas encore d'évaluation

- Networks on Chips: Technology and ToolsD'EverandNetworks on Chips: Technology and ToolsÉvaluation : 5 sur 5 étoiles5/5 (3)

- Top-Down Digital VLSI Design: From Architectures to Gate-Level Circuits and FPGAsD'EverandTop-Down Digital VLSI Design: From Architectures to Gate-Level Circuits and FPGAsPas encore d'évaluation

- Multisensor Instrumentation 6σ Design: Defined Accuracy Computer-Integrated Measurement SystemsD'EverandMultisensor Instrumentation 6σ Design: Defined Accuracy Computer-Integrated Measurement SystemsPas encore d'évaluation

- Algorithm-Structured Computer Arrays and Networks: Architectures and Processes for Images, Percepts, Models, InformationD'EverandAlgorithm-Structured Computer Arrays and Networks: Architectures and Processes for Images, Percepts, Models, InformationPas encore d'évaluation

- Multi-Camera Networks: Principles and ApplicationsD'EverandMulti-Camera Networks: Principles and ApplicationsHamid AghajanÉvaluation : 3 sur 5 étoiles3/5 (1)