Académique Documents

Professionnel Documents

Culture Documents

Programación AT89C52

Transféré par

Jhenrry C CHDescription originale:

Titre original

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

Programación AT89C52

Transféré par

Jhenrry C CHDroits d'auteur :

Formats disponibles

AT89C52

Programacin de los Microcontroladores 8052/8051

Datos personales

Ronald Mijail Dueas D Estudiante de Electronica y Sistemas Ver todo mi perfil

ELECTRONICA CUSCO

Mi lista de blogs

Puerto Paralelo DB25

Hace 3 aos

INTERFACE SERIAL RS232

Hace 3 aos

PROGRAMADOR DE ATMEL SERIE 89

GRABADOR SERIE 89 ATMEL

Hace 3 aos

GRABADOR ISP ATMEL AT89S51-AT89S52

GRABADOR SIMPLE POR PUERTO PARALELO

Hace 3 aos

martes 26 de agosto de 2008

Grabador ISP simple por puerto paralelo, para los AT89S51, AT89S52 ... http://grabador-isp-atmel.blogspot.com/ Grabador, programador de Atmel serie 89 AT89C51 /52 /55 y los At89S51/52/55 ... http://www.grabador-atmel.blogspot.com/ Programacion del pic17f877A http://www.programacion-pic16f877a.es.tl/

domingo 24 de febrero de 2008

PROGRAMACION DEL AT89C52

Todos los modelos de la familia 51 ejecutan cl mismo conjunto de instrucciones. Estas instrucciones estan optimizadas para cl control de aplicaciones en 8 bits. Estan provistas de una buena variedad de modos de direccionamiento para acceder a la memoria RAM de datos internos del microcontrolador, facilitando operaciones del tipo byte sobre una pequea estructura de datos. Permiten la manipulacion directa de control y procesamiento booleano de estructuras de datos del tamao de un bit. En esta breve introduccion se estudiaran los modos de direccionamiento y el juego de instrucciones agrupadas por especialidades de esta manera: Instrucciones aritmeticas. Instrucciones logicas. Instrucciones para la transferencia de datos en: a) RAM interna.

b) RAM externa. Instrucciones para cl tratamiento de tablas. Instrucciones booleanas. Instrucciones de salto.

MODOS DE DIRECCIONAMIENTO

Direccionamiento Directo El operando se especifica en la instruccion por un campo de direccion de 8 bits. Solo la RAM interna de datos (primeros 128 bytes) y la zona de SFR se pueden direccionar de esta forma. ejemplo: ADD A,38H; es decir, suma (ADD) el contenido del acumulador (A) con el contenido de la posicion de memoria (38):

Direccionamiento Indirecto La instruccion especifica un registro que contiene la direccion del operando. Tanto la memoria RAM interna (256 bytes/128 bytes) como la externa se pueden direccionar indirectamente. Los registros para direccionar sobre el mapa de 8 bits pueden ser el R0 y R1 del banco de registros seleccionado, o el Stack Pointer. El registro para direccionar sobre 16 bits solo puede ser el Puntero de Datos (Data Pointer = DPTR). Ejemplo: ADD A,@R0 ; Asi, si (RO)=38H la operaci6n sera: A << (A) + (38) Igual que en el ejemplo anterior (@) es el identificador del direccionamiento indirecto. Direccionamiento por registro

Los Microcontroladores 8052/8051, como se ha visto, contiene cuatro bancos de registros seleccionados por los bits 3 y 4 del PSW, y cada banco de registros tiene ocho registros del RO al R7 (vease Apartado 2.5). El propio codigo de operacion de la instruccion especifica con que registro se opera; es decir, cuando la i nstru ccion es ejecutada se accede a u no de los 8 reg istros del banco seleccionado.

Ejemplos: MOV Rn,A ; operacin: (Rn) << (A) MOV Rn,#dato; operacin (Rn) << (#dato) Direccionamiento implicito Algunas instrucciones especifican, implicitamente, el registro sobre el que van a operar, como el acumulador, el puntero de datos, etc. No necesitan especificar el operando porque esta implicito en el codigo de operacion.

ejemplos: INC A ; Incrementa el contenido del acumulador: A << (A) + 1 INC DPTR ; Incrementa puntero de datos: DPTR << (DPTR) + 1

Direccionamiento inmediato

Al codigo de operacion le sigue una constante en la memoria de programas. Ejemplo: MOV A, #255 ; Carga en el acumulador el numero decimal 255. en hexadecimal: MOV A, #FFH MOV A, #11111111B en binario: Direccionamiento indexado Este direccionamiento solo es posible en la memoria de programas y solo permite la lectura. Es utilizado para la lectura de tablas. Un registro base de 16 bits (cl DPTR o cl contador de programa) apunta a la base de la tabla y cl contenido del acumulador es cl offset que permite acceder a la lectura de esa posicion de la tabla. Es decir, la direccion de la tabla que se va a acceder esta formada por la suma del acumulador y cl puntero base. Se puede utilizar otro tipo de direccionamiento indexado en las instrucciones de salto. En este caso la direccion de destino del salto se calcula como la suma del puntero base y cl dato del acumulador.

CICLO DE INSTRUCCION

La ejecucion de un ciclo de instruccion comienza en cl estado 1 del ciclo maquina, cuando cl codigo de operacion es almacenado en cl Registro de Instruccion. (Para comprender este apartado tener a la vista la Figura 3.1 y la Tabla 4.5, Set de Instrucciones. )

Como norma general, una instruccion requiere de uno q mas ciclos maquina, en funcion de:

a) El codigo de operacion

Por ejemplo, la instruccion INC A (Figura 3.1 A) tiene 1 byte de instruccion y requiere 1 ciclo maquina, la instruccion INC DPTR, tambien, de 1 byte de instruccion requiere de 2 ciclos maquina (Figura 3.1 C) y la instruccion MUL AB requiere de 4 ciclos maquina para su total ejecucion y ocupa 1 byte en la memoria.

b) El numero de bytes

Por ejemplo, la instruccion MOV A, #data tiene 2 bytes de instruccion y requiere de 1 ciclo maquina (Figura 3.1 B). En cambio la instruccion MOV direct, # data al constar de 3 bytes necesita de 2 ciclos maquina. Esto no ocurre siempre, es decir, a mas bytes mas ciclos maquina, como puede verse en la Figura 3.1 B correspondiente a la instruccion MOV A, #data y en la Figura 3.1 D MOVX A,@Ri, la primera instruccion tiene 2 bytes y la segunda solo 1. en cambio la primera requiere 1 ciclo maquina y la segunda 2.

Ante la imposibilidad de establecer una norma o regla que facilite cl conocimiento del numero de bytes y ciclo de instruccion se ha editado la Tabla 4.5 con el set completo de instrucciones. Cabe destacar, tambien, en la Figura 3.1, que en cada ciclo maquina se producen 2 accesos a la memoria, cl primero, si es comienzo de ciclo de instruccion, siempre leera cl codigo de operacion, cl segundo, que normalmente se descarta, se utiliza para leer cl segundo byte, operando de la instruccion, como ocurre en la Figura 3.1 B.

TIPOS DE INSTRUCCIONES

El set de instrucciones del 8052/8051 se puede dividir segun las especialidades:

Instrucciones aritmeticas.

Instrucciones logicas.

Instrucciones de transferencia de datos.

Instrucciones booleanas

Instrucciones de salto. Pgina principal Suscribirse a: Entradas (Atom)

INSTRUCCIONES ARITMETICAS

MUL AB (multiplica) y DIV AB (divide)

INSTRUCCIONES LOGICAS

Incluye las instrucciones de rotacion a izquierda y derecha

INSTRUCCIONES DE TRANSFERENCIA DE DATOS

Las instrucciones Push y Pop actuan sobre el puntero a la pila (SP)

INSTRUCCIONES BOOLEANAS

ANL >> "and" / ORL >> "or" / CLR >> clear

INSTRUCCIONES DE SALTO

INSTRUCCIONES DE SALTO CONDICIONAL

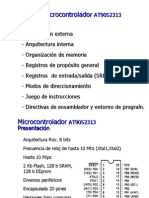

Microcontrolador ATMEGA16. Microcontrolador de ATMEL a 8 bits ATMEGA16. Caractersticas: Memoria Flash: 16Kb. Frecuencia de Operacin: 16Mhz. Pin count: 44 CPU: 8 bit AVR. Canales de ADC: 10. SRAM: 1Kb. EEPROM: 512 Bytes Voltaje de Operacin: 1.8V a 5.5V. # of touch channels: 16 Hardware Qtouch acquisition: no Hoja de datos

Atmega16Datasheet

Informacin tcnica

Atmega16TechnicalInfo

No hay crticas para este producto.

Escribir una crtica

Nombre:

Crtica:

Nota: HTML no sera traducido!

Calificacin: Malo Ingrese el siguiente cdigo:

Bueno

Continuar

Programador de microcontroladores AVR Dragon $ 800.00 MXN Aadir al carrito

Tarjeta de Desarrollo Mehenil 2 $ 220.00 MXN Aadir al carrito

Sensor de distancia infrarrojo salida analgica GP2Y0A21YK $ 270.00 MXN Aadir al carrito

KIT AVR Dragon + Mehenil 2. $ 950.00 MXN Aadir al carrito

AT90S2313 Microcontrolador ATMEL AVR $ 74.99 MXN Aadir al carrito

ATTINY26L Microcontrolador ATMEL AVR $ 59.99 MXN Aadir al carrito

ATTINY44 Microcontrolador ATMEL AVR $ 59.99 MXN

Aadir al carrito

AT90S2343 Microcontrolador ATMEL AVR $ 99.99 MXN Aadir al carrito

AT90S8515 Microcontrolador ATMEL AVR $ 79.99 MXN Aadir al carrito

AT90LS8535 Microcontrolador ATMEL AVR $ 99.99 MXN Aadir al carrito Etiquetas: microcontrolador

8 bits, atmel, atmega 16,

Caractersticas generales del ATmega8/8L

Microcontrolador AVR de 8 bit de alto rendimiento y bajo consumo. Arquitectura RISC avanzada. - 130 instrucciones. La mayora de un simple ciclo de clock de ejecucin. - 32 x 8 registros de trabajo de propsito general. - Capacidad de procesamiento de unos 16 MIPS a 16 MHz. - Funcionamiento esttico total. - Multiplicador On-Chip de 2 ciclos

Memorias de programa y de datos no voltiles. - 8K bytes de FLASH autoprogramable en sistema. Resistencia: 1.000 ciclos de escritura / borrado. - Seccin de cdigo aadida opcional con bits de bloqueo independientes. Programacin en sistema con el programa aadido On-Chip. Operacin de lectura durante la escritura. - 512 bytes de EEPROM. Resistencia: 100.000 ciclos de escritura / borrado. - 1K bytes de SRAM interna. - Bloqueo (cerradura) programable para la seguridad del software. Caractersticas de los perifricos. - Dos Timer/Contadores de 8 bits con prescaler separado y modo comparacin. - Un Timer/Contador de 16 bits con prescaler separado, modo comparacin y modo de captura. - Comparador analgico On-Chip. - Timer watchdog programable con oscilador separado On-Chip. - Interface serie SPI maestro/esclavo. - USART serie programable. - Contador en tiempo real con oscilador separado. - ADC de 8 canales en los encapsulados TQFP y MLF. 6 canales de 10 bits de precisin. 2 canales de 8 bits de precisin. - ADC de 6 canales en el encapsulado PDIP. 4 canales de 10 bits de precisin. 2 canales de 8 bits de precisin. - 3 canales de PWM. - Interface serie de dos hilos orientada a byte.

Caractersticas especiales del microcontrolador. - Reset de Power-on y deteccin de Brown-out programable. - Oscilador RC interno calibrado. - Fuentes de interrupcin externas e internas. - 5 modos de descanso: Idle, reduccin de ruido ADC, Power-save, Power-down y Standby. I/O y encapsulados - 23 lneas de I/O programables. - PDIP de 28 pines, TQFP y MLF de 32 pines. Tensiones de funcionamiento. - 2.7 - 5.5V (ATmega8L). - 4.5 - 5.5V (ATmega8).

Niveles de velocidad. - 0 - 8 MHz (ATmega8L). - 0 - 16 MHz (ATmega8).

Consumo de energa a 4MHz, 3V, 25C. - Activo: 3.6 mA. - Modo idle: 1.0 mA. - Modo power-down: 0.5 A.

Caractersticas generales del ATmega16/16L

Microcontrolador AVR de 8 bit de alto rendimiento y bajo consumo. Arquitectura RISC avanzada. - 131 instrucciones. La mayora de un simple ciclo de clock de ejecucin. - 32 x 8 registros de trabajo de propsito general. - Capacidad de procesamiento de unos 16 MIPS a 16 MHz. - Funcionamiento esttico total. - Multiplicador On-Chip de 2 ciclos

Memorias de programa y de datos no voltiles. - 16K bytes de FLASH autoprogramable en sistema. Resistencia: 1.000 ciclos de escritura / borrado. - Seccin de cdigo aadida opcional con bits de bloqueo independientes. Programacin en sistema con el programa aadido On-Chip. Operacin de lectura durante la escritura. - 512 bytes de EEPROM. Resistencia: 100.000 ciclos de escritura / borrado. - 1K bytes de SRAM interna. - Bloqueo (cerradura) programable para la seguridad del software. Interface JTAG. - Mantenimiento de eliminacin de errores On-Chip. - Programacin de FLASH, EEPROM, fusibles y bits de bloqueo a travs de la interface JTAG. - Capacidades de Boundary Scan de acuerdo con el Standard (norma) JTAG. Caractersticas de los perifricos. - Dos Timer/Contadores de 8 bits con prescaler separado y modo comparacin. - Un Timer/Contador de 16 bits con prescaler separado, modo comparacin y modo de captura.

- Comparador analgico On-Chip. - Timer watchdog programable con oscilador separado On-Chip. - Interface serie SPI maestro/esclavo. - USART serie programable. - Contador en tiempo real con oscilador separado. - ADC de 10 bit y 8 canales. 8 canales de terminacin simple 7 canales diferenciales slo en el encapsulado TQFP. 2 canales diferenciales con ganancia programable a 1x, 10x o 200x. - 4 canales de PWM. - Interface serie de dos hilos orientada a byte.

Caractersticas especiales del microcontrolador. - Reset de Power-on y deteccin de Brown-out programable. - Oscilador RC interno calibrado. - Fuentes de interrupcin externas e internas. - 6 modos de descanso: Idle, reduccin de ruido ADC, Power-save, Power-down, Standby y Standby extendido. I/O y encapsulados - 32 lneas de I/O programables. - PDIP de 40 pines, TQFP y MLF de 44 pines. Tensiones de funcionamiento. - 2.7 - 5.5V (ATmega16L). - 4.5 - 5.5V (ATmega16). Niveles de velocidad. - 0 - 8 MHz (ATmega16L). - 0 - 16 MHz (ATmega16).

Caractersticas generales del ATmega32/32L

Microcontrolador AVR de 8 bit de alto rendimiento y bajo consumo. Arquitectura RISC avanzada. - 131 instrucciones. La mayora de un simple ciclo de clock de ejecucin. - 32 x 8 registros de trabajo de propsito general. - Capacidad de procesamiento de unos 16 MIPS a 16 MHz. - Funcionamiento esttico total.

- Multiplicador On-Chip de 2 ciclos

Memorias de programa y de datos no voltiles. - 32K bytes de FLASH reprogramable en sistema. Resistencia: 1.000 ciclos de escritura / borrado. - Seccin de cdigo aadida opcional con bits de bloqueo independientes. Programacin en sistema con el programa aadido On-Chip. Operacin de lectura durante la escritura. - 1024 bytes de EEPROM. Resistencia: 100.000 ciclos de escritura / borrado. - 2K bytes de SRAM interna. - Bloqueo (cerradura) programable para la seguridad del software. Interface JTAG. - Mantenimiento de eliminacin de errores On-Chip. - Programacin de FLASH, EEPROM, fusibles y bits de bloqueo a travs de la interface JTAG. - Capacidades de Boundary Scan de acuerdo con el Standard (norma) JTAG. Caractersticas de los perifricos. - Dos Timer/Contadores de 8 bits con prescaler separado y modo comparacin. - Un Timer/Contador de 16 bits con prescaler separado, modo comparacin y modo de captura. - Comparador analgico On-Chip. - Timer watchdog programable con oscilador separado On-Chip. - Interface serie SPI maestro/esclavo. - USART serie programable. - Contador en tiempo real con oscilador separado. - ADC de 10 bit y 8 canales. 8 canales de terminacin simple. 7 canales diferenciales slo en el encapsulado TQFP. 2 canales diferenciales con ganancia programable a 1x, 10x o 200x. - 4 canales de PWM. - Interface serie de dos hilos orientada a byte.

Caractersticas especiales del microcontrolador. - Reset de Power-on y deteccin de Brown-out programable. - Oscilador RC interno calibrado. - Fuentes de interrupcin externas e internas. - 6 modos de descanso: Idle, reduccin de ruido ADC, Power-save, Power-down, Standby y Standby extendido. I/O y encapsulados - 32 lneas de I/O programables. - PDIP de 40 pines, TQFP y MLF de 44 pines.

Tensiones de funcionamiento. - 2.7 - 5.5V (ATmega32L). - 4.5 - 5.5V (ATmega32). Niveles de velocidad. - 0 - 8 MHz (ATmega32L). - 0 - 16 MHz (ATmega32).

Caractersticas generales del ATmega64/64L

Microcontrolador AVR de 8 bit de alto rendimiento y bajo consumo. Arquitectura RISC avanzada. - 130 instrucciones. La mayora de un simple ciclo de clock de ejecucin. - 32 x 8 registros de trabajo de propsito general + registros de control perifricos. - Capacidad de procesamiento de unos 16 MIPS a 16 MHz. - Funcionamiento esttico total. - Multiplicador On-Chip de 2 ciclos

Memorias de programa y de datos no voltiles. - 64K bytes de FLASH reprogramable en sistema. Resistencia: 1.000 ciclos de escritura / borrado. - Seccin de cdigo aadida opcional con bits de bloqueo independientes. Programacin en sistema con el programa aadido On-Chip. Operacin de lectura durante la escritura. - 2K bytes de EEPROM. Resistencia: 100.000 ciclos de escritura / borrado. - 4K bytes de SRAM interna. - Hasta 64K bytes de espacio de memoria externa opcional.

- Bloqueo (cerradura) programable para la seguridad del software. - Interface SPI para la programacin en sistema. Interface JTAG. - Mantenimiento de eliminacin de errores On-Chip. - Programacin de FLASH, EEPROM, fusibles y bits de bloqueo a travs de la interface JTAG. - Capacidades de Boundary Scan de acuerdo con el Standard (norma) JTAG. Caractersticas de los perifricos. - Dos Timer/Contadores de 8 bits con prescaler separado y modo comparacin. - Dos Timer/Contadores extendidos de 16 bits con prescaler separado, modo comparacin y modo de captura. - Comparador analgico On-Chip. - Timer watchdog programable con oscilador separado On-Chip. - Interface serie SPI maestro/esclavo. - Doble USART serie programable. - Contador en tiempo real con oscilador separado. - ADC de 10 bit y 8 canales. 8 canales de terminacin simple 7 canales diferenciales 2 canales diferenciales con ganancia programable a 1x, 10x o 200x. - 2 canales de PWM de 8 bit. - 6 canales PWM con resolucin programable desde 1 a 16 bits. - Interface serie de dos hilos orientada a byte.

Caractersticas especiales del microcontrolador. - Reset de Power-on y deteccin de Brown-out programable. - Oscilador RC interno calibrado. - Fuentes de interrupcin externas e internas. - 6 modos de descanso: Idle, reduccin de ruido ADC, Power-save, Power-down, Standby y Standby extendido. - Frecuencia de clock seleccionable por software. - Modo de compatibilidad con el ATmega103 seleccionado por un fusible. - Pull-up global deshabilitado. I/O y encapsulados - 53 lneas de I/O programables. - TQFP de 64 pines y MLF de 64 pines. Tensiones de funcionamiento. - 2.7 - 5.5V (ATmega64L). - 4.5 - 5.5V (ATmega64). Niveles de velocidad.

- 0 - 8 MHz (ATmega64L). - 0 - 16 MHz (ATmega64).

Vous aimerez peut-être aussi

- 100 circuitos de shields para arduino (español)D'Everand100 circuitos de shields para arduino (español)Évaluation : 3.5 sur 5 étoiles3.5/5 (3)

- Simulación de circuitos electrónicos con OrCAD® PSpice®D'EverandSimulación de circuitos electrónicos con OrCAD® PSpice®Pas encore d'évaluation

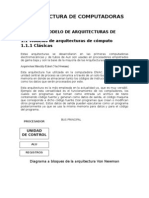

- Arquitectura de ComputadorasDocument53 pagesArquitectura de Computadorastilsma100% (3)

- Lenguaje Ensamblador Del Microprocesador PDFDocument54 pagesLenguaje Ensamblador Del Microprocesador PDFcacojl100% (1)

- Contador CanicasDocument8 pagesContador Canicasaioros2112Pas encore d'évaluation

- Introducción Al Psoc5Lp: Teoría y aplicaciones prácticaD'EverandIntroducción Al Psoc5Lp: Teoría y aplicaciones prácticaPas encore d'évaluation

- Manual Del At89c51Document9 pagesManual Del At89c51Asdrubal GonzalezPas encore d'évaluation

- Qué Operaciones de La Función Booleana 2 ExamenDocument6 pagesQué Operaciones de La Función Booleana 2 ExamenMarcos Alejandro Lopez Quintero0% (1)

- Avr Registros y InstruccionesDocument68 pagesAvr Registros y InstruccionesCarlosMarcial12Pas encore d'évaluation

- AT89C52 TablasDocument6 pagesAT89C52 TablasEdgar Mollinedo EscaleraPas encore d'évaluation

- LEDs rotativos con 8088 y TTLDocument7 pagesLEDs rotativos con 8088 y TTLMacs JazEsPas encore d'évaluation

- Microprocesador 8085Document9 pagesMicroprocesador 8085Martín LañónPas encore d'évaluation

- Caracteristicas Generales de 8085Document34 pagesCaracteristicas Generales de 8085Zabdiel Culebro HIpolitoPas encore d'évaluation

- Arquitectura del microprocesador Intel 8086 de 16 bitsDocument16 pagesArquitectura del microprocesador Intel 8086 de 16 bitsCastroPas encore d'évaluation

- Micro 8051Document14 pagesMicro 8051Hugo ReyesPas encore d'évaluation

- Microprocesador 8085Document16 pagesMicroprocesador 8085Martín LañónPas encore d'évaluation

- Programación de microcontroladores ATmega con división binariaDocument4 pagesProgramación de microcontroladores ATmega con división binariaAngelogc2014Pas encore d'évaluation

- Temporizadores Español AtmegaDocument77 pagesTemporizadores Español AtmegaHaslliEr HarrIson G. SeminArioPas encore d'évaluation

- Laboratorio de Sistemas Digitales 3Document12 pagesLaboratorio de Sistemas Digitales 3luisPas encore d'évaluation

- Induccion Microcontroladores PIC (Control Automatico Educacion) PDFDocument79 pagesInduccion Microcontroladores PIC (Control Automatico Educacion) PDFlord593Pas encore d'évaluation

- Clase 2 MICROPROCESADORES 8086 y 8088 - Registros, TerminalesDocument21 pagesClase 2 MICROPROCESADORES 8086 y 8088 - Registros, TerminalesMiltonPas encore d'évaluation

- Arquitectura interna del microprocesador 8086Document26 pagesArquitectura interna del microprocesador 8086tania alejandra mendezPas encore d'évaluation

- Realización Del Sistema de Control de Temperatura y HumedadDocument6 pagesRealización Del Sistema de Control de Temperatura y HumedadJose CordobaPas encore d'évaluation

- Microcontrolador 16F86Document13 pagesMicrocontrolador 16F86Flavio Gallegos HernandezPas encore d'évaluation

- Arquitectura Del Microprocesador z80Document5 pagesArquitectura Del Microprocesador z80manue1969Pas encore d'évaluation

- Análisis General de Un MicroprocesadorDocument20 pagesAnálisis General de Un MicroprocesadoroposeitorPas encore d'évaluation

- Microprocesador Z80Document8 pagesMicroprocesador Z80Eliuth Cruz CamarilloPas encore d'évaluation

- Set de Instrucciones 80C51Document2 pagesSet de Instrucciones 80C51ch3sshirePas encore d'évaluation

- Microprocesador 8080 ADocument7 pagesMicroprocesador 8080 AjavixojdnPas encore d'évaluation

- Marco Teorico 1Document13 pagesMarco Teorico 1André Cristhian Canales Canales MezaPas encore d'évaluation

- 5SB - Equipo 02 - Diagrama de ProcesadorDocument12 pages5SB - Equipo 02 - Diagrama de ProcesadorKenshin Ancona PerezPas encore d'évaluation

- Resumen de Caracteristicas Del Pic 16f887Document25 pagesResumen de Caracteristicas Del Pic 16f887PEdro CarvajalPas encore d'évaluation

- Guía Del Pic 16f84Document17 pagesGuía Del Pic 16f84b6dicPas encore d'évaluation

- PIC16F887Document17 pagesPIC16F887Juan Carlos Jaldin V100% (1)

- Informe 1111Document21 pagesInforme 1111Santi SevenfoldPas encore d'évaluation

- Arquitectura de Los Procesadores 8088 y 8086Document4 pagesArquitectura de Los Procesadores 8088 y 8086Carlos Andres100% (1)

- Manual ATMEGA 164PDocument16 pagesManual ATMEGA 164PFrancis SebastianPas encore d'évaluation

- Microprocesadores z80, 6800, 8086Document11 pagesMicroprocesadores z80, 6800, 8086Bryan Sagnay100% (1)

- Programar PLC 8E 8S PIC16F84Document5 pagesProgramar PLC 8E 8S PIC16F84Gaston Solorza LeyvaPas encore d'évaluation

- PIC16CXXDocument11 pagesPIC16CXXCarlos Ávila GómezPas encore d'évaluation

- PRACTICA 01: Operaciones Con Puertos I/O en EnsambladorDocument17 pagesPRACTICA 01: Operaciones Con Puertos I/O en EnsambladorAns Shel Cardenas YllanesPas encore d'évaluation

- Resumen Procesadores INTELDocument24 pagesResumen Procesadores INTELHéctor Concha FerxzPas encore d'évaluation

- Microprocesador 8085 características y partes internasDocument11 pagesMicroprocesador 8085 características y partes internasAdderly Chinchero TorresPas encore d'évaluation

- Lab 03 Puertos de Entrada y SalidaDocument15 pagesLab 03 Puertos de Entrada y SalidaJames Jerry YTPas encore d'évaluation

- Caracteristicas Principales Del Pic 16f887Document16 pagesCaracteristicas Principales Del Pic 16f887Douglas Joel ChaconPas encore d'évaluation

- Laboratorio de Sistemas Digitales 3Document12 pagesLaboratorio de Sistemas Digitales 3luisPas encore d'évaluation

- PIC18F4550Document19 pagesPIC18F4550luzPas encore d'évaluation

- Arquitectura Del Procesador y Organización Interna de La MemoriaDocument17 pagesArquitectura Del Procesador y Organización Interna de La MemoriaAndres RomeroPas encore d'évaluation

- Consulta 5 AyalaDocument7 pagesConsulta 5 AyalaEDSON MISAEL RODR�GUEZ GARC�APas encore d'évaluation

- Pic 16 F628Document23 pagesPic 16 F628Ariel Godoy67% (3)

- PIC16F84ADocument25 pagesPIC16F84AGerardo GonzalezPas encore d'évaluation

- Arquitectura de Los Procesadores 8088 y 8086Document3 pagesArquitectura de Los Procesadores 8088 y 8086Rodrigo Ortolá InocentiPas encore d'évaluation

- Pic 18 F 45506 Ago 2013Document50 pagesPic 18 F 45506 Ago 2013josuemxPas encore d'évaluation

- Práctica de laboratorio con PIC16F84ADocument25 pagesPráctica de laboratorio con PIC16F84AArmandinho Colque VargasPas encore d'évaluation

- Charla 1 de MicroprocesadoresDocument34 pagesCharla 1 de Microprocesadoresagustin cordobaPas encore d'évaluation

- Procesador z80Document15 pagesProcesador z80Abraham Contreras100% (1)

- El Microprocesador y Su Arquitectura PDFDocument46 pagesEl Microprocesador y Su Arquitectura PDFGonzalo Rojo PadillaPas encore d'évaluation

- Cuestionario MicroprocesadoresDocument6 pagesCuestionario MicroprocesadoresGénesisAndrimarPas encore d'évaluation

- 8085 Cas18Document50 pages8085 Cas18Carlos Javier BarriosPas encore d'évaluation

- Microcontrolador PIC16F887Document21 pagesMicrocontrolador PIC16F887Marving Velásquez RivasPas encore d'évaluation

- SPARC Arquitectura II: Introducción a SPARCDocument29 pagesSPARC Arquitectura II: Introducción a SPARCpelado27Pas encore d'évaluation

- Proton - Ucting.udg - MX Dpto Maestros Mateos z80 ArquitectuDocument7 pagesProton - Ucting.udg - MX Dpto Maestros Mateos z80 Arquitectusanchez2328Pas encore d'évaluation

- Intel 8080Document12 pagesIntel 8080Carlos MonteroPas encore d'évaluation

- Tesis GonzalezDocument121 pagesTesis GonzalezReynaldo ChuraPas encore d'évaluation

- 1.4 Caracter¡sticas Del Derecho ConstitucionalDocument6 pages1.4 Caracter¡sticas Del Derecho ConstitucionalMiguel AngelPas encore d'évaluation

- Red Integrada InformeDocument14 pagesRed Integrada InformeJhenrry C CHPas encore d'évaluation

- Aspectos Generales de La AutomatizaciónDocument17 pagesAspectos Generales de La AutomatizaciónRama UniNortePas encore d'évaluation

- Modelo Von NeumannDocument20 pagesModelo Von NeumannJesssssica11Pas encore d'évaluation

- Prácticas de Electrónica BásicaDocument22 pagesPrácticas de Electrónica BásicaJMPas encore d'évaluation

- Diploma Compu JemDocument13 pagesDiploma Compu JemELVIS ALBERTO OCHOA DÍAZPas encore d'évaluation

- Amplificador de AudioDocument5 pagesAmplificador de AudioLidaPas encore d'évaluation

- Final 5 Digitales 1Document19 pagesFinal 5 Digitales 1Victor Manuel CanahuiriPas encore d'évaluation

- Informe de ProgramacionDocument45 pagesInforme de ProgramacionLarry GarciaPas encore d'évaluation

- Tarea 2-GarciaDocument22 pagesTarea 2-GarciaCarlos Charly XPPas encore d'évaluation

- Alejandro Navarro Rojas Control5 ElectronicaIIDocument5 pagesAlejandro Navarro Rojas Control5 ElectronicaIIAlejandro Navarro RojasPas encore d'évaluation

- SD SES010 Analis Sist SecDocument32 pagesSD SES010 Analis Sist SecMiguel CuyaPas encore d'évaluation

- INFORME DIGITALES Practica 3 DecodificadorDocument9 pagesINFORME DIGITALES Practica 3 DecodificadorAlex Andrade100% (2)

- S3 Sistemas Combinacionales Con Compuertas LógicasDocument13 pagesS3 Sistemas Combinacionales Con Compuertas Lógicasantony bustamante100% (1)

- Tutor WinDocument10 pagesTutor WinNelsson AlvarezPas encore d'évaluation

- Curvas V-I BJT Emisor ComúnDocument9 pagesCurvas V-I BJT Emisor ComúnNoé VázquezPas encore d'évaluation

- Registros de CorrimientoDocument7 pagesRegistros de CorrimientoXimenaRenteríaPas encore d'évaluation

- Compuertas lógicas NAND, NOR, XOR y XNORDocument9 pagesCompuertas lógicas NAND, NOR, XOR y XNORjuancastrillonPas encore d'évaluation

- Informe 3-LaboDocument12 pagesInforme 3-LaboRonal HbPas encore d'évaluation

- Introducción a la electrónica digital y sistemas lógicos programablesDocument3 pagesIntroducción a la electrónica digital y sistemas lógicos programablesEdward FlorianPas encore d'évaluation

- GARANTIAS Y ARTÍCULOS DE PC A LA VENTADocument6 pagesGARANTIAS Y ARTÍCULOS DE PC A LA VENTAFelipe RivasPas encore d'évaluation

- Familias LógicasDocument6 pagesFamilias LógicasJonathan Sandoval FernándezPas encore d'évaluation

- Practica 7Document4 pagesPractica 7Solis Alfredo JosePas encore d'évaluation

- Informe 2 de AutomatizacionDocument21 pagesInforme 2 de AutomatizacionWilliam CardenasPas encore d'évaluation

- Preparatorio Lab DigitalesDocument9 pagesPreparatorio Lab DigitalesLaura VizcaínoPas encore d'évaluation

- Historia de Los MicrocontroladoresDocument3 pagesHistoria de Los MicrocontroladoresYolanda Chavez LopezPas encore d'évaluation

- Puertas lógicas, relés y PLCDocument27 pagesPuertas lógicas, relés y PLCjuan mezaPas encore d'évaluation

- Memoria Mapa MemoriaDocument3 pagesMemoria Mapa MemoriaJorge CañazacaPas encore d'évaluation

- Taller #1Document11 pagesTaller #1libyrodriguez123Pas encore d'évaluation

- Informe Previo N2 Microelectronica UnmsmDocument11 pagesInforme Previo N2 Microelectronica UnmsmRussell Oscar QFPas encore d'évaluation