Académique Documents

Professionnel Documents

Culture Documents

Arhitectura Calculatoarelor - Proc-Intel

Transféré par

ioana0simionCopyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

Arhitectura Calculatoarelor - Proc-Intel

Transféré par

ioana0simionDroits d'auteur :

Formats disponibles

138

Arhitectura calculatoarelor

n multe cazuri, este mai eficient realizarea transferurilor direct ntre periferic i memorie. n aceste cazuri, UCP acord unui modul de I/E permisiunea de citire din sau scriere n memorie, astfel c transferurile pot avea loc fr interveniei UCP. Aceast operaie se numete acces direct la memorie (DMA).

4.5. Procesoarele Intel

Firma Intel a fost cea care a proiectat primul microprocesor, n anul 1969. Acesta a fost microprocesorul 4004, de 4 bii. Au urmat apoi microprocesoarele de 8 bii 8080 i 8085. Primul procesor al familiei 80x86 (numit i familia cu arhitectura Intel Intel Architecture) a fost ns procesorul 8086, care a aprut n 1978, fiind urmat n scurt timp de o versiune mai ieftin pentru sisteme mai simple, procesorul 8088. Programele scrise pentru aceste procesoare pot fi executate fr modificri i pe ultimele procesoare ale familiei 80x86.

4.5.1. Prezentare general a procesoarelor Intel

8086 i 8088 Procesorul 8086 are registre de 16 bii, o magistral extern de date de 16 bii, i o magistral de adrese de 20 de bii, astfel c spaiul de adresare este de maxim 1 MB. Procesorul 8088 este similar, cu excepia faptului c magistrala extern de date este de 8 bii. Aceste procesoare au introdus conceptul de segmentare a memoriei: memoria este mprit n zone numite segmente de maxim 64 KB, iar cele patru registre de segment pot pstra adresele de baz ale segmentelor active. Prin utilizarea registrelor de segment poate fi adresat un spaiu de memorie de pn la 256 KB fr modificarea coninutului acestor registre, fiind disponibil un spaiu total de memorie de 1 MB. Aceste procesoare pot funciona numai n modul real, care este un mod uniproces, n care se execut un singur proces (program sau task) la un moment dat. Din punct de vedere al programatorului, cele dou procesoare sunt identice, cu excepia faptului c 8086 va prelucra datele ntr-un mod mai eficient dac acestea sunt aliniate la adrese de cuvnt (adrese pare). 80186 i 80188 Procesoarele 80186 i 80188 sunt versiuni mbuntite ale procesoarelor 8086, respectiv 8088. Au fost adugate noi instruciuni i anumite instruciuni vechi au fost optimizate pentru creterea vitezei. Aceste procesoare conin n aceeai capsul i circuite suplimentare: un generator de tact, un controler DMA cu dou canale, trei numrtoare/temporizatoare programabile, i un controler de ntreruperi, care poate gestiona patru surse externe de ntrerupere.

4. Unitatea central de prelucrare 80286

139

Procesorul 80286 poate funciona n modul real al procesoarelor precedente, dar dispune i de un mod de adresare virtual sau mod protejat. Acest mod utilizeaz coninutul registrelor de segment ca selectori sau pointeri n tabele ale descriptorilor de segment. Descriptorii furnizeaz adrese de baz de 24 de bii, permind adresarea unei memorii fizice de pn la 16 MB. Procesorul dispune de o unitate de gestiune a memoriei virtuale, cu care poate translata adrese pentru o memorie virtual de 1 GB n spaiul adreselor fizice de 16 MB. n modul protejat, procesorul poate funciona n regim multi-proces (multitasking), n care pot fi executate mai multe procese n mod concurent. n acest mod se realizeaz o comutare prin hardware ntre procesele care se execut concurent. Memoria utilizat de fiecare proces este protejat fa de aciunile altor procese. Pentru aceasta procesorul dispune de diferite mecanisme de protecie. Acestea cuprind testarea limitelor segmentelor, existena atributelor de segment care permit doar citirea coninutului unui segment sau doar execuia codului din acel segment, i pn la patru nivele de privilegiu pentru protecia codului sistemului de operare de programele de aplicaii sau de programele utilizatorului. Existena unor tabele ale descriptorilor locali de segment permite sistemului de operare protejarea ntre ele a programelor de aplicaii sau a programelor utilizatorului. Sunt disponibile instruciuni privilegiate suplimentare pentru setarea modului protejat i controlul proceselor multiple. 80386 Procesorul 80386 a introdus n cadrul arhitecturii Intel registre de 32 de bii, utilizate att pentru pstrarea datelor, ct i pentru adresare. Pentru compatibilitate cu procesoarele anterioare, aceste registre s-au obinut prin extinderea registrelor de 16 bii, fiind posibil utilizarea n continuare a vechilor registre, acestea constituind jumtatea de ordin inferior a registrelor de 32 de bii. A fost introdus un nou mod de funcionare, numit mod virtual 8086, care permite execuia mai eficient a programelor scrise pentru procesoarele 8086 i 8088 pe noul procesor de 32 de bii. Magistrala extern de adrese a fost extins la 32 de bii, spaiul adreselor fizice fiind astfel de 4 GB. Spaiul adreselor virtuale este de 64 TB. Dimensiunea fiecrui segment nu mai este limitat la 64 KB, dimensiunea maxim a unui segment fiind de 4 GB. Instruciunile originale au fost extinse cu noi forme care utilizeaz operanzi i adrese de 32 de bii, i au fost introduse instruciuni complet noi, ca de exemplu instruciuni pentru operaii la nivel de bit. Procesorul 80386 a introdus de asemenea mecanismul de paginare ca metod de gestiune a memoriei virtuale, dimensiunea fix de 4 KB a paginilor de memorie asigurnd o eficien mai ridicat comparativ cu utilizarea segmentelor, metoda fiind complet transparent pentru programele de aplicaii, fr o reducere semnificativ a vitezei de execuie. n plus, posibilitatea definirii segmentelor avnd dimensiunea maxim a spaiului adreselor fizice de 4 GB, mpreun cu paginarea, au permis introducerea modelului protejat de adresare liniar n cadrul arhitecturii, n care este necesar

140

Arhitectura calculatoarelor

o singur component a adresei pentru accesul la ntregul spaiu de adresare al memoriei. Acest model este utilizat i de sistemul de operare UNIX. Procesorul 80386 a fost primul din cadrul familiei 80x86 care a utilizat o form de prelucrare paralel. Arhitectura acestui procesor cuprinde un numr de ase uniti care funcioneaz n paralel. Acestea sunt urmtoarele: Unitatea de interfa cu magistrala, care realizeaz accesul la memorie i la dispozitivele de I/E; Unitatea de ncrcare a instruciunilor, care primete codul instruciunilor de la unitatea de interfa cu magistrala i le depune ntr-o coad de 16 octei; Unitatea de decodificare a instruciunilor, care decodific codul obiect al instruciunilor i genereaz un microcod pentru execuia acestora; Unitatea de execuie, care execut microcodul corespunztor fiecrei instruciuni; Unitatea de segmentare, care translateaz adresele logice n adrese liniare i efectueaz testele necesare proteciei; Unitatea de paginare, care translateaz adresele liniare n adrese fizice, efectueaz testele necesare proteciei paginilor de memorie i conine o memorie cache cu informaii despre pn la 32 de pagini cel mai recent accesate. 80486 Procesorul 80486 a extins posibilitile de execuie paralel a instruciunilor, n principal prin extinderea unitilor de decodificare a instruciunilor i de execuie ale procesorului 80386 n cinci etaje de tip pipeline, fiecare etaj opernd n paralel cu celelalte asupra a cinci instruciuni aflate n diferite faze de execuie. Fiecare etaj poate termina prelucrrile pe care le efectueaz asupra unei instruciuni ntr-o perioad de tact, astfel nct procesorul 80486 poate executa cte o instruciune n fiecare perioad de tact. Procesorului i s-a adugat o memorie cache de nivel 1 (L1 Level 1) de 8 KB pentru a crete n mod semnificativ procentul instruciunilor care se pot executa la rata de o instruciune ntr-o perioad de tact: astfel, i instruciunile cu acces la memorie se pot executa la aceast rat, dac operanzii acestora se afl n memoria cache L1. Procesorul 80486 a fost primul din familia 80x86 la care unitatea de calcul n virgul mobil a fost integrat n acelai circuit cu unitatea central. Au fost adugai de asemenea noi pini i noi instruciuni care permit realizarea unor sisteme mai complexe: sisteme multiprocesor i sisteme care conin o memorie cache de nivel 2 (L2 Level 2). Au fost dezvoltate versiuni ale procesorului 80486 n care au fost incluse faciliti pentru reducerea consumului de putere, ca i alte faciliti de gestiune a sistemului. Procesorul 80386 SL a fost de fapt primul care coninea asemenea faciliti, acestea fiind extinse apoi la procesoarele 80486 SL i 80486 SL Enhanced, care au fost utilizate pentru realizarea calculatoarelor notebook. Una din aceste faciliti

4. Unitatea central de prelucrare

141

este noul mod de gestiune a sistemului (System Management Mode SMM), pentru care s-a prevzut un pin dedicat de ntrerupere. Acest mod permite operaii complexe de gestiune a sistemului (ca de exemplu gestiunea puterii consumate de diferitele subsisteme ale calculatorului), ntr-un mod transparent pentru sistemul de operare i pentru programele de aplicaii. Facilitile numite Stop Clock i Auto Halt Powerdown permit funcionarea unitii centrale la o frecven redus a tactului pentru reducerea puterii consumate, sau chiar oprirea funcionrii (cu memorarea strii). Pentium Procesorul Pentium a adugat o nou linie de execuie de tip pipeline a instruciunilor, pentru a se obine performane superscalare. Cele dou linii de execuie a instruciunilor, numite u i v, permit execuia a dou instruciuni pe durata unei perioade de tact. Capacitatea memoriei cache L1 a fost de asemenea dublat, fiind alocai 8 KB pentru instruciuni i 8 KB pentru date. Memoria cache pentru date utilizeaz protocolul MESI, care permite gestiunea memoriei cache att prin metoda mai eficient write-back, ct i prin metoda write-through utilizat de procesorul 80486. Procesorul Pentium utilizeaz predicia salturilor pentru a crete performanele construciilor care utilizeaz bucle de program. S-au adugat extensii pentru a crete eficiena modului virtual 8086, i pentru a permite att pagini cu dimensiunea de 4 MB, ct i cu dimensiunea de 4 KB. Registrele generale sunt tot de 32 de bii, dar s-au adugat ci interne de date de 128 i 256 de bii pentru a crete viteza transferurilor interne, iar magistrala extern de date a fost extins la 64 de bii. Procesorului i s-a adugat un controler avansat de ntreruperi (Advanced Programmable Interrupt Controller APIC) pentru a permite realizarea sistemelor cu mai multe procesoare Pentium, fiind adugate de asemenea noi pini i un mod special de procesare dual pentru sistemele cu dou procesoare. Pentium Pro Procesorul Pentium Pro este primul din cadrul familiei de procesoare P6. Acest procesor are o arhitectur superscalar mbuntit, care permite execuia a trei instruciuni ntr-o perioad de tact. Procesorul Pentium Pro, ca i urmtoarele procesoare din familia P6, se caracterizeaz prin execuia dinamic a instruciunilor, care const din analiza fluxului de date, execuia instruciunilor ntr-o alt ordine dect cea secvenial, o predicie mbuntit a salturilor i execuia speculativ. Exist trei uniti de decodificare a instruciunilor, care lucreaz n paralel pentru decodificarea codului obiect n operaii elementare numite micro-operaii. Acestea sunt depuse ntr-un rezervor de instruciuni, i pot fi executate ntr-o ordine diferit de cea secvenial dac nu exist dependene de date. Execuia se realizeaz de ctre cele cinci uniti paralele de execuie: dou uniti pentru numere ntregi, dou uniti pentru numere n virgul mobil, i o unitate de interfa cu memoria. Unitatea de retragere (Retirement Unit) elimin din rezervorul de instruciuni micro-operaiile care au fost

142

Arhitectura calculatoarelor

executate, innd cont de salturile posibile. Pe lng cele dou memorii cache L1 de cte 8 KB, prezente i la procesorul Pentium, procesorul Pentium Pro dispune i de o memorie cache L2 de 256 KB, aflat n acelai circuit cu unitatea central, conectat cu aceasta printr-o magistral dedicat de 64 de bii. Memoria cache L1 are porturi duale (dou porturi de acces), iar memoria cache L2 permite pn la 4 accesuri concurente. Magistrala extern de date este orientat pe tranzacii, ceea ce nseamn c fiecare acces este tratat ca o cerere i un rspuns separat, fiind permise mai multe cereri n timp ce se ateapt un rspuns. Aceste caracteristici de acces paralel la date, mpreun cu posibilitile de execuie paralel a instruciunilor asigur creterea gradului de utilizare a procesorului i mbuntirea performanelor. Procesorul Pentium Pro are o magistral de adrese extins la 36 de bii, astfel nct spaiul adreselor fizice este de pn la 64 GB. Pentium II Procesorul Pentium II se bazeaz pe arhitectura Pentium Pro, la care s-au adugat extensiile MMX (Multimedia Extensions). La acest procesor s-au utilizat noile tehnici de ncapsulare numite Slot 1 i Slot 2. n cazul acestor tehnici, n locul unui soclu se utilizeaz un conector. Memoria cache L2 a fost mutat n afara capsulei procesorului. Att memoria cache L1 pentru date, ct i memoria cache L1 pentru instruciuni au fost extinse la 16 KB fiecare. Dimensiunea memoriei cache L2 poate fi de 256 KB, 512 KB, 1 MB sau 2 MB (numai cu tehnica Slot 2). Procesorul cu Slot 1 utilizeaz pentru comunicaia cu memoria cache L2 o magistral care funcioneaz la o frecven egal cu jumtatea frecvenei de tact a procesorului, n timp ce n cazul procesorului cu Slot 2 aceast frecven este egal cu frecvena de tact a procesorului. Procesorul Pentium II utilizeaz diferite stri cu consum redus de putere, ca de exemplu AutoHALT, Stop-Grant, Sleep i Deep Sleep, pentru reducerea puterii consumate n perioadele de inactivitate. Pentium III Acest procesor este ultimul din cadrul familiei P6, i se bazeaz pe arhitecturile procesoarelor Pentium Pro i Pentium II. Au fost adugate 70 de noi instruciuni la setul de instruciuni existent. Acestea sunt destinate att unitilor funcionale existente la procesoarele precedente, ct i noii uniti de calcul n virgul mobil de tip SIMD (Single Instruction, Multiple Data).

4.5.2. Microarhitectura procesoarelor din familia P6

4.5.2.1. Prezentare general a microarhitecturii

Microarhitectura procesoarelor din familia P6 este una superscalar cu trei ci. Aceasta nseamn c, prin utilizarea tehnicilor de prelucrare paralel, procesorul

4. Unitatea central de prelucrare

143

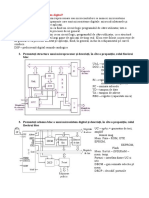

poate decodifica i executa n medie trei instruciuni n fiecare ciclu de ceas. Pentru a obine aceast rat de execuie a instruciunilor, procesoarele din familia P6 utilizeaz o cale de date de tip pipeline cu 12 etaje, care permite execuia instruciunilor ntr-o ordine diferit de cea specificat n program. Figura 4.11 prezint structura acestei ci de date, care este mprit n patru uniti de prelucrare: unitatea de extragere i decodificare, unitatea de expediere i execuie, unitatea de retragere i rezervorul de instruciuni. Instruciunile i datele sunt transmise acestor uniti prin unitatea de interfa cu magistrala.

Figura 4.11. Unitile de prelucrare din microarhitectura procesoarelor din familia P6 i interfaa acestora cu subsistemul de memorie.

Pentru a asigura furnizarea constant a instruciunilor i datelor la unitile de execuie din calea de date, microarhitectura utilizeaz dou nivele de memorie cache. Memoria cache L1 este mprit ntr-o memorie cache de 8 KB pentru instruciuni i o memorie cache de 8 KB pentru date, ambele integrate n calea de date. Memoria cache L2 este o memorie RAM static de 256 KB, 512 KB sau 1 MB, care este conectat la calea de date printr-o magistral de 64 de bii, funcionnd la frecvena de ceas a procesorului. Microarhitectura procesoarelor din familia P6 utilizeaz execuia dinamic a instruciunilor. Mecanismul de execuie dinamic cuprinde trei concepte:

144 Predicia salturilor;

Arhitectura calculatoarelor

Analiza dinamic a fluxului de date; Execuia speculativ. Predicia salturilor este un concept ntlnit la majoritatea arhitecturilor performante de calculatoare i a microprocesoarelor de vitez ridicat. Acest concept permite procesorului decodificarea instruciunilor de dup cele de salt pentru a nu goli calea de date pipeline la execuia instruciunilor de salt. Unitatea de extragere i decodificare a instruciunilor utilizeaz un algoritm de predicie optimizat pentru anticiparea direciei fluxului de instruciuni prin nivele multiple de salturi, apeluri de proceduri i reveniri din proceduri. Analiza dinamic a fluxului de date implic analiza n timp real a fluxului datelor prin procesor pentru a determina dependena datelor i a registrelor, i pentru a detecta posibilitatea execuiei instruciunilor ntr-o ordine diferit de cea specificat n program. Unitatea de expediere i execuie a instruciunilor poate monitoriza simultan mai multe instruciuni i poate executa aceste instruciuni ntr-o ordine n care se optimizeaz utilizarea unitilor multiple de execuie ale microarhitecturii, meninnd n acelai timp integritatea datelor asupra crora se opereaz. Aceast ordine de execuie asigur ocuparea unitilor de execuie chiar i atunci cnd apar dependene ntre datele instruciunilor. Execuia speculativ se refer la posibilitatea procesorului de a executa instruciuni aflate naintea instruciunii adresate de contorul de program, i de a furniza rezultatele n ordinea irului iniial de instruciuni. Pentru ca execuia speculativ s fie posibil, microarhitectura familiei P6 separ expedierea i execuia instruciunilor de producerea rezultatelor. Unitatea de expediere i execuie a instruciunilor utilizeaz analiza fluxului de date pentru a executa toate instruciunile din rezervorul de instruciuni i a memora rezultatele n registre temporare. Unitatea de retragere a instruciunilor caut apoi instruciunile care au fost executate i pentru care nu mai exist dependene de date cu alte instruciuni sau predicii nerezolvate ale salturilor. Atunci cnd se gsesc instruciuni care au fost executate, unitatea de retragere a instruciunilor depune rezultatele acestor instruciuni n memorie sau n registrele microarhitecturii (cele opt registre ale procesorului i opt registre ale unitii de calcul n virgul mobil), n ordinea specificat n program, i retrage aceste instruciuni din rezervorul de instruciuni.

4.5.2.2. Prezentare detaliat a microarhitecturii

Figura 4.12 prezint o schem bloc funcional a microarhitecturii procesoarelor din familia P6.

4. Unitatea central de prelucrare

145

Figura 4.12. Schema bloc funcional a microarhitecturii procesoarelor din familia P6.

n aceast schem, exist urmtoarele blocuri componente ale celor patru uniti de execuie i a subsistemului de memorie din Figura 4.11: Subsistemul de memorie: magistrala sistem, memoria cache L2, unitatea de interfa cu magistrala, memoria cache L1 de instruciuni, memoria cache L1 de date, unitatea de interfa cu memoria i bufferul de reordonare al memoriei. Unitatea de extragere i decodificare: unitatea de extragere a instruciunilor, bufferul pentru destinaia salturilor (BTB Branch Target Buffer), decodificatorul de instruciuni, secveniatorul microcodului i tabela de pseudonime a registrelor (Register Alias Table).

146

Arhitectura calculatoarelor Rezervorul de instruciuni: bufferul de reordonare. Unitatea de expediere i execuie: staia de rezervare, dou uniti de calcul pentru numere ntregi, dou uniti de calcul n virgul mobil i dou uniti de generare a adreselor. Unitatea de retragere a instruciunilor: unitatea de retragere i setul de registre al arhitecturii Intel. Subsistemul de memorie

Subsistemul de memorie al microarhitecturii P6 este format din memoria principal a sistemului, memoria cache primar (L1) i memoria cache secundar (L2). Unitatea de interfa cu magistrala acceseaz memoria sistemului prin magistrala sistemului (extern). Aceast magistral de 64 de bii este o magistral orientat pe tranzacii, ceea ce nseamn c fiecare acces la magistral este tratat prin operaii separate de cerere i rspuns. n timp ce unitatea de interfa cu magistrala ateapt rspunsul la o cerere de acces la magistral, se pot emite alte cereri. Unitatea de interfa cu magistrala acceseaz memoria cache L2 printr-o magistral de 64 de bii a memoriei cache. Aceast magistral este de asemenea orientat pe tranzacii, permind pn la patru accese concurente la memoria cache, i funcioneaz la aceeai frecven de ceas ca i procesorul. Accesul la memoria cache L1 se realizeaz prin magistrale interne, de asemenea la frecvena de ceas a procesorului. Memoria cache L1 de 8 KB pentru instruciuni este un set asociativ cu patru ci. Memoria cache L1 de 8 KB pentru date este un set asociativ cu dou ci, avnd dou porturi, i permite o operaie de ncrcare i una de memorare ntr-un ciclu. Coerena ntre memoriile cache i memoria sistemului este asigurat prin utilizarea protocolului MESI (Modified, Exclusive, Shared, Invalid). Acest protocol este utilizat pentru asigurarea coerenei ntre memoriile cache att la sistemele cu un singur procesor, ct i la cele multiprocesor. Cererile de acces la memorie de la unitile de execuie ale procesorului trec prin unitatea de interfa cu memoria i prin bufferul de reordonare al memoriei. n cazul unei lipse n memoria cache L1 pentru date, aceast memorie redirecteaz cererea ctre memoria cache L2, i apoi, n cazul unei lipse n aceast memorie, unitatea de interfa cu magistrala redirecteaz cererea ctre memoria sistemului. Cererile de acces la memoria cache L2 sau la memoria sistemului trec prin bufferul de reordonare al memoriei, care funcioneaz ca o staie de planificare i expediie. Aceast unitate pstreaz evidena tuturor cererilor de acces la memorie i poate reordona anumite cereri pentru a preveni blocajele i a mbunti rata de transfer. De exemplu, bufferul de reordonare al memoriei permite operaii speculative de ncrcare. (Operaiile de memorare sunt executate ntotdeauna n ordinea iniial, iar operaiile speculative de memorare nu sunt permise.)

4. Unitatea central de prelucrare Unitatea de extragere i decodificare

147

Unitatea de extragere i decodificare citete un ir de instruciuni din memoria cache L1 de instruciuni i le decodific ntr-o serie de micro-operaii. Acest ir de micro-operaii este transmis apoi la rezervorul de instruciuni. Unitatea de extragere a instruciunilor ncarc n fiecare ciclu de ceas o linie de 32 de octei din memoria cache de instruciuni. Unitatea marcheaz nceputul i sfritul instruciunilor n cadrul liniilor memoriei cache i transmite 16 octei aliniai la decodificatorul de instruciuni. Unitatea de extragere a instruciunilor calculeaz valoarea pointerului de instruciuni, pe baza intrrilor de la bufferul pentru destinaia salturilor, a strii excepiilor i a ntreruperilor. Pentru a executa predicia salturilor, bufferul pentru destinaia salturilor, cu 512 intrri, urmrete un numr mare de instruciuni aflate naintea contorului de program. n cadrul acestor instruciuni pot fi numeroase salturi, apeluri de proceduri i reveniri din proceduri, care trebuie anticipate n mod corect. Decodificatorul de instruciuni conine trei decodificatoare: dou decodificatoare pentru instruciuni simple i un decodificator pentru instruciuni complexe. Fiecare decodificator convertete o instruciune ntr-una sau mai multe micro-operaii, fiecare avnd dou surse logice i o destinaie logic. Micro-operaiile sunt instruciuni primitive care sunt executate n unitile paralele de execuie ale procesorului. Multe instruciuni ale procesorului sunt convertite direct n cte o singur micro-operaie de ctre decodificatoarele pentru instruciuni simple, iar anumite instruciuni sunt decodificate ntr-un numr de pn la patru micro-operaii. Instruciunile mai complexe sunt decodificate n secvene programate de micro-operaii obinute de la secveniatorul microcodului. Decodificatoarele de instruciuni realizeaz de asemenea decodificarea prefixelor de instruciuni i a operaiilor de ciclare. Aceste decodificatoare pot genera pn la ase micro-operaii pe ciclu de ceas (cte una de ctre decodificatoarele pentru instruciuni simple i patru de ctre decodificatoarele pentru instruciuni complexe). Setul de registre al procesorului poate cauza blocaje din cauza dependenelor ntre registre. Pentru a rezolva aceast problem, procesorul dispune de 40 de registre interne, care se utilizeaz pentru calcule. Aceste registre pot pstra att valori ntregi, ct i valori n virgul mobil. Pentru alocarea registrelor interne, micro-operaiile de la decodificatorul de instruciuni sunt transmise la tabela de pseudonime ale registrelor, unde referinele logice la registrele procesorului sunt convertite n referine fizice la registrele interne. In etapa final a procesului de decodificare, alocatorul din cadrul tabelei de pseudonime ale registrelor adaug bii de stare la micro-operaii pentru a le pregti n vederea execuiei ntr-o ordine diferit de cea secvenial, i transmite micro-operaiile rezultate la rezervorul de instruciuni. Rezervorul de instruciuni naintea depunerii micro-operaiilor n rezervorul de instruciuni (cunoscut i sub numele de buffer de reordonare), irul de instruciuni decodificat n micro-operaii

148

Arhitectura calculatoarelor

se afl n aceeai ordine cu cea n care acest ir a fost transmis la decodificatorul de instruciuni. Bufferul de reordonare este o memorie asociativ organizat n 40 de registre. Bufferul conine micro-operaii care ateapt pentru a fi executate, ca i microoperaii care au fost deja executate, dar ale cror rezultate nu au fost nc memorate. Unitatea de expediere i execuie poate executa micro-operaiile din bufferul de reordonare n orice ordine. Unitatea de expediere i execuie Unitatea de expediere i execuie planific i execut micro-operaiile depuse n bufferul de reordonare innd cont de dependenele de date i de disponibilitatea resurselor, i memoreaz temporar rezultatele acestor execuii speculative. Planificarea i expedierea micro-operaiilor din bufferul de reordonare este realizat de staia de rezervare. Aceasta urmrete n continuu bufferul de reordonare pentru a determina micro-operaiile care sunt gata de execuie (cele pentru care toi operanzii surs sunt disponibili) i le expediaz pe acestea la unitile de execuie disponibile. Rezultatele execuiei unei micro-operaii sunt returnate n bufferul de reordonare i sunt memorate mpreun cu micro-operaia pn cnd aceasta este retras din buffer. Acest proces de planificare i expediere permite execuia ntr-o ordine oarecare, n care micro-operaiile sunt expediate la unitile de execuie strict pe baza constrngerilor fluxului de date i a disponibilitii resurselor utilizate pentru execuie, fr a ine cont de ordinea iniial a instruciunilor. Execuia micro-operaiilor este realizat de dou uniti n virgul fix (VF), dou uniti pentru numere n virgul mobil (VM) i o unitate de interfa cu memoria, permind planificarea a pn la cinci micro-operaii ntr-un ciclu de ceas. Cele dou uniti n virgul fix pot executa n paralel dou micro-operaii pentru numere ntregi. Una din unitile n virgul fix poate gestiona micro-operaiile de salt. Aceast unitate poate detecta prediciile eronate ale salturilor i poate semnala bufferului pentru destinaia salturilor s iniializeze calea de date pipeline. Aceast operaie este realizat dup cum urmeaz. Decodificatorul de instruciuni marcheaz fiecare micro-operaie de salt cu ambele adrese posibile de destinaie ale saltului (adresa de salt i adresa instruciunii urmtoare). Atunci cnd unitatea n virgul fix execut micro-operaia de salt, aceasta este n msur s determine destinaia care a fost selectat. Dac destinaia anticipat a fost selectat, atunci micro-operaiile executate speculativ sunt marcate ca fiind utilizabile i execuia continu pe calea anticipat. Dac destinaia anticipat nu a fost selectat, o unitate de execuie din cadrul unitii n virgul fix modific starea tuturor micro-operaiilor de pe calea care nu a fost selectat pentru a le elimina din rezervorul de instruciuni. Unitatea respectiv transmite apoi destinaia corect a saltului la bufferul pentru destinaia salturilor, care iniializeaz calea de date pipeline de la noua adres. Unitatea de interfa cu memoria gestioneaz micro-operaiile de ncrcare i de memorare. Un acces de ncrcare necesit specificarea doar a adresei de memorie, astfel nct poate fi codificat ntr-o micro-operaie. Un acces de memorare necesit specificarea att a adresei, ct i a datei, astfel nct este codificat n dou micro-

4. Unitatea central de prelucrare

149

operaii. Partea unitii de interfa cu memoria care gestioneaz micro-operaiile de memorare dispune de dou porturi, ceea ce i permite prelucrarea n paralel a celor dou micro-operaii care codific accesul de memorare. Unitatea de interfa cu memoria poate executa deci n paralel att o ncrcare, ct i o memorare ntr-un ciclu de ceas. Unitatea de retragere a instruciunilor Unitatea de retragere a instruciunilor memoreaz n mod permanent rezultatele micro-operaiilor executate speculativ i elimin micro-operaiile din bufferul de reordonare. Ca i staia de rezervare, unitatea de retragere a instruciunilor testeaz n mod continuu starea micro-operaiilor din bufferul de reordonare, cutnd acele micro-operaii care au fost executate i nu au dependene cu alte micro-operaii din rezervorul de instruciuni. Aceast unitate retrage apoi micro-operaiile executate n ordinea iniial specificat n program, innd cont de ntreruperi, excepii i anticipri eronate ale salturilor. Unitatea de retragere a instruciunilor poate retrage trei micro-operaii pe ciclu de ceas. Pentru retragerea unei micro-operaii, unitatea scrie rezultatele n registrele procesorului sau n memorie. Dup memorarea rezultatelor, micro-operaia este eliminat din bufferul de reordonare.

Vous aimerez peut-être aussi

- 02 Evolutia Arhitecturilor Sist MicroprocesorDocument11 pages02 Evolutia Arhitecturilor Sist MicroprocesorCM MaryPas encore d'évaluation

- Alin Tema 2 SMPDocument5 pagesAlin Tema 2 SMPdragos_petrisorPas encore d'évaluation

- Atestare 2Document20 pagesAtestare 2Elena ChicuPas encore d'évaluation

- Unitatea Centrală de Prelucrare Şi Unitatea de MemorieDocument28 pagesUnitatea Centrală de Prelucrare Şi Unitatea de MemorieCarly DyaPas encore d'évaluation

- ProcesorDocument6 pagesProcesorMariana OrheiPas encore d'évaluation

- Memoria FizicaDocument19 pagesMemoria FizicacurspatrimoniuPas encore d'évaluation

- Asi Msi 10Document35 pagesAsi Msi 10Razvan IonutPas encore d'évaluation

- Teorie PMDDocument44 pagesTeorie PMDNico100% (3)

- Arhitectura Sistemelor de Calcul (ASC)Document13 pagesArhitectura Sistemelor de Calcul (ASC)Eduard StanescuPas encore d'évaluation

- Tema 5 ACRDocument37 pagesTema 5 ACRAlex RacuPas encore d'évaluation

- ProcesorulDocument24 pagesProcesorulAndreea Sascău100% (1)

- Evolutia MicroprocesoarelorDocument12 pagesEvolutia MicroprocesoarelorAlexandru PărduţPas encore d'évaluation

- Ucc - TestareDocument6 pagesUcc - Testaresserj21Pas encore d'évaluation

- Familia Microprocesoarelor Companiei IntellDocument3 pagesFamilia Microprocesoarelor Companiei IntellclaudePas encore d'évaluation

- Sisteme Cu MicroprocesoareDocument4 pagesSisteme Cu MicroprocesoareDiana NichiforPas encore d'évaluation

- Sisteme Cu Microprocesoare ExempleDocument91 pagesSisteme Cu Microprocesoare ExempleBuzoianu StefanPas encore d'évaluation

- CursArhCap9 1Document33 pagesCursArhCap9 1Victoria AbramovschiPas encore d'évaluation

- Carte Cu ProcesoareDocument10 pagesCarte Cu ProcesoareCRISTIANPas encore d'évaluation

- CristianAxenie Assembly Programming Course LabDocument403 pagesCristianAxenie Assembly Programming Course LabMu sicPas encore d'évaluation

- 24 Book30 Capitolul 24Document28 pages24 Book30 Capitolul 24Aurelian RaducuPas encore d'évaluation

- Componentele Unui CalculatorDocument6 pagesComponentele Unui Calculatorjohn_vi_2000Pas encore d'évaluation

- Referat MicroprocesoareDocument13 pagesReferat MicroprocesoareGîrneț Mihail100% (2)

- Lucrare de Specialitate: Calificarea: Tehnician Electronist Nivel 4Document20 pagesLucrare de Specialitate: Calificarea: Tehnician Electronist Nivel 4curspatrimoniuPas encore d'évaluation

- Microcontrolerele AVR Pe 8 BitiDocument19 pagesMicrocontrolerele AVR Pe 8 BitiolgaPas encore d'évaluation

- MicroprocesoareDocument12 pagesMicroprocesoareAndrei DenisPas encore d'évaluation

- Referat Microprocesoare PDFDocument13 pagesReferat Microprocesoare PDFpoly112Pas encore d'évaluation

- Familia ATMEL AVR 8bitiDocument21 pagesFamilia ATMEL AVR 8bitiMarlena NeștianPas encore d'évaluation

- SEP - Procesoare Digitale de Semnal in Virgula Mobila-Cap15Document5 pagesSEP - Procesoare Digitale de Semnal in Virgula Mobila-Cap15Mops LightPas encore d'évaluation

- Asc Registrii Si Memoriile Liniare Si SegmentateDocument23 pagesAsc Registrii Si Memoriile Liniare Si SegmentateTeodora FlorinaPas encore d'évaluation

- ACR Examen FinalDocument14 pagesACR Examen FinalCаша КушниренкоPas encore d'évaluation

- Proiectarea Microsistemelor DigitaleDocument34 pagesProiectarea Microsistemelor DigitaleIulia Casapu100% (1)

- Lucrarea de CursDocument26 pagesLucrarea de CursAlexandru DumbravaPas encore d'évaluation

- Procesorul (CPU)Document12 pagesProcesorul (CPU)Robert CincaPas encore d'évaluation

- Structura Calculatorului Şi Dispozitive de Intrare Eşire A IonformaţiţeiDocument46 pagesStructura Calculatorului Şi Dispozitive de Intrare Eşire A IonformaţiţeiMuntean Ionel0% (1)

- WWW - Referat.ro Echipamente Periferice - Docc29f8Document41 pagesWWW - Referat.ro Echipamente Periferice - Docc29f8Jonathan AdamsPas encore d'évaluation

- Componentele Unui Calculator Si Rolul LorDocument63 pagesComponentele Unui Calculator Si Rolul LorVasile BerceaPas encore d'évaluation

- Assembly LanguageDocument314 pagesAssembly Languagecacalau123Pas encore d'évaluation

- Caracteristici RISC, UltraSPARC II Si MagistraleDocument9 pagesCaracteristici RISC, UltraSPARC II Si MagistraleRoccoSuasitoPas encore d'évaluation

- Curs10 11Document18 pagesCurs10 11Cezara CocuPas encore d'évaluation

- Informatica 1Document9 pagesInformatica 1Ionut GheorghitaPas encore d'évaluation

- Arhitectura Calculatoaarelor C - 9Document10 pagesArhitectura Calculatoaarelor C - 9Popa DaniPas encore d'évaluation

- Arhitectura Sistemelor de CalculDocument41 pagesArhitectura Sistemelor de CalculVlad MuresanPas encore d'évaluation

- Structura MicroprocesoruluiDocument30 pagesStructura Microprocesoruluifanematreata100% (1)

- Curs Sisteme Cu MicroprocesorDocument25 pagesCurs Sisteme Cu MicroprocesorTudor MunteanuPas encore d'évaluation

- Microprocesorul INTEL 8086Document43 pagesMicroprocesorul INTEL 8086Alex FloreaPas encore d'évaluation

- Examen PMP2Document23 pagesExamen PMP2Tatar DanielPas encore d'évaluation

- Structura Interna de Baza A Procesoarelor Intel PDFDocument14 pagesStructura Interna de Baza A Procesoarelor Intel PDFБухонина ТатьянаPas encore d'évaluation

- 8 Multiprocesoare Pe UnDocument63 pages8 Multiprocesoare Pe UnCezar EnachePas encore d'évaluation

- Componentele Unui Calculator Si Rolul LorDocument63 pagesComponentele Unui Calculator Si Rolul LorDorian MikePas encore d'évaluation

- Proiect Birotica ProfesionalaDocument16 pagesProiect Birotica ProfesionalaFelly❤Pas encore d'évaluation

- Microprocesoare - Z80Document21 pagesMicroprocesoare - Z80Dragos TPas encore d'évaluation

- 12 Learn SVM KmeansDocument53 pages12 Learn SVM Kmeansioana0simionPas encore d'évaluation

- Tehnici de Criptare PDFDocument3 pagesTehnici de Criptare PDFiulyus2004Pas encore d'évaluation

- SecuritateDocument34 pagesSecuritatealexxxPas encore d'évaluation

- AC Memoria StivaDocument6 pagesAC Memoria Stivaioana0simionPas encore d'évaluation

- Arhitectura Calculatoarelor - Unitatea-IEDocument19 pagesArhitectura Calculatoarelor - Unitatea-IEioana0simionPas encore d'évaluation

- Analiza Numerica - CursDocument96 pagesAnaliza Numerica - Cursioana0simionPas encore d'évaluation

- Retele Petri ColorateDocument30 pagesRetele Petri Colorateioana0simionPas encore d'évaluation

- Tendinte in MecatronicaDocument29 pagesTendinte in Mecatronicaioana0simionPas encore d'évaluation

- Tehnici de OptimizareDocument21 pagesTehnici de Optimizareioana0simionPas encore d'évaluation

- TSA GlobalDocument329 pagesTSA Globalioana0simionPas encore d'évaluation

- GreedyDocument8 pagesGreedyioana0simionPas encore d'évaluation