Académique Documents

Professionnel Documents

Culture Documents

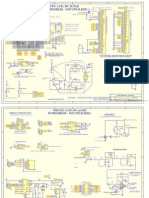

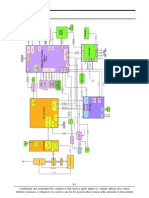

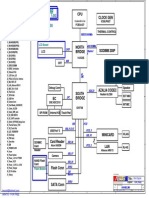

Main PCB: Neptune Lts

Transféré par

Ardianta YoppiDescription originale:

Titre original

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

Main PCB: Neptune Lts

Transféré par

Ardianta YoppiDroits d'auteur :

Formats disponibles

RX MID CHANNELS 850: CH190 -- 881,6 GSM: CH 62 -- 947,4 MHz EGSM: CH 37 -- 942,4Mhz DCS: CH 700 -- 1842,8MHz PCS: CH 661

-- 1960MHz

DCS/PCS OUT TX_OUT_HB

9

J1050 Coax Cable to Keyboard PCB

1 B+ TX_OUT_LB

5

3

21

U50 PA + Antenna Switch

1900 MHZ

GSM850/ GSM900 OUT

16 15 14 13

Power and Antenna Control

8 7 3 4 6

RF_SENSE

NEPTUNE LTS

TX_START

( to Atlas ) 1800 MHz

U800

(to U200) ( Frontend Control and Digital Modulation) (Clock ) MCLK (Reset ) MS (Data In /OUT) MDI

900 MHz

T9 W10 U9 U6 V8

SPI

DSP Peripherals accelerator, encryption Timer, Interupts

Power

H1 A11 E2 V5 K2 K3 J4 L1 R1 M1

IO_REG (VCC + 2.775V) (VCC + 2.775V) PERIPH_REG REF_REG (VCC + 1,575V) VBUCK (VCC + 1,875V) VSIM (from Atlas) SIM DIO (Data In /OUT) SIM RST (Reset ) SIM CLK SIM_PD

(Clock ) (from Atlas)

RAMP (PA Power Control)

(Transmitt Enable)

850 MHz from Neptune ( Frontend Control and Digital Modulation)

L1 Timer

DSP UltraLite 104 MHz

DSP Memory

SIM

Interface

(from / to J508)

(Transmitt Enable)

TX_START RX_ANT_EN

(Receive Enable)

TXI (NC)

CNTRL_1 CNTRL_2 CNTRL_3

MCLK

TX_EN

(Band select)

VSIM_EN

(to Atlas)

MDI

MS

RF_SENSE

B10

PA Control

Shared Memory 1Mbit RAM

DATA BUS D0-15 ADDRESS BUS A1-24

MCU Memory

External Memory

G8 E8 A2 SAW/ LNA Matching A3 SAW/ LNA Matching A5 SAW/ LNA Matching A6 SAW/ LNA Matching 1 2 G1 F1 Quadrature Generator LNA LNA Quadrature Mixer Polyphase Filter

E7

D7

C3 DAC1

D2 B7 D6 G5 GPIO

E6 C2

W7 G12 A13 VoiceBand MCU ARM7 52 MHz

W18 V17 G17 K16 J19 T16 T19 L16 N18 P2 N3 M4 P1 L3...

LNA

IIN IBIN

DC Correct RX/TX Switch ADC 13 bit Sync Filter Anti Drop Anti Alias Chanel Filter DAC 12 bit LPF Output Mixer F8 F7 F6 H7

Interface

ENR CLKR FSR DRI

N10 A4 26 MHz Oscillator Clock Generator

(100KHz)

(100KHz)

Serial Interface

CE0B CE_2 (NC) CS2B EB1B EB0B R WB OEB BURSTCLK LBAB ECBB

K1 G8 D6 F3 C2

U700 FLASH

F4 E4... RESET OUT VBUCK (from Atlas)

F5,D5 J2,H1,H8 C6 E5

QBIN

LNA

QIN

RX/TX Switch

ADC 13 bit

Sync Filter Digital TX Interface

Anti Drop

Anti Alias

Chanel Filter

DAC 12 bit

LPF D8 Clock Generator

MQSPI Display

G7 E5 C5 C6

U1051

Reference Devider

U250 GSM/ EDGE TRANCEIVER

( VCO Feedback )

GMSK Modulator

EDGE Modulator

EDGE FIR Filter

1 3

OSCO PERIPH_IO_REG OSCM (Clock enable) Y1201 2 26MHz RF_DATA RF_CLK RF_CS LDTO (NC)

(Data In /OUT) (Clock ) (U250 Control Bus) (Chip select)

8MB SRam G7 32 MB Flash LCD_RS LCD_CS LCD_CLK_DATA6 LCD_SDATA_DATA7 (to U1301 ATI LCD DATA (0 - 5)

Oscilator and

GMSK/ EDGE Select

Serial Interface

F4 F5 G4 G3

FIN

( VCO Tuning) Devider

U8 V7 W9

GPIO

U10 V6 U12 T15

SPI On Off

TOUT12 (Bias output for THERM signal) STANDBY_GATEB (to Clock enable Circuit) ANT_DETB (from J508) RTCK (to J508 Tri data write) LT_SNS_CTL ADC DATA 6

Pre-Distortion Filter

Anti Alias

( Lock Detect Out)

VCO1 (TX_LB)

Loop Filter

VCO2 (TX_HB) TX_EN

CP Phase Det. PA Control

H3 ADC Voltage G7.. Reg. C1..

VCO_REG PERIPH_IO_REG RF_REG OSCM

(VCCs from Atlas)

C18 E1 UART2 One BaseBand Timer UART / USB Keypad Wire Serial Audio Universal MQSPI Interface Interface Bus Port Interface Asynchron. Interface BT (rx) (tx) Rx /Tx A17 C15 D15 A15 F3.... V13 E3 U11 A12 B13 B15 V12 W12 D18 T12 N13 D16 B17 G3.... W13T11 V11 B14 T10 W11 D13 B12 B16 C16 A16 D19 N17 V16 G8 U13 W5 BLUE_HOST_WAKEB

Q801 2 Light Sensor

One Wire data from Battery

BB_SAP_CLK (clock) BB_SAP_FS (framesync) BB_SAP_RX BB_SAP_TX

USB_VPIN USB_XRXD_RTS USB_VPOUT_TXD USB_VMIN_RXD USB_TXENB USB_VMOUT

SJC_MOD KBC0-1 KBR0-7 (13 MHz) CLK 13 MHz

BLUE_CLK_ENB

BB_SPI_CLK BB_SPI_MOSI BB_SPI_MISO AUL_CS AUL_INT GA_SPI_CS GA_INT TRI_SPI_CS STANDBY_1_5V

U804

4 1 2

Neptune Atlas USB/ RS232 Communication

Neptune Atlas Neptune ATI Communication

(from/ to Neptune Serial Audio for Ringtone and Voice Audio)

(from/ to U301 BT, J1300 Neptune - BT - Neptune Communication and Wakeup)

U806

STANDBY_GATEB

(from Neptune GPIO) (from/ to J508 and Sidekeys)

Level Shift 4

BLUE_WAKEB

OWB

BLUE_RX BLUE_TX BLUE_RTSB BLUE_CTSB

Revision Overview Rev. 1.0: Initial Block Diagram RESETB WDOG (Watchdog) CLK 32KHZ RESET OUT GPIO_RESET

STANDBY

(to Atlas)

(to U700)

L7

Main PCB

(to ATI)

Up, Down VA, PTT

(from /to Atlas and BT)) (to Atlas) (from Atlas)

SIDE KEYS

Servive, Engineering & Optimization LEVEL 3 AL Block Diagram L7 Alexander Buehler, Michael Mauderer

2005.08.26 Rev. 1.0

Page 1of 3

(from Atlas)

(from Atlas)

(to Atlas)

(from Neptune)

Graphics Accelerator Camera /Display

P15 P19 K16

(from Neptune)

(from Atlas)

(ATI- Neptune Tri-Flash -Neptune Communication)

BB_SPI_CLK BB_SPI_MOSI BB_SPI_MISO GA_SPI_CS LCDC_OE LCDC_GS LCDC_LS LCDC_DCLK LCDC_SD LCDC_CM ATI_GPIO_C1

R14 R16 R15 P16 R2 T1 R1 P1 F1 E1 F16 J5 N2 H4 K4 M2 J5 M5 M1 L5 K5 L1 L4 M4 N1 N5 P2 N4 P4 F15

SPI SPI Timer Power Control

R6 T6 T7 V6 Image Data R7 T8 R8 R9 U19 CLK_32KHZ_2_7V GA_CORE (GRAPH_REG) 2_7V_REG (IO_REG) P504 GPIO_REG (VBUCK)

Bluetooth

(on PCB) Strip Line Antenna

Output Enable (VSync) Gate Start (H Sync) Latch Start Data Clock Serial Data Color Mode RESET

GPIO_RESET

H16

U1301 ATI

K15

E14

GA_INT LCD_RS LCD_CS LCD_CLK LCD_DATA (0 - 5) LCD_SDATA

L7 Main PCB V50x, V600 V30x, V400,

Board to Board Connector J508

GND MIC_BIAS GND ALERT+ ALERTGND GND INT_MIC+ GND GND RTCK GND TRI_SPI_CS BB_SPI_CLK BB_SPI_MOSI BB_SPI_MISO GND PERIPH_REG LEDKP VBOOST 2 1 4 3 6 5 8 7 10 9 12 11 14 13 16 15 18 17 20 19 22 21 24 23 26 25 28 27 30 29 32 31 34 33 35 36 38 37 40 39 g1- g4 SIM_REG (from Atlas) GND SJC_MOD (from Neptune) ANT_DET (to Neptune) GND SIM_DIO SIM_RST (from/to Neptune) SIM_CLK LED_CONTROL (from Atlas) KBC0 (to Neptune) KBC1 KBR0 KBR1 KBR2 KBR3 (from Neptune) KBR4 KBR5 KBR6 KBR7 ON1B (from Atlas) GND

(Neptume / ATI Communication Bus Tri Flash Write Data)

20

CAM_REG

DISPLAY CONNECTOR J503

BLUE_TX BLUE_RX BLUE_CTSB BLUE_RTSB BLUE_WAKEB BLUE_HOST_WAKEB BLUE_CLK_ENB RESET_B CLK_32KHZ 5 33 29 31 11 9 13 22 12 27 28 30 32

Bluetooth

25 10 21 BT_ANTENNA PERIPH_REG BT_REG 1

Y300

(from Atlas) (from Atlas)

(from/ to U301 BT, Neptune - BT - Neptune Communication and Wakeup)

U301

16 15

(from Neptune/ Atlas) (from Atlas)

(from/ to Neptune Serial Audio for Ringtone and Voice Audio)

BB_SAP_RX BB_SAP_FS (framesync) BB_SAP_CLK(clock) BB_SAP_TX

Neptune Atlas USB/ RS232 Communication

VBOOST DISP_LED1 DISP_LED2 DISP_LED3 DISP_LED4 GND PERIPH_REG GND VBUCK LCDC_OE LCDC_GS LCDC_LS GND LCDC_DCLK GND LCDC_SD VBUCK GND LCDC_CM ATI_GPIO_C1 GND GND

2 4 6 8 10 12 14 16 18 20 22 24 26 28 30 32 34 36 38 40 g2 g4

1 3 5 7 9 11 13 15 17 19 21 23 25 27 29 31 33 35 37 39 g1 g3

LCDC_RED5 LCDC_RED4 LCDC_RED3 LCDC_RED2 LCDC_RED1 LCDC_RED0 LCDC_GREEN5 LCDC_GREEN4 LCDC_GREEN3 LCDC_GREEN2 LCDC_GREEN1 LCDC_GREEN0 LCDC_BLUE0 LCDC_BLUE1 LCDC_BLUE2 LCDC_BLUE3 LCDC_BLUE4 LCDC_BLUE5 GND ATI_GPIO_C0 GND GND

CAM_D0 CAM_D1 CAM_D2 CAM_D3 CAM_D4 CAM_D5 CAM_D6 CAM_D7 CAM_HSYNC CAM_VSYNC CA_CLK_OUT CAM_CLK_IN CAM_SCL CAM_SDA CAM_RESET

5 7 9 10 11 12 13 14 15 16 6 2 1 3 23 22

CAMERA CONNECTOR

Sync.

W8 V8 W9 W6 W7 V7 L2 J2

RGB Data

Control

U2243

SDIO Interface ID

L16 L14 L17 K17 K16 J17 CAM_REG

U2242

CAM_PWRDWN

USB_VPIN USB_XRXD RTS USB_VPOUT TXD USB_VMIN RXD USB_TXENB USB_VMOUT

Neptune Atlas Communication

BB-SPI_CLK BB_SPI_MOSI BB_SPI_MISO AUL CS AUL_INT

(to J508 Power Key)

BB SAP CLK

BB SAP RX BB SAP TX

BB SAP FS

ON1B

IO REG

(Bias)

BATTERY CHARGER

(from Acesory Connector) (EXT Power)

BATT CONN. M1400

3 2 4 1 VR1201 / ESD

GND TOUT12 (Bias Voltage from

Neptune)

NC NC

NC NC

R4

T17 T18 U16 U18 N14

F14

R5

B2 C4 F4 B1 B3 E4

R3

P4

VBUS T14 C15 P13 AD D14 CONV. U14 F13 D/A E15 B16 SIM_PD (toNeptune) CHRGRAW (VBUS)(VBUS Sense) THERM BATT+ (Battery Sense) BATTISNS (Batt Current) BATTISNS (Charge Current - ) CHRGISNSP (Charger Current + )

(One Wire Bus to Neptune)

STEREO DET.

(to J508)

SH10 ESD

(Shield contacts)

ALERTALERT+ SPKRM SPKRP

13 Bit SAP V10 Alert U8 Amplifier T6 R7 Handset Amplifier Microphone Supply Amplifier Headset Amplifier Stereo Det. Headset Det.

(tx) (rx) CODEC 16 BIT STEREO

USB/RS232

Neptune PCap

(communication)

PRI SPI CNTL. LOGIC

Neptune PCap Communication

OWB THERM

ON LOGIC

FL505 SH11

(to J508)

G

CHARGE CONTR. CHRGCTRL

(Current Control)

S M1 D S M2 R910 G R911 D S M3 D S D902

MIC_BIAS1 MIC_INM

P9 T9

Color definition only for this section ! Main Charge Path B+ support without Ext Charger B+ support with Ext Charger

G

B12

J500 5

VBUS (to Charging Circuit)

U900 ATLAS UL

Logic

B14

BATTFET BPFET

B+

(Main Source for Atlas)

Battery to BPLUS Switch

M4 G

VBUS to BP Switch VBUS

(from Acesory Connector) (EXT Power)

LED CNTL.

2 4 3 1 G1-G4

(Shield)

UID

ESD VR500 D526 VR524 VR523

(from Atlas) VBOOST (PPD device support) VBUS (Accessory Detection signal)

B4 D2

UID DD+

H8

F3 E3

VBUS 5V Pass FET USB EMU Interface

B+ Sense

C6 B6 D6 F6 B8 C5 D12 V17

Y900

DISP_LED1 DISP_LED2 (to J503) DISP_LED3 DISP_LED4 LED_CONTROL (to J58) LEDKP RTC_BATT

Charger and Powersource Control

J506 RTC

FL500

TIMER

V16 F12 R16 P16 V12 K10 U15 E12

STANDBY (from U806) CLK_32KHZ (to Neptune and U301 BT) CLK_32KHZ_2_7V (to J1300) CLK 13 MHZ (from Neptune) WDOG (from Neptune) TX_START (from Neptune, Tx Mode indication for Atlas) RESETB

(from/ to Neptune and U700)

L16 REF REG

Switcher Boost 300mA

CAMERA REG

Switcher Buck 350mA

PERIPH IO REG

VIB REG

RF REG

IO REG

BT REG

to Vibrator Motor

GRAPH REG

AUDIO REG

VSIM

VCO REG

M18

K17

K11 N5

G16

F16

H3

K2

H4

U6

H2

C913

V2

P2

Mini USB

( 2,775V ) PERIPH_REG

( 1,275 ) GRAPH_REG

( 1,575V ) REF_REG

( 2,775V ) AUD_ REG

( 1,8/ 3V ) SIM_REG

( 2,775 ) CAM_REG

( 2,775V ) RF_REG

( 1,875V ) BT_REG

VCO_REG_CNTL

Q901

F3,E13........

(Main Source- from M3)

( 1,875V ) VBUCK

C936

( 2,775 ) IO_REG

( 5,5V ) VBOOST

VIB_REG

(to Neptune amd J508)

(to Atlas, Neptune, ATI)

(Atlas internal and J508)

( 1,3V )

( 2,775V )

VSIM_EN

(only used in Atlas)

( Atlas, Neptune, U700,ATI, )

(to Atlas and J508)

VCO_REG

Servive, Engineering & Optimization LEVEL 3 AL Block Diagram L7

VIB

2005.08.26 Rev. 1.0

(to U301)

(to Neptune)

(to U250)

(to U250)

(to P504)

(to ATI)

B+

Alexander Buehler, Michael Mauderer

Page 2of 3

L7

Keyboard PCB

Antenna Circuit

Internal Antenna M500 J513 Coax Cable to Main PCB M501 Mechanical Antenna Switch

ANT_DETB

(to J508)

Board to Board Connector J508

GND MIC_BIAS GND ALERT+ ALERTGND GND INT_MIC+ GND GND RTCK GND TRI_SPI_CS BB_SPI_CLK BB_SPI_MOSI BB_SPI_MISO GND PERIPH_REG LEDKP VBOOST 1 2 4 3 5 6 7 8 10 9 12 11 13 14 16 15 18 17 19 20 22 21 24 23 25 26 28 27 30 29 31 32 34 33 36 35 37 38 39 40 g1- g4 SIM_REG GND SJC_MOD ANT_DET (from Antenna) GND SIM_DIO SIM_RST SIM_CLK LED_CONTROL (NC) KBC0 KBC1 KBR0 KBR1 KBR2 KBR3 KBR4 KBR5 KBR6 KBR7 ON1B GND ON1B VBOOST LEDKP 6 1

M1200

6 2 1 SIM Connector 5 1.8 or 3V 4 SIM Card 3 VSIM GND VSIM

Alert J500 Mic J505

KEYPAD MATRIX

0-9,*,#, Left-Right, Center, Soft L+R, Menu, Send, Volume U-D Smart, Customer Clear Power Key Blue Keypad LEDS D501-D505 D510, D511

RTCK TRI_SPI_CS

U500

5 4

(VCC)

A1 C2 B1 7

J511

4 VCC 8 2 D1 D3 1 D2 3 6 CMD D0 CLK 5 CLK

U501

RTCK CMD

GND

Trans Flash Card Reader (Single Speed)

Servive, Engineering & Optimization LEVEL 3 AL Block Diagram L7 Alexander Buehler, Michael Mauderer

2005.08.26 Rev. 1.0

Page 3of 3

Vous aimerez peut-être aussi

- Circuito de Motorola L6Document2 pagesCircuito de Motorola L6Angel RamirezPas encore d'évaluation

- Dell Inspiron 1525 Schematic DiagramDocument47 pagesDell Inspiron 1525 Schematic Diagramogon601100% (2)

- Intel CPU: Ddriii 800/1066/1333 Ddriii 800/1066/1333 Ics9Lrs3197AklftDocument50 pagesIntel CPU: Ddriii 800/1066/1333 Ddriii 800/1066/1333 Ics9Lrs3197Aklftdrop9721Pas encore d'évaluation

- Exploring BeagleBone: Tools and Techniques for Building with Embedded LinuxD'EverandExploring BeagleBone: Tools and Techniques for Building with Embedded LinuxÉvaluation : 4 sur 5 étoiles4/5 (2)

- Sony Aa CDX-CA680X CDX-L580XDocument8 pagesSony Aa CDX-CA680X CDX-L580XБорис ДидорукPas encore d'évaluation

- Asus 1000 r1.2g SchematicsDocument51 pagesAsus 1000 r1.2g SchematicsEduardo GuajardoPas encore d'évaluation

- Temic 0675 c9Document37 pagesTemic 0675 c9andrzejPas encore d'évaluation

- CCTV Surveillance: Video Practices and TechnologyD'EverandCCTV Surveillance: Video Practices and TechnologyÉvaluation : 4 sur 5 étoiles4/5 (1)

- SRT 4155 and SRT4355 - ServicemanualDocument40 pagesSRT 4155 and SRT4355 - ServicemanualMohamed MakiPas encore d'évaluation

- Semiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsD'EverandSemiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsPas encore d'évaluation

- Datasheet Micro M65582AMF-105FPDocument46 pagesDatasheet Micro M65582AMF-105FPsel_mor100% (1)

- P2S SchematicsDocument17 pagesP2S SchematicsAsraful SardarPas encore d'évaluation

- Physics and Technology of Crystalline Oxide Semiconductor CAAC-IGZO: Application to LSID'EverandPhysics and Technology of Crystalline Oxide Semiconductor CAAC-IGZO: Application to LSIPas encore d'évaluation

- Quanta Bd3a r3c SchematicsDocument44 pagesQuanta Bd3a r3c SchematicsKostas AthanasiadisPas encore d'évaluation

- Digital Signal Processing Using the ARM Cortex M4D'EverandDigital Signal Processing Using the ARM Cortex M4Évaluation : 1 sur 5 étoiles1/5 (1)

- Hws 13642Document3 pagesHws 13642dhieward100% (2)

- PLC: Programmable Logic Controller – Arktika.: EXPERIMENTAL PRODUCT BASED ON CPLD.D'EverandPLC: Programmable Logic Controller – Arktika.: EXPERIMENTAL PRODUCT BASED ON CPLD.Pas encore d'évaluation

- Sony - Mbx-188 m612 Dvt2 - 512mb Vram - Rev 1.0Document77 pagesSony - Mbx-188 m612 Dvt2 - 512mb Vram - Rev 1.0Gabriel Lorenzo0% (1)

- HP TX2500 PDFDocument40 pagesHP TX2500 PDFcucuPas encore d'évaluation

- From GSM to LTE-Advanced Pro and 5G: An Introduction to Mobile Networks and Mobile BroadbandD'EverandFrom GSM to LTE-Advanced Pro and 5G: An Introduction to Mobile Networks and Mobile BroadbandPas encore d'évaluation

- Dell Xps m1530 Intel Discrete - Wistron HawkeDocument57 pagesDell Xps m1530 Intel Discrete - Wistron Hawkemaoh80Pas encore d'évaluation

- 8051 Microcontroller: An Applications Based IntroductionD'Everand8051 Microcontroller: An Applications Based IntroductionÉvaluation : 5 sur 5 étoiles5/5 (6)

- Ecs V10il1 - 37GV10000-C0 - Rev CDocument32 pagesEcs V10il1 - 37GV10000-C0 - Rev CHendra R. Rattu75% (4)

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2D'EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2Pas encore d'évaluation

- Schematics Laptop Dell Inspiron 700m 710m Wistron MolokaiDocument39 pagesSchematics Laptop Dell Inspiron 700m 710m Wistron MolokaiFábio DominguesPas encore d'évaluation

- Exploring Arduino: Tools and Techniques for Engineering WizardryD'EverandExploring Arduino: Tools and Techniques for Engineering WizardryÉvaluation : 4.5 sur 5 étoiles4.5/5 (5)

- Acer Aspire 5235 5535 5735 - Wistron Cathedral Peak IIDocument44 pagesAcer Aspire 5235 5535 5735 - Wistron Cathedral Peak IIMatias ArPas encore d'évaluation

- CompTIA A+ CertMike: Prepare. Practice. Pass the Test! Get Certified!: Core 1 Exam 220-1101D'EverandCompTIA A+ CertMike: Prepare. Practice. Pass the Test! Get Certified!: Core 1 Exam 220-1101Pas encore d'évaluation

- Dell Inspiron 1440 - Wistron ALBA UMADocument61 pagesDell Inspiron 1440 - Wistron ALBA UMACao Bồi Nông ThônPas encore d'évaluation

- Service Manual: CDX-L480XDocument20 pagesService Manual: CDX-L480Xkeremelekika7Pas encore d'évaluation

- SA-VK650GCP: DVD Stereo SystemDocument47 pagesSA-VK650GCP: DVD Stereo SystemArturo Tapia SolisPas encore d'évaluation

- Quanta ZHG A 12011017 ACER AO725 PDFDocument28 pagesQuanta ZHG A 12011017 ACER AO725 PDFlalukurniawanPas encore d'évaluation

- Circuit Diagram 1201-4529 1B 1Document14 pagesCircuit Diagram 1201-4529 1B 1Juan Luis VallejoPas encore d'évaluation

- DELL Inspiron N4020Document88 pagesDELL Inspiron N4020Deddy SuyantoPas encore d'évaluation

- GT I9505 Tshoo 7 PDFDocument132 pagesGT I9505 Tshoo 7 PDFAlvaro Eduardo Chaparro Giron0% (1)

- Amd690gm-M2 1219Document34 pagesAmd690gm-M2 1219imblack73100% (1)

- Ponyprog Circuit For AVR& PIC16F84Document6 pagesPonyprog Circuit For AVR& PIC16F84tiensinh1Pas encore d'évaluation

- Dell D600Document49 pagesDell D600caf_desknotePas encore d'évaluation

- Samsung GT-I9100 Galaxy S II - 08 Level 3 Repair - Block, PCB Diagrams, Flow Chart of TroubleshootingDocument79 pagesSamsung GT-I9100 Galaxy S II - 08 Level 3 Repair - Block, PCB Diagrams, Flow Chart of TroubleshootingYe Yint Aung100% (4)

- Acer Aspire 5745p 5745pg 5820t Quanta Zr7 Rev 3b SCHDocument49 pagesAcer Aspire 5745p 5745pg 5820t Quanta Zr7 Rev 3b SCHWade DyerPas encore d'évaluation

- Asus Eeepc 1008ha - Rev 1.3gDocument50 pagesAsus Eeepc 1008ha - Rev 1.3gFelipePas encore d'évaluation

- Samsung GT-C3322 Metro Duos SchematicsDocument3 pagesSamsung GT-C3322 Metro Duos SchematicsTerry MetamorfosaPas encore d'évaluation

- Easypic Fusion v7 SCH v101Document2 pagesEasypic Fusion v7 SCH v101vietanh_askPas encore d'évaluation

- Fujitsu-Siemens AMILO Li2727 Schematic DiagramDocument38 pagesFujitsu-Siemens AMILO Li2727 Schematic DiagramAhmed RedaPas encore d'évaluation

- Foxconn 915a01 SchematicsDocument52 pagesFoxconn 915a01 SchematicsMauricio Gálvez MarínPas encore d'évaluation

- 6012 SchematicsDocument24 pages6012 SchematicsDexter DanielPas encore d'évaluation

- ZA3 (11.6") Block Diagram: Za3 PCB Stack UpDocument34 pagesZA3 (11.6") Block Diagram: Za3 PCB Stack UpJoshua LeePas encore d'évaluation

- Asus EeePC 1000HE Schematic DiagramsDocument48 pagesAsus EeePC 1000HE Schematic DiagramsMicu Adrian DanutPas encore d'évaluation

- Acer Aspire 5930GDocument50 pagesAcer Aspire 5930Gperaja12Pas encore d'évaluation

- Steval Mki062v2 SchematicDocument2 pagesSteval Mki062v2 Schematicd280299Pas encore d'évaluation

- Esquematico 620cd B465 Bm5016Document54 pagesEsquematico 620cd B465 Bm5016Daniel ValerianoPas encore d'évaluation

- LCD Controller s6b0108Document24 pagesLCD Controller s6b0108Sunny HuxiPas encore d'évaluation

- 3pi SchematicDocument1 page3pi SchematicKevin JeromePas encore d'évaluation

- Touchlogger: Inferring Keystrokes On Touch Screen From Smartphone MotionDocument6 pagesTouchlogger: Inferring Keystrokes On Touch Screen From Smartphone Motionjordan SPas encore d'évaluation

- Remastering Distro Linux Ubuntu 16.04 LTS (Xenial Xerus) Using Respin For Supporting Optimization of Operation System Performance in PT Pegadaian Regional Office X PDFDocument7 pagesRemastering Distro Linux Ubuntu 16.04 LTS (Xenial Xerus) Using Respin For Supporting Optimization of Operation System Performance in PT Pegadaian Regional Office X PDFEren JeagerPas encore d'évaluation

- Kursus Asas TiktokDocument28 pagesKursus Asas TiktokAinun Rafieza Ahmad Tajuddin100% (3)

- 1-Cloud Learning User's Guide-For Distributor - V3.0Document14 pages1-Cloud Learning User's Guide-For Distributor - V3.0New Naruy Hard RainPas encore d'évaluation

- CS304 QUIZ 1 SOLVED 2021 by Lon MuskDocument63 pagesCS304 QUIZ 1 SOLVED 2021 by Lon MuskAsif100% (1)

- Unit 1. Introduction To ComputersDocument9 pagesUnit 1. Introduction To ComputersRaju KumaarPas encore d'évaluation

- Supplier/Vendor Ageing Analysis in SAP Query DesignerDocument31 pagesSupplier/Vendor Ageing Analysis in SAP Query Designerskskumar4848Pas encore d'évaluation

- BlockworldDocument4 pagesBlockworldMauro GasparofPas encore d'évaluation

- Easy Crypto Mining 101Document19 pagesEasy Crypto Mining 101Brandace HopperPas encore d'évaluation

- A Study On E Recruitment: B. Raghavendra, C. Priyanka, G. ChaithanyaDocument10 pagesA Study On E Recruitment: B. Raghavendra, C. Priyanka, G. Chaithanyamoupali besraPas encore d'évaluation

- Cambium PTP600 Series 10-08 System Release NotesDocument8 pagesCambium PTP600 Series 10-08 System Release NotesmensoPas encore d'évaluation

- E-Commerce Chapter 3Document57 pagesE-Commerce Chapter 3Mạnh Lê ĐứcPas encore d'évaluation

- ID 734397.1-PO Output For Communication Concurrent Request Does Not Print Terms & ConditionsDocument1 pageID 734397.1-PO Output For Communication Concurrent Request Does Not Print Terms & ConditionsssssdevendragulvePas encore d'évaluation

- Ec2 WGDocument1 645 pagesEc2 WGTrưởng PhạmPas encore d'évaluation

- RTN 950 Configuration Guide (Web LCT) - (V100R002C01&C02 - 03) PDFDocument1 177 pagesRTN 950 Configuration Guide (Web LCT) - (V100R002C01&C02 - 03) PDFvydaicaPas encore d'évaluation

- 11b/g Wireless Outdoor Client Bridge/AP: User's ManualDocument56 pages11b/g Wireless Outdoor Client Bridge/AP: User's ManualwasiuddinPas encore d'évaluation

- Touchstone-2-Workbook-Answers - PDF (PDF - TXT)Document2 pagesTouchstone-2-Workbook-Answers - PDF (PDF - TXT)Karina Marin sosaPas encore d'évaluation

- Integration Guide For The Fanuc (S-CUBE) Base Handling Application V4.00 Rev CDocument69 pagesIntegration Guide For The Fanuc (S-CUBE) Base Handling Application V4.00 Rev Cfranck.nzonzitenwhil.comPas encore d'évaluation

- Google Certified Professional Cloud Architect - Part 3: Course FeaturesDocument5 pagesGoogle Certified Professional Cloud Architect - Part 3: Course Featureshuber.mcPas encore d'évaluation

- F59L1G81MA EliteSemiconductorDocument44 pagesF59L1G81MA EliteSemiconductorjustin tiongcoPas encore d'évaluation

- Buy Apple Gift Cards - AppleDocument1 pageBuy Apple Gift Cards - AppleKfmy NannyPas encore d'évaluation

- Business Intelligence-Final PrintDocument13 pagesBusiness Intelligence-Final PrintsahrPas encore d'évaluation

- Smart-Catalogue Feb PDFDocument17 pagesSmart-Catalogue Feb PDFMasautso MwalePas encore d'évaluation

- ENGL286 Answers 177Document13 pagesENGL286 Answers 177nightingGale SxrxzxPas encore d'évaluation

- Zebra Zebralink™ Suite of Software & Tools: The Power Behind The PrinterDocument2 pagesZebra Zebralink™ Suite of Software & Tools: The Power Behind The PrinterUsama ShafiqPas encore d'évaluation

- Genetic Algorithm AI MLDocument7 pagesGenetic Algorithm AI MLtarun saiPas encore d'évaluation

- Open Source Software NoticeDocument55 pagesOpen Source Software NoticeethioelectricianPas encore d'évaluation

- Example Thesis About CCTVDocument4 pagesExample Thesis About CCTVheatherfreekindependence100% (2)

- Chapter TwoDocument26 pagesChapter TwoAbenezer TeshomePas encore d'évaluation

- Math Kernel LibraryDocument4 pagesMath Kernel Libraryava939Pas encore d'évaluation