Académique Documents

Professionnel Documents

Culture Documents

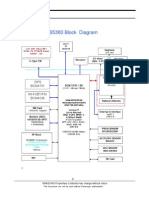

Cube33 02

Transféré par

Bayanaa PeaceTitre original

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

Cube33 02

Transféré par

Bayanaa PeaceDroits d'auteur :

Formats disponibles

8

68040

AD(31:0)

SIZR(1:0)

R_W

_LOCK

_LOCKE

_CIOUT

TRANSFER

TRAITS

R16

T14

S13

T10

_TSR

_TA

_TEA

_TCITBI

S11

T9

PULLUP1

T13

T17

_BG(0)

_BBR

_IPL(2:0)

_AVEC

T11

1

SC(1:0)

S7

_MODEN

PULLUP1

T5

S6

TESTTDI

TESTTCK

TESTTMS

PON

S3

S4

S5

T3

AD(31:0)

SIZ(1:0)

R_W

TT(1:0)

S18

R18

R1

96

_BR(2:0)

_BR(2:0)

102

_BB

151

_LOCK

147

_LOCKE

_LOCK

_LOCKE

DLE

163

PON

_BR

_IPEND

_IPL(2:0)

_AVEC

_MI

_RSTO

_RSTI

T18

_BRR(0)

VCC

R27

10K

VCC

S1

VD(15:0)

R51

10K

R26

10K

_AVEC

_LOCK

_RESETOUT

R3

T2

_VRAS

_VCAS(1:0)

_VWE

VMA(8:0)

_VDTOE

VDSF

_VSYNC

HSYNC_

VBLANK_

_VSOE(1:0)

VSC(1:0)

TESTTDO040

VCC

R21

10K

NO LOAD

2

173

VLOAD

VCLK

_RASA

_RASB

_RASC

_RASD

_RASV

_CAS0(3:0)

_CAS1(3:0)

_WE(3:0)

MA0(10:0)

MA1(10:0)

_ROMSEL

PD0(3:0)

PD1(3:0)

VCC

MEMCTL

R24

10K

NO LOAD

1

R25

10K

NO LOAD

0

_RDLE0

_RDLE1

_RDLOE0

_RDLOE1

WRLE0

WRLE1

_WRLOE

LATCH CTL

CR20

CR17

MMBD201T1

P2

P1

MMBD201T1

P2

31

MMBD201T1

MMBD201T1

MISC

P2

29

28

BITS 31:28 SD FIELD:0

_CONFIGRST

CR10

P1

NO_LOAD

P1

CR9

MMBD201T1

P2

166

TDI

164

TCK

165

TMS

168

ATPG

TESTDOPC

TESTTCK

TESTTMS

AD(31:0)

P1

MMBD201T1

GPOUT

_TMCINT(2:0)

TDO

14

18

19

15

13

17

10

VLOAD

44

40

42

41

43

_RASA

_RASB

_RASC

_RASD

P1

P2

NO_LOAD

CR5

P1

P2

11

NO_LOAD

10

RESETOUT

74F00

R79

CLKC25M

U40

74ACT00

10

8

9

RESETOUT

P1

CR16

RESETOUT2

LA TEST POINTS

_DEVRST

NO_LOAD

9

FL3

100MHz

MMBD201T1

20

23

JP5

P2

NO_LOAD

ADBF

22

28

27

26

25

24

ADBJ

CLKBCLKB

WRLE0

10

74F00

8

R83

_LATWRLE0

_LATWRLE0R

C99

0.1

50V

_WRLOE

171

ADBDRIVE

172

GPOUT

_TMCINT(2:0)

167

TESTTDO

NO_LOAD

GPOUT

1

2

R95

R94

10

RC1

1.0K

TESTPLLEN

VCC

R119

10K

RC1

U42

R115

MC88915FN70

FEEDBACK

SYNC(0)

11

SYNC(1)

6

REFSEL

18

PLLEN

12

FREQSEL

4

_RST

CLKBCLK2

VCCA

LOCK

2XQ

Q0

Q1

Q2

Q3

Q4

_Q5

QDIV2

21.5

R117

19

26 CLKPLLOUTX2

CLKPCLK

14

21.5

R114

16

CLKPLLQ0

21

23

28

2 CLKPLLQ5

CLKBCLK

21.5

R114

CLKBCLKB

25

21.5

R122

CLKQDIV2

SPEEDSEL

VCC

10UH

C100

3300PF

50V

VCC

L10

CLKPLLQ1

9

GNDA

CLKNBIC

21.5

R118

10K

R23

VCC

162

1.0K

BITS 11:8 = Board Revision

MMBD7000L

MEMSPSEL1

MEMSPSEL0

C102

0.1

50V

R2

1.0K

R105

475

_CONFIGSPD

JP3

VCC

C101

0.1

50V

L9

10uH

PLLSIG1

1.0M

1

2

GPOUT JUMPER

PWRPLLGND

AD(31:0)

_LATWRLE1R

10

PWRPLLVCC

WRLE0

WRLE1

JP4

R106

R73

_LATWRLE1

U36

CLKPLLQ3

ADBDATAIN

PHASE LOCKED LOOP

_RDLE0

_RDLE1

_RDLOE0

_RDLOE1

NO_LOAD

CR38

74F00

WRLE1

1

2

U36

10

JTAG

CR18

CLK25PLLIN

10

INTERLEAVE LATCH CLOCKS

MA0(10:0)

MA1(10:0)

_ROMSEL

12

MMBD201T1

P2

_CAS0(3:0)

_CAS1(3:0)

_WE(3:0)

ADB DRIVER

MMBD201T1

CLOCK SPEED SELECT

NO_LOAD

VCC

MMBD201T1

_VRAS

_VCAS(1:0)

_VWE

VMA(8:0)

_VDTOE

VDSF

_VSYNC

HSYNC

VBLANK

_VSOE(1:0)

CLKVSC(1:0)

MMBD201T1

BITS 15:12 = CPU TYPE: 1000 = TCUBEBW

CR6

_CONFIGRST

P2

13

_CONFIGRST

P1

CLKC33M

CLK25PLLIN

AD(31:0)

ADBDRIVE

182

CR7

P2

14

74ACT00

P1

CR8

MMBD201T1

P2

15

ADB

ADBDATAIN

CR19

P2

30

169

ADBDATAIN

P1

CR11

_RESETOUT

RESETOUT

_CPURSTIN

_LOCKE

P1

160

RST

_CONFIGRST

P1

RESETOUT

U26

CONFIGURATION

B

U9

LOW CURRENT SELECT:

2 Installed = DATA BUS

1 Installed = ADDRESS and CONTROL

0 Installed = ARBITRATION and MISC

_BB

RESET INVERTERS

ARBITRATION

_IPL(2:0)

PULLUP1

U2

AM27C010

_BG(2:0)

_BG(2:0)

VD(15:0)

CLKVCLK

R40

221

_CE

_OE

_P

VPP

VCC

R39

221

22

24

31

VCC

PD1(3:0)

D(7:0)

A(16:0)

_ROMSELR

3:0

ROM_D(7:0)

ROM_A(16:0)

SYSTEM BUS

Q16

VCC

VCC

MA1R(5:0)

JTAQ

PULLUPS

PD0(3:0)

7:4

16:11

261

VIDEO

TDO

TDI

TCK

TMS

_TRST

CLKC25M

R4

PON

RESET

_CDIS

_MDIS

EPROM

10:0

_ROMSEL

162

_CPURSTIN

161

_RESETIN

_CPURSTIN

_DEVRST

PD0(3:0)

PD1(3:0)

VCC

AD(31:0)

SIZ(1:0)

_RW

TT(1:0)

177

176

175

_TS

100

_TA

99

_TEA

98

_TCITBI

_TCITBI

TRANSFER

CONTROL

ARB

R15

_TBI

_BG

_BB

CLK20

CLK25

CLK33

CLOCKS

101

_TS

_TA

_TEATMC

_LOCKR

_LOCKER

_BB

SC(1:0)

_RESETOUT

_TIP

_TS

_TA

_TEA

_TCI

179

CLK100

144

BCLKIN

145

BCLKE

CLKBCLK

TM(2:0)

TLN(1:0)

UPA(1:0)

SIZ(1:0)

N16

R_WR

MA0R(10:0)

BUS

TT(1:0)

TMC

PST(3:0)

A(31:0)

TMC_CHIP

CLOCKS/STATUS

PCLK

BCLK

D(31:0)

TTR(1:0)

U18

MC68040_33MHZ

R9

R7

CLKPCLK

CLKBCLK

C117

3300PF

50V

C116

3300PF

50V

C106

3300PF

50V

C115

3300PF

50V

C109

3300PF

50V

_CONFIGRST

P1

CR13

P1

P2

NO_LOAD

P1

CR12

CR15

P1

ADBF

CR14

R102

MMBD201T1

MMBD201T1

MMBD201T1

P2

1

AD(31:0)

P2

ADBDRIVE

MMBD201T1

ADBDRVRES

U9

74ACT00

MMBT4401T1

P2

Q8

1.0K

RESETOUT

AD(31:0)

BITS 2:0 = CPU SPEED: 101 = 20MHZ

110 = 25MHZ

111 = 33MHZ

BITS 5:4 = MEM SPEED: 11 = 100NS

10 = 80NS

01 = 70NS

12

13

11

_CONFIGSPD

PN4643AA

CPU : TMC : EPROM : PLL : CONFIG : ADB

6

Sheet

of

17

Cube33-02.pdf 001

Vous aimerez peut-être aussi

- Samsung GT-P1000 Galaxy Tab Level 3 Service ManualDocument49 pagesSamsung GT-P1000 Galaxy Tab Level 3 Service Manualnonyabizness2003Pas encore d'évaluation

- Vehicle Engine Management SystemDocument4 pagesVehicle Engine Management SystemfadholiPas encore d'évaluation

- Volvo Aw71 ManualDocument152 pagesVolvo Aw71 Manualjbouza83% (6)

- 8/7/2014 5:29:10 PM Parameters and Signals (ACS550/204c) : Name Value Unit Min MaxDocument9 pages8/7/2014 5:29:10 PM Parameters and Signals (ACS550/204c) : Name Value Unit Min MaxDinhnamsgpPas encore d'évaluation

- Certificado 015Document4 pagesCertificado 015Nicolas Yussepe BonillaPas encore d'évaluation

- Admiral TG 2100A Admiral TG2100A Chasis PTFM05Document1 pageAdmiral TG 2100A Admiral TG2100A Chasis PTFM05dexterconexion1312Pas encore d'évaluation

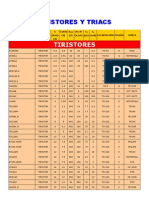

- TIRISTORES Y TRIACS Limberth BustamanteDocument18 pagesTIRISTORES Y TRIACS Limberth Bustamantegatito556Pas encore d'évaluation

- SPD62Document1 pageSPD62vikramsimhareddyPas encore d'évaluation

- Elec. Schema TD6Document5 pagesElec. Schema TD6Katrien GoutryPas encore d'évaluation

- GT S5360Document51 pagesGT S5360radiobrunoPas encore d'évaluation

- Imp Part No 07-03-19Document11 pagesImp Part No 07-03-19Manish JhaPas encore d'évaluation

- Lcnouaa1'E - T - 4 - Pnofnua.U - Cnouas1'Ht - 44O - Emmu 1O M - Eall 8T4Iiili10Document4 pagesLcnouaa1'E - T - 4 - Pnofnua.U - Cnouas1'Ht - 44O - Emmu 1O M - Eall 8T4Iiili10rcv436Pas encore d'évaluation

- 2001 Automatic TransmissionDocument125 pages2001 Automatic Transmission08088338Pas encore d'évaluation

- Catalogo, Sockolet, Threadolet, Nippolet, Swaged NippleDocument3 pagesCatalogo, Sockolet, Threadolet, Nippolet, Swaged NippleD_carolina50% (2)

- VDB3054 Highway & Traffic Engineering MAY 2016 Examples - Horizontal CurveDocument5 pagesVDB3054 Highway & Traffic Engineering MAY 2016 Examples - Horizontal CurveZulaika LainiPas encore d'évaluation

- Bill of Materials-LcmbDocument6 pagesBill of Materials-Lcmb??????Pas encore d'évaluation

- Integrated Gate Drive Optocoupler: Product SelectionDocument2 pagesIntegrated Gate Drive Optocoupler: Product SelectionNarendra BholePas encore d'évaluation

- Engine Control For 2TR-FE: 90 Toyota Tacoma (Em01D0U)Document12 pagesEngine Control For 2TR-FE: 90 Toyota Tacoma (Em01D0U)DanielPas encore d'évaluation

- Diagnostic Socket OBDIIDocument1 pageDiagnostic Socket OBDIIfadholiPas encore d'évaluation

- Behringer Djx700 Professional Mixer DJ Schematic AudioDocument10 pagesBehringer Djx700 Professional Mixer DJ Schematic AudioMinciuna Catalin100% (1)

- (D-A G (Qine O Onvstru Gttoni: You Are Required ToDocument3 pages(D-A G (Qine O Onvstru Gttoni: You Are Required ToMostafaPas encore d'évaluation

- ¡ Semiconductor: MSM80C88A-10RS/GS/JSDocument37 pages¡ Semiconductor: MSM80C88A-10RS/GS/JSZarate BismkPas encore d'évaluation

- SZ.818.015C100 Last Mutation: 201202211410SSTADocument7 pagesSZ.818.015C100 Last Mutation: 201202211410SSTAQuang Huy HàPas encore d'évaluation

- CT-X218 CT-X458 CT-X258: Simple ManualDocument9 pagesCT-X218 CT-X458 CT-X258: Simple ManualWłodzimierz SurdackiPas encore d'évaluation

- Bom - Sentsor Core Esp32-MicroDocument1 pageBom - Sentsor Core Esp32-MicroAlexander Figueroa100% (1)

- (1/ (CA 0,5) ) - (1/ (CA0 0,5) ) (1/ (CA 2) ) : Axis Title Axis TitleDocument3 pages(1/ (CA 0,5) ) - (1/ (CA0 0,5) ) (1/ (CA 2) ) : Axis Title Axis TitleRenan BaiaPas encore d'évaluation

- Shimpo STH SeriesDocument8 pagesShimpo STH SeriesElectromatePas encore d'évaluation

- Dan's Fanuc Spindle InfoDocument13 pagesDan's Fanuc Spindle InfoPham LongPas encore d'évaluation

- ABB - VFD - Common - Parameters SettingsDocument7 pagesABB - VFD - Common - Parameters Settingssivasakti chp2Pas encore d'évaluation

- 4D56Document106 pages4D56Nery Bardales Leon0% (2)

- Samsung GT-E3210 08 Level 3 Repair - Block-, PCB Diagrams, Flow Chart of TroubleshootingDocument38 pagesSamsung GT-E3210 08 Level 3 Repair - Block-, PCB Diagrams, Flow Chart of TroubleshootingAmat Sofiyan100% (1)

- Sprite BOMDocument2 pagesSprite BOMbillPas encore d'évaluation

- Sprite BOMDocument2 pagesSprite BOMbillPas encore d'évaluation

- Diagrama SA AK300Document14 pagesDiagrama SA AK300Jaciel Fielder Jimenez100% (1)

- PIC32 WEB Rev.a SchematicDocument1 pagePIC32 WEB Rev.a SchematicFernando Piedade100% (1)

- Inter-M A-60 - 120 Service ManualDocument9 pagesInter-M A-60 - 120 Service ManualGaniza Long0% (2)

- Dsa 284557 PDFDocument6 pagesDsa 284557 PDFrrebollarPas encore d'évaluation

- VNX - Su Avensis Main Characteristics 2003 2009 PDFDocument814 pagesVNX - Su Avensis Main Characteristics 2003 2009 PDFprog-toy91% (11)

- cp14b85l LRDocument5 pagescp14b85l LRvebicitaPas encore d'évaluation

- F28379DControlCARD V1.1.1 1Document6 pagesF28379DControlCARD V1.1.1 1Marco FajardoPas encore d'évaluation

- Engine PetrolDocument6 pagesEngine Petrolsadeli53Pas encore d'évaluation

- DBDocument5 pagesDBjuliocesar.caPas encore d'évaluation

- Quasar Arm SCHDocument3 pagesQuasar Arm SCHNacer MezghichePas encore d'évaluation

- 644Document11 pages644Tony RamirezPas encore d'évaluation

- GD70 16M R9H00488 PSRPT 2021-07-17 20.55.43Document11 pagesGD70 16M R9H00488 PSRPT 2021-07-17 20.55.43rafi bungsuPas encore d'évaluation

- TS-SLW700AIWA усилвател PDFDocument35 pagesTS-SLW700AIWA усилвател PDFvalkovPas encore d'évaluation

- Semiconductor KRA101S KRA106S: Technical DataDocument7 pagesSemiconductor KRA101S KRA106S: Technical Datapromatis5746Pas encore d'évaluation

- 1 231085 000061246568 09082018 CCDocument1 043 pages1 231085 000061246568 09082018 CCVergaraJuan0% (1)

- RET Template OKV-V1.0Document35 pagesRET Template OKV-V1.0Zul QaddimPas encore d'évaluation

- MT8888Document1 pageMT8888Dan Nguyen VanPas encore d'évaluation

- Item No. QTY Part No. Description VendorDocument11 pagesItem No. QTY Part No. Description Vendorokan uysalPas encore d'évaluation

- mc14518bcp en PDFDocument8 pagesmc14518bcp en PDFdellcoPas encore d'évaluation

- Manual Servicio Panasonic Sl-sx289vDocument16 pagesManual Servicio Panasonic Sl-sx289vRafael Hernandez100% (1)

- Semiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsD'EverandSemiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsPas encore d'évaluation

- Advanced Electric Drives: Analysis, Control, and Modeling Using MATLAB / SimulinkD'EverandAdvanced Electric Drives: Analysis, Control, and Modeling Using MATLAB / SimulinkPas encore d'évaluation

- Variable Speed AC Drives with Inverter Output FiltersD'EverandVariable Speed AC Drives with Inverter Output FiltersPas encore d'évaluation

- What I Learned Coding X-Wing vs. TIE Fighter: Peter LincroftDocument40 pagesWhat I Learned Coding X-Wing vs. TIE Fighter: Peter LincroftevandrixPas encore d'évaluation

- Mavic 3 - Specs - DJIDocument10 pagesMavic 3 - Specs - DJIZeljko GogicPas encore d'évaluation

- Thomson THG540Document36 pagesThomson THG540Tibi SloviPas encore d'évaluation

- iSTAT Quick Reference GuideDocument40 pagesiSTAT Quick Reference GuideTony ChenPas encore d'évaluation

- White Elements Graphic DesignDocument10 pagesWhite Elements Graphic DesignIzaz ArefinPas encore d'évaluation

- How To Install Dev-C++ and GLUTDocument15 pagesHow To Install Dev-C++ and GLUTMelquior PaniniPas encore d'évaluation

- AOC LE32H158I Service ManualDocument165 pagesAOC LE32H158I Service ManualvmalvicaPas encore d'évaluation

- InstallationDocument111 pagesInstallationSuma P RPas encore d'évaluation

- SQL Server Installation and ConfigurationDocument52 pagesSQL Server Installation and ConfigurationAshish ChoudharyPas encore d'évaluation

- Digital Design and Computer Architecture, 2: EditionDocument135 pagesDigital Design and Computer Architecture, 2: EditionСергей КапустаPas encore d'évaluation

- Dyna Line, ButtonsDocument20 pagesDyna Line, Buttonsgus459Pas encore d'évaluation

- Assignment-5 RES500-Academic Writing and Research Skills 1 Semester (2019-2020)Document5 pagesAssignment-5 RES500-Academic Writing and Research Skills 1 Semester (2019-2020)Fatima WassliPas encore d'évaluation

- DSpace TutorialDocument55 pagesDSpace TutorialCristobalPonceSalazar100% (1)

- Hipaa Nist StandardDocument152 pagesHipaa Nist Standardmrehan2k2Pas encore d'évaluation

- P780Document50 pagesP780Shailesh BhanushaliPas encore d'évaluation

- COM4805 Assignment 1Document33 pagesCOM4805 Assignment 1Jason Warren BlandPas encore d'évaluation

- CCHM Lec 1Document3 pagesCCHM Lec 1QUIAL BINPas encore d'évaluation

- Manual TV LG 50pj350Document242 pagesManual TV LG 50pj350manolito454Pas encore d'évaluation

- Data Sheet 7KG8501-0AA01-0AA0: Measuring FunctionsDocument3 pagesData Sheet 7KG8501-0AA01-0AA0: Measuring FunctionstojestePas encore d'évaluation

- Java Course Content Updated - WinPath ITDocument5 pagesJava Course Content Updated - WinPath ITSridhar SPas encore d'évaluation

- Config Cisco 881 Isla PartidaDocument4 pagesConfig Cisco 881 Isla PartidaJohan Frederick FoitzickPas encore d'évaluation

- Meghan Ficarelli ResumeDocument1 pageMeghan Ficarelli ResumemegficPas encore d'évaluation

- Slot07 08 09 RecursionDocument82 pagesSlot07 08 09 RecursionCông QuânPas encore d'évaluation

- Procurement Strategy: By: Reden Delos Santos Mojica Jen Marjorie F. Nicolas Wesley Rabe Jetro TorresDocument33 pagesProcurement Strategy: By: Reden Delos Santos Mojica Jen Marjorie F. Nicolas Wesley Rabe Jetro Torresrl magsino100% (1)

- 2019 - Decision Tree Analysis With Posterior ProbabilitiesDocument10 pages2019 - Decision Tree Analysis With Posterior ProbabilitiesAvifa PutriPas encore d'évaluation

- Introduction ISO 55001Document66 pagesIntroduction ISO 55001Indra GirsangPas encore d'évaluation

- Chapter 2.2 Basic GUI ComponentsDocument26 pagesChapter 2.2 Basic GUI ComponentsPabbura_HatiPas encore d'évaluation

- VAR CopenhagenDocument16 pagesVAR CopenhagenCLIDERPas encore d'évaluation

- Philippine Auditing Practices Statements (PAPS) 1009 Computer Assisted Audit TechniquesDocument9 pagesPhilippine Auditing Practices Statements (PAPS) 1009 Computer Assisted Audit Techniqueserjan nina bombayPas encore d'évaluation

- Ict-112-Lec-1812s Week 19-Long Quiz 004Document9 pagesIct-112-Lec-1812s Week 19-Long Quiz 004Allick Fitzgerald Nanton Jr.Pas encore d'évaluation