Académique Documents

Professionnel Documents

Culture Documents

Delay Components in Circuit

Transféré par

ashrafuli_44Description originale:

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

Delay Components in Circuit

Transféré par

ashrafuli_44Droits d'auteur :

Formats disponibles

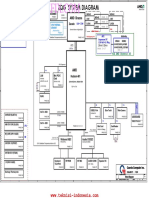

CS623

CS623 CAD for VLSI

The following slides are adopted from UTD 3325 Slides

Lecture 30 : Delay Components in a Circuit

Shankar Balachandran Dept. of Computer Science and Engineering Indian Institute of Technology Madras shankar@cse.iitm.ac.in

1 April 2007 2

CS623

CS623

Combinational Circuit Timing Parameters

Timing parameters (contd)

Vin Vmax 0.5Vmax 0 Vout Vmax 0.9Vmax 0.5Vmax 0.1Vmax tpLH tpHL time

Rise Time (tr), the time required for a signal to transition from 10% of its maximum value to 90% of its maximum value. Fall Time (tf), the time required for a signal to transition from 90% of its maximum value to 10% of its maximum value. Propagation Delay (tpLH, tpHL), the delay measured from the time the input is at 50% of its full swing value to the time the output reaches its 50% value.

1 April 2007 1 April 2007

0 tr tf

time

CS623

CS623

Example: Gate delay

Determine the worst case propagation delay through these circuits.

2 ns 4 ns 2 gd 5 gd

Timing Analysis of Combinational Circuits

Using gates with finite propagation delays, tpLH and tpHL instead of zero gate delays used in functional analysis.

Gate tpLH tpHL INV 3 ns 2 ns XOR 5 ns 4 ns

t p = 2 + 4 = 6 ns

3 gd

3 gd 2 gd

6 gd

t p = max {( 2 + 5 ) , ( 3 + 5 ) , ( 3 )} = 8 gd

5 gd 3 gd

1 April 2007

1 April 2007

t p = max {( 2 + 5 ) , ( 3 + 5 ) , ( 3 ) , ( 6 + 3 )} = 9 gd

CS623

01 Transition on Vin Vin V1 V2 V3 Vout

t=0 4 2 3 2 5 8 ns

CS623

Setup and Hold Times

Gate INV XOR tpLH 3 ns 5 ns tpHL 2 ns 4 ns

Setup time, tsu, is the time period prior to the clock becoming active (edge or level) during which the flip-flop inputs must remain stable. Hold time, th, is the time after the clock becomes inactive during which the flip-flop inputs must remain stable. Setup time and hold time define a window of time during which the flip-flop inputs cannot change quiescent interval.

Vin V1 V2 V3

3 2 3 4 5

10 Transition on Vin

1 April 2007

9 ns

7

1 April 2007

Vout

CS623

CS623

Propagation Delay

Propagation delay, tpHL and tpLH , has the same meaning as in combinational circuit beware propagation delays usually will not be equal for all input to output pairs. There can be two propagation delays: tC-Q (clockQ delay) and tD-Q (dataQ delay). For a level or pulse triggered latch:

Data input should remain stable till the clock becomes inactive. Clock should remain active till the input change is propagated to Q output. That is, active period of the clock,

1 April 2007 1 April 2007

Latch & Flip-flop Timing Parameters

tw > max {tpLH, tpHL}

9

10

CS623

CS623

Latch and Flip-flop Timings

CLK

Characterizing Timing

Setup time, hold time Propagation delays

tD-Q

th tsu tC-Q

Q

Flip-flop tsu th tsu th Latch

1 April 2007

tD-C tC-Q Flip-Flop

tD-C tC-Q Latch

Q

1 April 2007

tC-Q

11

tC-Q tD-Q

12

CS623

CS623

More Precise FF Setup & Hold Times

CLK t D Q t

350 300 Minimum Data-Output

Sequential Circuit Timing

Once the functionality of a sequential network is designed, its timing parameters must be determined. Timing problems can be very subtle because timing parameters can vary with device age and other operating conditions.

Clk-Output [ps]

250 200 150 100

Setup

Hold

Sampling Window

50 0 -200 -150 -100 -50 0 50 100 150 200

1 April 2007

Data-Clk [ps]

13

1 April 2007

14

CS623

CS623

Timing Parameters

Global setup time (Tsu) Global hold time (Th) Maximum clock frequency Clock skew.

These parameters are derived using the circuit (known) delays described below.

tio delay from input of IFL to output of OFL tif delay from circuit inputs of flip-flop inputs tfo delay from flip-flop outputs to circuit outputs tff delay from flip-flop outputs to flip-flop inputs tc-q clock to Q propagation delay of flip-flops tsu setup time of flip-flops

1 April 2007

Global Setup and Hold Times

Changes that occur at inputs can be delayed by as much as maximum tif by the time they reach the flip-flop inputs. Hence, we want to setup circuit inputs relative to clock edge appearing at the flip-flops. Th Tsu

tc th tif tsu tif

CLK (at clock source) CK (at FF clock input) X (at sequential circuit input)

D (at FF input)

Tsu = tsumax + tifmax tcmin

1 April 2007

th hold time of flip-flops tc clock delay; time required for clock to reach all flip-flops

15

Similarly, hold time of the circuit inputs relative to the system clock at the source is given by Th = thmax tif min + tcmax

16

CS623

CS623

Clock Frequency

The limiting factor on the clocking rate is the propagation delay through the IFL block:

Clock Frequency

The limiting factor on the clocking rate is the propagation delay through the combinational logic block (input forming logic):

Dj

Qj

Comb. logic

CKj

Di

CKi CLK tff

Qi

1 April 2007

17

1 April 2007

Changes on the Qs must propagate through the IFL before they can affect the next state

Changes on the Qs must propagate through the combinational logic before they can affect the next state

18

CS623

CS623

Maximum Clock Frequency

CKi Qi

Maximum Clock Frequency

Dj Qj

CKi Qi

tC-Q

Dj

tff

tsu

Comb. logic

CKj

Di

CKi

Qi

tC-Q

Dj

tff

tsu

Tck (=Tclk)

Edge Triggering

CLK

tff

Tck (=Tclk)

Edge Triggering

For an edge-triggered circuit: minimum clock period is,

For an edge-triggered circuit: minimum clock period is,

Tclk tC Q ,max + t ff ,max + tsu,max

1 April 2007

Tclk t C Qmax + t ffmax + t sumax

Maximum Clock Frequency:

Maximum Clock Frequency:

19

f clk

1 April 2007

1 Tclk

f clk

20

1 Tclk

CS623

CS623

Timing Violations

Tclk tC Qmax + t f f max + tsumax

The clock period (Tclk) has a lower bound of tff.max . If the clock period is equal to (tff.max + tC-Q.max) then the flip-flop state changes can violate setup times. Remedy :

Clock Skew

The previous discussion assumes that clock signals arrive at all flip-flops simultaneously - this is not a good assumption since it is not true in practice. Because of different wire lengths over which the clock signals travel and the load at the destination, there is a slight difference in clock arrival times at different flip-flop inputs. Clock skew, tskew, is the difference in time between triggering edges seen at different flip-flops. Clock skew affects minimum Tclk.

22

Use faster flip-flops (decrease tC-Q )

1 April 2007

21

Use a slower clock (increase clock period, Tclk)

CS623

1 April 2007

Use faster gates (decrease tff )

CS623

Max. Clock Frequency with Skew

CKi CKj Qj

Max. Clock Frequency with Skew

tskew tp tff tsu

CLK tff

Dj

Qj

CKi CKj

tskew

tskew tC-Q tff tsu

Comb. logic

CKj

Di

CKi

Qi

Qj

Di

Di

Tck (=Tclk)

Therefore, for an edge-triggered circuit with clock skew,

Therefore, for an edge-triggered circuit with clock skew,

Tck (=Tclk)

Tclk tskew,max + t p ,max + t ff ,max + t su ,max

Clock skew is a significant factor in determining the speed of high-performance sequential circuits. The larger the skew, the slower the circuit will operate.

1 April 2007 1 April 2007

Tclk t skewmax + tC Qmax + t ffmax + tsumax

Clock skew is a significant factor in determining the speed of high-performance synchronous circuits. The larger the skew, the slower the circuit will operate.

23

24

CS623

CS623

Maximum Allowable Clock Skew

Can any skew be countered simply by slowing down the clock? No

If the skew is too large, state change caused by an edge at FFi will change the state of FFj erroneously when the clock edge finally gets there!

Dj Qj

Timing Analysis Example

For the circuit given below determine all the sequential circuit timing parameters.

CKi

tskew tC-Q th

tC Q + t ff t skew + th

Comb. logic

CKj

Di

CKi

Qi

tskew CKj

Qi

CLK

tff

tff

Dj

state of Dj before clock becomes active state of Dj after clock becomes active

In the worst case, if tff = 0 then,

tskewallowed = tC Qmin thmax

flip-flops propagation delay must be greater than its hold time.

For a D flip-flop use: tsu = 2ns, th = 15ns and tC-Q = 20ns For a NAND gate use: tp,max = 10ns and tp,min = 3ns

1 April 2007

1 April 2007

25

26

CS623

CS623

tif ,max = 3t p ,max,nand = 30ns tif ,min = 2t p ,min,nand = 6ns t ff ,max = 2t p ,max,nand = 20ns t ff ,min = 2t p ,min,nand = 6ns tc ,max = 2t p ,max,nand = 20ns tc ,min = 2t p ,min,nand = 6ns

Tsu = t su ,max + tif ,max tc ,min = 2 + 30 6 = 26ns Th = th ,max tif ,min + tc ,max = 20 + 15 6 = 29ns Tclk tC Q ,max + t ff ,max + tsu ,max = 20 + 20 + 2 = 42ns f clk ,max = 1/ 42ns = 23.8MHz tskew,max = tC Q ,min + t ff ,min th ,max = 20 + 6 15 = 11ns

1 April 2007 1 April 2007

1-Phase Clock w/ Level Triggering

For a D flip-flop use: tsu = 2ns, th = 15ns, tC-Q = 20ns For a NAND gate use: tp,max = 10ns, tp,min = 3ns

Positive clock skew

Latch must be open for less than the shortest combinational logic delay but more than the worst setup time.

t w td q min + tlmin thmax t skewmax t skewmax

28

and

tlmin t w td q min + thmax + t skewmax

d q min

Why is clock skew irrelevant in this example?

27

( (t

t w > t sumax or

+ tl min t w thmax

CS623

CS623

Sequential Systems Using Latches

Latches can be used to create sequential systems. However, since these are level-triggered clocking must be done carefully must ensure that state changes only once per clock cycle. tw < tff.min+ tD-Q.min

Dj Qj CLK Qi

tskew

Clocking Constraints with Latches

CKi CKj Dj Qj Di

tw tsu tw tskew

Comb. logic

CKj

Di

CKi

Comb. logic > (tD-Q.max + tff.max+ tsu.max)

CLK tff

CKj

tD-Q

Di

CKi

Qi

tskew

Qi

tff th

CLK

tff

Dj

Use narrow-width clock whose pulse width is less than the fastest possible path through the combinational logic.

1 April 2007 1 April 2007

tw < t D Qmin + t ffmin thmax tskewmax tw > tsumax

30

To guarantee correct next state, make sure that the clock period is longer than the worst-case propagation delay through the combinational logic.

29

CS623

Clocking Frequency with Latches

Tclk

CKi CKj Qj Dj

Dj

tskew tw tsu tD-Q tff tsu

Comb. logic

CKj

Di

CKi

Qi

tskew

Qj

CLK

tff

Di

Tclk > tskewmax + tw tsumin + t D Qmax + t ffmax + tsumax

1 April 2007

31

Vous aimerez peut-être aussi

- Grit: The Power of Passion and PerseveranceD'EverandGrit: The Power of Passion and PerseveranceÉvaluation : 4 sur 5 étoiles4/5 (588)

- 16-Bit Microcontroller IPDocument2 pages16-Bit Microcontroller IPashrafuli_44Pas encore d'évaluation

- The Yellow House: A Memoir (2019 National Book Award Winner)D'EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Évaluation : 4 sur 5 étoiles4/5 (98)

- Atmel MCS-51 Hardware ArchitectureDocument47 pagesAtmel MCS-51 Hardware Architectureashrafuli_44Pas encore d'évaluation

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeD'EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeÉvaluation : 4 sur 5 étoiles4/5 (5795)

- Wishbone System-On-Chip (Soc) Interconnection Architecture For Portable Ip CoresDocument140 pagesWishbone System-On-Chip (Soc) Interconnection Architecture For Portable Ip Coresashrafuli_44Pas encore d'évaluation

- Never Split the Difference: Negotiating As If Your Life Depended On ItD'EverandNever Split the Difference: Negotiating As If Your Life Depended On ItÉvaluation : 4.5 sur 5 étoiles4.5/5 (838)

- 8051 Microcontroller With RF ModuleDocument56 pages8051 Microcontroller With RF Moduleashrafuli_44Pas encore d'évaluation

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceD'EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceÉvaluation : 4 sur 5 étoiles4/5 (895)

- Large Egg Nutrition PDFDocument1 pageLarge Egg Nutrition PDFashrafuli_44Pas encore d'évaluation

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersD'EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersÉvaluation : 4.5 sur 5 étoiles4.5/5 (345)

- American Egg Board - Specifics About Eggs PDFDocument3 pagesAmerican Egg Board - Specifics About Eggs PDFashrafuli_44Pas encore d'évaluation

- Shoe Dog: A Memoir by the Creator of NikeD'EverandShoe Dog: A Memoir by the Creator of NikeÉvaluation : 4.5 sur 5 étoiles4.5/5 (537)

- ENC Egg Labeling Guide PDF Proof PDFDocument4 pagesENC Egg Labeling Guide PDF Proof PDFashrafuli_44Pas encore d'évaluation

- Aeb Buyers Guide PDFDocument56 pagesAeb Buyers Guide PDFashrafuli_44Pas encore d'évaluation

- The Little Book of Hygge: Danish Secrets to Happy LivingD'EverandThe Little Book of Hygge: Danish Secrets to Happy LivingÉvaluation : 3.5 sur 5 étoiles3.5/5 (400)

- Modelsim CMD ReferenceDocument453 pagesModelsim CMD Referenceashrafuli_44Pas encore d'évaluation

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureD'EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureÉvaluation : 4.5 sur 5 étoiles4.5/5 (474)

- Questa Sim User ManualDocument1 489 pagesQuesta Sim User Manualbesha198775% (4)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryD'EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryÉvaluation : 3.5 sur 5 étoiles3.5/5 (231)

- DD D GS: Jfet DC Source Data and ResultDocument12 pagesDD D GS: Jfet DC Source Data and ResultEris PresnediPas encore d'évaluation

- On Fire: The (Burning) Case for a Green New DealD'EverandOn Fire: The (Burning) Case for a Green New DealÉvaluation : 4 sur 5 étoiles4/5 (74)

- Lissajous PDFDocument2 pagesLissajous PDFmldgmPas encore d'évaluation

- The Emperor of All Maladies: A Biography of CancerD'EverandThe Emperor of All Maladies: A Biography of CancerÉvaluation : 4.5 sur 5 étoiles4.5/5 (271)

- Ies Electronics Engineering Microwave Engineering PDFDocument51 pagesIes Electronics Engineering Microwave Engineering PDFTHILAGAVATHI APas encore d'évaluation

- Arduino Spectum AnalyzerDocument4 pagesArduino Spectum Analyzernguyen van ANPas encore d'évaluation

- Poynting PATCH-26Document6 pagesPoynting PATCH-26Carlos CostaPas encore d'évaluation

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaD'EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaÉvaluation : 4.5 sur 5 étoiles4.5/5 (266)

- Network and Communication Important QuestionDocument9 pagesNetwork and Communication Important QuestionShadab AlamPas encore d'évaluation

- The Unwinding: An Inner History of the New AmericaD'EverandThe Unwinding: An Inner History of the New AmericaÉvaluation : 4 sur 5 étoiles4/5 (45)

- Acer 4253 - Zqe - ZQGDocument41 pagesAcer 4253 - Zqe - ZQGA Sufri ParaungiPas encore d'évaluation

- Team of Rivals: The Political Genius of Abraham LincolnD'EverandTeam of Rivals: The Political Genius of Abraham LincolnÉvaluation : 4.5 sur 5 étoiles4.5/5 (234)

- AR-727iV3: Part NO. AR-727i V3 AR-727CM V3Document4 pagesAR-727iV3: Part NO. AR-727i V3 AR-727CM V3jorge franco HerreraPas encore d'évaluation

- Service Manual: Hcd-Cpz1DabDocument90 pagesService Manual: Hcd-Cpz1Dabboroda2410Pas encore d'évaluation

- Prolink PWN3702PDocument2 pagesProlink PWN3702PBenny LukitoPas encore d'évaluation

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyD'EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyÉvaluation : 3.5 sur 5 étoiles3.5/5 (2259)

- ISCOM5104G-GP (T) Configuration Guide (Web) (Rel - 01)Document31 pagesISCOM5104G-GP (T) Configuration Guide (Web) (Rel - 01)Francois BeunierPas encore d'évaluation

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreD'EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreÉvaluation : 4 sur 5 étoiles4/5 (1091)

- Ffmpeg Codecs ListDocument10 pagesFfmpeg Codecs ListSharbate AzamPas encore d'évaluation

- Handover IEEEDocument9 pagesHandover IEEEnguyenky0511Pas encore d'évaluation

- Casa Systems C40G Converged Cable Access Platform (CCAP) : Data SheetDocument5 pagesCasa Systems C40G Converged Cable Access Platform (CCAP) : Data SheetVitaly ChistyakovPas encore d'évaluation

- Lecture 02Document19 pagesLecture 02Sajjad AhmadPas encore d'évaluation

- 1W Chapter 2 00 全まとめDocument62 pages1W Chapter 2 00 全まとめMinh Manh NgoPas encore d'évaluation

- 1 SKG Network Intro PDFDocument29 pages1 SKG Network Intro PDFVed BharathPas encore d'évaluation

- EN500 User ManualDocument12 pagesEN500 User ManualBasPas encore d'évaluation

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)D'EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Évaluation : 4.5 sur 5 étoiles4.5/5 (121)

- Silicon NPN Power Transistors: 2SD669 2SD669ADocument5 pagesSilicon NPN Power Transistors: 2SD669 2SD669AJaPan LifePas encore d'évaluation

- SyllabusDocument2 pagesSyllabusadithiyan baladjyPas encore d'évaluation

- 7.1.2.7 Packet Tracer - Logging Network ActivityDocument3 pages7.1.2.7 Packet Tracer - Logging Network ActivityIl IasPas encore d'évaluation

- App ListDocument12 pagesApp ListYobu Prabha100% (1)

- Digital Gauge Interface Device: For Connect All Digital Gauge or Measuring Devices To Read Measurement DataDocument2 pagesDigital Gauge Interface Device: For Connect All Digital Gauge or Measuring Devices To Read Measurement DataboonluePas encore d'évaluation

- Smart Monitoring Information System Based On RF 433 MHZ (SMIS)Document7 pagesSmart Monitoring Information System Based On RF 433 MHZ (SMIS)fan nstPas encore d'évaluation

- TCP ComDocument1 pageTCP Comsunil_ghadiya8276100% (1)

- Redundancy Load Balancing PDFDocument17 pagesRedundancy Load Balancing PDFMukesh SainiPas encore d'évaluation

- 1 13 010 Is mc1 - DatasheetDocument3 pages1 13 010 Is mc1 - DatasheetMuhammad ImranPas encore d'évaluation

- Airtel Useful NumbersDocument3 pagesAirtel Useful NumbersKelechi OgbonnayaPas encore d'évaluation

- Ocs Lab No 1Document3 pagesOcs Lab No 1Wajiha AhmedPas encore d'évaluation

- Her Body and Other Parties: StoriesD'EverandHer Body and Other Parties: StoriesÉvaluation : 4 sur 5 étoiles4/5 (821)

- Teletalk Bangladesh LTDDocument2 pagesTeletalk Bangladesh LTDFaishal YousufPas encore d'évaluation