Académique Documents

Professionnel Documents

Culture Documents

Procesador z80

Transféré par

Abraham ContrerasTitre original

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

Procesador z80

Transféré par

Abraham ContrerasDroits d'auteur :

Formats disponibles

INSTITUTO TECNOLGICO DE DURANGO

INGENIERA MECATRNICA

MICROCONTROLADORES

INVESTIGACIN DE LA ESTRUCTURA INTERNA DEL MICROPROCESADOR ZILOG Z80.

CATEDRTICO: M. C. JESS MONTESINOS MERAZ. ALUMNO: CONTRERAS RODRGUEZ ABRAHAM.

FECHA DE ENTREGA: 13 DE SEPTIEMBRE DE 2012

MICROPROCESADOR ZILOG Z80

El Zilog Z80 (Z80) es un microprocesador de 8 bits cuya arquitectura se encuentra a medio camino entre la organizacin de acumulador y de registros de propsito general. Si consideramos al Z80 como procesador de arquitectura de registros generales, se sita dentro del tipo de registro-memoria. Fue lanzado al mercado en julio de 1976 por la compaa Zilog, y se populariz en los aos 80 a travs de ordenadores como el Sinclair ZX Spectrum, Amstrad CPC o los ordenadores de sistema MSX. Es uno de los procesadores de ms xito del mercado, del cual se han producido infinidad de versiones clnicas, y sigue siendo usado de forma extensiva en la actualidad en multitud de sistemas embebidos.

INTRODUCCIN El Z80 estaba diseado para ser compatible a nivel de cdigo con el Intel 8080, de forma que la mayora de los programas para el 8080 pudieran funcionar en l, especialmente el sistema operativo CP/M El Z80 tena ocho mejoras fundamentales respecto al Intel 8080: Un conjunto de instrucciones mejorado, incluyendo los nuevos registros ndice IX e IY y las instrucciones necesarias para manejarlos. Dos bancos de registros que podan ser cambiados de forma rpida para acelerar la respuesta a interrupciones. Instrucciones de movimiento de bloques, E/S de bloques y bsqueda de bytes. Instrucciones de manipulacin de bits. Un contador de direcciones para el refrescamiento de la DRAM integrado, que en el 8080 tena que ser proporcionado por el conjunto de circuitos de soporte. Alimentacin nica de 5 voltios.

Necesidad de menos circuitos auxiliares, tanto para la generacin de la seal de reloj como para el enlace con la memoria y la E/S. Ms barato que el Intel 8080. El Z80 elimin rpidamente al Intel 8080 del mercado y se convirti en uno de los procesadores de 8 bits ms populares. Las primeras versiones funcionaban a 2,5 MHz, pero su velocidad ha aumentado hasta los 20 MHz. As, la versin ms utilizada fue el Z80A funcionando a 3,58 MHz (un cuarto de la frecuencia PAL o NTSC) siendo la velocidad de fbrica de 4 MHz. En la actualidad Zilog sigue fabricando versiones del Z80 original y otros modelos compatibles con l que mejoran las prestaciones. CARACTERSTICAS FUNDAMENTALES DEL Z80 1) El transporte de seales se realiza sobre tres buses, el bus de direcciones, el bus de datos, as como el bus de control. 2) Rgimen de interrupcin uniforme, con la posibilidad de encadenar las prioridades de los circuitos perifricos. 3) Alto grado de programabilidad. 4) Reloj nico. 5) Fuente de voltaje nica de +5 Volts. El microprocesador Z80 contiene las siguientes unidades funcionales: 1) 2) 3) 4) 5) 6) 7) 8) Unidad aritmtica y lgica. El contador de programa. El apuntador del stack. Registros de propsito general. Registros de ndice. Registros de interrupciones. Registro de banderas. Registro para refrescar memorias dinmicas.

USOS NOTABLES A comienzos de los aos 1980 el Z80 o versiones clnicas del mismo fueron usadas en multitud de ordenadores domsticos, como la gama MSX, el Radio Shack TRS-80, el Sinclair ZX80, ZX81 y ZX Spectrum. Las Game Boy y Game Boy Color de Nintendo utilizan una variante del Z80 fabricada por Sharp. CLNICOS Sharp y NEC fabrican clnicos del Z80 (Sharp LH-0080 y NEC PD780C). National Semiconductor fabric un procesador clnico, el NSC800, con tecnologa CMOS pero que no era compatible pin a pin. Hitachi fabric una

versin con tecnologa CMOS curiosamente la propia Zilog.

mejorada,

cuya

segunda

fuente

fue

En la actualidad la propia Zilog fabrica una versin mejorada del Z80 llamada eZ80, que funcionando a 50 MHz tiene un rendimiento similar a un Z80 funcionando a 150 MHz y adems puede direccionar hasta 16 MB de memoria RAM extendiendo el tamao de los registros, frente a los 64 KB del Z80. No todos los clones de este microprocesador tienen conectado el pin NMI, por lo que al intentar usarlo en algunos modelos este hace caso omiso.

NEC NEC PD780C, clon del Z80 en la placa madre de un ZX Spectrum.

Toshiba TMPZ84C015 - un Z80 que incluye funciones de perifricos y otros en el mismo chip. ESTRUCTURA A pesar de ser un microprocesador de 8 bits, el Z80 puede manejar instrucciones de 16 bits y puede direccionar hasta 64 KB de RAM. Una de las caractersticas ms reseables es que tiene las instrucciones del Intel 8080 como subconjunto, de modo que algunos ordenadores basados en Z80 podan ejecutar programas diseados para el CP/M del 8080. Esto ha hecho que los formatos de instruccin del Z80 sean bastante complejos, ya que tienen que mantener su compatibilidad con el 8080. Sin embargo el Z80 ha conseguido mejorar al microprocesador de Intel en velocidad, ha aadido nuevos modos de direccionamiento y contiene un juego de instrucciones ms amplio.

ARQUITECTURA FUNDAMENTAL DEL MICROPROCESADOR Z 80

LA UNIDAD ARITMTICA Y LGICA (ALU) Las operaciones del CPU Z80 se realizan con un grupo de dispositivos lgicos conocidos comnmente como unidad aritmtica y lgica (ALU) esta efecta las siguientes operaciones: 1) 2) 3) 4) 5) Suma binaria. Operaciones lgicas. Complementar a dos. Corrimiento de un bit a la derecha o a la izquierda. Registro de resultados importantes como el acarreo, signo, acarreo auxiliar, paridad o si el resultado es cero. 6) Comparaciones. 7) Poner, Limpiar o probar un bit.

EL CONTADOR DE PROGRAMA (PC) Es un registro de 16 bits, que continuamente tiene la direccin de la localidad de memoria siguiente que se va a accesar, de esa localidad obtiene el cdigo de la instruccin a ejecutarse, en la CPU el PC se incrementa en uno, cada vez que el microprocesador lee el cdigo de la instruccin contenida en la localidad direccionada, de esta forma el contador del programa direcciona secuencialmente las localidades de la memoria ROM, donde se encuentra almacenado el programa. EL APUNTADOR DEL STACK (SP) El microprocesador Z80 cuenta con el registro de pila (SP) o stack pointer que contiene una direccin de memoria RAM a partir de la cual y en forma descendente, se almacenan los contenidos de un par de registros, o a partir del cual en forma ascendente se obtienen los ltimos dos datos de 8 bits almacenados en esa rea, el SP es un registro de 16 bits, para almacenar en el stack el contenido de un par de registros se utiliza la instruccin PUSH y para cargar a un par de registros con los dos ltimos bytes del stack se utiliza la instruccin POP. REGISTROS DE PROPSITO GENERAL El microprocesador Z80 contiene 14 registros de 8 bits separados en dos grupos: GRUPO 1; A, B, C, D, E, H, y L. GRUPO 2; A', B', C', D', E', H' y L.

Todas las instrucciones trabajan con los registros del grupo 1, con las instrucciones EX y EXX se logra el intercambio entre los contenidos de los registros del grupo 1 con los contenidos de los registros del grupo 2, el grupo 2 se utiliza en cierta forma como stack del grupo 1, dentro de la propia CPU. Con los 14 registros de propsito general se efectan por medio de las instrucciones las siguientes funciones: 1) 2) 3) 4) 5) 6) Recibir datos desde la memoria. Enviar datos hacia la memoria. Incrementar o decrementar en uno su contenido. Formar una direccin con el contenido de un par de registros. Transferir datos entre los registros. Obtener un operando durante las funciones de la ALU.

REGISTROS DE NDICE IX e IY. Estos son registros de 16 bits cada uno y conservan direcciones base que se usan para modo de direccionamiento indexado, en este modo un registro de ndice se usa como base para apuntar a una regin de la memoria. La direccin efectiva de la localidad de memoria a donde se va a depositar el dato o de donde se va a leer, se obtiene, al sumar el contenido del registro de ndice y el valor de 8 bits contenido en el campo de "desplazamiento" de las instrucciones que emplean direccionamiento con ndice, estos desplazamientos se especifican con nmeros enteros signados con el complemento a dos. REGISTRO DE INTERRUPCIONES El Z80 opera en modo de interrupcin en el que responde como una "llamada" indirecta en respuesta a una solicitud de interrupcin. El registro I se usa para este propsito almacenando los 8 bits ms significativos de la direccin indirecta mientras que el dispositivo que interrumpe proporciona los 8 bits menos significativos de la direccin ndice, esta caracterstica permite que las rutinas servicio de las interrupciones se localicen en cualquier parte de la memoria y que se puedan accesar en un tiempo muy corto. BANDERAS DE ESTADO El microprocesador Z80 tiene un registro de 8 Flips Flops, para monitorear ciertos resultados de las operaciones de la ALU, a la informacin que almacenan estos flips-flops se conoce como banderas de estado, las banderas se actualizan despus de cada operacin con alguno de los registros, no todas las operaciones modifican a todas las banderas, de los 8 bits del registro de banderas, nicamente seis registran informacin til para el programador, cuatro de estas banderas se prueban, esto es, se usan como condiciones de salto (JP), llamada (CALL), o regreso (RET), estas banderas son; 1) La paridad o sobre flujo (P/V). El registro "P" se utiliza para realizar funciones auxiliares necesarias para el usuario, le sirven para interpretar los resultados, es uno cuando el resultado de la operacin lgica del complemento a dos produce un acarreo, de otro forma es un cero lgico. 2) SIGN (S); Set if into the result of ALU operation the most significant bit = 1, otherwise reset. 3) ZERO (Z); Set if result of ALU operation is zero otherwise it is reset. 4) AUXILIARY CARRY; Set if carry out results b3 into b4 otherwise reset. 5) CARRY (C); Set if result of addition or subtraction operation result in a carry or borrow of the highest order bit, otherwise reset.

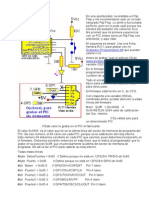

TERMINALES DEL MICROPROCESADOR Z80 El Z80 es un microprocesador de 8 bits y cuenta con 158 instrucciones y 10 modos de direccionamiento. El circuito integrado del microprocesador Z80 se deposita en un encapsulado Dual In Line de 40 terminales, de las cuales 5 son nicamente de entrada, 24 son de salida y 8 son bidireccionales, adems, existen dos que sirven para conectar la fuente de alimentacin y otra ms que es la entrada del reloj.

Todas ellas tienen caractersticas elctricas compatibles con la tecnologa TTL, el intervalo de voltajes de entrada para un cero lgico es; 0.3 Vil 0.8 volts, el intervalo del voltaje de entrada para un uno lgico es; 2.0 Vih Vcc, el voltaje mximo de salida para un cero lgico es; Vol=0.4Volts, y el voltaje mnimo de salida para un uno lgico es; Voh=2.4Volts El Z80 opera con una fuente de alimentacin de +5.0 Volts conectada a la terminal 11, (pin 11), la tierra de la fuente se conecta a la terminal GND, (pin 29), el consumo tpico de corriente para el Z80 es de 90 mA. Cuenta con 18 registros de 8 bits y 4 registros de 16 bits, todos los registros del Z80 se implementan con una RAM esttica, los registros incluyen 2 bancos de 6 registros de propsito general, que se usan individualmente como registros de 8 bits, o en pares como registros de 16 bits, existen tambin 2 bancos de registros denominados "acumulador" y "banderas", adems cuenta con 6 registros de propsito especial, 4 registros de 16 bits, PC, SP, IX e IY, y 2 registros de 8 bits, el registro del refresh "R" y el registro de interrupciones "I",

la aritmtica de 8 bits de las funciones, y las instrucciones lgicas de la CPU se ejecutan en la ALU, la ALU realiza las siguientes funciones son: 1) Sumar. 2) Restar. 3) Funcin lgica AND. 4) Funcin lgica OR. 5) Funcin lgica OR-EX. 6) Comparacin. 7) Desplazamientos a la derecha y a la izquierda. 8) Incrementar bytes. 9) Decrementar bytes. 10) Poner bits en uno lgico. 11) Poner bits en cero lgico y 12) Comprobar el estado de los bits. LNEAS DE DIRECCIONES (A0 - A15), Pines 30-40, 1-5 respectivamente Se forman con 16 lneas de direcciones, tienen la facultad de establecerse en tercer estado, estas seales proporcionan las direcciones correspondientes a intercambios de datos entre la memoria, la CPU y los puertos de los perifricos, la capacidad de direccionamiento con 16 bits es de 64 Kbytes y 256 puertos de entrada y salida, son activas en estado alto, los 8 bits menos significativos se usan para permitirle al usuario seleccionar los 256 puertos E/S, (A0-A7), en donde A0 es el bit menos significativo. LNEAS DE DATOS (DO - D7), Pines 14, 15, 12, 8, 7, 9, 10 y 13 Se forman con 8 lneas de datos bidireccionales con capacidad del tercer estado, son activas en nivel alto, se utilizan para el intercambio de datos con la memoria, y perifricos de E/S. CICLO DE MAQUINA UNO (M1), Salida activa en nivel bajo, indica que en este ciclo de mquina uno el microprocesador va a obtener el cdigo operacional de una instruccin, en las instrucciones que tienen un cdigo operacional de 2 bytes esta seal se opera al obtener cada uno de los bytes del cdigo operacional, al igual que para indicar el reconocimiento de un ciclo de interrupcin cuando ocurre (IORQ)'. REQUERIMIENTO DE MEMORIA (MREQ)', Pin 19 Salida activa en nivel bajo, esta seal indica una peticin que interrelaciona a la memoria con la CPU, obtiene una direccin valida de las lneas de direccionamiento, esta terminal tiene capacidad del tercer estado.

REQUERIMIENTO DE E/S (IORQ), Pin 20 Es salida triestado activa en nivel bajo, esta seal indica que la mitad baja del bus de direcciones mantiene una direccin vlida de E/S, para efectuar una operacin de lectura o escritura de E/S, se genera esta seal cuando el ciclo de maquina 1 (M1) reconoce una interrupcin, indica que el vector de respuesta de la interrupcin se coloca en el bus de datos, las operaciones de reconocimiento de interrupcin ocurren durante el ciclo de maquina 1, mientras que las operaciones de E/S nunca se producen durante este ciclo. LECTURA (RD), Pin 21 Salida triestado activa en nivel bajo, indica que la CPU desea leer datos desde la memoria de un dispositivo externo de E/S, el dispositivo E/S se direcciona a la memoria o al perifrico, se usa esta terminal para dirigir los datos al bus de datos de la CPU. ESCRITURA (WR)', pin 22 Salida triestado activa en nivel bajo, indica que el bus de datos de la CPU va a obtener datos vlidos para ser almacenados en la memoria o en algn dispositivo de E/S. REFRESCO DE LA MEMORIA DINMICA (RFSH)', Pin 28 Salida activa en nivel bajo, indica que los siete bits inferiores de las lneas de direccionamiento contienen una direccin vlida de refresco de memoria, se utiliza para el mantenimiento de datos en memorias dinmicas, con esta se efecta una lectura de refrescamiento para todas las memorias dinmicas. PARO (HALT), Pin 18 Salida que activa en nivel bajo, indica que la CPU realiza una instruccin por software de paro (HALT), y que espera una interrupcin (NMI)' o (INT)' antes de que contine la operacin, mientras permanezca en este estado la CPU ejecuta operaciones NOP, para mantener activo el refresco de las memorias dinmicas, al aplicarse un reset se continua con la operacin. ESPERA (WAIT), Pin 24 Es una entrada activa en nivel bajo, le indica al microprocesador que la memoria direccionada o los dispositivos perifricos de E/S no son tan rpidos como para realizar una transferencia de datos a la velocidad de la CPU, o no estn listos para una transferencia de informacin, la CPU continua con el estado de espera durante todo el tiempo que esta terminal es activa, esto les permite a los otros dispositivos sincronizarse con la CPU.

REQUISICIN DE INTERRUPCIN MASCARABLE (INT), Pin 16 Entrada activa en nivel bajo, esta terminal se acciona con dispositivos E/S externos, una requisicin (INT)' se atiende al final de la instruccin que se ejecuta, si el enable interno del Flip Flop de interrupcin IFF1 controlado por software se encuentra habilitado, y si la requisicin de bus no esta activa, al aceptar la CPU una interrupcin enva una seal de reconocimiento, la peticin de E/S se realiza durante el ciclo de mquina 1, al principio del siguiente ciclo de instruccin, esta peticin solo es valida bajo control del programa interno, reconociendo la CPU tres modos diferentes de interrupcin. INTERRUPCIN NO MASCARABLE (NMI)', Pin 17 Entrada que se activa con un flanco de bajada mediante un impulso que identifica una interrupcin obligada, posiciona al contador de programa (PC) en la direccin 0066h desde donde continua el proceso, esta tiene una prioridad ms alta que la interrupcin (INT)' y siempre se reconoce al final de la instruccin que se ejecuta, independientemente del estado del IFF1, el contador de programa PC se almacena automticamente en el stack pointer externo de forma que el usuario regrese al programa en el mismo punto del que fue interrumpido. REHABILITACIN (RESET), Pin 26 Entrada que se activa con un flanco de bajada mediante un impulso, obliga a la CPU a reiniciar su actividad, coloca al contador de programa (PC) en la localidad de inicio de memoria 0000h, desde donde empieza el proceso, durante este tiempo el bus de direcciones y el bus de datos adquieren el estado de alta impedancia y todas las terminales de control de salida adquieren el estado inactivo. REQUERIMIENTO DE LAS TERMINALES DE LA CPU (BUSRQ), Pin 25 Esta entrada es activa en nivel bajo, le indica a la CPU que coloque todas sus lneas en estado de alta impedancia, (tan pronto el ciclo de maquina 1 actual termine), a peticin del perifrico externo que desea tomar el control del sistema, regresa el control a la CPU cuando esta seal (BUSRQ)' pasa al nivel alto, se utiliza para pedir que el bus de direcciones, el bus de datos y las terminales de salida triestado del bus de control vayan a un estado de alta impedancia de tal forma que otros dispositivos controlen esos buses. ENTREGA DE LAS TERMINALES DE LA CPU (BUSAK)', Pin 23 Salida activa en nivel bajo, es una indicacin para el perifrico que efecta una peticin (BUSRQ)' de que su peticin ha sido concedida por parte del microprocesador, sirve para indicar al dispositivo que solicita este reconocimiento, que el bus de direcciones, el bus de datos y el bus de las

terminales de control triestado han sido puestos en su estado de alta impedancia y que el dispositivo externo puede ahora controlar estas terminales. RELOJ (CK), Pin 6 Entrada configurada por un tren de impulsos tiles, es la diferencia que permite la secuencia de tiempos de operacin, se implanta fsicamente con un oscilador de onda cuadrada cuya frecuencia depende del tipo de caractersticas de la CPU Z80, requiere oscilacin de una fase con niveles TTL, una forma de satisfacer todos los requerimientos de voltaje es por medio de una resistencia de activacin "pull up" de 330 ohms conectada entre +Vcc y la terminal de salida de un oscilador implantado con circuitos TTL que generen oscilaciones. ALIMENTACIN POSITIVA DE +5 VOLTS (Vcc), Pin 11 Esta es una entrada de alimentacin de tensin de +5 volts con un 5 % de tolerancia. TIERRA (GND), Pin 29 Terminal de alimentacin negativa, requiere un potencial de 0.0 volts que sirven de referencia para la interconexin de los dispositivos.

CONCLUSIN El microprocesador Zilog Z80 contiene 8 bits y manejar instrucciones de 16 bits; es de alta programabilidad y es compatible con el microprocesador 8080 de Intel. Ha tenido su gran popularidad ya que inicio en la dcada de los 80s donde se empezaban a crear nuevos aparatos que hicieron una revolucin en la vida de las personas para uso domsticos, personales e industriales y estos necesitaban un microprocesador potente para su poca donde este le ganaba a varios de sus competencias por que tenia mejores caractersticas de funcionamiento y/o tenia un precio mas barato en el mercado. Donde este fue clonado en su poca de auge por fbricas pero con deficiencias en frecuencia, programacin, costo, respuesta, etctera. Sin poder igualar al Z80 de la marca Zilog donde ahorita todava se sigue fabricando utilizndose mas en sistemas embebidos donde la marca Zilog lo ha mejorado llamndolo eZ80

Vous aimerez peut-être aussi

- Antenas verticales para bajas frecuencias: (MF y HF)D'EverandAntenas verticales para bajas frecuencias: (MF y HF)Pas encore d'évaluation

- Microprocesador Z80Document8 pagesMicroprocesador Z80Alissa100% (1)

- Interrupciones Del Procesador Z80Document5 pagesInterrupciones Del Procesador Z80Joel Lema ChulliPas encore d'évaluation

- Informe Z80Document15 pagesInforme Z80Bry Ruiz MendezPas encore d'évaluation

- Curso Microprocesadores y Microcontroladores Unidad 1Document87 pagesCurso Microprocesadores y Microcontroladores Unidad 1Carlos BaezPas encore d'évaluation

- AmstradPersonal02 PDFDocument88 pagesAmstradPersonal02 PDFTorres Danilo MauricioPas encore d'évaluation

- Bootloader USB para PIC18F4550 A FullDocument9 pagesBootloader USB para PIC18F4550 A Fullhackheredgar100% (2)

- Todo Sobre El Procesador Z80Document290 pagesTodo Sobre El Procesador Z80Manuel Riveros Ticona100% (1)

- Curso de Microcontroladores Pic16f87xDocument43 pagesCurso de Microcontroladores Pic16f87xEsteban Laime GonzalesPas encore d'évaluation

- Manejo de LCD y GLCDDocument18 pagesManejo de LCD y GLCDLuisHernandezPas encore d'évaluation

- Guia Pics CompletaDocument142 pagesGuia Pics Completaapi-27535945100% (4)

- Introducción A La EspecificaciónDocument13 pagesIntroducción A La Especificaciónparayasa50Pas encore d'évaluation

- (BASIC-16f877a) Encender y Apagar Led Con El Mismo PulsadorDocument1 page(BASIC-16f877a) Encender y Apagar Led Con El Mismo PulsadorJeysonPas encore d'évaluation

- LCD y GLCD Con Pic 16f877a (Informe 4)Document26 pagesLCD y GLCD Con Pic 16f877a (Informe 4)davicho47100% (2)

- Capitulo8. USART Del ATmega32 (Español)Document29 pagesCapitulo8. USART Del ATmega32 (Español)Fortino100% (5)

- Manual IceplusDocument40 pagesManual IceplusEmilioPas encore d'évaluation

- Programador de Pics 16F84 PDFDocument7 pagesProgramador de Pics 16F84 PDFRaul MonroyPas encore d'évaluation

- Simulacdor Z80Document3 pagesSimulacdor Z80Saquil WillyPas encore d'évaluation

- Guia de Visualino PDFDocument37 pagesGuia de Visualino PDFluis0% (1)

- RevD Manual Compl SC5E MDB DUALDocument35 pagesRevD Manual Compl SC5E MDB DUALbettdeki0% (1)

- Probador Puerto Paralelo2Document5 pagesProbador Puerto Paralelo2Miguelina ParadaPas encore d'évaluation

- P05 Programacion en MikroBasicDocument9 pagesP05 Programacion en MikroBasicRicardo NarvaezPas encore d'évaluation

- Manual MikrocDocument131 pagesManual MikrocJUAR_22Pas encore d'évaluation

- EL - Sistemas Integrados Con Arduino PDFDocument151 pagesEL - Sistemas Integrados Con Arduino PDFmiltonPas encore d'évaluation

- Tutorial Proton Parte 2Document10 pagesTutorial Proton Parte 2HectorLopezPas encore d'évaluation

- Curso de Microcontroladores PIC16F87XDocument69 pagesCurso de Microcontroladores PIC16F87XUlises Aguilar100% (1)

- Zilog Z80 Es Un Microprocesador de 8 Bits Cuya Arquitectura Se Encuentra A Medio Camino Entre La Organización de Acumulador y de Registros Generales.Document9 pagesZilog Z80 Es Un Microprocesador de 8 Bits Cuya Arquitectura Se Encuentra A Medio Camino Entre La Organización de Acumulador y de Registros Generales.Sergio Ibarra MPas encore d'évaluation

- Un Microprocesador de 8 Bits Z80Document85 pagesUn Microprocesador de 8 Bits Z80Sebastián SandovalPas encore d'évaluation

- Curso - PIC18Document78 pagesCurso - PIC18Roberto Bravo MuñozPas encore d'évaluation

- GLCDDocument3 pagesGLCDChristian CanchigniaPas encore d'évaluation

- Curso MikrobasicDocument9 pagesCurso MikrobasicEdson RodasPas encore d'évaluation

- Cambiar de 16F84A - A - 16F628ADocument4 pagesCambiar de 16F84A - A - 16F628Aroky23Pas encore d'évaluation

- Ccs Protocolo SpiDocument29 pagesCcs Protocolo SpiMario Andres Caceres Nocera0% (1)

- Caracteristicas PC Industrial SimaticDocument30 pagesCaracteristicas PC Industrial SimaticAlberto Lopez SanchezPas encore d'évaluation

- Arduino DUE Marzo2014Document63 pagesArduino DUE Marzo2014Sherma007100% (1)

- PP PLC 003 v1.0 PLC Mitsubishi - Programacion SFCDocument17 pagesPP PLC 003 v1.0 PLC Mitsubishi - Programacion SFCRicardo Pelao LetelierPas encore d'évaluation

- Atmega164p EspañolDocument378 pagesAtmega164p EspañolMarco SolísPas encore d'évaluation

- Tutorial ArdublockDocument4 pagesTutorial ArdublockAbigail Noelia Panozo GonzalesPas encore d'évaluation

- Manual LotoDocument131 pagesManual LotoCarlos ArangurenPas encore d'évaluation

- Contador de Programa Del Microprocesador Z80Document10 pagesContador de Programa Del Microprocesador Z80FernandoQuisaguano0% (1)

- Detector de Fugas en Capacitores ElectroliticosDocument14 pagesDetector de Fugas en Capacitores ElectroliticosEfrain ConriquezPas encore d'évaluation

- Tema - 7 Funciones en CCS PDFDocument38 pagesTema - 7 Funciones en CCS PDFAJ SotoPas encore d'évaluation

- Manual de Manejo de MikrocDocument42 pagesManual de Manejo de MikrocFran-klin YalliPas encore d'évaluation

- Programador Universal Microchip Picstart PlusDocument51 pagesProgramador Universal Microchip Picstart PlusELPICHUE100% (1)

- Pic16f887 EntregarDocument171 pagesPic16f887 EntregarErnesto NetoPas encore d'évaluation

- Primera: ParteDocument3 pagesPrimera: ParteJuan Luis100% (1)

- El Módulo Adc de Los Avr PDFDocument27 pagesEl Módulo Adc de Los Avr PDFmi_papiPas encore d'évaluation

- 12F629 Flip FlopDocument2 pages12F629 Flip FlopBedia FrankPas encore d'évaluation

- Conectando Un PIC Al Puerto Serie (RS232) - PROTONDocument8 pagesConectando Un PIC Al Puerto Serie (RS232) - PROTONEstetico100% (1)

- P01 IDE MikroC Edicion Compilacion Simulacion y Depuracion de Un ProgramaDocument15 pagesP01 IDE MikroC Edicion Compilacion Simulacion y Depuracion de Un ProgramaaLciLPas encore d'évaluation

- ARM 7y9Document94 pagesARM 7y9alfredo_06_82@hotmail.comPas encore d'évaluation

- Catalogo PatziTec Marzo21Document41 pagesCatalogo PatziTec Marzo21Abel FloresPas encore d'évaluation

- EL Libro SlackwareDocument126 pagesEL Libro SlackwareMaiman LatoPas encore d'évaluation

- Monitoreo, control y adquisición de datos con arduino y visual basic .netD'EverandMonitoreo, control y adquisición de datos con arduino y visual basic .netPas encore d'évaluation

- Proton - Ucting.udg - MX Dpto Maestros Mateos z80 ArquitectuDocument7 pagesProton - Ucting.udg - MX Dpto Maestros Mateos z80 Arquitectusanchez2328Pas encore d'évaluation

- Microprocesador Z80Document8 pagesMicroprocesador Z80Eliuth Cruz CamarilloPas encore d'évaluation

- Arquitectura Del Microprocesador z80Document5 pagesArquitectura Del Microprocesador z80manue1969Pas encore d'évaluation

- Arq-24 933 045-Z80Document21 pagesArq-24 933 045-Z80Brigitte RivasPas encore d'évaluation

- Tarea - Pizarras VirtualesDocument6 pagesTarea - Pizarras VirtualesHelenBelénDesiderioPortillaPas encore d'évaluation

- Material Uso de Mentimeter PDFDocument14 pagesMaterial Uso de Mentimeter PDFJUDITH ORTIZPas encore d'évaluation

- Capitulo 7Document21 pagesCapitulo 7Henry JiménezPas encore d'évaluation

- Examen de Excel 2016Document5 pagesExamen de Excel 2016kevin Acosta ChPas encore d'évaluation

- U04 - Guía Del Estudiante FSD 1Document8 pagesU04 - Guía Del Estudiante FSD 1Washington CeliPas encore d'évaluation

- Curso WhatsApp BusinessDocument16 pagesCurso WhatsApp BusinessIng. Alicia M. Castillo H.Pas encore d'évaluation

- Manual de ScrivenerDocument88 pagesManual de Scrivenermousescribd93% (15)

- Terminos ClavesDocument5 pagesTerminos ClavesAlexa CardozaPas encore d'évaluation

- Configuración Dispositivos MultifunciónDocument38 pagesConfiguración Dispositivos MultifuncióndavidPas encore d'évaluation

- Google Ads Measurement Certification Exam Answers ES+LATAM Version New VersionDocument303 pagesGoogle Ads Measurement Certification Exam Answers ES+LATAM Version New VersionAnoni HomemPas encore d'évaluation

- Presentacion OhanaNetworks2020Document13 pagesPresentacion OhanaNetworks2020Carlos Moises Cajachagua GarciaPas encore d'évaluation

- Introduccion Al STEP7 PDFDocument16 pagesIntroduccion Al STEP7 PDFJuan ChazarraPas encore d'évaluation

- Análisis Sintáctico DescendenteDocument7 pagesAnálisis Sintáctico DescendenteMiguel Enrique Junior Zavaleta RojasPas encore d'évaluation

- Instructivo de Afiliación y Actualización de Datos Siseve 2020 1Document11 pagesInstructivo de Afiliación y Actualización de Datos Siseve 2020 1cynthia quispe ninaPas encore d'évaluation

- Exposición de Correo ElectrónicoDocument10 pagesExposición de Correo ElectrónicomeliyirmariPas encore d'évaluation

- Unidad 2 Algoritmos Basicos de Dibujo en 2 Dimensiones PDFDocument40 pagesUnidad 2 Algoritmos Basicos de Dibujo en 2 Dimensiones PDFCarlos MichuPas encore d'évaluation

- SAM Fusion Informe 4Document13 pagesSAM Fusion Informe 4Eduardo GarciaPas encore d'évaluation

- Trabajo Final Sistemas OperativosDocument16 pagesTrabajo Final Sistemas Operativossilvia angueiraPas encore d'évaluation

- 12.1.4.4 Lab - Mobile Device FeaturesDocument4 pages12.1.4.4 Lab - Mobile Device FeaturesELVIS EMANUEL SANDOVAL SUAREZPas encore d'évaluation

- Administracion de Recursostarea Semana 4Document4 pagesAdministracion de Recursostarea Semana 4Martin Alejandro Catrilef Fuentes100% (3)

- Adriana SalinasDocument8 pagesAdriana SalinasAdriana SalinasPas encore d'évaluation

- Dii XXXX Fav Seguridad y Prevencion Ciudadana Ley Integral para La Seguridad en Las Telecomunicaciones en La Republica de Honduras 1Document22 pagesDii XXXX Fav Seguridad y Prevencion Ciudadana Ley Integral para La Seguridad en Las Telecomunicaciones en La Republica de Honduras 1Dirección Ejecutiva C-LibrePas encore d'évaluation

- Plantilla Periodico5Document4 pagesPlantilla Periodico5amandaPas encore d'évaluation

- Manual de VBA para ExcelDocument87 pagesManual de VBA para Excelantonio_c200Pas encore d'évaluation

- Procesamiento Por LotesDocument38 pagesProcesamiento Por LotesDaniel Lagos HernandezPas encore d'évaluation

- Aventura Digital Crear Tu Pagina en 7 Dias v1 0Document43 pagesAventura Digital Crear Tu Pagina en 7 Dias v1 0Ñelo SaPas encore d'évaluation

- ACA No.2 GERENCIA DE PROYECTOS FEBRERO 2023Document1 pageACA No.2 GERENCIA DE PROYECTOS FEBRERO 2023sebasghostPas encore d'évaluation

- Resumen Ejecutivo Del Proyecto Impresión 3DDocument2 pagesResumen Ejecutivo Del Proyecto Impresión 3DArlette CruzPas encore d'évaluation

- Guía de Comandos IOS CISCODocument13 pagesGuía de Comandos IOS CISCOCarlos Lopera100% (2)

- Curriculum VitaeDocument3 pagesCurriculum VitaeJeff LimaPas encore d'évaluation