Académique Documents

Professionnel Documents

Culture Documents

Boundary Scan

Transféré par

mechbull11Description originale:

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

Boundary Scan

Transféré par

mechbull11Droits d'auteur :

Formats disponibles

Boundary Scan

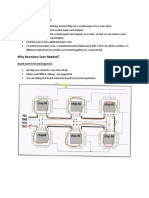

Developed to test interconnect between chips on PCB

Originally referred to as JTAG (Joint Test Action Group) Uses scan design approach to test external interconnect No-contact probe overcomes problem of in-circuit test: surface mount components with less than 100 mil pin spacing

double-sided component mounting micro- and floating vias

Standardized test interface

IEEE standard 1149.1 Four wire interface TMS - Test Mode Select

I/O buffer w/ BS cell

Core Application Logic

BS Int

TCK - Test Clock TDI - Test Data In BS chain TDO - Test Data Out TRST - reset (optional & rarely included)

TMS TCK TDI TDO

Additional logic :

Boundary Scan (cont.)

1 Boundary Scan cell per I/O pin Test Access Port (TAP)

4-wire interface TMS

TCK TDI TDO

TDI

BS Chain (I/O buffers) User Defined Registers Bypass Register Instruction Decoder Instruction Register MUX MUX

FF

TDO

TAP controller

16-state FSM controlled by TMS & TCK

various registers for instructions

operations

TMS TCK

TAP Controller

Boundary Scan Cell Architecture

MUX IN MUX

Basic BS Cell

OUT SOUT D Q CAP CK D Q UPD CK Mode_Control

Bi-directional buffers require multiple BS cells

BS test data in (SIN) Input data to IC core Input Cell

SIN

Shift_DR Capture_DR Update_DR

BS Cell Operation Operational Data Mode Transfer Normal IN OUT Scan SIN CAP Capture IN CAP Update CAP UPD

Tri-state control Control Cell From IC core Output data Output From IC core Cell

Pad

BS test data out (SOUT)

Boundary Scan TAP Controller Operation

0 Note: transitions on rising edge of TCK based on TMS value 1 Test Logic Reset 0 Run Test Idle 1 Select DR

0

1 Select IR

0

Shift DR

1

Shift IR

1

Exit-1 DR 1 0

0

Exit-1 IR 1 0 0

0

Pause DR

1

Pause IR

1

Exit-2 DR

1

Exit-2 IR

1

Update DR

1 0

Update IR

1 0

1. Send test instruction serially via TDI into Instruction Register (shift-IR) 2. Decode instruction and configure test circuitry (update-IR) 3. Send test data serially into Data Register (shift-DR) via TDI 4. Execute instruction (updateDR & capture-DR) 5. Retrieve test results captured in Data Register (shift-DR) serially via TDO

Capture DR

0

Capture IR

0

Boundary Scan Instructions

Defined by IEEE 1149.1 standard:

Mandatory Instructions Extest to test external interconnect between ICs Bypass to bypass BS chain in IC Sample/Preload BS chain samples external I/O IDCode 32-bit device ID Optional Instructions Intest to test internal logic within the IC RunBIST to execute internal Built-In Self-Test if applicable (this is rare) UserCode 32-bit programming data code for programmable logic circuits User Defined Instructions

Boundary Scan: User-Defined Instructions

User-defined instructions facilitate: public instructions (available for customer use) private instructions (for the manufacturer use only) extending the standard to a universal interface for any system operation feature or function a communication protocol to access new IC test functions

In FPGAs

Access to configuration memory to program device Access to FPGA core programmable logic & routing resources Xilinx is one of few to offer this

Boundary Scan: Advantages

Its a standard!!! (IEEE 1149.1) allows mixing components from different vendors provides excellent interface to internal circuitry Supported by CAD tool vendors, IC & FPGA manufacturers Allows testing of board & system interconnect back-plane interconnect test w/o using PCB functionality very high fault coverage for interconnect Useful in diagnosis & FMA provides component-level fault isolation allows real-time sampling of devices on board useful at wafer test (fewer probes needed) BS path reconfigured to bypass ICs for faster access P1500 uses BS circuitry around cores inside SoCs

TRST pin is not optional in order to initialize all cores

Boundary Scan: Disadvantages

Overhead: Logic: about 300 gates/chip for TAP + about 15 gates/pin overall overhead typically small (1-3%) but significant for only testing external interconnect especially tri-state (2 cells) & bi-directional buffers (3 cells) I/O Pins: 4 5 if optional TRST (Test Reset) pin is included

Must be included in SoC cores to meet P1500 standards

I/O delay penalty 1 MUX delay on all input & output pins this can be reduced by design Internal scan design cannot have multiple chains Cannot test at system clock speed But internal BIST can run at system clock speed

Vous aimerez peut-être aussi

- Digital Circuit Testing: A Guide to DFT and Other TechniquesD'EverandDigital Circuit Testing: A Guide to DFT and Other TechniquesPas encore d'évaluation

- 15-Chapter 10 BSCAN 1500 PDFDocument81 pages15-Chapter 10 BSCAN 1500 PDFVeeranjaneyulu DhikondaPas encore d'évaluation

- Why Boundary Scan Needed?Document39 pagesWhy Boundary Scan Needed?srikanth100% (1)

- VLSI Test Principles and Architectures: Design for TestabilityD'EverandVLSI Test Principles and Architectures: Design for TestabilityÉvaluation : 4.5 sur 5 étoiles4.5/5 (4)

- Jtag PresentationDocument21 pagesJtag PresentationNivaz ChockkalingamPas encore d'évaluation

- Digital Testing: Key Concepts of Scan-Path DesignDocument54 pagesDigital Testing: Key Concepts of Scan-Path DesignaguohaqdoPas encore d'évaluation

- Tap ControllerDocument16 pagesTap ControllerMoin PashaPas encore d'évaluation

- Testing and Design-for-Testability (DFT) For Digital Integrated CircuitsDocument95 pagesTesting and Design-for-Testability (DFT) For Digital Integrated Circuitsnagabhairu anusha100% (1)

- Logic BIST Case Studies and Real IssuesDocument10 pagesLogic BIST Case Studies and Real IssuesprakashthamankarPas encore d'évaluation

- Asic Design Flow:: Specification FloorplanDocument9 pagesAsic Design Flow:: Specification Floorplanp gangadhar KumarPas encore d'évaluation

- Using OCC For Full Scan Design PDFDocument6 pagesUsing OCC For Full Scan Design PDFUmesh ParasharPas encore d'évaluation

- DFT DRC - PPT 0Document3 pagesDFT DRC - PPT 0Mohan RajPas encore d'évaluation

- Test PointsDocument21 pagesTest Pointsanusha killariPas encore d'évaluation

- Scan Chain Insertion and ATPG Using Design Compiler and TetraMAXDocument47 pagesScan Chain Insertion and ATPG Using Design Compiler and TetraMAXLakshmi PrasadPas encore d'évaluation

- UncertaintyDocument24 pagesUncertaintyramana459Pas encore d'évaluation

- Automating P1500 Wrapper CreationDocument24 pagesAutomating P1500 Wrapper CreationKrish GokulPas encore d'évaluation

- JTAG Boundary Scan TestingDocument12 pagesJTAG Boundary Scan TestinglavanyaPas encore d'évaluation

- Scan InsertionDocument40 pagesScan InsertionAmena FarhatPas encore d'évaluation

- How To Use Embedded Instruments and IJTAG-JTAG An IEEE P1687 Tutorial PDFDocument10 pagesHow To Use Embedded Instruments and IJTAG-JTAG An IEEE P1687 Tutorial PDFAnjali TailorPas encore d'évaluation

- DFT Lbist PDFDocument10 pagesDFT Lbist PDFAman TyagiPas encore d'évaluation

- Hold and Setup Violation and SDFDocument2 pagesHold and Setup Violation and SDFIlaiyaveni IyanduraiPas encore d'évaluation

- An Introduction To DFT - Bridging & Switch Level FaultsDocument24 pagesAn Introduction To DFT - Bridging & Switch Level FaultsNaga NitheshPas encore d'évaluation

- Testing of Repairable Embedded Memories in SoC Approach and ChallengesDocument6 pagesTesting of Repairable Embedded Memories in SoC Approach and Challengesassantiago1Pas encore d'évaluation

- DFTC1 2007.12 LabGuide-đã Chuyển ĐổiDocument123 pagesDFTC1 2007.12 LabGuide-đã Chuyển Đổihung nguyenPas encore d'évaluation

- MBIST Verification Best Practices ChallengesDocument5 pagesMBIST Verification Best Practices ChallengessureshPas encore d'évaluation

- Cell-Aware: ImproveDocument5 pagesCell-Aware: ImproveSiva SreeramdasPas encore d'évaluation

- VLSIGURU SCAN INSERTION LABDocument2 pagesVLSIGURU SCAN INSERTION LABsenthilkumarPas encore d'évaluation

- DFT (Design For Testability)Document21 pagesDFT (Design For Testability)lavanyaPas encore d'évaluation

- Layout Synthesis Benchmarks Focus on Speed, Skew, TestabilityDocument10 pagesLayout Synthesis Benchmarks Focus on Speed, Skew, TestabilityVishakh BharadwajPas encore d'évaluation

- VLSIGURU DFT TRAINING SCAN INSERTION LABDocument2 pagesVLSIGURU DFT TRAINING SCAN INSERTION LABsenthilkumarPas encore d'évaluation

- Hierarchical Scan and Atpg For Two Stage PDFDocument3 pagesHierarchical Scan and Atpg For Two Stage PDFNeusilica school of VLSIPas encore d'évaluation

- EdtDocument10 pagesEdtjagruthimsPas encore d'évaluation

- 5 Simulation VCSDocument54 pages5 Simulation VCSThi NguyenPas encore d'évaluation

- LBIST - A Technique For Infield SafetyDocument4 pagesLBIST - A Technique For Infield Safetyrahul1990bhatiaPas encore d'évaluation

- On Chip Clock Controller For At-Speed TestingDocument4 pagesOn Chip Clock Controller For At-Speed TestingSachin*123Pas encore d'évaluation

- VLSIGURU DFT TRAINING SCAN INSERTION LABDocument2 pagesVLSIGURU DFT TRAINING SCAN INSERTION LABsenthilkumarPas encore d'évaluation

- Vlsiguru DFT Training Edt Insertion Lab ObservationsDocument12 pagesVlsiguru DFT Training Edt Insertion Lab ObservationssenthilkumarPas encore d'évaluation

- Lab1 DC Tmax 2012 1217 v1Document43 pagesLab1 DC Tmax 2012 1217 v1jasonturfPas encore d'évaluation

- Case12d ObservationDocument3 pagesCase12d ObservationsenthilkumarPas encore d'évaluation

- IDDQ TestingDocument38 pagesIDDQ TestingVeeranjaneyulu DhikondaPas encore d'évaluation

- Scan ChainsDocument3 pagesScan Chainsnehasoni100% (1)

- Enhanced Timing Closure Using LatchesDocument6 pagesEnhanced Timing Closure Using LatchesMelody ShieldsPas encore d'évaluation

- Mentorpaper 27753Document8 pagesMentorpaper 27753Sunil VermaPas encore d'évaluation

- Paper-Loc and LosDocument5 pagesPaper-Loc and LosRUPIREDDY PRAVEENPas encore d'évaluation

- IJTAG Tutorial FINAL Circuitnet PDFDocument9 pagesIJTAG Tutorial FINAL Circuitnet PDFSairam Prasad MarataPas encore d'évaluation

- Synthesis Netlist - Library Model - Dofile CommandsDocument30 pagesSynthesis Netlist - Library Model - Dofile CommandsPrafulani GajbhiyePas encore d'évaluation

- Assignment 1Document3 pagesAssignment 1dheeraj.d JainPas encore d'évaluation

- Stuck at FaultDocument6 pagesStuck at Faultamy2chang_1Pas encore d'évaluation

- 1 LOS and LOC in Vlsi Conference-ProceedingDocument9 pages1 LOS and LOC in Vlsi Conference-Proceedingbharghav saiPas encore d'évaluation

- Design For TestDocument4 pagesDesign For TestDivya PatelPas encore d'évaluation

- MbistDocument38 pagesMbistNaga NitheshPas encore d'évaluation

- Timing Paths: Timing Analysis Is Performed by Splitting The Design Into Different Paths Based OnDocument3 pagesTiming Paths: Timing Analysis Is Performed by Splitting The Design Into Different Paths Based OnNandaPas encore d'évaluation

- SCAN Test: Each Portion of Integrated Circuit Is Tested Using ATPG Technique To Detect IntraDocument3 pagesSCAN Test: Each Portion of Integrated Circuit Is Tested Using ATPG Technique To Detect Intrahumtum_shri5736Pas encore d'évaluation

- ATPG IMP QuestionsDocument1 pageATPG IMP QuestionsMayur MestryPas encore d'évaluation

- Dftadvisor TutorialDocument36 pagesDftadvisor TutorialSrikiran DevarabhotlaPas encore d'évaluation

- Lab4 Testing DFTDocument6 pagesLab4 Testing DFTDeepuPas encore d'évaluation

- SmartScan CompressionDocument5 pagesSmartScan CompressionAlexPas encore d'évaluation

- Sample Vlsi ResumeDocument2 pagesSample Vlsi ResumePavan KumarPas encore d'évaluation

- Modus Test Solution TBDocument4 pagesModus Test Solution TBbharath.chokkamPas encore d'évaluation

- Macro ImpDocument8 pagesMacro Impmechbull11Pas encore d'évaluation

- Dvba PGDocument97 pagesDvba PGYasser E KasanPas encore d'évaluation

- 2006 AprilDocument141 pages2006 Aprilmechbull11Pas encore d'évaluation

- IEEE WorkShop Slides LavretskyDocument185 pagesIEEE WorkShop Slides Lavretskymechbull11Pas encore d'évaluation

- Write To CSV File From CDocument1 pageWrite To CSV File From Cmechbull11Pas encore d'évaluation

- IC FabricationDocument9 pagesIC FabricationkranemetalPas encore d'évaluation

- Keys and Couplings: Types, Forces, StrengthDocument20 pagesKeys and Couplings: Types, Forces, Strengthyogwani79Pas encore d'évaluation

- Nano Generators: Presented By: Devdas Malekar (112110004)Document12 pagesNano Generators: Presented By: Devdas Malekar (112110004)mechbull11Pas encore d'évaluation

- A Project Report On Seminar On NanogeneratorsDocument2 pagesA Project Report On Seminar On Nanogeneratorsmechbull11Pas encore d'évaluation

- CastingDocument9 pagesCastingmechbull11Pas encore d'évaluation

- Sheetmetal TutorialDocument5 pagesSheetmetal TutorialramtcePas encore d'évaluation

- Re Engineering Case StudyDocument7 pagesRe Engineering Case Studymechbull11Pas encore d'évaluation

- June 09Document1 pageJune 09mechbull11Pas encore d'évaluation

- Stuttering TherapyDocument154 pagesStuttering Therapymechbull11100% (1)

- Hi 3110 - V Rev KDocument54 pagesHi 3110 - V Rev KÁlvaro Eduardo López LimaPas encore d'évaluation

- Msi A320m Pro m2 DatasheetDocument1 pageMsi A320m Pro m2 DatasheetDaniel SuarezPas encore d'évaluation

- Roll area size parameter specifies bytes for user context memory allocationDocument3 pagesRoll area size parameter specifies bytes for user context memory allocationgautampoddarPas encore d'évaluation

- Gb/Datatransfer and Camlink Explorer: PC Requirements Minimum PreferredDocument1 pageGb/Datatransfer and Camlink Explorer: PC Requirements Minimum Preferrednnn765Pas encore d'évaluation

- Conceptronic CMED3PLUS QuickstartDocument17 pagesConceptronic CMED3PLUS QuickstartJohn WaltersPas encore d'évaluation

- DDJ-RR Update Manual e PDFDocument8 pagesDDJ-RR Update Manual e PDFgusycaroPas encore d'évaluation

- 2004 - Airbus - A380 - An Afdx Based Flight Test Computer - Autest.2004.1436931 PDFDocument4 pages2004 - Airbus - A380 - An Afdx Based Flight Test Computer - Autest.2004.1436931 PDFHakan SolmazPas encore d'évaluation

- 15 056 UniWest Data EV1Document2 pages15 056 UniWest Data EV1TYO WIBOWOPas encore d'évaluation

- Eaton 9130 DSP Firmware Upgrade Guide 2.543Document11 pagesEaton 9130 DSP Firmware Upgrade Guide 2.543AlejandroPas encore d'évaluation

- File Organization (IS 211) : Dr. Howida YoussryDocument15 pagesFile Organization (IS 211) : Dr. Howida YoussryEslam Sayed GalalPas encore d'évaluation

- 4-CH AHD DVR with 2TB StorageDocument3 pages4-CH AHD DVR with 2TB StorageAmine Slimani100% (1)

- Refurbished Macs and Accessories for SaleDocument4 pagesRefurbished Macs and Accessories for SaleGyárfás AttilaPas encore d'évaluation

- ASUS X570 Full SpecsDocument1 pageASUS X570 Full SpecsFadlurrahman UmarPas encore d'évaluation

- ENG20009 Project S2 2023Document8 pagesENG20009 Project S2 2023sade wadePas encore d'évaluation

- ProDisplay P223Document4 pagesProDisplay P223peterzPas encore d'évaluation

- Esquematico 620cd B465 Bm5016Document54 pagesEsquematico 620cd B465 Bm5016Daniel ValerianoPas encore d'évaluation

- Specification of PCB800099 Controller Board V1.0Document10 pagesSpecification of PCB800099 Controller Board V1.0benabdullahPas encore d'évaluation

- Autolab Application Note AUT01Document2 pagesAutolab Application Note AUT01onePas encore d'évaluation

- DDR3 Device Operation Timing DiagramDocument154 pagesDDR3 Device Operation Timing DiagramPavani AchyuthaPas encore d'évaluation

- Everex Stepnote Va Series User ManualDocument140 pagesEverex Stepnote Va Series User ManualmrjqPas encore d'évaluation

- Date: 18/2/2013: Mainboard Chipset FSB RAM VGA VSL OT RM Processor (Box With Fan) Internal Hard DriveDocument2 pagesDate: 18/2/2013: Mainboard Chipset FSB RAM VGA VSL OT RM Processor (Box With Fan) Internal Hard DriveAlan AccreatiaPas encore d'évaluation

- Docu8299 RecoverPoint Deploying With AIX Hosts Technical NotesDocument28 pagesDocu8299 RecoverPoint Deploying With AIX Hosts Technical Notesw00kkkPas encore d'évaluation

- Quickspecs: HP Z2 G9 Tower Workstation Desktop PCDocument57 pagesQuickspecs: HP Z2 G9 Tower Workstation Desktop PCAlaa GhPas encore d'évaluation

- 3 ARM ExceptionsDocument26 pages3 ARM ExceptionsSaket JainPas encore d'évaluation

- TMS 320 ArchitectureDocument45 pagesTMS 320 Architectureprakash subramanianPas encore d'évaluation

- Abhishek ResumeDocument3 pagesAbhishek Resumesantosh_maniPas encore d'évaluation

- Basic Unit of Computer SystemDocument21 pagesBasic Unit of Computer SystemGemex4fsh100% (3)

- WIFI Kit 32Document1 pageWIFI Kit 32lucaPas encore d'évaluation

- Microprocessor PDFDocument3 pagesMicroprocessor PDFmkrajasekarPas encore d'évaluation