Académique Documents

Professionnel Documents

Culture Documents

Sistema Minimo Micro 8088

Transféré par

miguelon04Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

Sistema Minimo Micro 8088

Transféré par

miguelon04Droits d'auteur :

Formats disponibles

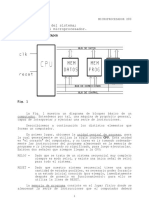

DESCRIPCION DE LOS COMPONENTES DEL SISTEMA MINIMO DEL MICROPROCESADOR INTEL 8088, EN UNA PLACA PRINCIPAL DE UN COMPUTADOR PERSONAL

XT CONCEPTOS GENERALES Antes de empezar con la descripcin del funcionamiento de una PC basada en el microprocesador 8088, es necesario conocer primero ciertos trminos que se usarn a lo largo de este trabajo: MICROPROCESADOR: Pastilla de silicio integrada que cumple rdenes segn las instrucciones que se le ingrese. Un microprocesador esta gobernado por un reloj maestro que controla el flujo de las operaciones internas de ste. El microprocesador no posee ningn perifrico integrado (Timers, memoria, etc). Un microprocesador posee registros que son operados por las instrucciones que se den al microprocesador y que pueden poseer los datos o resultados de la operacin que se realiza. Posee usualmente tres tipos de buses: Datos, Control y Direcciones BUS DE DATOS: Conjunto de pines o vas de datos (bus) que juntos transfieren informacin (datos) de y hacia el microprocesador. BUS DE DIRECCIONES: Bus que contiene la direccin de memoria o del dispositivo al que se desea acceder. BUS DE CONTROL: Encargado de controlar las operaciones entre el Microprocesador y sus perifricos. Controla lecturas, escrituras y retardos del mismo. MEMORIA RAM: Memoria de acceso aleatorio. Memoria leble y escribible en cualquier momento. Normalmente aqu se almacena la informacin y los programas de usuario que se ejecutan en el microprocesador. MEMORIA ROM: Memoria de slo lectura. Esta memoria slo se puede leer en el microprocesador. Contiene las rutinas BIOS del fabricante, que controlan a bajo nivel los perifricos del microprocesador. Esta memoria es a primera que se lee al momento de encender el computador. CANAL DMA: Canal de Acceso directo a memoria. Son un conjunto de lneas que permiten el acceso directo a la memoria del sistema, sin pasar por el microprocesador, evitndole trabajo extra. Usualmente los dispositivos que usan canales DMA, necesitan acceder a una gran cantidad de datos de un solo golpe, por ejemplo las tarjetas de sonido y dispositivos de almacenamiento. IRQ: Peticin de Interrupcin por parte de un perifrico, a la que el microprocesador responde interrumpiendo lo que estaba haciendo y luego ejecutando el servicio de interrupcin correspondiente al nmero de interrupcin, retomando su anterior trabajo al finalizar la rutina. Las interrupciones permiten que el microprocesador ejecute varias tareas a la vez. CIRCUITO DE BSCULA CERROJO: Se refiere al circuito integrado 74LS373, que es un circuito integrado que permite la multiplexacin del bus de direcciones junto con el bus datos en el microprocesador. RD, WR: Corresponden a las lneas de control del microprocesador cuando ste realiza alguna operacin con un dispositivo externo (Memorias, etc.). La lnea RD se activa (nivel activo 0), cuando el microprocesador desea leer algn dato de una direccin; y la lnea WR (Nivel activo 0), se activa cuando el microprocesador desea escribir en una direccin dada.

3.

EL MICROPROCESADOR 8088

Corresponde al primer microprocesador de Intel de 8 bits (8 bits de datos + 20 de direccin), lo que nos da un espacio de direccionamiento de 220=1048576 bytes, o lo que es lo mismo, hasta un 1MB de memoria. Este microprocesador posee 18 registros, agrupados de la siguiente manera: AX (AH AL): BX (BH BL): CX (CH CL): DX (DH DL): DI: Acumulador Base Cuenta Datos ndice Destino

1 Up & Uc

SI: SS: SP: CS: IP: BP: ES: DS: Flags

ndice Origen Segmento de pila Puntero de pila Segmento de cdigo Puntero de instruccin Puntero base Segmento extra Segmento de datos

El direccionamiento que usa este microprocesador se basa en la forma Segmento:Desplazamiento. Cada segmento tiene una longitud de 216 bytes (64KB). Los desplazamientos corresponden a las direcciones entre segmento y segmento. La direccin fsica real a la que accede el microprocesador se puede calcular por [Segmento] x 10h + [Desplazamiento]. FUNCIONAMIENTO DEL MICROPROCESADOR Al ser inicializado el microprocesador, lo primero que hace es generar la direccin de memoria 0000h, para el ROM BIOS. Luego activa el pin ALE, para que el los bits bajos de la direccin (AD0-AD7) queden almacenados en el circuito de Bscula Cerrojo. Luego de ello, activa el pin RD, con lo que recibe el dato correspondiente al cdigo de operacin de la primera instruccin almacenada el ROM BIOS a travs de sus lneas de datos (con ello se explica la necesidad del circuito bscula cerrojo). Una vez recibido este primer dato, el microprocesador busca en su tabla de cdigos, a qu operacin se refiere y segn ello, puede generar una nueva direccin al siguiente dato para completar su operacin. Este ciclo se repite siempre, la variacin puede estar en que el perifrico direccionado, puede ser ROM, RAM o un perifrico. En caso que el microprocesador desee escribir en la memoria, se genera primero la direccin, como en el caso anterior, slo que esta vez se ponen los datos en el bus de datos y luego se activa el pin WR. Adicionalmente, posee en su configuracin unos pines llamados NMI, INTA, INT, HOLD y HLDA que controlan procesos que veremos ms adelante. 4. GENERADOR DE RELOJ 8284

Es el encargado de generar las seales de reloj necesarias para sincronizar las operaciones del CPU junto con los dems dispositivos. Este circuito integrado, posee en su configuracin un cristal de 14.3MHz que permite la operacin del CPU a 4.77MHz aproximadamente. Esto nos da un periodo de 210ns Adicionalmente, posee en su configuracin el control de los pines de Reset y Ready, que controlan el hacer un Reset al microprocesador y la disponibilidad del mismo, respectivamente. Adicionalmente posee una salida OSC que es un reloj de la misma frecuencia que la del cristal y se dirige a los slots de expansin para controlar algn proceso externo. 5. CONTROLADOR PROGRAMABLE DE INTERRUPCIONES 8259

Este circuito integrado controla las interrupciones del sistema. Como el microprocesador slo posee dos entradas de interrupcin, y puede controlar muchas ms, es necesario algn integrado que no permita ello. El 8259 cumple este propsito.

2 Up & Uc

IRQ IRQ0 IRQ1 IRQ2 IRQ3 IRQ4 IRQ5 IRQ6 IRQ7

FUNCION Reloj en tiempo real Teclado PC-Net Puerto serie secundario Puerto serie primario Disco duro Diskette Impresora

El 8259 posee cuatro palabras de control que se encargan de configurar al integrado para que funcione correctamente. En la primera palabra de estado (ICW1), se configura el modo del 8259 (es decir para que trabaje junto con otro ms y ampliar las interrupciones), el modo de disparo de las interrupciones (Nivel o flanco descendente) y parte de los vectores de interrupcin. En la segunda palabra de estado (ICW2), se configuran los vectores de interrupcin. La tercera palabra funciona cuando el 8259 trabaja en modo mltiple con otros ms. Aqu se configura el modo maestro/esclavo. 6. CONTROLADOR PROGRAMABLE DE PERIFERICOS 8255

Circuito Integrado que permite la comunicacin del CPU con perifricos externos a travs de la implementacin de tres puertos E/S independientes y programables. En una PC/XT, el 8255 permite el control del teclado, del speaker y parte de IRQ1 (ver diagrama de bloques anteriormente descrito). El 8255, se configura a travs de una byte de control ubicado en la direccin base del PPI + 3h, en este byte, se configuran los modos y el tipo de puerto a usar, para cada uno de los tres que posee el PPI. La palabra de estado del 8255 es la siguiente: D7 1 D6 MODO D5 MODO D4 PA D3 PC7-PC4 D2 MODO D1 PB D0 PC3-PC0

Los bits D6 y D5 controlan el modo de transferencia de datos de PA y PC7-PC4; el bit D2 indica el modo de los puertos PB y PC3-PC0. Los dems bits indican cmo funcionarn los puertos (1=entrada, 0=salida).

7.

CONTROLADOR DE ACCESO DIRECTO A MEMORIA 8237

Este circuito integrado permite arbitrar el uso de los canales DMA del sistema, en total de cuatro. El 8237 funciona en conjunto con dos integrados 74LS670 y 74LS373 que permiten que el dispositivo genere sus propias direcciones de memoria, de manera similar a un microprocesador. Ello permite el acceso a la memoria por parte del dispositivo sin necesidad del microprocesador, evitndole trabajo. El funcionamiento del 8237 es como sigue: El dispositivo que desea el acceso directo a memoria enva una seal DRQn, con n como el nmero de canal (0-3).

3 Up & Uc

Si el canal DMA est disponible, el controlador DMA enva una seal al pin HOLD del 8088. ste indicar su aceptacin devolviendo una seal HLDA, que se mantendr durante el proceso DMA. Una vez que sucede esto, el Controlador DMA devuelve una seal DACKn, que indica que el CPU ha aceptado la peticin DMA y se encuentra listo para operar en la memoria. Se enva tambin una seal AEN que es la habilitacin del bus de datos y el de direcciones para el dispositivo que hizo la peticin. El dispositivo realiza las operaciones pertinentes sobre la memoria y al finalizar desactiva la seal DRQn y el sistema regresa a su estado original. Hay que tener en cuenta que cuando se realiza un acceso DMA, el controlador no aceptar otras peticiones adicionales. Hay que tomar en cuenta tambin que el acceso DMA no acceda a posiciones que no le sean permitidas. Esto es responsabilidad del programador.

8.

CONTROLADOR DE INTERVALOS 8253

Es un integrado que posee en su interior tres contadores/temporizadores programables independientes descendentes. En el sistema PC/XT, el temporizador 0, produce IRQ0, el temporizador 1, controla el primer canal DMA y el temporizador 2, controla las frecuencias producidas en el speaker. El 8253, posee cuatro registros que controlan el funcionamiento de cada uno de los temporizadores/contadores. Los tres primeros corresponden a los datos a cargar en los tres contadores/temporizadores. El cuarto configura los modos de funcionamiento de los contadores/temporizadores. 9. CO-PROCESADOR MATEMATICO 8087

Funciona como un microprocesador controlador por el 8088, slo que ste est especializado en operaciones de coma flotante, agilizando los clculos matemticos realizados por programas que hagan uso de este procesador. 10. ROM BIOS 2764 Es un chip de memoria EPROM (Memoria Borrable y Programable de Solo Lectura). Su capacidad es de 64KB y en la PC/XT, hay 6 integrados de este tipo, sumando un total de 384KB. Aqu est almacenado el cdigo correspondiente al ROM BIOS, que es donde se almacenan las rutinas de bajo nivel que controlan los perifricos, ah es donde se almacenan inicialmente los servicios de interrupcin, las palabras de configuracin de los perifricos del 8088, el soporte de ROM BASIC y las rutinas de autodiagnstico que se ejecutan al momento de encender el computador. El 2764, se puede borrar aplicando luz ultravioleta sobre la ventana de borrado, que es una cubierta transparente que cubre al ncleo del chip. El proceso de borrado toma entre 5 y 15 minutos, dependiendo de la potencia y de la longitud de onda de la luz utilizada. Tambin es posible el borrado exponiendo el integrado a la luz solar. Este proceso es ms lento (1 semana en algunos casos) pero tambin posible. En los ROM BIOS modernos, se usan memorias EEPROM, que permiten la actualizacin fcil del cdigo del BIOS debido a que estas memorias se pueden borrar con voltaje (12 18V) y se programan con ese mismo voltaje. 11. RAM 4164 La RAM del XT, es del tipo dinmico, es decir esta RAM est hecha de condensadores y debe ser refrescado su contenido peridicamente sino los datos se perderan, esto se refleja en su baja velocidad respecto a otros tipos de RAM (SRAM). El acceso a la RAM se da a travs de decodificadores de direccin alta (74158), que se encargan de seleccionar al chip correcto que trabajan en conjunto con sendos decodificadores 74LS138 para la seleccin de filas y columnas y ejecucin de ciclos RAS y CAS. Los bytes ms bajos se obtienen directamente del bus externo. Adicionalmente a esto, existe un generador de paridad par que genera un noveno bit en la DRAM para salvaguardar la integridad de los datos.

4 Up & Uc

Vous aimerez peut-être aussi

- Prácticas de redes de datos e industrialesD'EverandPrácticas de redes de datos e industrialesÉvaluation : 4 sur 5 étoiles4/5 (5)

- Infografia El Computador.Document1 pageInfografia El Computador.Amanda Ruiz50% (2)

- UF0852 - Instalación y actualización de sistemas operativosD'EverandUF0852 - Instalación y actualización de sistemas operativosÉvaluation : 5 sur 5 étoiles5/5 (1)

- Computadores para bases de datos. IFCT0310D'EverandComputadores para bases de datos. IFCT0310Pas encore d'évaluation

- Programación de microcontroladores paso a paso: Ejemplos prácticos desarrollados en la nubeD'EverandProgramación de microcontroladores paso a paso: Ejemplos prácticos desarrollados en la nubePas encore d'évaluation

- Las Puertas Dimensionales en El EspacioTiempo PARTE IDocument28 pagesLas Puertas Dimensionales en El EspacioTiempo PARTE IComunidad Pagana de MéxicoPas encore d'évaluation

- Arquitectura interna del microprocesador Z80Document85 pagesArquitectura interna del microprocesador Z80Victor Hugo Hernandez100% (1)

- MicroprocesadorDocument6 pagesMicroprocesadorJOSUE Home100% (1)

- Introducción Al Psoc5Lp: Teoría y aplicaciones prácticaD'EverandIntroducción Al Psoc5Lp: Teoría y aplicaciones prácticaPas encore d'évaluation

- FCN-1-40 en EsDocument40 pagesFCN-1-40 en EsMario Rojas Jimenez100% (1)

- EMS InformaticaDocument9 pagesEMS InformaticaJosue PazPas encore d'évaluation

- El Microprocesador 8085Document11 pagesEl Microprocesador 8085neptuno97Pas encore d'évaluation

- Tarea1 Investigacion MicrocontroladoresDocument19 pagesTarea1 Investigacion MicrocontroladoresGIOVANIPas encore d'évaluation

- Informe DescriptivoDocument13 pagesInforme Descriptivowilson moyaPas encore d'évaluation

- PC XT 8086Document31 pagesPC XT 8086Adrian OdrielPas encore d'évaluation

- Unidad IDocument10 pagesUnidad IJose Manuel Godoy EscribarPas encore d'évaluation

- Microprocesador, Memoria RAM y Disco Duro, Requerimientos Básicos de Los Sistemas Operativos.Document18 pagesMicroprocesador, Memoria RAM y Disco Duro, Requerimientos Básicos de Los Sistemas Operativos.Yajaira Soledad Chipantiza FreirePas encore d'évaluation

- temasDocument24 pagestemasGerardo CruzPas encore d'évaluation

- Componentes Del MicroprocesadorDocument25 pagesComponentes Del Microprocesadorel_cuate1883% (6)

- Chip PropellerDocument5 pagesChip PropellerTimothy AdamsPas encore d'évaluation

- Introducción a los microprocesadoresDocument22 pagesIntroducción a los microprocesadoresAlexis Rafael Narvaez MendozaPas encore d'évaluation

- Unidad Central de ProcesamientoDocument18 pagesUnidad Central de ProcesamientoJaime Hernnadez LopezPas encore d'évaluation

- Operaciones Basicas Del Microprocesaror 1Document22 pagesOperaciones Basicas Del Microprocesaror 1jesusPas encore d'évaluation

- Arquitectura Del Microprocesador Intel 8086/8088Document24 pagesArquitectura Del Microprocesador Intel 8086/8088Jairo AntonPas encore d'évaluation

- Diseño de Microcomputadores1Document5 pagesDiseño de Microcomputadores1Carlos VenegasPas encore d'évaluation

- Z80 microprocesador arquitecturaDocument85 pagesZ80 microprocesador arquitecturaSebastián SandovalPas encore d'évaluation

- Material de Apoyo (Información Del Taller)Document20 pagesMaterial de Apoyo (Información Del Taller)Jose Guillermo AcostaPas encore d'évaluation

- Micro Proce Sad orDocument82 pagesMicro Proce Sad orOscar Duque SuarezPas encore d'évaluation

- Unidad 2 ArquitecturaDocument8 pagesUnidad 2 ArquitecturaStroker CasablancasPas encore d'évaluation

- Diseño Lógico de Procesadores y su OrganizaciónDocument7 pagesDiseño Lógico de Procesadores y su OrganizaciónOmer100% (2)

- Arquitectura Del Microprocesador 80286Document20 pagesArquitectura Del Microprocesador 80286Richard vega marcelo100% (1)

- Vdocuments - MX Operacion de Micros e InterfacesDocument29 pagesVdocuments - MX Operacion de Micros e Interfacesmario floresPas encore d'évaluation

- La Unidad de ControlDocument4 pagesLa Unidad de ControlBryan MosqueraPas encore d'évaluation

- Mantenimiento equipos cómputoDocument7 pagesMantenimiento equipos cómputoHernando Rodríguez QuinteroPas encore d'évaluation

- Analisis de La Arquitectura Interna Del Pic16f887Document12 pagesAnalisis de La Arquitectura Interna Del Pic16f887jared porfirioPas encore d'évaluation

- Exposicion MicrocontroladoresDocument33 pagesExposicion MicrocontroladoresRosita Mtz SPas encore d'évaluation

- Partes Que Integran Un ProcesadorDocument7 pagesPartes Que Integran Un ProcesadoryareliiiiPas encore d'évaluation

- APUNTE PARCIAL 1 Final Sistemas DigitalesDocument21 pagesAPUNTE PARCIAL 1 Final Sistemas DigitalesRodrigo LopezPas encore d'évaluation

- Semana 2-Arquitectura Del MicroprocesadorDocument25 pagesSemana 2-Arquitectura Del MicroprocesadorDaniel MalpartidaPas encore d'évaluation

- R. A. 1.1 Componentes Del MicroprocesadorDocument29 pagesR. A. 1.1 Componentes Del MicroprocesadorJOSE GILBERTO CANO GREENEPas encore d'évaluation

- MICROPROCESADORESDocument24 pagesMICROPROCESADORESRaul TamezPas encore d'évaluation

- TAREA 1pdfDocument11 pagesTAREA 1pdfjavierPas encore d'évaluation

- Ejercicios HardwareDocument6 pagesEjercicios HardwarenandoPas encore d'évaluation

- Presentación - MICROCHIPSDocument16 pagesPresentación - MICROCHIPSEmmanuel AburtoPas encore d'évaluation

- Capitulo 2 Entradas y SalidasDocument22 pagesCapitulo 2 Entradas y SalidasMauricio Cortes CuamatziPas encore d'évaluation

- CgrwyDocument17 pagesCgrwyKevin SosaPas encore d'évaluation

- UntitledDocument8 pagesUntitledAlexander Marcos ChacaliazaPas encore d'évaluation

- Microcontroladores HC08 de Freescale - Guía de introducción deDocument22 pagesMicrocontroladores HC08 de Freescale - Guía de introducción dekkkkkkkkkkkkPas encore d'évaluation

- 1 Parcial de Microprocesadores VirtualDocument4 pages1 Parcial de Microprocesadores VirtualjuanitoPas encore d'évaluation

- Sistema de buses en computadorasDocument42 pagesSistema de buses en computadorasluisoswal91Pas encore d'évaluation

- Introduccion A Microprocesador y A ComputadoraDocument62 pagesIntroduccion A Microprocesador y A ComputadoraYAJAIRA EVELIN HOLGUIN GUTIERREZPas encore d'évaluation

- Chipset Ensamble ComponentesDocument16 pagesChipset Ensamble ComponentesFernando LópezPas encore d'évaluation

- Arquitectura Von Neumann y HarvardDocument26 pagesArquitectura Von Neumann y HarvardUlivari Alexander GomezPas encore d'évaluation

- Teoria MicroprocesadoresDocument12 pagesTeoria MicroprocesadoresJoshuan Salazar AlvaradoPas encore d'évaluation

- Arquitectura Del PLCDocument12 pagesArquitectura Del PLCSaid Jara100% (1)

- Procesador 8 BitsDocument12 pagesProcesador 8 BitsEnrique Galindo100% (1)

- R Circuito de Disparo Con MicrocontroladoresDocument15 pagesR Circuito de Disparo Con MicrocontroladoresIsidro HernandezPas encore d'évaluation

- Unidad 2Document24 pagesUnidad 2Rogelio Anguiano SantosPas encore d'évaluation

- Arquitectura de Un MicroprocesadorDocument4 pagesArquitectura de Un MicroprocesadorRolando NinaPas encore d'évaluation

- ArquiDocument24 pagesArquiangelmauriciormzPas encore d'évaluation

- Actividad 5Document9 pagesActividad 5juan mezaPas encore d'évaluation

- Comunicación Interna de La ComputadoDocument26 pagesComunicación Interna de La ComputadoJoel RamirezPas encore d'évaluation

- El UP 8086 Fue de Los Primeros en Utilizar Un Bus de 16Document4 pagesEl UP 8086 Fue de Los Primeros en Utilizar Un Bus de 16Annie UniPas encore d'évaluation

- Areli Bravo - Actividad 1Document19 pagesAreli Bravo - Actividad 1Juari RamosPas encore d'évaluation

- Catalogo 10-10-2021Document37 pagesCatalogo 10-10-2021Jose OteroPas encore d'évaluation

- Clase FSM Maquinas AlgoritmicasDocument12 pagesClase FSM Maquinas Algoritmicasjornada660Pas encore d'évaluation

- Ud3 FHWDocument22 pagesUd3 FHWHebePas encore d'évaluation

- Explicar Métodos de Conversión y Los Registros de Un Procesador 8086Document10 pagesExplicar Métodos de Conversión y Los Registros de Un Procesador 8086Sanchez Bernabe75% (4)

- Resumen S.O Memoria VirtualDocument5 pagesResumen S.O Memoria VirtualTomás Sierra VallePas encore d'évaluation

- Resumen Desktop LaptopDocument5 pagesResumen Desktop LaptopEdge123123Pas encore d'évaluation

- Tipos de Memoria RAMDocument3 pagesTipos de Memoria RAMLuciano CsekePas encore d'évaluation

- Semana 02 Arquitectura de ComputadorasDocument30 pagesSemana 02 Arquitectura de ComputadorasMarcoPzPas encore d'évaluation

- Auditoria de SistemasDocument28 pagesAuditoria de SistemasJOSE DAVID DURANPas encore d'évaluation

- Ensayo Tecnico Arquitectura Del Ordenador Junior213Document14 pagesEnsayo Tecnico Arquitectura Del Ordenador Junior213Mr. WolfPas encore d'évaluation

- Actividad de Aprendizaje #1 - Arquitectura de ComputadoresDocument8 pagesActividad de Aprendizaje #1 - Arquitectura de Computadoresestampas12Pas encore d'évaluation

- Todo El Material UnificadoDocument12 pagesTodo El Material UnificadoJL AlarconPas encore d'évaluation

- Símbolos de Diagramas de FlujoDocument6 pagesSímbolos de Diagramas de FlujoJossy MoralesPas encore d'évaluation

- Control y Recuperación de ConcurrenciaDocument18 pagesControl y Recuperación de ConcurrenciaRenan PMPas encore d'évaluation

- Memoria RamDocument12 pagesMemoria RamGabriel QuiroaPas encore d'évaluation

- Configuración red PPI maestro-esclavoDocument15 pagesConfiguración red PPI maestro-esclavoMartinBancheroPas encore d'évaluation

- Flytech PDFDocument40 pagesFlytech PDFRaul Lopez CruzPas encore d'évaluation

- IyCnet Hardware Modicon M340-MinDocument65 pagesIyCnet Hardware Modicon M340-Minsergio toledoPas encore d'évaluation

- Los Sistemas de Archivos o FicherosDocument5 pagesLos Sistemas de Archivos o FicherosDuanes Erick100% (1)

- Operacion y Programacion de Sistemas de Control Con PLCDocument84 pagesOperacion y Programacion de Sistemas de Control Con PLCCrist VillarPas encore d'évaluation

- Configurar FTPDocument2 pagesConfigurar FTPmirkitoPas encore d'évaluation

- Taller de La Memoria RAMDocument7 pagesTaller de La Memoria RAMJuan Sebastian Parrado Romero100% (3)

- Actividad 2 Sistemas OperativosDocument8 pagesActividad 2 Sistemas OperativosAngel Alejandro JassoPas encore d'évaluation

- Catalogo Estacion Total CHC CTS 112R4 EsDocument2 pagesCatalogo Estacion Total CHC CTS 112R4 EsingridnaPas encore d'évaluation

- Almacenamiento y Medios FísicosDocument12 pagesAlmacenamiento y Medios FísicosCarlos LariosPas encore d'évaluation

- TCC Evidencias DigitalesDocument14 pagesTCC Evidencias Digitaleserik martinezPas encore d'évaluation