Académique Documents

Professionnel Documents

Culture Documents

Fpga A2 2004

Transféré par

Cayo B. LealTitre original

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

Fpga A2 2004

Transféré par

Cayo B. LealDroits d'auteur :

Formats disponibles

Indice Laboratorio de Dise o Microelectrnico, 4o Curso, P94 n o

1. Introduccin o 1.1. Evolucin de los dispositivos programables . . . . . . . . . . . . . . . . . . . . . . o 1.2. Estructura general de las FPGAs . . . . . . . . . . . . . . . . . . . . . . . . . . . 2. Arquitectura de las FPGA de Xilinx 2.1. Tecnolog de programacin . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . a o 2.2. Descripcin de las principales familias . . . . . . . . . . . . . . . . . . . . . . . . o 2.3. Arquitectura de la familia XC2000 . . . . . . . . . . . . . . . . . . . . . . . . . . 3. 1 1 2 4 4 5 6

FPGA: Nociones bsicas e a implementacin o

M. L. Lpez Vallejo y J. L. Ayala Rodrigo o

Especicaciones

3.1. Estructura . . . . . . . . . . . . . . . . . . . 3.2. Bloques lgicos . . . . . . . . . . . . . . . . o 3.3. Descripcin detallada de la LUT . . . . . . o 3.3.1. Implementacin de memorias CMOS o 3.4. Recursos de interconexin . . . . . . . . . . o 3.5. Circuito de control de programacin . . . . o . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7

8 8 9 10 11 12 12

Referencias

Abril 2004

LDIM

Proyecto nal 2003-2004

LDIM

Proyecto nal 2003-2004

1.

Introduccin o

Cuando se aborda el dise o de un sistema electrnico y surge la necesidad de implementar n o una parte con hardware dedicado son varias las posibilidades que hay. En la gura 1 se han representado las principales aproximaciones ordenndolas en funcin de los parmetros coste, a o a exibilidad, prestaciones y complejidad. Como se puede ver, las mejores prestaciones las proporciona un dise o full-custom, consiguindose a costa de elevados costes y enorme complejidad de n e dise o. En el otro extremo del abanico de posibilidades se encuentra la implementacin software, n o que es muy barata y exible, pero que en determinados casos no es vlida para alcanzar un nivel a de prestaciones relativamente alto.

Programa software

utilizando las l neas de direcciones como entradas y las de datos como salidas (implementa una tabla de verdad). Hay dos tipos bsicos de PROM: a 1. 2. Programables por mscara (en la fbrica), proporcionan mejores prestaciones. Son las a a denominadas de conexiones hardwired. Programables en el campo (eld) por en usuario nal. Son las EPROM y EEPROM. Proporcionan peores prestaciones, pero son menos costosas para vol menes peque os de u n produccin y se pueden programar de manera inmediata. o

Flexibilidad

Lgica programable: MPGAs FPGAs

Complejidad Coste Prestaciones

El PLD, Programmable Logic Device, es una matriz de puertas AND conectada a otra matriz de puertas OR ms biestables. Cualquier circuito lgico se puede implementar, por tanto, como a o suma de productos. La versin ms bsica del mismo es una PAL, con un plano de puertas AND o a a y otro jo de puertas OR. Las salidas de estas ultimas se pueden pasar por un biestable en la mayor de los circuitos del mercado. a Ventaja: son bastante ecientes si implementan circuitos no superiores a unos centenares de puertas. Inconvenientes: arquitectura r gida, y est limitado por un n mero jo de biestables y a u entradas/salidas. La PLA, Programmable Logic Array, es ms exible que la PAL: se pueden programar las a conexiones entre los dos planos. Estos dispositivos son muy simples y producen buenos resultados con funcionalidades sencillas (slo combinacional). Hace falta algo un poco ms sosticado y o a general: una matriz de elementos variados que se puedan interconectar libremente. Este es el caso de una MPGA (Mask-Programmable Gate Array), cuyo principal representante est constituido a por un conjunto de transistores ms circuiter de E/S. Se unen mediante pistas de metal que a a hay que trazar de forma optima, siendo sta la mscara que hay que enviar al fabricante. e a Las FPGA (Field Programmable Gate Array), introducidas por Xilinx en 1985, son el dispositivo programable por el usuario de ms general espectro. Tambin se denominan LCA a e (Logic Cell Array). Consisten en una matriz bidimensional de bloques congurables que se pueden conectar mediante recursos generales de interconexin. Estos recursos incluyen segmentos o de pista de diferentes longitudes, ms unos conmutadores programables para enlazar bloques a a pistas o pistas entre s En realidad, lo que se programa en una FPGA son los conmutadores . que sirven para realizar las conexiones entre los diferentes bloques, ms la conguracin de los a o bloques.

Clulas estndar

Full-custom

Figura 1: Diferentes soluciones para el diseo de circuitos digitales n

Entre estas dos opciones se puede elegir la fabricacin de un circuito electrnico realizado o o mediante dise o semi-custom, utilizando clulas estndar, o recurrir a un circuito ya fabricado n e a que se pueda programar in situ, como son las FPGAs. De estas dos opciones la primera proporciona mejores prestaciones, aunque es ms cara y exige un ciclo de dise o relativamente a n largo. Por otro lado, los dispositivos lgicos programables constituyen una buena oferta para o realizar dise os electrnicos digitales con un buen compromiso coste-prestaciones. Y lo que es n o mejor, permiten obtener una implementacin en un tiempo de dise o asombrosamente corto o n (con la consiguiente reduccin del parmetro clave: Time to market). o a Otro aspecto que se debe tener en cuenta para decidirse por este tipo de implementacin es o que el coste de realizacin es muy bajo, por lo que suele ser una buena opcin para la realizacin o o o de prototipos. En estas notas vamos a describir de forma muy somera en qu consisten estos dispositivos, e particularizando para una familia del fabricante Xilinx. La informacin contenida en ellas se o basa en gran medida en las siguientes fuentes: sobre arquitectura de FPGAs [BFRV92, Xil91, n CSR+ 99a]; sobre dise o de circuitos [WE94, CSR + 99b].

1.2.

Estructura general de las FPGAs

1.1.

Evolucin de los dispositivos programables o

El proceso de dise o de un circuito digital utilizando una matriz lgica programable puede n o descomponerse en dos etapas bsicas: a 1. 2. Dividir el circuito en bloques bsicos, asignndolos a los bloque congurables del disposia a tivo. Conectar los bloques de lgica mediante los conmutadores necesarios. o

Se entiende por dispositivo programable aquel circuito de propsito general que posee una o estructura interna que puede ser modicada por el usuario nal (o a peticin suya, por el fabrio cante) para implementar una amplia gama de aplicaciones. El primer dispositivo que cumpli eso tas caracter sticas era una memoria PROM, que puede realizar un comportamiento de circuito

LDIM

Proyecto nal 2003-2004

LDIM

Proyecto nal 2003-2004

Bloque Lgico

Clula E/S

Bloques Lgicos

Interconexin

Canal de Interconexin

Bloques Lgicos

MATRIZ SIMTRICA

Recursos de Interconexin

BASADA EN CANALES

Interconexiones sobre Bloques Lgicos

Bloques PDL

Interconexiones

Figura 2: Estructura general de una FPGA (en concreto de XILINX)

Para ello el fabricante proporciona las herramientas de dise o adecuadas. n Los elementos bsicos constituyentes de una FPGA como las de Xilinx se pueden ver en la a gura 2 y son los siguientes: 1. Bloques lgicos, cuya estructura y contenido se denomina arquitectura. Hay muchos tipos o de arquitecturas, que var principalmente en complejidad (desde una simple puerta hasta an mdulos ms complejos o estructuras tipo PLD). Suelen incluir biestables para facilitar la o a implementacin de circuitos secuenciales. Otros mdulos de importancia son los bloques o o de Entrada/Salida, Recursos de interconexin, cuya estructura y contenido se denomina arquitectura de rutao do. Memoria RAM, que se carga durante el RESET para congurar bloques y conectarlos.

PLD JERRQUICO MAR DE PUERTAS

Figura 3: Tipos de FPGAs

2. 3.

2.

2.1.

Arquitectura de las FPGA de Xilinx

Tecnolog de programacin a o

Entre las numerosas ventajas que proporciona el uso de FPGAs dos destacan principalmente: el bajo coste de prototipado y el corto tiempo de produccin. No todo son ventajas. Entre los o inconvenientes de su utilizacin estn su baja velocidad de operacin y baja densidad lgica (poca o a o o lgica implementable en un solo chip). Su baja velocidad se debe a los retardos introducidos por o los conmutadores y las largas pistas de conexin. o Por supuesto, no todas las FPGA son iguales. Dependiendo del fabricante nos podemos encontrar con diferentes soluciones. Las FPGAs que existen en la actualidad en el mercado se pueden clasicar como pertenecientes a cuatro grandes familias, dependiendo de la estructura que adoptan los bloques lgicos que tengan denidos. Las cuatro estructuras se pueden ver en o la gura 3, sin que aparezcan en la misma los bloques de entrada/salida. 1. 2. 3. 4. Matriz simtrica, como son las de XILINX e Basada en canales, ACTEL Mar de puertas, ORCA PLD jerrquica, ALTERA o CPLDs de XILINX. a

Antes de continuar con conocimientos ms avanzados acerca de FPGAs (de XILINX en cona creto), hay que aclarar cmo se realiza el proceso de programacin (ie., las conexiones necesarias o o entre bloques y pistas). En primer lugar, si se piensa que el n mero de dispositivos de conexin u o que hay en una FPGA es muy grande (t picamente superior a 100.000), es necesario que cumplan las siguientes propiedades: Ser lo ms peque os que posible. a n Tener la resistencia ON lo ms baja posible, mientras la OFF ha de ser lo ms alta posible a a (para que funcione como conmutador). Se deben poder incorporar al proceso de fabricacin de la FPGA. o El proceso de programacin no es unico, sino que se puede realizar mediante diferentes o tecnolog as, como son clulas RAM estticas, transistores EPROM y EEPROM, etc. En el e a caso de las FPGAs de XILINX los elementos de programacin se basan en clulas de memoria o e RAM que controlan transistores de paso, puertas de transmisin o multiplexores. En la gura 4 se o puede ver esquemticamente cmo son. Dependiendo del tipo de conexin requerida se elegir un a o o a modelo u otro.

En concreto, para explicar el funcionamiento y la estructura bsica de este tipo de dispositivos a programables slo se considerarn las distintas familias de XILINX. o a 3

LDIM

Proyecto nal 2003-2004

LDIM

Proyecto nal 2003-2004

Pistas

Clula SRAM

Clula SRAM

Clula SRAM

MUX

Salidas

Transistor de paso

Puerta de de transmisin

Pista/Bloque Pista

Pista

Pista

Pista

Clula SRAM

Entradas

A B C D

Tabla de look-up

S D Q

Con transistor de paso

Con puerta de transmisin

Con multiplexor

R

Figura 4: Tipos de conectores utilizados por XILINX

Es importante destacar que si se utilizan clulas SRAM la conguracin de la FPGA ser vlie o a a da unicamente mientras est conectada la alimentacin, pues es memoria voltil. En los sistemas e o a nales est claro que hace falta alg n mecanismo de almacenamiento no voltil que cargue las a u a clulas de RAM. Esto se puede conseguir mediante EPROMs o disco. e Este elemento de programacin es relativamente grande (necesita por lo menos 5 transistoo res), pero se puede implementar en el proceso normal de fabricacin del circuito (es CMOS). o Adems, permite recongurar la FPGA de una forma muy rpida. a a

Reloj (Clk)

Figura 5: Arquitectura del CLB de la XC2000

2.2.

Descripcin de las principales familias o

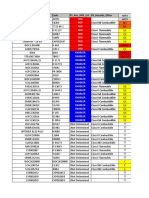

Hay m ltiples familias lgicas dentro de XILINX. Las primeras que surguieron son: XC2000 u o (descatalogada en el a o 1999), XC3000 y XC4000, correspondientes respectivamente a la prin mera, segunda y tercera generacin de dispositivos, que se distinguen por el tipo de bloque o lgico congurable (CLB) que contienen. En la actualidad existen tambin las familias de FPo e GA SpartanII, SpartanIII, Virtex, VirtexII y VirtexPro. La tabla 1 muestra la cantidad de CLBs que puede haber en cada FPGA de las familias base y ese mismo valor expresado en puertas equivalentes. SERIE XC2000 XC3000 XC4000XL Tipo CLB 1 LUT, 1 FF 1 LUT, 2 FF 3 LUT, 2 FF No de CLBs 64-100 64-484 64-3.136 Puertas Equivalentes 1.200-1.800 1.500-7.500 1.600-180.000

Los bloques lgicos congurables de la familia XC2000 se componen de una tabla de looko up con cuatro entradas y un biestable, con lo que puede generar cualquier funcin de hasta o 4 variables o dos funciones de 3 variables. El de la familia XC3000 es ms complejo: permite a implementar una funcin de 5 variables o dos funciones de 4 variables (limitadas a 5 difereno tes entradas, claro). Adems contiene dos biestables y cierta lgica. La familia XC4000 es ya a o mucho ms sosticada. Tiene tres tablas de look-up dispuestas en dos niveles, llegando a poder a implementar funciones de hasta 9 variables. En general, los recursos de interconexin son de tres tipos: o Conexiones directas, permiten la conexin de las salidas del CLB con sus vecinos ms o a directos (N, S, E y O). Interconexiones de propsito general, para distancias superiores a un CLB (ms all del o a a vecino). Son pistas horizontales y verticales del tama o de un CLB, pero que se pueden n empalmar para crear pistas ms largas. a L neas de largo recorrido, suelen cubrir lo ancho o largo de la pastilla. Permiten conexiones con un retardo mucho menor que uniendo las anteriores. El camino cr tico de un circuito es el recorrido que, desde una entrada hasta una salida, presenta un retardo mximo. a

Cuadro 1: Familias del fabricante XILINX

El bloque lgico ha de ser capaz de proporcionar una funcin lgica en general y reprogramao o o ble. La mejor forma de realizar esto es mediante una tabla de valores preasignados o tablas de look-up. Bsicamente, una tabla de look-up (LUTs en adelante) es una memoria, con un a circuito de control que se encarga de cargar los datos. Cuando se aplica en una direccin las o entradas de la funcin booleana la memoria devuelve un dato, lo que se puede hacer correspono der con la salida requerida. Falta a adir los componentes necesarios para desempe ar funciones n n no implementables con una memoria, tales como una bater de registros, multiplexores, buers a etc. Estos componentes estn en posiciones jas del dispositivo. a La ventaja de la utilizacin de este tipo de tablas es su gran exibilidad: una LUT de k o k entradas puede implementar cualquier funcin booleana de k variables, y hay 2 2 funciones o posibles. El inconveniente es obvio: ocupan mucho espacio y no son muy aprovechables. 5

2.3.

Arquitectura de la familia XC2000

Aunque hoy en d no se encuentran disponibles las FPGAs de esta familia, dado que cona tienen la arquitectura ms sencilla, vamos a utilizarlas como base para comprender el funcionaa miento de este tipo de dispositivos. En la gura 5 se puede ver cmo es el bloque congurable bsico de las XC2000. Contiene o a como elementos principales una tabla de look-up de 4 entradas y un biestable D. La tabla de look-up puede reproducir cualquier funcin de cuatro variables o dos funciones de tres variables. o De las dos salidas del CLB una se puede registrar, o se pueden dejar las dos combinacionales. 6

LDIM

Proyecto nal 2003-2004

LDIM

Proyecto nal 2003-2004

Lneas de Largo recorrido

CLB

CLB

Conexiones de propsito general

este enunciado (sacadas de [Xil91]), permitindose la realizacin de las simplicaciones que se e o consideren oportunas. A continuacin se darn algunas directrices sobre qu simplicaciones se o a e pueden hacer y cul es la forma de abordarlas. a Ha de quedar claro desde el principio que este dise o tiene un margen de libertad bastante n grande. Es decir, NO hay que hacer una FPGA idntica a una de la familia XC2000, sino que se e deben adaptar las especicaciones de la misma para poder utilizar las tcnicas vistas en clase: e dise o con doble fase de reloj, elementos CMOS de cualquiera de los tipos estudiados, etc. n

Matriz

de Conexin

Matriz

de Conexin

3.1.

Estructura

Conexiones directas

CLB

CLB

Matriz

de Conexin

Matriz

de Conexin

Figura 6: Recursos de interconexin en la familia XC2000 o

Adicionalmente, en el bloque hay 6 multiplexores que permitirn seleccionar las conexiones a que se desea hacer dentro de cada CLB particular. Por ello, en sus terminales de seleccin o necesitarn un elemento de memoria con el valor deseado (ver gura 4). Ntese que la salida a o del biestable se puede llevar de vuelta a una de las entradas de la LUT, siempre y cuando se conguren adecuadamente los selectores oportunos. Esto es muy util, pues permite implementar estructuras realimentadas como son contadores o mquinas de estados. a Por otro lado, la arquitectura de rutado de la familia XC2000 utiliza tres tipos de recursos de interconexin: conexiones directas, conexiones de propsito general y l o o neas de largo recorrido. Todos estos recursos se pueden ver en la gura 6. Las conexiones directas (en la gura aparecen slo para un CLB) proporcionan enlace desde la salida de un CLB hasta sus vecinos superior, o inferior y a la derecha. Si hay que conectar una red a un bloque ms lejano hay que utilizar las a conexiones de propsito general, que son segmentos de pista dispuestas horizontal y verticalmente o a lo largo de toda la FPGA. En particular, en esta familia hay cuatro segmentos horizontales y cinco verticales por canal. Su longitud est limitada siempre a la distancia ja entre 2 CLBs, a por lo que para realizar conexiones ms largas hay que utilizar las matrices de interconexin. a o Es importante observar que la utilizacin de estos recursos repercutir negativamente en las o a prestaciones del dise o, pues los conectores de la matriz introducen forzosamente un retardo. n Las l neas de largo recorrido se utilizan para conexiones que han de llegar a varios CLBs con bajo skew.

La FPGA que se debe realizar constar de 16 CLBs. En principio basta con este tama o, a n pues el dise o ha de ser completamente regular y estructurado, caracterizando perfectamente a n nivel de mdulos, lo que lo har fcilmente ampliable. Recordamos que la meta que se persigue o a a es un dise o correcto, con un trazado simple y bien estructurado. n Adems de los 16 CLBs, es necesario implementar los recursos de conexin (tanto las l a o neas como las matrices de interconexin) y el sistema de control que gestione la programacin de o o toda la FPGA. Para facilitar la comprensin del problema, hay que ver en el dise o dos estructuras supero n puestas: una correspondiente a la FPGA propiamente dicha, como la ve el dise ador nal; otra n estructura constituye el entramado necesario para realizar la programacin de la FPGA. Esta o ultima parte es transparente para el usuario. Es importante destacar que la programacin de la FPGA no es cr o tica en cuanto a prestaciones, porque se hace una unica vez y no es determinante. Slo ha de ser correcta. Sin embargo, o s interesa optimizar el funcionamiento de la FPGA una vez programada para la implementacin o nal.

3.2.

Bloques lgicos o

La arquitectura del CLB de la XC2000 se present en la gura 5, siendo sus componentes o principales: Una LUT de 4 entradas y 2 salidas Un biestable. Seis multiplexores, cada uno con sus correspondientes elementos de memoria. La LUT que vamos a implementar es como se describi en el ejercicio 4 (apartado 3.3). Es o decir, ha de ser capaz de implementar dos funciones de 4 entradas independientes 1 . En Xilinx, el biestable del CLB dispone de una entrada de reloj o enable que se puede excitar con tres l neas: La entrada de reloj clk. La entrada de propsito general C. o La funcin combinacional G (salida de la LUT). o

3.

Especicaciones

Como ya se ha comentado, vamos a dise ar una versin simplicada de una FPGA de n o la familia XC2000 de Xilinx. Todo el dise o debe seguir las especicaciones que acompa an n n 7 8

LDIM

Proyecto nal 2003-2004

LDIM

Proyecto nal 2003-2004

A F

A B C D

F

D

Tabla de look-up

X Y

a b c 0 0 0 0 1 1 1 1 0 0 1 1 0 0 1 1 0 1 0 1 0 1 0 1

f 1 0 1 0 1 0 1 1

a Memoria b c 8x1 f

S Q

Switch 2x2

R

Din(0..1) Prog

D G

Figura 9: S mbolo de la LUT

Figura 10: Implementacin LUT con SRAM o

Reloj ( 2) 1,

Figura 7: Biestable del CLB

Figura 8: Matriz de interconexin o

Dado que nosotros trabajamos con dos fases de reloj, no tiene mucho sentido que se puedan utilizar otras se ales como reloj, por lo que una implementacin perfectamente vlida del CLB n o a ser la de la gura 7. En cuanto al tipo de biestable, el que se encuentra realmente en el CLB a de Xilinx es congurable, de forma que se puede programar como latch D sensible al nivel o biestable D sensible al anco. Para nuestros propsitos ser suciente implementar uno de los o a dos tipos de biestable2 , sin que sea programable. Con esto el n mero de multiplexores del CLB u que nos hacen falta es menor. Cualquier otra simplicacin que se haga al CLB habr de justicarse de forma similar a la o a realizada en el prrafo anterior. a

Si queremos realizar una LUT de dos salidas lo podemos hacer con 2 memorias de 2 k posiciones, o lo que es mejor, con una memoria de k l neas de direccin y 2 bit de palabra. Por o supuesto, se est ocupando mucha area, pero esta es la mejor forma de realizar una funcin a o booleana cualquiera. Se deja al alumno decidir la mejor forma de implementar la memoria para conseguir un buen compromiso area-tiempo de acceso. La equivalencia de terminales entre la LUT y la memoria son los siguientes. Las l neas de entrada corresponden al bus de direcciones; las l neas de datos equivalen a bus de datos de entrada; las salidas (X, Y en nuestro caso) corresponden a bus de datos de salida; y la se al de n programacin ser la l o a nea de lectura/escritura, R/ W de la memoria. Dependiendo del tipo de implementacin de la memoria se puede necesitar alguna entrada ms (por ejemplo, se puede o a utilizar alguna se al de reloj para temporizar el funcionamiento de la memoria). n 3.3.1. Implementacin de memorias CMOS o

a Una memoria CMOS3 integra los siguientes componentes bsicos: La clula de memoria. Puede ser esttica o dinmica dependiendo de la forma de almacee a a namiento del dato. Las clulas estticas son ms grandes que las dinmicas, pero tienen e a a a la ventaja de no necesitar refresco. La forma ms eciente de distribuir las clulas es a e colocarlas en una matriz cuadrada, como se muestra en la gura 11. El decodicador de las, que permite seleccionar la la de la matriz de clulas de memoria e a la que se quiere acceder (tanto para lectura como para escritura). Para ello se utilizarn a parte de las l neas de direccin. o El decodicador de columnas, que permite seleccionar las clulas de la palabra que se va a e leer o escribir entre los datos de la la proporcionada por el decodicador de las. Circuito de escritura de las clulas adecuadas (las de la palabra deseada). e Circuito de lectura de la la adecuada (sense amplier). Circuito de control de l nea de bit, que acondiciona esta l nea para que sean factibles las operaciones de lectura y escritura. La forma de distribuir las clulas en la matriz se describe a continuacin. Hay que intentar e o hacer una matriz lo ms cuadrada posible. Siguiendo la terminolog de la gura 11, supongamos a a que tenemos una memoria con 2k palabras (por lo tanto con k l neas de direccin) y cada palabra o

3

3.3.

Descripcin detallada de la LUT o

Hasta ahora, se ha presentado el CLB de la XC2000 desde el punto de vista de un usuario nal. Dado que ahora se va a implementar siguiendo una metodolog full-custom, es necesario a conocer ms detalles. En la gura 9 se ve el conjunto de entradas y salidas que tiene realmente a la LUT. Como se puede observar, en el s mbolo aparecen dos entradas nuevas, las relacionadas con la programacin de la LUT: o Las l neas de datos Din, sirven para introducir en la LUT los datos de programacin. o La l nea de programacin Prog, su valor ser diferente en funcin del modo en que se o a o est (programacin/funcionamiento normal). e o Como ya se ha explicado previamente, la forma inmediata de implementar una LUT es utilizar una memoria RAM esttica. Por ejemplo, considera la tabla de verdad de la funcin a o f = ab + c que aparece en la gura 10. Si esta funcin lgica se implementa con una LUT de o o o tres entradas, ser necesaria una RAM de 2 3 = 8 posiciones, y almacenaremos 1 en la posicin a 000, 0 en la posicin 001, y as sucesivamente. o

NOTA: las salidas de la LUT en las especicaciones de Xilinx se llaman F y G, siendo X e Y las salidas del CLB; adoptaremos esta notacin a partir de ahora. o 2 Atencin, un biestable no es un registro dinmico. o a

1

El cap tulo 8 de [WE94] contiene una excelente descripcin de la implementacin de memorias CMOS. o o

10

LDIM

Proyecto nal 2003-2004

LDIM

Proyecto nal 2003-2004

La salida Y se puede conectar a la entrada B del CLB situado a la derecha.

Decod. filas Matriz de clulas .... nxm

clula addr(k-l)

control lnea

addr(k-l)

addr(l) r/w

.... Sense ampl. Decod. columnas Cto. escritura

Decod filas

addr(l)

Decod cols.

Sense ampl. Cto. escritura

r/w clk

Evidentemente esto es para los CLBs internos de la FPGA. Los que estn en la periferia e se podrn conectar directamente a los pads de E/S. Por supuesto, las l a neas de E/S del CLB no tienen por qu tener la orientacin mostrada en la gura, cada proyecto se realizar con la e o a orientacin que cada grupo estime mejor. o En cuanto a las l neas de largo recorrido, se deja a voluntad del dise ador implementar las n que son programables. En caso de considerarlas, se tendr que elegir qu entradas y salidas del a e CLB tendrn acceso a las mismas. En la gura 13 se ha presentado como ejemplo dos l a neas de largo resorrido y algunas entradas accediendo a las mismas. Hablamos de l neas programables porque hay 2 l neas de largo recorrido que en nuestro caso NO sern programables y s son a obligatorias: las l neas que llevan las dos fases del reloj, que como se sabe, se deben rutar con especial cuidado.

Dato(0..i)

Dato_in

Dato_out

Figura 11: Estructura de una memoria

Figura 12: R/W de una clula de memoria e

3.5.

Circuito de control de programacin o

tiene b bits. En total tendremos 2k b clulas. Todas estas clulas se ordenan en una matriz de e e neas de direccin o dimensiones n m, donde m = 2kl y n = 2l b, siendo l una parte de las l necesaria para hacer la seleccin de las columnas. Hay que intentar que n y m sean lo ms o a parecido posible para tener forma cuadrada. En la gura 12 aparece representada la relacin existente entre todos los elementos constio tuyentes de la memoria y su disposicin en las operaciones de lectura y escritura. o

3.4.

Recursos de interconexin o

Como se expuso en la seccin 2.3, la arquitectura de rutado de la familia XC2000 utiliza tres o tipos de recursos de interconexin: conexiones directas, conexiones de propsito general y l o o neas de largo recorrido (ver gura 6). Toda esta estructura se puede simplicar para hacerla ms fcil a a de implementar. En esta seccin hacemos una propuesta de cmo se pueden realizar. o o Comenzando por las conexiones de propsito general, sabemos que se basan en la unin de o o segmentos de pista entre CLBs. Para simplicar el rutado vamos a considerar que son 4 l neas tanto en sentido horizontal com en vertical. Necesitaremos dos clulas especiales para realizarlas: e La matriz de interconexin (gura 8), que permite el cruce de pistas horizontales y vertio cales. No tiene por qu posibilitar la conexin de todas las l e o neas con todas. Se implementar utilizando 4 switch de 2x2. a Mdulos de conexin de las entradas y salidas del CLB a los segmentos de pista de las o o conexiones de propsito general. Un ejemplo de cmo se puede hacer estas conexiones o o se ve en la gura 13. Como se ve, hay que facilitar el acceso a las entradas del CLB y la salida del mismo. No tiene por qu ser el acceso slo a las l e o neas verticales; esto depender fundamentalmente del trazado que se realice del CLB. a Siguiendo esta propuesta, las conexiones directas que vamos a implementar son las descritas en el manual de Xilinx: La salida X se puede conectar a las entradas A o B del CLB inferior o a las entradas C o D del CLB superior. 11

Esta parte de la FPGA debe ser una extensin del circuito de programacin de una LUT. o o Ha de ser un circuito unico que congure forma secuencial toda la FPGA. Aunque el la familia XC2000 hay varias formas de programar la FPGA, nosotros nos centraremos en el modo ms sencillo: el denominado modo Serial/Slave. En este caso los datos llegan a en serie por un pin de entrada de datos de forma s ncrona: un reloj (CCLK) valida los datos de la entrada serie (DIN). Se deja a alumno denir el formato de los datos de entrada cuando se est en a conguracin. El control de la FPGA se puede hacer desde un microprocesador, resultando el o esquema de conexin ms sencillo el que aparece en la gura 14. o a Resulta evidente que hay que utilizar los recursos de interconexin para realizar la proo gramacin, por lo que ser necesario congurar primero las interconexiones para realizar la o a programacin de los CLBs. o Para programar las LUTs, se sugiere como forma sencilla de implementacin comenzar cono gurando todas las l neas para que lleven a, b c y d a todos los CLBs de la FPGA. Luego se utilizar unas lneas de seleccin de CLB que vayan habilitando cada CLB mientras se hace an o la programacin. o Son necesarios unos decodicadores globales que sirvan para llevar el dato a cada la/columna de CLBs. Esto se puede ver como el acceso en escritura a una memoria. Si se realiza la escritura por las o columnas, har falta unos registros de desplazamiento an globales. Todos los elementos de memoria se deben enlazar siguiendo una losof scan-path. a

Referencias

[BFRV92] Stephen D. Brown, Robert J. Francis, Jonathan Rose, and Zvonko G. Vranesic. Field-Programmable Gate Arrays. Kluwer Academic Publishers, Norwell, Massachusetts, 1992.

a o [CSR+ 99a] P. Chow, S. Ong Seo, J. Rose, K. Chung, G. Pez-Monzn, and I. Rahardja. The design of an sram-based eld programmable gate array-part i: Architecture. IEEE Trans. on VLSI Systems, 7(2):191197, June 1999.

12

LDIM

Proyecto nal 2003-2004

LDIM

Proyecto nal 2003-2004

PHI 1

PHI 2

SISTEMA MICROPROCESADOR

CLK

CLK

PHI 1 PHI 2 M0 DONE M1

DONE

PUERTO E/S

M2

FPGA

DOUT

DIN

Largo Recorrido

A B C D

din

prog X Elem. mem.

RESET

RESET RESET

CLB

Y clk enb d_in progM

Figura 14: Conexin de programacin. o o

Matriz

de Conexin Mdulo de conexin

A B C D clk enb X din prog

Matriz

de Conexin

din A B C D clk enb prog X

[CSR+ 99b] P. Chow, S. Ong Seo, J. Rose, K. Chung, G. Pez-Monzn, and I. Rahardja. The a o design of an sram-based eld programmable gate array-part ii: Circuit design and layout. IEEE Trans. on VLSI Systems, 7(3):321330, September 1999. [WE94] [Xil91] Neil H. E. Weste and Kamran Eshraghian. Principles of CMOS VLSI Design. Addison-Wesley, 2nd edition, 1994. Xilinx Inc., 2100 Logic Drive, San Jose, CA 95124. The Programmable Gate Array Data Book, 1991.

CLB

Y

CLB

Y

Matriz

de Conexin

Matriz

de Conexin Mdulo de conexin

din A B C D clk

prog X

CLB

Y enb

Figura 13: Esquema de posibles conexiones en la FPGA. Detalle de conexin con su elemento de memoria. o

13

14

Vous aimerez peut-être aussi

- Revolucion InalambricaDocument9 pagesRevolucion InalambricaEmanuel GarcesPas encore d'évaluation

- Matriz Compatibilidad Guamal Rev30092021Document12 pagesMatriz Compatibilidad Guamal Rev30092021MONICA GARCIAPas encore d'évaluation

- Muestreo Discrecional o Por JuicioDocument3 pagesMuestreo Discrecional o Por JuicioJorge Javier Granda Granadino100% (1)

- WPS SmawDocument4 pagesWPS SmawMarcos Gajardo0% (1)

- Tarea 2 Trabajo ColaborativoDocument26 pagesTarea 2 Trabajo ColaborativoSteven Rodriguez100% (1)

- Seguridad en Laboratorios de Ingenieria CivilDocument34 pagesSeguridad en Laboratorios de Ingenieria CivilMarlon Mark Sánchez PoncePas encore d'évaluation

- 2 - NSR-10Document6 pages2 - NSR-10Freddy GutierrezPas encore d'évaluation

- Sistemas Automáticos de Extinción de Incendios para La Protección de Motores de VehículosDocument5 pagesSistemas Automáticos de Extinción de Incendios para La Protección de Motores de VehículosarwisisPas encore d'évaluation

- Motor Suzuki 350 - Septiembre 2017Document2 pagesMotor Suzuki 350 - Septiembre 2017Martin Alejandro D'EliaPas encore d'évaluation

- PA3 Geometria TerminadoDocument26 pagesPA3 Geometria TerminadoRobertoespinozaq100% (1)

- Medio Fisico - Lomas de Jesus PDFDocument95 pagesMedio Fisico - Lomas de Jesus PDFJackeline Alegre RamirezPas encore d'évaluation

- Generaciones de Las ComputadorasDocument23 pagesGeneraciones de Las ComputadorasAnderson PrietoPas encore d'évaluation

- Pemsa Guía Instalación RejibandDocument20 pagesPemsa Guía Instalación RejibandVEMATELPas encore d'évaluation

- Perfiles suelos oficinasDocument3 pagesPerfiles suelos oficinasDaniela Milan Noels100% (1)

- 3 Ejemplos Con SolverDocument7 pages3 Ejemplos Con SolverMarco NovoaPas encore d'évaluation

- Requerimientos Instalacion ElectricaDocument14 pagesRequerimientos Instalacion ElectricasalgoraPas encore d'évaluation

- Gq-Fo-29 Al 36 Formatos InspeccionesDocument14 pagesGq-Fo-29 Al 36 Formatos InspeccionesGloria HernandezPas encore d'évaluation

- Retroalimentacion Modelos CDocument65 pagesRetroalimentacion Modelos CMonik Martinez67% (3)

- CO-PE-1PE403-ME-SA-04 Reporte Diario de Producción Cisterna REV 01Document5 pagesCO-PE-1PE403-ME-SA-04 Reporte Diario de Producción Cisterna REV 01Yesika RiosPas encore d'évaluation

- Telnet SSHDocument14 pagesTelnet SSHJeison VargasPas encore d'évaluation

- Procesamiento de carnes frías en planta de CarnifreshDocument2 pagesProcesamiento de carnes frías en planta de CarnifreshDixie Julieth Ibarra Rivera100% (1)

- Cálculo Del Rendimiento Del ConcretoDocument2 pagesCálculo Del Rendimiento Del ConcretoEfrain Sotelo Buatista100% (1)

- Impacto Ambiental Del Sector de La Construcción - Fábio Maia GuzenskiDocument232 pagesImpacto Ambiental Del Sector de La Construcción - Fábio Maia GuzenskiRicardo MantariPas encore d'évaluation

- Catalogo Herramientas Bosch PDFDocument50 pagesCatalogo Herramientas Bosch PDFRebeca AlvarezPas encore d'évaluation

- 0 - Diseño de Bocatoma - Quebrada ChamicoDocument12 pages0 - Diseño de Bocatoma - Quebrada Chamicoanon_71920229Pas encore d'évaluation

- Manual de Ingenierias en La EdificacionDocument131 pagesManual de Ingenierias en La EdificacionJorge Abraham DevoPas encore d'évaluation

- Autorización de Creación de Usuario Página Web PDFDocument1 pageAutorización de Creación de Usuario Página Web PDFAngelaPas encore d'évaluation

- Banco Temático de Encofrados Fierrería - Tomo IvDocument274 pagesBanco Temático de Encofrados Fierrería - Tomo IvDesiderio Chavez YauriPas encore d'évaluation

- CP #6 - Clase 14 - TQDocument5 pagesCP #6 - Clase 14 - TQAlejandra CruzPas encore d'évaluation

- Paquete Estandar AislanteDocument2 pagesPaquete Estandar AislanteDavid VillaPas encore d'évaluation