Académique Documents

Professionnel Documents

Culture Documents

Tanner Manual

Transféré par

Santhameena MuthuramalingamDescription originale:

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

Tanner Manual

Transféré par

Santhameena MuthuramalingamDroits d'auteur :

Formats disponibles

The following is the path for opening S-Edit tool : Start All Programs Tanner EDA Tanner V 15 S-Edit

Edit V15.0 32 Bit

To do schematic entry , run S-Edit tool

To create a new design : File New Design

Enter the design name and give the path where it should be saved. Example : techlabs_designs is the design folder C:\Documents and Settings\phanendra\My Documents\Tanner_lab is the target location of design folder

Add component libraries. The path for component libraries is given below. My Documents\Tanner EDA\Tanner Tools v15.0\Process\Generic_250nm Click add in S-Edit window for adding the libraries and follow the path of process folder.

Double click all the component libraries under Generic_250nm and add all tanner database files (.tdb). To add Spice commands and Spice Elements for setting spic e simulation follow the path. My Documents\Tanner EDA\Tanner Tools v15.0\Process\Standard Libraries

Now , we need to create a new cell.

Give a new name for cell

Scroll mouse for Zoom In and Zoom Out. And to view entire design press home button on keyboard. Click on Generic_250nm_Devices folder on libraries

To add any component either drag the component on to the design area (black region with grids) or click Instance , then Instance Cell pops up where a user can change the properties . Keeping the icon on the design area , components icon can be placed N number of times. Either press ESC button on keyboard or Done on Instance Cell window to stop placing of cells.

In the same way place PMOS component on the design area.

To Zoom the design area scroll the mouse or press home button on keyboard. 7

Now place Vdd and Gnd Instances from the Misc folder under Library.

Now place a DC Voltage and Pulse Voltage source from the Spice Elements folder under Library. 8

To place a Voltage Source, Click Spice Elements, Under Spice Elements Click Voltage Source and then Instance.

To place a DC voltage source, change the interface to DC and edit the voltage value . Click done only after placing the voltage source on design area.

To place a Pulse voltage source, change the interface to DC and edit the voltage value . Click done only after placing the voltage source on design area.

Place Vdd and Gnd even for the voltage sources as shown.

Now place Input and Output ports.

10

When an input port is placed, In port window pops up where we can edit the port name , font size and orientation. Even the port orientation can be changed by pressing r button on key board.

Now we have placed all the components on the design window. And connections are made using the wire as shown below

11

Now we need to set up simulation.

12

Now , give the path of library file. My Documents\Tanner EDA\Tanner Tools v15.0\Process\Generic_250nm\ Generic_250nm_Tech \Generic_250nm.lib After giving the path of Generic_250nm.lib, add TT as shown below. My Documents\Tanner EDA\Tanner Tools v15.0\Process\Generic_250nm\ Generic_250nm_Tech \Generic_250nm.lib TT TT is the corner model used . There are different types of Corner models in .lib file * TT : Typical model for NMOS & PMOS * SS : Slow NMOS Slow PMOS model * FF : Fast NMOS Fast PMOS model * SF : Slow NMOS Fast PMOS model Set Transient Analysis as shown below .

13

Run Simulation.

14

To view waveforms , place PrintVoltage from Spice Commands library.

Now , Run Simulation. 15

Waveforms can be viewed on W-Edit tool once Simulation is Run again.

Waveforms can be expanded by clicking Chart Expand Traces on W-Edit window.

To extract the spice netlist from schematic, go to S-Edit and click the T-Spice option.

16

The following spice netlist is extracted from the schematic which contains the information of the circuit connections across its nodes, analysis setup , voltages applied and type of library used for simulation.

Save the netlist as inverter_sch.sp ********* Simulation Settings - General Section ********* .lib "C:\Documents and Settings\phanendra\My Documents\Tanner EDA\Tanner Tools v15.0\Process\Generic_250nm\Generic_250nm_Tech\Generic_250nm.lib" TT *-------- Devices With SPICE.ORDER == 0.0 -------***** Top Level *****

17

MNMOS_2_5v_1 Out In Gnd 0 NMOS25 W=1.5u L=250n AS=975f PS=4.3u AD=975f PD=4.3u $ $x=4793 $y=3700 $w=414 $h=600 MPMOS_2_5v_1 Out In Vdd Vdd PMOS25 W=3u L=250n AS=1.95p PS=7.3u AD=1.95p PD=7.3u $ $x=4793 $y=4700 $w=414 $h=600 *-------- Devices With SPICE.ORDER > 0.0 -------VVoltageSource_2 Vdd Gnd DC 5 $ $x=1800 $y=3800 $w=400 $h=600 VVoltageSource_1 In Gnd PULSE(0 5 0 5n 5n 95n 200n) $ $x=3400 $y=3600 $w=400 $h=600 .PRINT TRAN V(In) $ $x=2850 $y=4350 $w=1500 $h=300 $r=180 .PRINT TRAN V(Out) $ $x=6250 $y=4050 $w=1500 $h=300 ********* Simulation Settings - Analysis Section ********* .tran 50n 1u start=0 ********* Simulation Settings - Additional SPICE Commands ********* .end

L-EDIT

CMOS Inverter Structure: -

18

The following is the path for opening L-Edit tool : Start All Programs Tanner EDA Tanner V 15 L-Edit V15.0 32 Bit

To do Layout , run L-Edit tool. Follow window pops up.

Go to File New

19

Click Browse My Documents\Tanner EDA\Tanner Tools v15.0 \Process \Generic_250nm \Generic_250nm_Tech and add Generic_250nm_TechSetup.tdb file and click ok.

Go to Cell New

20

Name the Cell

Grids spacing can be minimized or maximized using or + sign To change the technology Goto setup-> Design

21

Select Lambda or microns accordingly and click ok Before designing layout we need to remember following equations N Diffusion = N Implant and Active (1) P Diffusion = P Implant and Active - (2) From layer palette, we can select layer then for drawing layer we need to switch at Drawing boxes as follows

Now we can start layout designing. We are Taking Example of CMOS Layout design Background of L-Edit is P-Substrate by default We need to design PMOS, First draw active

22

Now draw P Implant over Active with keeping in mind Lambda based design rules

Now draw poly over it accordingly

23

Now draw Contact for Active region

Now draw metal1 around Contact

24

We have designed source, gate and drain. Now we have to design bulk by creating a N+ diffusion

Now we need to put this in N-Well

25

We can perform DRC (Design Rule Check) at every stage

If we are violating any Design rule then it will be shown in Error verification navigator

26

By clicking on the error, the tool points to the error that occur on layout.

27

By increasing the poly density area in the layout we can minimize that error. And again run DRC check.

We need to design Gate contact.

28

To define port, go to (A)

We can now find the port name added to gate .

29

Similarly we do NMOS layout.

After connecting NMOS and PMOS , CMOS layout looks like as follows. 30

Now we can extract netlist by doing some settings

31

32

Click options in Setup Extract above, and uncheck all Hiper Verify Options.

Run Extraction, An spice file will open as follows

This netlist is saved as inverter_layout.spc VVoltageSource_1 Vdd Gnd DC 5 VVoltageSource_2 vin Gnd PULSE(0 5 0 5n 5n 95n 200n) .PRINT TRAN V(vin) .PRINT TRAN V(vout) .tran 1ns 500ns Final netlist .lib "C:\Documents and Settings\phanendra\My Documents\Tanner EDA\Tanner Tools v15.0\Process\Generic_250nm\Generic_250nm_Tech\Generic_250nm.lib" TT

33

M1 Vout Vin GND GND_ NMOS25 l=1.95e-006 w=2.55e-006 ad=5.1e-012 as=4.08e012 pd=9.1e-006 ps=8.3e-006 $(24.65 -272199 26.6 -272197) M2 Vout Vin VDD VDD PMOS25 l=1.95e-006 w=2.55e-006 ad=5.2275e-012 as=3.9525e-012 pd=9.2e-006 ps=8.2e-006 $(24.65 -272194 26.6 -272192) VVoltageSource_1 Vdd Gnd DC 5 VVoltageSource_2 Vin Gnd PULSE(0 5 0 5n 5n 95n 200n) .PRINT TRAN V(Vin) .PRINT TRAN V(Vout) .tran 1ns 500ns .end

After saving spice file, we can simulate it, W-Edit will invoked and we can check the response:

34

LVS (Layout Vs Schematic)

We got two output files (one from S-Edit and second from L-Edit), Now we can compare results by using LVS 35

Double click on LVS, and file -> new & Select file type-> LVS setup, then ok

We need to browse spice netlist files for layout netlist and Schematic netlist

36

After including these files, we need to run verification as follows & Results can be checked from Verification Window.

Both netlists are equal.

37

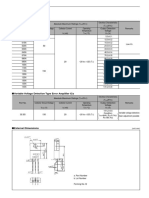

Experiment No. 5: 5. Schematic Entry and SPICE simulation of MOS differential amplifier. Determination of gain, bandwidth, output impedance and CMRR. Theory : A differential amplifier is a type of electronic amplifier that multiplies the difference between two inputs by some constant factor (the differential gain). Many electronic devices use differential amplifiers internally. The output of an ideal differential amplifier is given by:

Where and are the input voltages and Ad is the differential gain. In practice, however, the gain is not quite equal for the two inputs. This means, for instance, that if and are equal, the output will not be zero, as it would be in the ideal case. A more realistic expression for the output of a differential amplifier thus includes a second term.

Ac is called the common-mode gain of the amplifier. As differential amplifiers are often used when it is desired to null out noise or biasvoltages that appear at both inputs, a low common-mode gain is usually considered good. The common-mode rejection ratio, usually defined as the ratio between differentialmode gain and common-mode gain, indicates the ability of the amplifier to accurately cancel voltages that are common to both inputs. Common-mode rejection ratio (CMRR):

In a perfectly symmetrical differential amplifier, Ac is zero and the CMRR is infinite. Note that a differential amplifier is a more general form of amplifier than one with a single input; by grounding one input of a differential amplifier, a single-ended amplifier results. An operational amplifier, or op-amp, is a differential amplifier with very high differential-mode gain, very high input impedances, and a low output impedance. Some kinds of differential amplifier usually include several simpler differential amplifiers. For example, an instrumentation amplifier, a fully differential

38

amplifier, an instrument amplifier, or an isolation amplifier are often built from several op-amps. Differential amplifiers are found in many systems that utilise negative feedback, where one input is used for the input signal, the other for the feedback signal. A common application is for the control ofmotors or servos, as well as for signal amplification applications. In discrete electronics, a common arrangement for implementing a differential amplifier is the long-tailed pair, which is also usually found as the differential element in most op-amp integrated circuits. A differential amplifier is used as the input stage emitter coupled logic gates. Design : In S-Edit, draw the circuit as shown below.

Convert the schematic to symbol

39

40

Using the lines for drawing, create a symbol for op-amp as below.

Make the connections accordingly.

41

Again create a symbol for the above circuit and make the connections accordingly.

Vpwr and Vpwr/2 are the instance name of the voltage souces. Now place the spice commands for finding out the gain, bandwidth.

42

Simulation setup

Then click run simulation

43

Gain , Frequency and Bandwidth can be viewed from simulation window above. And waveforms can be viewed from w-Edit

6th Experiment is already shown in the Tanner working Flow. 7th Experiment is 10 Bit Number Controlled Oscillator. The following schematic shows 10 bit VCO. By changing the values of D0 D9 the input pulse applied varies accordingly.

44

Vous aimerez peut-être aussi

- Mentor Graphics Lab ManualDocument27 pagesMentor Graphics Lab ManualHavi KosuruPas encore d'évaluation

- DEC Report 4 (C)Document11 pagesDEC Report 4 (C)S M Akash100% (1)

- Tanner EDA Simulation DetailedDocument125 pagesTanner EDA Simulation DetailedJayaram KumarPas encore d'évaluation

- Week #6 - Verilog Behavioural Modeling (Part 4) FSMDocument21 pagesWeek #6 - Verilog Behavioural Modeling (Part 4) FSMKhayrinNajmiPas encore d'évaluation

- VLSI & Embedded Systems Lab ManualDocument137 pagesVLSI & Embedded Systems Lab Manualganga avinash reddyPas encore d'évaluation

- Experiment 7 - Flip-FlopsDocument4 pagesExperiment 7 - Flip-FlopsPrr PrrPas encore d'évaluation

- Vlsi Implementation For High Speed AddersDocument6 pagesVlsi Implementation For High Speed AddersPardha Saradhi Damarla100% (1)

- Designing Finite State Machines (FSM) Using VerilogDocument8 pagesDesigning Finite State Machines (FSM) Using VerilogusaravanakumarPas encore d'évaluation

- 20.10.20 Line CodingDocument27 pages20.10.20 Line CodingDivyanshi SharmaPas encore d'évaluation

- Chapter - 03 Baseband Demodulation-DetectionDocument34 pagesChapter - 03 Baseband Demodulation-DetectionOsob MohamudPas encore d'évaluation

- Hardwired Control Unit: A Case-Study Report Submitted For The Requirement ofDocument23 pagesHardwired Control Unit: A Case-Study Report Submitted For The Requirement ofShinde D PoojaPas encore d'évaluation

- Abdullah Khurram - Coal Lab 12Document9 pagesAbdullah Khurram - Coal Lab 12muhammad saadPas encore d'évaluation

- IC Layout Using L-EDITDocument16 pagesIC Layout Using L-EDITEliasA.TiongkiaoPas encore d'évaluation

- Revision Notes On TransistorsDocument5 pagesRevision Notes On TransistorsvproPas encore d'évaluation

- 4bit ComparatorDocument7 pages4bit ComparatorDavis Spat TambongPas encore d'évaluation

- Delay Optimization TechniquesDocument38 pagesDelay Optimization TechniquesiknowiamanidiotPas encore d'évaluation

- Introduction To TMS320C6713 DSP Starter Kit DSK)Document18 pagesIntroduction To TMS320C6713 DSP Starter Kit DSK)Anup DharanguttiPas encore d'évaluation

- Design of A RISC Microcontroller Core in 48 HoursDocument11 pagesDesign of A RISC Microcontroller Core in 48 HoursPulkit TrivediPas encore d'évaluation

- Vlsi Lab ManualDocument26 pagesVlsi Lab ManualAnirban Das DebPas encore d'évaluation

- Multilevel view of a machine's architectureDocument3 pagesMultilevel view of a machine's architectureVarsha Rani0% (1)

- Stick Diagram & Euler Path: VLSI Design CourseDocument20 pagesStick Diagram & Euler Path: VLSI Design CourseSelvasundar KumarPas encore d'évaluation

- DLD GTU Question Bank: Chapter-1 Binary SystemDocument5 pagesDLD GTU Question Bank: Chapter-1 Binary Systemnirav34Pas encore d'évaluation

- Mutation TesingmutationDocument249 pagesMutation TesingmutationKhushboo Khanna100% (1)

- Calculate Fibonacci Numbers in Assembly LanguageDocument2 pagesCalculate Fibonacci Numbers in Assembly LanguageDilawarPas encore d'évaluation

- Moving To Altium Designer From Mentor Graphics DxDesignerDocument39 pagesMoving To Altium Designer From Mentor Graphics DxDesigneronafetsPas encore d'évaluation

- Electrical Network Analysis Lab Course Lab Course: Prepared By: Husan AliDocument34 pagesElectrical Network Analysis Lab Course Lab Course: Prepared By: Husan AliengrhusanPas encore d'évaluation

- Digital Integrated Circuits: A Design PerspectiveDocument84 pagesDigital Integrated Circuits: A Design PerspectivedurraizaliPas encore d'évaluation

- Experiment No 6: Implementation of Instruction Fetch Unit: Team Details: Terminal No: SL No Name Id No 1 2 3Document6 pagesExperiment No 6: Implementation of Instruction Fetch Unit: Team Details: Terminal No: SL No Name Id No 1 2 3Shreenath VyasPas encore d'évaluation

- Dynamic Logic CktsDocument16 pagesDynamic Logic CktsaashishscribdPas encore d'évaluation

- Orcad PSpice DesignerDocument47 pagesOrcad PSpice DesignerAishwarya JS100% (1)

- TCL TutorialDocument161 pagesTCL TutorialvsalaiselvamPas encore d'évaluation

- To Design An Adaptive Channel Equalizer Using MATLABDocument43 pagesTo Design An Adaptive Channel Equalizer Using MATLABAngel Pushpa100% (1)

- 8086 Inst and Assembler DirectivesDocument49 pages8086 Inst and Assembler DirectivesGiridhar Kattiri100% (2)

- VLSI I - V CharacteristicsDocument46 pagesVLSI I - V CharacteristicsMALATHI .LPas encore d'évaluation

- Question Bank - MCQ Based Exam - UNIT-3 - SPDocument9 pagesQuestion Bank - MCQ Based Exam - UNIT-3 - SPVishal KesharwaniPas encore d'évaluation

- Flash ADC MidsemDocument9 pagesFlash ADC MidsemBikashKumarMoharanaPas encore d'évaluation

- Single Stage AmplifiersDocument38 pagesSingle Stage AmplifiersSivakumar PothirajPas encore d'évaluation

- Digital Flip-Flops Applications Registers CountersDocument52 pagesDigital Flip-Flops Applications Registers CountersGeethanjali.pPas encore d'évaluation

- 16 Bit Accumulator Using NAND and Logical Effort MethodDocument22 pages16 Bit Accumulator Using NAND and Logical Effort MethodJaydip FadaduPas encore d'évaluation

- ECE 4141-Experiment 3 - CMOS NAND Transistors Sizing Simulation Using PSPICEDocument6 pagesECE 4141-Experiment 3 - CMOS NAND Transistors Sizing Simulation Using PSPICEAnwar Zainuddin100% (2)

- Solid State Device Modeling 1Document199 pagesSolid State Device Modeling 1DarwinPas encore d'évaluation

- 32k-Bit Sleepy SramDocument18 pages32k-Bit Sleepy Sramapi-19668941Pas encore d'évaluation

- Barrel ShifterDocument79 pagesBarrel ShifterVinay Reddy100% (2)

- 2 To 4 DecoderDocument6 pages2 To 4 DecoderKrishna PremPas encore d'évaluation

- CS 102 Lab 1Document18 pagesCS 102 Lab 1Abdulaziz Altararwah0% (1)

- Software Design For Low PowerDocument20 pagesSoftware Design For Low PowerGokul B S MandyaPas encore d'évaluation

- Hardware Software Codesign Question PaperDocument2 pagesHardware Software Codesign Question PaperRaviPas encore d'évaluation

- CS 212 Object Oriented Programming LabDocument7 pagesCS 212 Object Oriented Programming LabEisha FatimaPas encore d'évaluation

- CMOS Inverter Characteristics and DC AnalysisDocument8 pagesCMOS Inverter Characteristics and DC AnalysisShambhavi SonuPas encore d'évaluation

- Short Question Answers Computer ScienceDocument5 pagesShort Question Answers Computer ScienceAnonymous sCZxIO100% (2)

- Lecture 8 - Circuits Design Issues and Layout FormationDocument18 pagesLecture 8 - Circuits Design Issues and Layout FormationevildoctorbluetoothPas encore d'évaluation

- HSPICE Quick ManualDocument4 pagesHSPICE Quick ManualSurila GuglaniPas encore d'évaluation

- MODULE 4: 8051 Serial Port Programming in Assembly and C: Microcontroller Notes:18EE52Document51 pagesMODULE 4: 8051 Serial Port Programming in Assembly and C: Microcontroller Notes:18EE52SuprithaPas encore d'évaluation

- Chapter02 - Logic Design With MOSFETsDocument51 pagesChapter02 - Logic Design With MOSFETsbal3xPas encore d'évaluation

- In Put Out Put OrganizationDocument45 pagesIn Put Out Put OrganizationdevibalaPas encore d'évaluation

- Lab ViewDocument39 pagesLab ViewKlodian PerhatiPas encore d'évaluation

- Mos Transistor TheoryDocument144 pagesMos Transistor TheorymailtolokiPas encore d'évaluation

- CCS TivaWareDocument26 pagesCCS TivaWareJoginder YadavPas encore d'évaluation

- Tanner ManualDocument44 pagesTanner ManualRami ReddyPas encore d'évaluation

- VLSI LAB Tutorials TannerEDADocument45 pagesVLSI LAB Tutorials TannerEDARajesh NelavalaPas encore d'évaluation

- Transmission Line Theory: Dr. Ray KwokDocument42 pagesTransmission Line Theory: Dr. Ray KwokOCZulfikar BariklanaPas encore d'évaluation

- EE219 - Tutorial (5) - Fall 2012Document7 pagesEE219 - Tutorial (5) - Fall 2012Amera AdilPas encore d'évaluation

- Is Placed in Series With The Input Voltage Source in Fig. 4.2. Determine V /VDocument16 pagesIs Placed in Series With The Input Voltage Source in Fig. 4.2. Determine V /Vleelee leePas encore d'évaluation

- Balun Converts Electrical Signals Between Balanced and UnbalancedDocument11 pagesBalun Converts Electrical Signals Between Balanced and UnbalancedtwinspikaPas encore d'évaluation

- Chapter 15 Power Suplies (Voltage Regulators)Document110 pagesChapter 15 Power Suplies (Voltage Regulators)Jasmine TenPas encore d'évaluation

- DD Practicals Master ManualDocument58 pagesDD Practicals Master Manualraghu_chandra_3Pas encore d'évaluation

- La1836 PDFDocument13 pagesLa1836 PDFUsarioerPas encore d'évaluation

- Experiment No - 14Document8 pagesExperiment No - 14Konem SolutionsPas encore d'évaluation

- Chapter 3 - Methods of AnalysisDocument18 pagesChapter 3 - Methods of AnalysisSarah AzlinaPas encore d'évaluation

- Lab Manual ADE FinalDocument39 pagesLab Manual ADE FinalNithiyaPas encore d'évaluation

- Feedback Amplifiers PDFDocument2 pagesFeedback Amplifiers PDFMariaPas encore d'évaluation

- Field Effect Transistors: Dr. Naser Qamhieh UAEU / Department of Physics 1Document8 pagesField Effect Transistors: Dr. Naser Qamhieh UAEU / Department of Physics 1AyeshaPas encore d'évaluation

- Capacitors 2: Answer: ExplanationDocument12 pagesCapacitors 2: Answer: ExplanationVia Marie MesaPas encore d'évaluation

- DSD Project Name Abstract Quiz DisplayDocument2 pagesDSD Project Name Abstract Quiz DisplayNaveen KumarPas encore d'évaluation

- Fun Circuit Experiments With Light and Soundsrev2Document43 pagesFun Circuit Experiments With Light and Soundsrev2vjeran bachPas encore d'évaluation

- ZVS and ZCS Resonant ConverterDocument79 pagesZVS and ZCS Resonant ConverterKaumilPas encore d'évaluation

- Theory:: Experiment No. 6 Implementation of Full Adder and Full Subtractor Using Logic Gates ObjectiveDocument8 pagesTheory:: Experiment No. 6 Implementation of Full Adder and Full Subtractor Using Logic Gates ObjectiveMusic LifePas encore d'évaluation

- Electric 4rdDocument26 pagesElectric 4rdMohammed ElmadaniPas encore d'évaluation

- BritanniaDocument1 pageBritanniaVina PropertyPas encore d'évaluation

- CAD VLSI Design Course ExcerptsDocument18 pagesCAD VLSI Design Course ExcerptsThi NguyenPas encore d'évaluation

- Opamp Ac CharacteristicsDocument14 pagesOpamp Ac Characteristicsssmanohar50% (2)

- Error Amplifier Ics (Se Series)Document1 pageError Amplifier Ics (Se Series)klaus allowsPas encore d'évaluation

- DL 1002Document2 pagesDL 1002Gagan SLPas encore d'évaluation

- Verilog Tutorial - Two Phase Clocking Guide: Lukasz StrozekDocument6 pagesVerilog Tutorial - Two Phase Clocking Guide: Lukasz StrozekMilen MilenovPas encore d'évaluation

- Open House PresentationDocument18 pagesOpen House PresentationArsalan AhmedPas encore d'évaluation

- Opamp Written NotesDocument24 pagesOpamp Written Notesyashwanth h nPas encore d'évaluation

- UCi BME 140 ReviewDocument20 pagesUCi BME 140 ReviewlandyachtdrvrPas encore d'évaluation

- TCB-1100 Circuit Description GuideDocument42 pagesTCB-1100 Circuit Description Guideyo8rzePas encore d'évaluation

- Design an Instrumentation AmplifierDocument4 pagesDesign an Instrumentation AmplifierArun RajeshPas encore d'évaluation

- NMOS PLAsDocument2 pagesNMOS PLAsFLOWERPas encore d'évaluation