Académique Documents

Professionnel Documents

Culture Documents

Verilog

Transféré par

Reggie Fresco AguilarDescription originale:

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

Verilog

Transféré par

Reggie Fresco AguilarDroits d'auteur :

Formats disponibles

FROM: Gekas G DATE: Jun.

19, 2004 10:17 am gmt SUBJECT: Verilog Vga controller problem Hi, I am a new in HDL synthesis and programming of programmable devices. Currently I am working on a mouse project and I have problems with my vga_controller module. Despite the fact that in Modelsim simulation everything works as needed, when I program a Xilinx 4010XL device, nothing works as it should. The module that I test is a simple vga controller that generates 2 pulses h_sync and v_sync so as the display works in 640*400 resolution @60Hz. I also have 6 bits for the colours (rgb). In modelsim everything works perfect but in the real thing, the screen doesn't receive any signal or the signals (h_sync and v_sync) are unsynchronized. Below I provide my Verilog code, so whoever has a bit of free time, please take a look at it. Note that the design must run at 25Mhz. //Here is the module. The job that I want this to do is create a totally //black screen with a //white cursor (32*32 pixels) drawn on the upper left //corner of the screen (co ordinates (0, 0)). module vga_controller(clk, reset, h_sync, v_sync, rgb); input clk, reset; output h_sync, v_sync; output [5:0] rgb; wire [9:0] h_counter; wire [8:0] v_counter; reg h_sync, v_sync; reg [5:0] rgb; reg [9:0] x_pos; reg [8:0] y_pos; parameter h_counter_start_value = 10'd751; parameter v_counter_start_value = 9'd413; parameter zero = 4'b000; parameter low = 1'b0; wire [9:0] up_bound_x; wire [8:0] up_bound_y; wire row_fin, h_sync_low, v_sync_high; wire rgb_wire; //The ports of the below modules are described as this //counter_X(set (synchronous), reset (asynchronous), clock, data_in, chip_enable , output_count) counter_10 inst0(h_counter == 10'd800, reset, clk, h_counter_start_value, !reset , h_counter); counter_9 inst1(v_counter == 9'd449, reset, clk, v_counter_start_value, row_fin, v_counter); assign row_fin = (h_counter == 10'd751); //End of one line of pixels assign h_sync_low = (h_counter > 10'd654 & h_counter < 10'd751) ? 1'b0 : 1'b1; assign v_sync_high = (v_counter > 9'd410 & v_counter < 9'd413) ? 1'b1 : 1'b0; //Upper bounds of coordinations in the screen assign up_bound_x = {x_pos[9:5] + 1, x_pos[4:0]}; assign up_bound_y = {y_pos[8:5] + 1, y_pos[4:0]}; assign rgb_wire = (h_counter < up_bound_x & h_counter >= x_pos & v_counter < up_bound_y & v_counter >= y_pos ) ? 1 : 0; always @(posedge reset or posedge clk) if(reset) begin rgb <= 6'b000000; h_sync <= 0; v_sync <= 1;

x_pos <= 0; y_pos <= 0; end else begin h_sync <= h_sync_low; if(row_fin) v_sync <= v_sync_high; if(rgb_wire) rgb <= 6'b111111; else rgb <= 6'b000000; end endmodule

Vous aimerez peut-être aussi

- Lab 6Document13 pagesLab 6Ashok kumarPas encore d'évaluation

- Vga Display VHDLDocument43 pagesVga Display VHDLManuel Garay GutierrezPas encore d'évaluation

- VLSI LAB Record WorkDocument38 pagesVLSI LAB Record WorkJayanth KumarPas encore d'évaluation

- Lab3 VGADocument10 pagesLab3 VGAAshok kumarPas encore d'évaluation

- Ee529 Asg2Document16 pagesEe529 Asg2dd23015Pas encore d'évaluation

- Verilog CodeDocument85 pagesVerilog Codeappuamreddy75% (8)

- Lab 2 - Uso de Display 7 Segmentos en Arduino. Entradas AnalogicasDocument27 pagesLab 2 - Uso de Display 7 Segmentos en Arduino. Entradas Analogicasroger david pimienta barrosPas encore d'évaluation

- Basic Verilog Programs FileDocument33 pagesBasic Verilog Programs FileDaniel Anderson72% (18)

- H.D.L - Lab: For IV Semester B.EDocument76 pagesH.D.L - Lab: For IV Semester B.EvijaykannamallaPas encore d'évaluation

- Lab 21Document12 pagesLab 21mithila_aloPas encore d'évaluation

- Beginning FPGA Programming - Partie39Document5 pagesBeginning FPGA Programming - Partie39ali alilouPas encore d'évaluation

- Lpc213xx and Nokia7110Document17 pagesLpc213xx and Nokia7110hypernuclidePas encore d'évaluation

- Computer Graphics Lab Day-1: HereDocument7 pagesComputer Graphics Lab Day-1: HereIhsan baustPas encore d'évaluation

- Fa19 Eee 025 (DSD Lab05)Document11 pagesFa19 Eee 025 (DSD Lab05)tslfmn083Pas encore d'évaluation

- Ece574 2015 Light Sensor VGA ProjectDocument4 pagesEce574 2015 Light Sensor VGA Projectmanik9000Pas encore d'évaluation

- CaseDocument25 pagesCaseDeepanshu Midha5140Pas encore d'évaluation

- Ecad and Vlsi Lab ManualDocument125 pagesEcad and Vlsi Lab Manualsameer7mohammadPas encore d'évaluation

- Important Information Verilog EE271Document9 pagesImportant Information Verilog EE271Jogi HarshPas encore d'évaluation

- Basys3 InterfacesDocument85 pagesBasys3 InterfacesSanjeev sharmaPas encore d'évaluation

- Lab 07Document10 pagesLab 07api-241454978Pas encore d'évaluation

- Lecture2 CuongDocument51 pagesLecture2 Cuongsongoku711Pas encore d'évaluation

- 05 Laboratory Exercise 5full-PermissionDocument10 pages05 Laboratory Exercise 5full-PermissionDomsPas encore d'évaluation

- List of Lab Exercises For VHDL LabDocument3 pagesList of Lab Exercises For VHDL LabDivyanshu ShekharPas encore d'évaluation

- Top-Down Design and Synthesis Issues For Sequential Processes (That's Two Tips!)Document9 pagesTop-Down Design and Synthesis Issues For Sequential Processes (That's Two Tips!)chunnumunnuPas encore d'évaluation

- Lab 6 Verilog Data FlowDocument13 pagesLab 6 Verilog Data FlowUsama Javid MughalPas encore d'évaluation

- HW/SW Co-Design For Soc With Vivado HLS: Example 6-1 Serial AdditionDocument9 pagesHW/SW Co-Design For Soc With Vivado HLS: Example 6-1 Serial AdditionHamdan AbdellatefPas encore d'évaluation

- ECE448 Lecture7 VGA 1Document66 pagesECE448 Lecture7 VGA 1Mendbayar MbPas encore d'évaluation

- Log inDocument12 pagesLog inrahulhaldankarPas encore d'évaluation

- Lab 3Document6 pagesLab 3anonymous bunnyPas encore d'évaluation

- CSO FileDocument47 pagesCSO FileHimanshu GautamPas encore d'évaluation

- VHDL Lab ProgramsDocument51 pagesVHDL Lab ProgramsvenkiPas encore d'évaluation

- Projects With Microcontrollers And PICCD'EverandProjects With Microcontrollers And PICCÉvaluation : 5 sur 5 étoiles5/5 (1)

- FPGA ReportDocument4 pagesFPGA Reportprasad357Pas encore d'évaluation

- JakirDocument7 pagesJakirEmtiaz ShemantoPas encore d'évaluation

- UTFTDocument8 pagesUTFTJose Ramon Juan EscribanoPas encore d'évaluation

- Arduino Syntax PDFDocument6 pagesArduino Syntax PDFMarco AntonioPas encore d'évaluation

- Exp 4Document7 pagesExp 4PravinPas encore d'évaluation

- VHDL Coding Tips and TricksDocument209 pagesVHDL Coding Tips and TricksvinutaPas encore d'évaluation

- Multiplication of 2 NoDocument4 pagesMultiplication of 2 NosridharparthipanPas encore d'évaluation

- Vga Ping Pong GameDocument53 pagesVga Ping Pong Gamegaurav311086100% (2)

- ES FinalDocument26 pagesES FinalBilal AhmedPas encore d'évaluation

- Arduino Starter Kit PDFDocument58 pagesArduino Starter Kit PDFpolikarpaPas encore d'évaluation

- Arduino Course Final Exam Time: 45 Min: Choose The Best Answer For Each QuestionDocument6 pagesArduino Course Final Exam Time: 45 Min: Choose The Best Answer For Each QuestionalanPas encore d'évaluation

- Toaz - Info Arduino Course Final Exam PRDocument6 pagesToaz - Info Arduino Course Final Exam PRmontassar limemPas encore d'évaluation

- Toaz - Info Arduino Course Final Exam PRDocument6 pagesToaz - Info Arduino Course Final Exam PRmontassar limemPas encore d'évaluation

- HD44780 CommandsDocument3 pagesHD44780 CommandsPhani ChakravarthiPas encore d'évaluation

- DSD Lab Manuals: Design and Implementation of Multiplier in FpgaDocument5 pagesDSD Lab Manuals: Design and Implementation of Multiplier in FpgaAL RIZWANPas encore d'évaluation

- Beginning FPGA Programming - Partie76Document5 pagesBeginning FPGA Programming - Partie76ali alilouPas encore d'évaluation

- DSD PPT Usr and CN and Odd DividerDocument22 pagesDSD PPT Usr and CN and Odd Dividerece19637ec003Pas encore d'évaluation

- Arduino Thermometer With 7-Segment LEDDocument26 pagesArduino Thermometer With 7-Segment LEDRohit AdnaikPas encore d'évaluation

- Arduino-TempHumidity-with-LCD-And-Web-Interface ALLSTEPSDocument12 pagesArduino-TempHumidity-with-LCD-And-Web-Interface ALLSTEPSKurniawan SusiloPas encore d'évaluation

- Chapter 10 Arithmetic Ckts Presentation.VDocument109 pagesChapter 10 Arithmetic Ckts Presentation.VsirishaPas encore d'évaluation

- Cordic-Based Sine Computer (MyHDL) PDFDocument10 pagesCordic-Based Sine Computer (MyHDL) PDFredbookmanPas encore d'évaluation

- VLSI Lab Manual Exercise ProblemsDocument38 pagesVLSI Lab Manual Exercise ProblemsPrakhar Kumar100% (1)

- Interfacing LCD With Atmega32 Microcontroller Using Atmel StudioDocument5 pagesInterfacing LCD With Atmega32 Microcontroller Using Atmel StudioAbdulPas encore d'évaluation

- Vlsi RecordDocument54 pagesVlsi Record21311a04j5Pas encore d'évaluation

- Lab 7Document2 pagesLab 7anon-101637100% (2)

- CISCO PACKET TRACER LABS: Best practice of configuring or troubleshooting NetworkD'EverandCISCO PACKET TRACER LABS: Best practice of configuring or troubleshooting NetworkPas encore d'évaluation

- C Programming for the Pc the Mac and the Arduino Microcontroller SystemD'EverandC Programming for the Pc the Mac and the Arduino Microcontroller SystemPas encore d'évaluation

- Enhance Your Jump Rope Workout RoutineDocument8 pagesEnhance Your Jump Rope Workout Routinetigerlo75Pas encore d'évaluation

- Faction Misty MountainsDocument1 pageFaction Misty MountainsStormJaegerPas encore d'évaluation

- Taf Ias Academy Perambalur BranchDocument5 pagesTaf Ias Academy Perambalur BranchTAF PERAMBALURPas encore d'évaluation

- 2011 Book Sales by NielsenDocument34 pages2011 Book Sales by NielsencchansereiyutPas encore d'évaluation

- Naruto Shippuden Naruto Vs (1) - Sasuke - NDS PDFDocument1 pageNaruto Shippuden Naruto Vs (1) - Sasuke - NDS PDFMustapha ElamraniPas encore d'évaluation

- SQL Queries For PracticeDocument2 pagesSQL Queries For Practicerboy1993Pas encore d'évaluation

- William McElcheran: Paper To Bronze May 4-31 Online Exhibition CatalogueDocument19 pagesWilliam McElcheran: Paper To Bronze May 4-31 Online Exhibition CatalogueKinsman Robinson GalleriesPas encore d'évaluation

- Brad Duban ResumeDocument1 pageBrad Duban ResumeBradDubanPas encore d'évaluation

- Blogging and VloggingDocument4 pagesBlogging and VloggingJerome Metierre0% (1)

- Comcast-Chat 7-28Document10 pagesComcast-Chat 7-28GIMMY67Pas encore d'évaluation

- 50 Winners - May 3rdDocument2 pages50 Winners - May 3rdMaloPas encore d'évaluation

- Gothic 2 Noc Kruka Returning Poradnik ChomikujDocument2 pagesGothic 2 Noc Kruka Returning Poradnik ChomikujStevePas encore d'évaluation

- How To Write An EmailDocument2 pagesHow To Write An Emaillimi4Pas encore d'évaluation

- SQL Database Developer Resume SampleDocument2 pagesSQL Database Developer Resume SampleBranZzZzZPas encore d'évaluation

- How To Compile Avl On Windows Using MinGW Without X 11 LibraryDocument2 pagesHow To Compile Avl On Windows Using MinGW Without X 11 LibraryPaul Pipi OkonkwoPas encore d'évaluation

- Nfs MW RulesDocument3 pagesNfs MW RulesRania AhmedPas encore d'évaluation

- Learn Dutch Phone AlphabetDocument2 pagesLearn Dutch Phone AlphabetNadim TareqPas encore d'évaluation

- Tugas 2 Bahasa InggrisDocument3 pagesTugas 2 Bahasa InggrisWanPas encore d'évaluation

- Social Media Package RatesDocument2 pagesSocial Media Package RatesHighly RelevantPas encore d'évaluation

- Cinna DockDocument2 pagesCinna DockPradeep KrPas encore d'évaluation

- Web Page Maker Complete Urdu Tutorial by Murad KhanDocument6 pagesWeb Page Maker Complete Urdu Tutorial by Murad KhanMURAD_KHANPas encore d'évaluation

- Wasting Time On The InternetDocument2 pagesWasting Time On The InternetJose Antonio MartinezPas encore d'évaluation

- Taarak MehtaDocument1 pageTaarak MehtaKneerdipPas encore d'évaluation

- Language Learning Links v3 3Document67 pagesLanguage Learning Links v3 3api-27502770950% (2)

- Time Paradox Sans - YouTubeDocument1 pageTime Paradox Sans - YouTubeKaden ReidPas encore d'évaluation

- How To Secure A Media Sponsor For Your Events.ADocument4 pagesHow To Secure A Media Sponsor For Your Events.ApandalocalPas encore d'évaluation

- Bromothymol BlueDocument3 pagesBromothymol Bluenike1312Pas encore d'évaluation

- Forums-Installation Helps Common ErrorsDocument2 pagesForums-Installation Helps Common Errorsshahali01Pas encore d'évaluation

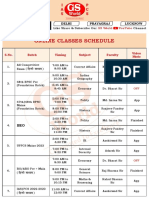

- 27 Oct 2022 GS WORLD CLASSES SCHEDULE-1Document3 pages27 Oct 2022 GS WORLD CLASSES SCHEDULE-1Tigers SarafPas encore d'évaluation

- Resume (Trey Williams)Document1 pageResume (Trey Williams)Trey-Ceaser Moyce Williams IIIPas encore d'évaluation