Académique Documents

Professionnel Documents

Culture Documents

Microelectronic Devices and Circuits-EECS105 Final Exam

Transféré par

Hamed GhanbariDescription originale:

Titre original

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

Microelectronic Devices and Circuits-EECS105 Final Exam

Transféré par

Hamed GhanbariDroits d'auteur :

Formats disponibles

EECS105

1 of 13

Fall 2000

Microelectronic Devices and Circuits- EECS105 Final Exam

Wednesday, December 13, 2000

Costas J. Spanos University of California at Berkeley College of Engineering Department of Electrical Engineering and Computer Sciences

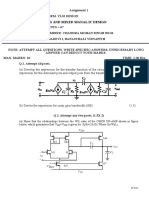

Your Name: ____________________________________________ (last) (first) Your Signature: __________________________________________ 1. Print and sign your name on this page before you start. 2. You are allowed three, 8.5x11 handwritten sheets. No books or notes! 3. Do everything on this exam, and make your methods as clear as possible. Problem 1 ________ / 24 Problem 2 ________ / 26 Problem 3 ________ / 26 Problem 4 ________ / 24 TOTAL _________ / 100 MOS Device Data (you may not have to use all of these...) n Cox = 50 A/V 2, pC ox = 25 A/V2, V Tn = -V Tp = 1V, Lmin = 2m. VBS = 0. n = p = 0.1V 1 when L = 1m, and it is otherwise proportional to 1/L Cox = 2.3fF/ m2 , Cjn = 0.1fF/m 2, C jp = 0.3fF/ m2 , Cjswn = 0.5fF/ m, Cjswp = 0.35fF/m, Covn = 0.5fF/m, Covp = 0.5fF/ m

EECS105

2 of 13

Fall 2000

Problem 1 of 4: Answer each question briefly and clearly. (4 points each, total 24)

Why are bipolar transistors capable of providing more drive current compared to MOS transistors that occupy similar area? (give a qualitative answer)

Comparing a Common Collector to a Common Drain voltage buffer amplifier, one sees some advantages and disadvantages. Place a mark below to indicate your choice, trying to get the largest DC voltage gain.

Aspect Rin Rout Av

CC

CD

In the IC industry layout designers can manipulate lateral device dimensions (L, W, area of baseemitter junction, etc.) while process designers manipulate vertical dimensions (Tox, base-width) and doping levels. List a parameter that each designer can change to affect the respective parameter, or write none if the designer cannot affect the value of the respective parameter: Parameter VTn ro (NMOS) gm (NMOS) ro (npn) gm (npn) Cgs Layout Designer Process Designer

EECS105

3 of 13

Fall 2000

What advantage(s) does a cascode configuration has over a cascade configuration?

Which conditions must be satisfied so that the open circuit time constant method leads to an exact solution?

In your own words, how does the dreaded Miller effect limit frequency response of a high voltage gain amplifier?

EECS105

4 of 13

Fall 2000

Problem 2 of 4 (26 points)

Consider the following cascode amplifier, driven by a perfect current source (r oc= ) For each of the following questions, make sure that you show the expressions before you plug in the specific values. A correct expression is worth 70% of the credit, even if the numerical calculation is incorrect!

a) Find (W/L)1 ratio so that the overall Gm of this amp is 1mS. (Do not specify values for W and for L here. That comes later). (5 points)

Expression for (W/L)1 (W/L) 1=

Value

EECS105

5 of 13

Fall 2000

b) Assume that gm2=gm1, and ro2 = ro1 . Find the value of L1 so that ro1 = 200k, and calculate the respective value of the overall Rout of this amplifier. (5 points)

Expression for L1 L1 =

Value

Expression for Rout Rout =

Value

EECS105

6 of 13

Fall 2000

c) Find the open circuit voltage gain of this two stage amplifier (roc= ). (5 points)

Expression for Voltage Gain vout/vin =

Value

in db

d) Calculate VBIAS (ignoring channel-length modulation). Assume that (W/L)1 = (W/L)2 = 16 (note that this is not the correct answer to question 2.a) (5 points)

Expression for VBIAS VBIAS =

Value

EECS105

7 of 13

Fall 2000

e) Assuming that (W/L) 2 = 16, find the value for VG2 that will give you the maximum voltage swing for this amp. Explain your thinking in one sentence (ignore channel length modulation). (6 points)

What limits Vout min?

Expression for VG2 VG2 =

Value

EECS105

8 of 13

Fall 2000

Problem 3/4 (26 points)

Consider the following pnp CE amplifier. Note that o = 50, IS= 10-17 A and VA = infinity. (Be very careful with signs in this problem!). For each of the following questions, make sure that you show the expressions before you plug in the specific values. A correct expression is worth 70% of the credit, even if the numerical calculation is incorrect!

a) Calculate VBIAS so that Vout = 2.5V. Ignore I B and Rs for this question. (Do NOT assume that VBE is exactly -0.7V). (5 points)

Expression for VBIAS VBIAS=

Value

EECS105

9 of 13

Fall 2000

b) Find Rout and the voltage gain, if R L = infinity. (8 points)

Expression for Rout Rout =

Value

Expression for Voltage Gain vout/vin =

Value

c) Calculate the value of R L that will cut the gain by a factor of two. (Assume that R L is connected through a small coupling capacitor, so that it does not disrupt the biasing of the transistor.) (5 points)

Expression for RL that cuts the gain by a factor of 2. RL =

Value

EECS105

10 of 13

Fall 2000

d) If you could increase o, how much would you have to increase it in order to increase the gain by 10%. (Hint: assume that the new, improved o = Xo, and write an expression that you can use to calculate the value of the factor X). (8 points)

Expression for X (multiplier for increasing o.) X=

Value

EECS105

11 of 13

Fall 2000

Problem 4/4 (24 points)

The following is a cascade of three 2-ports: a transconductance amplifier, a current buffer and a voltage buffer. The aim of this circuit is to produce lots of voltage gain over a wide bandwidth. .

a) Find the low frequency voltage gain vout/vin. (this means that you can ignore all the capacitors). Do this in stages as shown in the table below: (6 points)

Expression v2/vs = v3/v2 = vout/v3 = vout/vs =

Value

EECS105

12 of 13

Fall 2000

b) Replace all cross-over caps C1, C2 , C3, with their Miller equivalent CM1 , CM2 , CM3 . (6 points)

Expression CM1 = CM2 = CM3 = c) Calculate the Open Circuit Time Constant for the nodes 1, 2, 3 and 4. (6 points)

Value

Expression RT1 = RT2= RT3= RT4= Total

RC RC1 = RC2 = RC3 = RC4 =

Value

EECS105 d) Calculate the 3db of this amp (6 points)

13 of 13

Fall 2000

Expression for 3db. 3db =

Value

~ Thats All Folks! ~

Vous aimerez peut-être aussi

- Cascode AmplifierDocument6 pagesCascode AmplifierRajesh NatarajanPas encore d'évaluation

- Ee414 The4Document1 pageEe414 The4Asif SiddiquePas encore d'évaluation

- Aicd Exam SolutionDocument16 pagesAicd Exam SolutionTenzin ChoendenPas encore d'évaluation

- HW 3Document5 pagesHW 3BrimwoodboyPas encore d'évaluation

- 6.012 Electronic Devices and Circuits: Final ExaminationDocument13 pages6.012 Electronic Devices and Circuits: Final ExaminationhelpsatyaPas encore d'évaluation

- Exam SolutionsDocument7 pagesExam SolutionsfaisalphyPas encore d'évaluation

- 6002x FinalReview S2012 CleanDocument80 pages6002x FinalReview S2012 CleanGemini GntPas encore d'évaluation

- MIT6 012S09 Ex03 Final 07Document18 pagesMIT6 012S09 Ex03 Final 07Gopi KrishnaPas encore d'évaluation

- Design & Testing of A RC Coupled Single Stage BJT AmplifierDocument6 pagesDesign & Testing of A RC Coupled Single Stage BJT AmplifierAaron GonsalvesPas encore d'évaluation

- Two StageDocument6 pagesTwo StageSiphosethuSidloyiPas encore d'évaluation

- Problem Solving With MATLAB: CPET 190Document19 pagesProblem Solving With MATLAB: CPET 190Zan LaylePas encore d'évaluation

- Birla Institute of Technology and Science Pilani, Pilani Campus (Raj.)Document3 pagesBirla Institute of Technology and Science Pilani, Pilani Campus (Raj.)Arihant JainPas encore d'évaluation

- E3-238: Analog VLSI Circuits Lab 2: InstructionsDocument4 pagesE3-238: Analog VLSI Circuits Lab 2: InstructionsR SHARMAPas encore d'évaluation

- AEC LabManualDocument30 pagesAEC LabManualPrateek PaliwalPas encore d'évaluation

- AD 20flash 20converterDocument7 pagesAD 20flash 20converterChú Cá ConPas encore d'évaluation

- Power System Analysis and Design 6th Edition Glover Test BankDocument14 pagesPower System Analysis and Design 6th Edition Glover Test BankMatthewGreenefgjtb100% (22)

- Midterm 2 Exam: Y-Parameters of The Amplifier With Feedback in (Ii) - You Must Show Your Work. (3 Points)Document9 pagesMidterm 2 Exam: Y-Parameters of The Amplifier With Feedback in (Ii) - You Must Show Your Work. (3 Points)Shubhresh Kumar JhaPas encore d'évaluation

- Lab1 Ee140 s13 v1Document6 pagesLab1 Ee140 s13 v1Mohd YasirPas encore d'évaluation

- Elec Eng 2ei5 Microelectronic Devices and Circuits I Winter 2013 Final Exam - 4/22/13Document7 pagesElec Eng 2ei5 Microelectronic Devices and Circuits I Winter 2013 Final Exam - 4/22/13SonDinhQuangPas encore d'évaluation

- Eecs311 Lab06 PDFDocument28 pagesEecs311 Lab06 PDFGwenShepherdPas encore d'évaluation

- University of Edinburgh College of Science and Engineering School of Engineering and ElectronicsDocument15 pagesUniversity of Edinburgh College of Science and Engineering School of Engineering and ElectronicsSyed Fasih Ur RehmanPas encore d'évaluation

- Final Exam 2002Document12 pagesFinal Exam 2002Stephanie MurphyPas encore d'évaluation

- EE3408E Project Design A Two-Stage Operational AmplifierDocument4 pagesEE3408E Project Design A Two-Stage Operational AmplifierLaSo ASPas encore d'évaluation

- Design Opamp Summer CircuitDocument9 pagesDesign Opamp Summer CircuitA RPas encore d'évaluation

- Solns 2cmosDocument18 pagesSolns 2cmosramprakash_rampelliPas encore d'évaluation

- Digital Measurement Techniques-EIC703Document3 pagesDigital Measurement Techniques-EIC703sitaram_1Pas encore d'évaluation

- Experiment 1Document5 pagesExperiment 1Abdul Basir SahebzadehPas encore d'évaluation

- Experiment 3Document5 pagesExperiment 3Qurat AinniPas encore d'évaluation

- Sample 1Document8 pagesSample 1nradhy2725Pas encore d'évaluation

- Lecture13 BJT Transistor Circuit AnalysisDocument24 pagesLecture13 BJT Transistor Circuit Analysisazur33nPas encore d'évaluation

- Adc Lab Manual PDFDocument74 pagesAdc Lab Manual PDFJega Deesan75% (4)

- Subject: Analog and Mixed Signal Ic DesignDocument2 pagesSubject: Analog and Mixed Signal Ic DesignchandravinitaPas encore d'évaluation

- Final Exam 2020Document9 pagesFinal Exam 2020侯蕴书Pas encore d'évaluation

- Sharmi ECE a-D-Circuits Lab ManualDocument74 pagesSharmi ECE a-D-Circuits Lab ManualSharmila83Pas encore d'évaluation

- EE5310/EE3002: Analog Circuits Tutorial 1 Problems 6, 8, 10, 11 Are OptionalDocument10 pagesEE5310/EE3002: Analog Circuits Tutorial 1 Problems 6, 8, 10, 11 Are Optionaldummy1957jPas encore d'évaluation

- LT SpiceDocument6 pagesLT SpiceVijay Preetham100% (1)

- Lab 2: Frequency and Time Response of Second Order Systems, Week of October 10, 2011Document9 pagesLab 2: Frequency and Time Response of Second Order Systems, Week of October 10, 2011Carlos ReyesPas encore d'évaluation

- Function GeneratorDocument13 pagesFunction GeneratorDilJalaayPas encore d'évaluation

- HomeworkDocument4 pagesHomework1dmsrufPas encore d'évaluation

- A Be Midterm Spring KeyDocument11 pagesA Be Midterm Spring KeyRex ChemPas encore d'évaluation

- Last Modified On September 3, 2004 by Stanley Wang and Henry JenDocument3 pagesLast Modified On September 3, 2004 by Stanley Wang and Henry JenThomas GeorgePas encore d'évaluation

- Design Project: (Due: Friday, December 8, 2006, 5pm PT)Document6 pagesDesign Project: (Due: Friday, December 8, 2006, 5pm PT)Ibrahim MuhammedPas encore d'évaluation

- Lab10 2011Document5 pagesLab10 2011Venkat RamananPas encore d'évaluation

- Ee141 HW5 2Document3 pagesEe141 HW5 2Vidhya DsPas encore d'évaluation

- Name: - Student IDDocument10 pagesName: - Student IDMete SakallıPas encore d'évaluation

- Midterm 07Document10 pagesMidterm 07ubertomePas encore d'évaluation

- EE477L HW1 Sp24Document4 pagesEE477L HW1 Sp24Archit SethiPas encore d'évaluation

- Midterm1 SolutionDocument7 pagesMidterm1 SolutionSova ŽalosnaPas encore d'évaluation

- Ee311 Homework4 2012 PDFDocument1 pageEe311 Homework4 2012 PDFtechaddicttPas encore d'évaluation

- Introduction To Logic Design Experiments 1 Thru 10Document36 pagesIntroduction To Logic Design Experiments 1 Thru 10George Kokkinias100% (1)

- ME862VI-SampleMidSemQuestions 01Document4 pagesME862VI-SampleMidSemQuestions 01Manoj S KPas encore d'évaluation

- Electric Circuit Exam INIESATDocument2 pagesElectric Circuit Exam INIESATMBIEDA NGOMEGNI FRANK GAETANPas encore d'évaluation

- EE 330 Exam 2 Spring 2015 PDFDocument10 pagesEE 330 Exam 2 Spring 2015 PDFeng2011techPas encore d'évaluation

- Lab 1: Multi-Stage Amplifiers: Philippine Institute For Integrated CircuitsDocument3 pagesLab 1: Multi-Stage Amplifiers: Philippine Institute For Integrated CircuitsIdk RebollosPas encore d'évaluation

- Lab#2 OpAmps 110420 V7Document4 pagesLab#2 OpAmps 110420 V7FrenkiPas encore d'évaluation

- ECD Lab 2 PDFDocument12 pagesECD Lab 2 PDFMaryam MahmoodPas encore d'évaluation

- Power Amplifiers Part 1 Class A: We Have Studied The Design of Small-Signal AmplifiersDocument18 pagesPower Amplifiers Part 1 Class A: We Have Studied The Design of Small-Signal AmplifiersmalamigsajpanPas encore d'évaluation

- Electronics 3 Checkbook: The Checkbooks SeriesD'EverandElectronics 3 Checkbook: The Checkbooks SeriesÉvaluation : 5 sur 5 étoiles5/5 (1)

- EpanDocument2 pagesEpanHamed GhanbariPas encore d'évaluation

- Ext VPNDocument1 pageExt VPNHamed GhanbariPas encore d'évaluation

- WWW Mut-Es Ac IrDocument1 pageWWW Mut-Es Ac IrHamed GhanbariPas encore d'évaluation

- HostDocument6 pagesHostHamed GhanbariPas encore d'évaluation

- Professional 2003 Microsoft Office Visio This File Created byDocument10 pagesProfessional 2003 Microsoft Office Visio This File Created bySasan Ahdi RezaeiehPas encore d'évaluation

- Professional 2003 Microsoft Office Visio This File Created byDocument10 pagesProfessional 2003 Microsoft Office Visio This File Created bySasan Ahdi RezaeiehPas encore d'évaluation

- ExamDocument13 pagesExamHamed GhanbariPas encore d'évaluation

- Student Guide To US UniversitiesDocument15 pagesStudent Guide To US Universitiesparth149Pas encore d'évaluation

- Microelectronic Devices and Circuits: Final ExamDocument6 pagesMicroelectronic Devices and Circuits: Final ExamHamed GhanbariPas encore d'évaluation

- ODN Planning and Design Suggestions TLFDocument52 pagesODN Planning and Design Suggestions TLFJairo Aguero MarotoPas encore d'évaluation

- Radio Frequency RemoteDocument9 pagesRadio Frequency RemoteRupesh SolankiPas encore d'évaluation

- DHI-KTP01 Datasheet 20200218 PDFDocument3 pagesDHI-KTP01 Datasheet 20200218 PDFDeltaz AZPas encore d'évaluation

- SVPWM ThesisDocument61 pagesSVPWM ThesisjyotiblossomsPas encore d'évaluation

- Monoband SDR HF Receiver DR2C-YU1LMDocument12 pagesMonoband SDR HF Receiver DR2C-YU1LMSmai HondoPas encore d'évaluation

- Panasonic 2007 LCD Models TV Service Guide PDFDocument109 pagesPanasonic 2007 LCD Models TV Service Guide PDFOakkar OrgPas encore d'évaluation

- Stabilizer Transfer Functions: Single Input Power System Stabilizer (PSS1A)Document4 pagesStabilizer Transfer Functions: Single Input Power System Stabilizer (PSS1A)Moisés JúniorPas encore d'évaluation

- Semiconductors & Communications (V) D Drive Theory and QuestionsDocument63 pagesSemiconductors & Communications (V) D Drive Theory and QuestionsAvi KedarrPas encore d'évaluation

- Arduino-Based Oscilloscope Using Mobile Device Technology and Bluetooth LEDocument74 pagesArduino-Based Oscilloscope Using Mobile Device Technology and Bluetooth LEElbert John Alejo Orozco67% (3)

- FRAX User's Manual: © 2009 Megger AB Released in 2008-12-10Document10 pagesFRAX User's Manual: © 2009 Megger AB Released in 2008-12-10ryan940100% (1)

- Thermal Printer Head ftp-642mcl001Document7 pagesThermal Printer Head ftp-642mcl001Sveto SlPas encore d'évaluation

- Bq24735 1-To 4-Cell Li+ Battery Smbus Charge Controller For Supporting Turbo Boost Mode With N-Channel Power Mosfet SelectorDocument46 pagesBq24735 1-To 4-Cell Li+ Battery Smbus Charge Controller For Supporting Turbo Boost Mode With N-Channel Power Mosfet SelectorricharPas encore d'évaluation

- Elspec 4400Document5 pagesElspec 4400vgarudaPas encore d'évaluation

- Flowserve Dataflo Digital Electronic Positioner DFP17Document32 pagesFlowserve Dataflo Digital Electronic Positioner DFP17Jose Alfredo Marinez ContrerasPas encore d'évaluation

- SMPS Telchom 2KW PDFDocument96 pagesSMPS Telchom 2KW PDFDiyon NothinglastnamePas encore d'évaluation

- Logic Families LectureDocument20 pagesLogic Families LectureHarshad LokhandePas encore d'évaluation

- Quadrature-Mirror Filter BankDocument63 pagesQuadrature-Mirror Filter BankffggPas encore d'évaluation

- RS-422 Splitter PDFDocument1 pageRS-422 Splitter PDFNisar AhmedPas encore d'évaluation

- Caddy LHN 130, 140, 200, (Caddy) PDFDocument36 pagesCaddy LHN 130, 140, 200, (Caddy) PDFPE TruPas encore d'évaluation

- Dse 74xx Mkii Data Sheet UsDocument2 pagesDse 74xx Mkii Data Sheet UsRonald Victor Galarza HermitañoPas encore d'évaluation

- Saturable ReactorDocument2 pagesSaturable ReactorGilberto ManhattanPas encore d'évaluation

- 15EC63 Module 1 04-02-2019Document45 pages15EC63 Module 1 04-02-2019garry pintoPas encore d'évaluation

- Module 4Document91 pagesModule 4mahendra naikPas encore d'évaluation

- Man Bo-01ka enDocument12 pagesMan Bo-01ka enqwkerbk090909Pas encore d'évaluation

- Very Low Frequency (VLF) Cable Testing, Recommended Test Voltages and DurationDocument2 pagesVery Low Frequency (VLF) Cable Testing, Recommended Test Voltages and DurationTommy SiddiqPas encore d'évaluation

- A194518 R0 V 01Document1 pageA194518 R0 V 01Roman Travin0% (1)

- BD Class D ModulationDocument18 pagesBD Class D ModulationDiego Cowes100% (1)

- CDMA Overview Session 2Document27 pagesCDMA Overview Session 2David JohnsPas encore d'évaluation

- Datasheet Mosfet Driver ADP3110A Dual Bootstrapped, 12 V MOSFETDocument12 pagesDatasheet Mosfet Driver ADP3110A Dual Bootstrapped, 12 V MOSFETdouglasPas encore d'évaluation

- Anyhertz Drive ShenzenDocument5 pagesAnyhertz Drive ShenzenJose EspinozaPas encore d'évaluation