Académique Documents

Professionnel Documents

Culture Documents

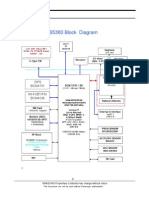

SAP-1 Simple As Possible Computer With Microcoded ROM

Transféré par

pong74lsTitre original

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

SAP-1 Simple As Possible Computer With Microcoded ROM

Transféré par

pong74lsDroits d'auteur :

Formats disponibles

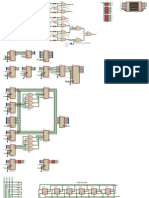

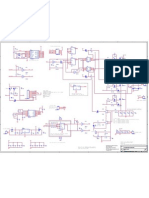

Cp Lp Ep Lm Lrm Erm Li Ei La Ea Su Eu Lb Lo HLT NOP

OP7

OP6

OP5

OP4

OP3

OP2

OP1

OP0

U1:A

VCC 1 3 2 CLR VCC ADR23 ADR22 ADR21 ADR20 D7 D6 D5 D4 D3 D2 D1 D0 W7 W6 W5 W4 W3 W2 W1 W0 CLK CLK Rcs Cp Lp Ep Lm Lrm W[0..7] A0 A1 A2 A3 A4 A5 A6 A7 B0[0..7] B1[0..7] A8 A9 A10 A11 A12 A13 A14 A15 B2[0..7] B3[0..7] Erm Li Ei La Ea Eu Lb Lo

SW4

? ? ? ? ? ? ? ? ? PC3 ? PC2 ? PC1 ? PC0 ? ? FLload ? ? I6 I5 I4 I3

Start

Clear/Start

U1:B

Clear 4 6 VCC 5 74HC00 CLR

? ? ? ? ? ? ? ?

W7 W6 W5 W4 W3 W2 W1 W0

? ? ? ?

ADR23 ADR22 ADR21 ADR20

? ? ? ?

D7 D6 D5 D4 D3 D2 D1 D0

U1:C

VCC 10 8 9 VCC OPCode / Data Switches

SW1

OFF

9 10 11 12 13 14 15 16

SW2 SW5 SW3

Write Mem SWEram Single Step Low

OFF

5 6 7 8

ON

Address Switch

ON

U1:D

High 13 11 VCC 12 HLT 74HC00 1 2 13

4 3 2 1

8 7 6 5 4 3 2 1

U3:A

12

U2:A SW7

To Program Manually: Set SW6 up to manual mode. Set SW7 down to program mode. Set SW8 up to manual mode. Set addresses and data using the DIP switches. Toggle SW3 to load the data into RAM. To Program Automatically: Set SW6 up to manual mode. Set SW7 down to program mode. Set SW8 down to automatic mode. If the simulation is not running it can be started and when the loading is complete the FLload flag will equal 1. If the simulation was already started then press SW4 to clear the counters and restart the process. The debug menu can be used to view the contents of RAM. To Execute a Program: Set SW7 and SW8 up to Run mode then set SW6 to Auto. Press clear to reset the Program Counter to zero and re-execute the program. VCC ENprog VCC 1 3 2 10 8 9 12 13 11 CLK

U2:C U2:D

CLK

SW6

VCC OEDIPSWin DIPSWin Up = Run Down = Program Manual/Auto

Manual

U2:B

Auto 4 6 VCC 5 VCC 3 4 5

U3:B

6

VCC

U4:A SW8

autoDATAin Up = Manual Data Entry, Run Down = Automatic Data Entry U4:A(CLK) INIT=LOW START=0 COUNT=-1 CLOCK=10 HLT 74HC107 1 12 4 J CLK R K Q 2 Q 3

13 CLR

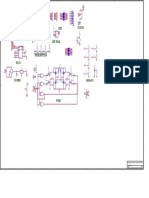

Note: The 555 timer circuit has been substituted with a virtual clock source to speed up the simulation.

U6

Ep VCC VCC Erm SELWEram 2 3 5 6 11 10 14 13 1 15 1A 1B 2A 2B 3A 3B 4A 4B A/B E 74HC157 Run/Program Selector 1Y 2Y 3Y 4Y 4 7 9 12 ENpc ENmar OEram WEram VCC CLK2 SWEram autoDATAin VCC VCC 2 3 5 6 11 10 14 13 1 15

U7

1A 1B 2A 2B 3A 3B 4A 4B A/B E 74HC157 Manual/Auto Data Input Selector 1Y 2Y 3Y 4Y 4 7 9 12 autoADRin DIPSWin ROMin SELWEram ADR10 ADR20 ADR11 ADR21 ADR12 ADR22 ADR13 ADR23 autoADRin 2 3 5 6 11 10 14 13 1 15

U8

1A 1B 2A 2B 3A 3B 4A 4B A/B E 74HC157 Address Input Selector 1Y 2Y 3Y 4Y 4 7 9 12 ADR00 ADR01 ADR02 ADR03

U5:A

CLK Lrm 1 3 2 74HC00

ENprog

U9

3 4 5 6 7 10 2 9 1 D0 D1 D2 D3 ENP ENT CLK LOAD MR 74HC161 Auto-Programmer CLR Q0 Q1 Q2 Q3 RCO 14 13 12 11 15 ADR10 ADR11 ADR12 ADR13 12 CLK2 11 D CLK R Q 74HC74 8 ADR10 ADR11 ADR12 ADR13 FLload 8 7 6 5 4 3 2 1 23 22 19 21 18 20

U11

A0 A1 A2 A3 A4 A5 A6 A7 A8 A9 A10 A11 CE OE/VPP 2732 Program ROM "Auto-Programmer" Instead of manually entering data this subcircuit will load the RAM with the first 16 bytes of the linked "Program ROM.bin" file. D0 D1 D2 D3 D4 D5 D6 D7 9 10 11 13 14 15 16 17 W0 W1 W2 W3 W4 W5 W6 W7

U10:A

Q 5 CLK2

10

U10:B

Q 9

D CLK

CLK2

Q 74HC74

CLR

CLR

U4:B

74HC107 8 U4:B(CLK) INIT=LOW START=0 COUNT=-1 CLOCK=10 9 11 J CLK R K Q 6 CLK2 Q 5 CLK2

13

ROMin

CLR

U12

W4 W5 W6 W7 CLK 14 13 12 11 7 1 2 9 10 15 D0 D1 D2 D3 CLK OE1 OE2 E1 E2 MR 74HC173 Instruction Register Q0 Q1 Q2 Q3 3 4 5 6 I3 I4 I5 I6 CLK Ei Li Rcs W0 W1 W2 W3 14 13 12 11 7 1 2 9 10 15

10

U13

D0 D1 D2 D3 CLK OE1 OE2 E1 E2 MR 74HC173 Instruction Register Q0 Q1 Q2 Q3 3 4 5 6 W0 W1 W2 W3

Li Rcs

U14

3 4 5 6 VCC VCC CLK Rcs 7 10 2 9 1 D0 D1 D2 D3 ENP ENT CLK LOAD MR 74HC161 Control Sequence Counter Q0 Q1 Q2 Q3 RCO 14 I0 13 I1 12 I2 11 15 I0 10 I1 9 I2 8 7 6 5 4 3 25 24 21 23 2 20 22 27 1

U15

A0 A1 A2 A3 A4 A5 A6 A7 A8 A9 A10 A11 A12 CE OE PGM VPP 27C64 Control ROM - High D0 D1 D2 D3 D4 D5 D6 D7 11 12 13 15 16 17 18 19 Ei Li Erm Lrm Lm Ep Lp Cp I0 10 I1 9 I2 8 7 6 5 4 3 25 24 21 23 2 20 22 27 1

U16

A0 A1 A2 A3 A4 A5 A6 A7 A8 A9 A10 A11 A12 CE OE PGM VPP 27C64 Control ROM - Low D0 D1 D2 D3 D4 D5 D6 D7 11 12 13 15 16 17 18 19 NOP HLT Lo Lb Eu Su Ea La

I3 I4 I5 I6

I3 I4 I5 I6

Rcs

U5:B

CLR NOP 4 6 5 74HC00 9 10

U5:C

VCC 8 Rcs

VCC

74HC00

U17

W0 W1 W2 W3 VCC Cp CLK Lp CLR 3 4 5 6 7 10 2 9 1 D0 D1 D2 D3 ENP ENT CLK LOAD MR 74HC161 Program Counter Q0 Q1 Q2 Q3 RCO 14 13 12 11 15 PC0 PC1 PC2 PC3 VCC ENpc 3 4 5 6 1 13

U18

A0 A1 A2 A3 OEA OEB 74HC243 Program Counter B0 B1 B2 B3 11 10 9 8 W0 W1 W2 W3 D0 D1 D2 D3 D4 D5 D6 D7 OEDIPSWin VCC 2 3 4 5 6 7 8 9 19 1

U19

A0 A1 A2 A3 A4 A5 A6 A7 CE AB/BA 74HC245 Data Input 3-State Buffer B0 B1 B2 B3 B4 B5 B6 B7 18 17 16 15 14 13 12 11 W0 W1 W2 W3 W4 W5 W6 W7

U21 U20

W0 W1 W2 W3 CLK 14 13 12 11 7 1 2 9 10 15 D0 D1 D2 D3 CLK OE1 OE2 E1 E2 MR 74HC173 Memory Address Register Q0 Q1 Q2 Q3 3 4 5 6 ADR00 ADR01 ADR02 ADR03 2 3 5 6 11 10 14 13 1 15 1A 1B 2A 2B 3A 3B 4A 4B A/B E 74HC157 Memory Address Selector 1Y 2Y 3Y 4Y 4 7 9 12 10 9 8 7 6 5 4 3 25 24 21 23 2 26 1 20 27 22

U22

A0 A1 A2 A3 A4 A5 A6 A7 A8 A9 A10 A11 A12 A13 A14 CE WE OE 62256 RAM D0 D1 D2 D3 D4 D5 D6 D7 11 12 13 15 16 17 18 19 W0 W1 W2 W3 W4 W5 W6 W7

ENmar

Lm Rcs

WEram OEram

U24

W0 W1 W2 W3 CLK 14 13 12 11 7 1 2 9 10 15 D0 D1 D2 D3 CLK OE1 OE2 E1 E2 MR 74HC173 Accumulator (LSB) Q0 Q1 Q2 Q3 3 4 5 6 5 3 14 12 6 2 15 11 7 6 5 9 Q0 Q1 Q2 Q3 3 4 5 6 Su 8 10 12 11 13 Su

U30

A0 A1 A2 A3 B0 B1 B2 B3 C0 74HC283 Full Adder C4 9 Carry S0 S1 S2 S3 4 1 13 10

1 3 2 4

La

U26

W0 W1 W2 W3 CLK 14 13 12 11 7 1 2 9 10 15 D0 D1 D2 D3 CLK OE1 OE2 E1 E2 MR 74HC173 B Register (LSB)

U28:D

74HC86

Lb

U23

W0 W1 W2 W3 W4 W5 W6 W7 2 3 4 5 6 7 8 9 19 1 A0 A1 A2 A3 A4 A5 A6 A7 CE AB/BA 74HC245 B0 B1 B2 B3 B4 B5 B6 B7 18 17 16 15 14 13 12 11 18 17 16 15 14 13 12 11

U32

B0 B1 B2 B3 B4 B5 B6 B7 A0 A1 A2 A3 A4 A5 A6 A7 CE AB/BA 74HC245 2 3 4 5 6 7 8 9 19 1 W0 W1 W2 W3 W4 W5 W6 W7

Ea

Eu

U25

W4 W5 W6 W7 CLK 14 13 12 11 7 1 2 9 10 15 D0 D1 D2 D3 CLK OE1 OE2 E1 E2 MR 74HC173 Accumulator (MSB) Q0 Q1 Q2 Q3 3 4 5 6 5 3 14 12 6 2 15 11 7 6 5 9 Q0 Q1 Q2 Q3 3 4 5 6 Su 8 10 12 11 13 Carry

U31

A0 A1 A2 A3 B0 B1 B2 B3 C0 74HC283 Full Adder C4 9 S0 S1 S2 S3 4 1 13 10

1 3 2 4

La

U27

W4 W5 W6 W7 CLK 14 13 12 11 7 1 2 9 10 15 D0 D1 D2 D3 CLK OE1 OE2 E1 E2 MR 74HC173 B Register (MSB)

U29:D

74HC86

Lb

U33

W4 W5 W6 W7 CLK 14 13 12 11 7 1 2 9 10 15 D0 D1 D2 D3 CLK OE1 OE2 E1 E2 MR 74HC173 Output Register Q0 Q1 Q2 Q3 3 4 5 6 OP4 OP5 OP6 OP7 CLK W0 W1 W2 W3 14 13 12 11 7 1 2 9 10 15

U34

D0 D1 D2 D3 CLK OE1 OE2 E1 E2 MR 74HC173 Output Register Q0 Q1 Q2 Q3 3 4 5 6 OP0 OP1 OP2 OP3

Lo CLR

Lo CLR

Vous aimerez peut-être aussi

- SAP-1 Simple As Possible Computer Schematic Diagram - Updated DesignDocument1 pageSAP-1 Simple As Possible Computer Schematic Diagram - Updated Designpong74lsPas encore d'évaluation

- SAP-1 Simple As Possible Computer Schematic DiagramDocument1 pageSAP-1 Simple As Possible Computer Schematic Diagrampong74ls100% (5)

- QRS-Card™ Cardiology Suite 4.06 Software QRS-Blue™ ECG Device Operating InstructionsDocument193 pagesQRS-Card™ Cardiology Suite 4.06 Software QRS-Blue™ ECG Device Operating InstructionsHacker CrashPas encore d'évaluation

- Acknowledgements and Table of ContentsDocument4 pagesAcknowledgements and Table of ContentsJocelyn Bell100% (1)

- Microprocessor in PacemakerDocument5 pagesMicroprocessor in PacemakerAbdullah JavaidPas encore d'évaluation

- Ec 6502 Principles of Digital Signal Processing - Question Bank - 2018Document17 pagesEc 6502 Principles of Digital Signal Processing - Question Bank - 2018shankarPas encore d'évaluation

- QRS-Card Stress ECG System: HighlightsDocument2 pagesQRS-Card Stress ECG System: HighlightsJhancarlos JuanmacalderonPas encore d'évaluation

- Dumping Code For Spying and Windows ToolsDocument13 pagesDumping Code For Spying and Windows ToolsRahul GandhiPas encore d'évaluation

- 65GZ032prg v0.11Document77 pages65GZ032prg v0.11DavePas encore d'évaluation

- M68kOpcodes-v2 3Document1 pageM68kOpcodes-v2 3Fabien BarbierPas encore d'évaluation

- SAP-3 Simple As Possible ComputerDocument18 pagesSAP-3 Simple As Possible ComputerAnthony K. Singleton100% (5)

- English NotesDocument6 pagesEnglish NotesSnissa Karim100% (1)

- Willem Eprom 4 and 3.5 SchematicDocument1 pageWillem Eprom 4 and 3.5 SchematicAislan SouzaPas encore d'évaluation

- SAP-1 Simple As Possible Computer With Discrete Component RAMDocument1 pageSAP-1 Simple As Possible Computer With Discrete Component RAMpong74lsPas encore d'évaluation

- SAP-1 Simple As Possible Microprocessor - Original DesignDocument1 pageSAP-1 Simple As Possible Microprocessor - Original DesignFarhan S. Adul100% (1)

- Cpu Logic DiagramDocument0 pageCpu Logic DiagramMauricio RaúlPas encore d'évaluation

- ASAP-2 Almost Simple As Possible Computer SchematicDocument1 pageASAP-2 Almost Simple As Possible Computer Schematicpong74lsPas encore d'évaluation

- PR D Q: Control Input Pin 1 - Direction Pin 3 - Step Pulses Pin 5 - Motor On/Off (0 On)Document1 pagePR D Q: Control Input Pin 1 - Direction Pin 3 - Step Pulses Pin 5 - Motor On/Off (0 On)Serchu_29Pas encore d'évaluation

- DOP7Document2 pagesDOP7Nghia Do100% (1)

- ID 4801 SchematicDocument1 pageID 4801 Schematicmjs6029100% (1)

- Osciloscopio Bs11-1Document1 pageOsciloscopio Bs11-1Abelardo PeironePas encore d'évaluation

- Iocard Master 64Document1 pageIocard Master 64rdorwPas encore d'évaluation

- Daewoo DVG 6000DDocument12 pagesDaewoo DVG 6000DOssian Valera PinedaPas encore d'évaluation

- Driver StepDocument1 pageDriver StepTam Phuong NguyenPas encore d'évaluation

- SCH UnipolarDocument1 pageSCH UnipolarSerchu_29Pas encore d'évaluation

- (UPC1888ECT) 715A802-XX Cmpc19 (P991) 'Cost Down For NecDocument1 page(UPC1888ECT) 715A802-XX Cmpc19 (P991) 'Cost Down For NecStefano PartexanoPas encore d'évaluation

- Schema 151Document4 pagesSchema 151bubu tymonPas encore d'évaluation

- (Codientu - Org) Sodomach-NguyenlyDocument1 page(Codientu - Org) Sodomach-NguyenlyQuy Nhơn Điện tửPas encore d'évaluation

- Apple k94 Chopin 820-3069-A PCBDocument3 pagesApple k94 Chopin 820-3069-A PCBCristiano MarquesPas encore d'évaluation

- W375 L3 V1.2 SchemDocument3 pagesW375 L3 V1.2 SchemAdrian PeterPas encore d'évaluation

- Transisorfm 15 Watt Schematic FM DIYDocument1 pageTransisorfm 15 Watt Schematic FM DIYGabrielRichardHeizerMillerPas encore d'évaluation

- Acd-28 Sm-6088cd Server SCHDocument1 pageAcd-28 Sm-6088cd Server SCHPaula TonelloPas encore d'évaluation

- MMB0 RevC SchematicDocument1 pageMMB0 RevC SchematicbiotekyPas encore d'évaluation

- OV7670 + AL422B (FIFO) Camera Module (V2.0) SchematicDocument1 pageOV7670 + AL422B (FIFO) Camera Module (V2.0) SchematicMuhammad Alfiansyah100% (3)

- Spock: Power Serial I/ODocument5 pagesSpock: Power Serial I/OSanyi Ocsai100% (2)

- Schematic1 - Page1Document1 pageSchematic1 - Page1Phan Văn TúPas encore d'évaluation

- Schematic DiagramDocument13 pagesSchematic DiagramSas WajiPas encore d'évaluation

- CidfrDocument3 pagesCidfrRey LuckytronicPas encore d'évaluation

- Digital PRE Amplifier: C30 R22 C33 C34 R24Document1 pageDigital PRE Amplifier: C30 R22 C33 C34 R24Ricardo Ignacio Parra JaraPas encore d'évaluation

- Haier HT-2199 SCHDocument1 pageHaier HT-2199 SCHCristina NistorPas encore d'évaluation

- At 52 MinDocument1 pageAt 52 MinRichard Llanque HuarachiPas encore d'évaluation

- 42 47 SMPS Inverter 715G3812Document4 pages42 47 SMPS Inverter 715G3812stollllePas encore d'évaluation

- mlt666 Rev2.8l 166Document1 pagemlt666 Rev2.8l 166victoras21Pas encore d'évaluation

- Samsung Sch-A410 Service ManualDocument30 pagesSamsung Sch-A410 Service Manualsaboor ashraf100% (1)

- PICKIT2Document1 pagePICKIT2NinhĐứcThànhPas encore d'évaluation

- MCD Demo2 Manual enDocument33 pagesMCD Demo2 Manual enmario_villarreal_110% (1)

- DFR0063 v1.2 SchematicDocument1 pageDFR0063 v1.2 SchematicVasi ValiPas encore d'évaluation

- PinOut Diagrams PDFDocument4 pagesPinOut Diagrams PDFDaryl ScottPas encore d'évaluation

- Labx 1 SCHDocument2 pagesLabx 1 SCHercervantesPas encore d'évaluation

- LAB-X1 SchematicDocument2 pagesLAB-X1 SchematicRenato MirandaPas encore d'évaluation

- GT S5360Document51 pagesGT S5360radiobrunoPas encore d'évaluation

- Mackie PPM-808S Preamp SectionDocument11 pagesMackie PPM-808S Preamp Sectionsamb1978Pas encore d'évaluation

- CircuitDocument1 pageCircuitShahid Naseem100% (1)

- Titanium Custom 1100a PDocument13 pagesTitanium Custom 1100a PVictor Rambo100% (1)

- LCR Metar - Sve ShemeDocument7 pagesLCR Metar - Sve ShemeKarlo MužinićPas encore d'évaluation

- Daewoo HC-6120 6220 Home Teather Con DVD Diagramas PCBDocument27 pagesDaewoo HC-6120 6220 Home Teather Con DVD Diagramas PCBJavier Silva AlanisPas encore d'évaluation

- Panasonic TC 50ps14 Service Manual PDF 76296Document1 pagePanasonic TC 50ps14 Service Manual PDF 76296stuartPas encore d'évaluation

- Q9T4 FP91G Interface BDDocument5 pagesQ9T4 FP91G Interface BDax63naPas encore d'évaluation

- SCH Code Access Sys k639Document1 pageSCH Code Access Sys k639Gaurav SharmaPas encore d'évaluation

- Hardware System For Real Time Gps TrackingDocument8 pagesHardware System For Real Time Gps TrackingAshit AdhikariPas encore d'évaluation

- 100407Document4 pages100407ioan cristian cotorobaiPas encore d'évaluation

- 6AV66440AA012AX0 Datasheet enDocument6 pages6AV66440AA012AX0 Datasheet enJoseph MagonduPas encore d'évaluation

- 750 In001 - en P PDFDocument302 pages750 In001 - en P PDFArmandoOlivaresPas encore d'évaluation

- Astra AllDocument192 pagesAstra Allmnbvqwert33% (3)

- Bowex - : Curved-Tooth Gear Couplings Shaft CouplingsDocument16 pagesBowex - : Curved-Tooth Gear Couplings Shaft CouplingsRogelio ManeiroPas encore d'évaluation

- Peugeot 5008 Suv BrochureDocument24 pagesPeugeot 5008 Suv BrochureMamphayssou N'GUESSAN100% (1)

- LuxOR Revalia Spec SheetDocument2 pagesLuxOR Revalia Spec SheetmonicaPas encore d'évaluation

- 225-227 WiringDocument205 pages225-227 WiringMohamedAl-gamalPas encore d'évaluation

- Boat Wiring Color Chart - BoatWiringDocument5 pagesBoat Wiring Color Chart - BoatWiringRenganathanPadmanabhanPas encore d'évaluation

- TICS Resistance For MITSUBISHI InddDocument31 pagesTICS Resistance For MITSUBISHI InddBradley Lodder92% (13)

- How To Make A CRT TV Into An OscilloscopeDocument10 pagesHow To Make A CRT TV Into An OscilloscopeNusret YılmazPas encore d'évaluation

- 88-02 Cummins Exhaust BrakeDocument24 pages88-02 Cummins Exhaust Brakemark_dayPas encore d'évaluation

- Abloy-EL440 441 442 443 PDFDocument2 pagesAbloy-EL440 441 442 443 PDFDanPas encore d'évaluation

- Group 3 Electrical SystemDocument16 pagesGroup 3 Electrical SystemTaha RdmanPas encore d'évaluation

- Pxi Express Embedded ControllersDocument9 pagesPxi Express Embedded ControllersyamaxiPas encore d'évaluation

- Manual FFU DC EB PDFDocument34 pagesManual FFU DC EB PDFSalaar AnsarPas encore d'évaluation

- Moving Rotating EquipmentDocument35 pagesMoving Rotating EquipmentAun AbbasPas encore d'évaluation

- Black & Decker Running New WireDocument131 pagesBlack & Decker Running New Wirehanner90100% (27)

- Listado de Repuestos 6bt JCCDocument4 pagesListado de Repuestos 6bt JCCGian Carlos Apolinario TitoPas encore d'évaluation

- RE18301-91 - Cartridge Valves - NloDocument12 pagesRE18301-91 - Cartridge Valves - NloTaller PahrPas encore d'évaluation

- ESCB200: Electronic Compensated Standard Current BurdenDocument25 pagesESCB200: Electronic Compensated Standard Current BurdenMiloradPas encore d'évaluation

- P633 OrderForm - v52 - 112021Document14 pagesP633 OrderForm - v52 - 112021keglobalPas encore d'évaluation

- MOV Test FormDocument1 pageMOV Test FormAli Akbar100% (1)

- Metering Is Our Business: High Precision Integrated MeterDocument2 pagesMetering Is Our Business: High Precision Integrated MeterYigit SarıkayaPas encore d'évaluation

- Ease of Use: Product Sheet Thermoflexx 80Document4 pagesEase of Use: Product Sheet Thermoflexx 80Chamakhi AmeurPas encore d'évaluation

- Design Condition: B Regulator General DrawingDocument20 pagesDesign Condition: B Regulator General DrawingHassan SleemPas encore d'évaluation

- YLAA Engineering GuideDocument64 pagesYLAA Engineering GuideJoe YoungPas encore d'évaluation

- Voip TrainingDocument12 pagesVoip TrainingMC. Rene Solis R.100% (7)

- Adi Wijaya Project - Vc0-ReportDocument7 pagesAdi Wijaya Project - Vc0-Reportryhz0410Pas encore d'évaluation

- Triode Electronics Jcm800 2204 50W LayoutDocument1 pageTriode Electronics Jcm800 2204 50W LayoutDimce BusinoskiPas encore d'évaluation