Académique Documents

Professionnel Documents

Culture Documents

UC3845

Transféré par

roozbehxoxCopyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

UC3845

Transféré par

roozbehxoxDroits d'auteur :

Formats disponibles

www.fairchildsemi.

com

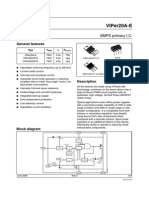

UC3842/UC3843/UC3844/UC3845

SMPS Controller

Features

Low Start up Current Maximum Duty Clamp UVLO With Hysteresis Operating Frequency up to 500KHz

Description

The UC3842/UC3843/UC3844/UC3845 are fixed frequencycurrent-mode PWM controller. They are specially designed for Off-Line and DC to DC converter applications with minimum external components. These integrated circuits feature a trimmed oscillator for precise duty cycle control, a temperature compensated reference, high gain error amplifier, current sensing comparator and a high current totempole output for driving a Power MOSFET. The UC3842 and UC3844 have UVLO thresholds of 16V (on) and 10V (off). The UC3843 and UC3845 are 8.5V(on) and 7.9V (off). The UC3842 and UC3843 can operate within 100% duty cycle. The UC3844 and UC3845 can operate with 50% duty cycle.

8-DIP 8-SOP

14-SOP

Internal Block Diagram

* NORMALLY 8DIP/8SOP PIN NO. * ( ) IS 14SOP PINNO. * TOGGLE FLIP FLOP USED ONLY IN UC3844, UC3845

Rev. 1.0.1

2002 Fairchild Semiconductor Corporation

UC3842/UC3843/UC3844/UC3845

Absolute Maximum Ratings

Parameter Supply Voltage Output Current Analog Inputs (Pin 2.3) Error Amp Output Sink Current Power Dissipation at TA25C (8DIP) Power Dissipation at TA25C (8SOP) Power Dissipation at TA25C (14SOP) Storage Temperature Range Lead Temperature (Soldering, 10sec) Symbol VCC IO V(ANA) ISINK (E.A) PD(Note1,2) PD(Note1,2) PD(Note1,2) TSTG TLEAD Value 30 1 -0.3 to 6.3 10 1200 460 680 -65 ~ +150 +300 Unit V A V mA mW mW mW C C

Note: 1. Board Thickness 1.6mm, Board Dimension 76.2mm 114.3mm, (Reference EIA / JSED51-3, 51-7) 2. Do not exceeed PD and SOA (Safe Operation Area)

Power Dissipation Curve

1200 8DIP 1100 POWER DISSIPATION (mW) 1000 900 800 700 600 500 400 300

0 10 20 30 40 50 60 70 80 90 100 110 120 130 140 150

14SOP

8SOP

AMBIENT TEMPERATURE ()

Thermal Data

Characteristic Thermal Resistance Junction-ambient Symbol Rthj-amb(MAX) 8-DIP 100 8-SOP 265 14-SOP 180 Unit C/W

Pin Array

8DIP,8SOP 14SOP

COMP 1

VREF

COMP 1

14 VREF

VFB 2

VCC

N/C

13

N/C

CURRENT SENSE

OUTPUT

VFB 3

12

VCC

RT/ CT 4

5 GND

N/C 4

11 PWR VC

CURRENT SENSE

10 OUTPUT

N/C

GND

RT/C T 7

PWR GND

UC3842/UC3843/UC3844/UC3845

Electrical Characteristics

(VCC=15V, RT=10k, CT=3.3nF, TA= 0C to +70C, unless otherwise specified) Parameter REFERENCE SECTION Reference Output Voltage Line Regulation Load Regulation Short Circuit Output Current OSCILLATOR SECTION Oscillation Frequency Frequency Change with Voltage Oscillator Amplitude ERROR AMPLIFIER SECTION Input Bias Current Input Voltage Open Loop Voltage Gain Power Supply Rejection Ratio Output Sink Current Output Source Current High Output Voltage Low Output Voltage CURRENT SENSE SECTION Gain Maximum Input Signal Power Supply Rejection Ratio Input Bias Current OUTPUT SECTION Low Output Voltage High Output Voltage Rise Time Fall Time Start Threshold Min. Operating Voltage (After Turn On) VOL ISINK = 20mA ISINK = 200mA VOH tR tF ISOURCE = 20mA ISOURCE = 200mA TJ = 25C, CL= 1nF (Note 3) TJ = 25C, CL= 1nF (Note 3) UC3842/UC3844 UC3843/UC3845 UC3842/UC3844 UC3843/UC3844 13 12 14.5 7.8 8.5 7.0 0.08 1.4 13.5 13.0 45 35 16.0 8.4 10.0 7.6 0.4 2.2 150 150 17.5 9.0 11.5 8.2 V V V V ns ns V V V V GV VI(MAX) PSRR IBIAS (Note 1 & 2) Vpin1 = 5V(Note 1) 12V VCC 25V (Note 1,3) 2.85 0.9 3 1 70 -3 3.15 1.1 -10 V/V V dB A IBIAS VI(E>A) GVO PSRR ISINK ISOURCE VOH VOL Vpin1 = 2.5V 2V VO 4V (Note3) 12V VCC 25V (Note3) Vpin2 = 2.7V, Vpin1 = 1.1V Vpin2 = 2.3V, Vpin1 = 5V Vpin2 = 2.3V, RL = 15k to GND Vpin2 = 2.7V, RL = 15k to Pin 8 2.42 65 60 2 -0.6 5 -0.1 2.50 90 70 7 -1.0 6 0.8 -2 2.58 1.1 A V dB dB mA mA V V f f/VCC VOSC TJ = 25C 12V VCC 25V 47 52 0.05 1.6 57 1 kHz % VP-P VREF VREF VREF ISC TJ = 25C, IREF = 1mA 12V VCC 25V 1mA IREF 20mA TA = 25C 4.90 5.00 6 6 -100 5.10 20 25 -180 V mV mV mA Symbol Conditions Min. Typ. Max. Unit

UNDER-VOLTAGE LOCKOUT SECTION VTH(ST) VOPR(MIN)

UC3842/UC3843/UC3844/UC3845

Electrical Characteristics (Continued)

(VCC=15V, RT=10k, CT=3.3nF, TA= 0C to +70C, unless otherwise specified) Parameter PWM SECTION Max. Duty Cycle Min. Duty Cycle TOTAL STANDBY CURRENT Start-Up Current Operating Supply Current Zener Voltage IST ICC(OPR) VZ ICC = 25mA Vpin3=Vpin2=ON 30 0.45 14 38 1 17 mA mA V D(Max) D(Max) D(MIN) UC3842/UC3843 UC3844/UC3845 95 47 97 48 100 50 0 % % % Symbol Conditions Min. Typ. Max. Unit

Adjust VCC above the start threshould before setting at 15V

Note: 1. Parameter measured at trip point of latch 2. Gain defined as: V pin1 A = ----------------- ,0 Vpin3 0.8V V pin3 3. These parameters, although guaranteed, are not 100 tested in production.

UC3842

Figure 1. Open Loop Test Circuit

High peak currents associated with capacitive loads necessitate careful grounding techniques Timing and bypass capacitors should be connected close to pin 5 in a single point ground. The transistor and 5k potentiometer are used to sample the oscillator waveform and apply an adjustable ramp to pin 3.

UC3842/UC3843/UC3844/UC3845

UC3842/44 UC3843/45

Figure 2. Under Voltage Lockout

During Under-Voltage Lock-Out, the output driver is biased to a high impedance state. Pin 6 should be shunted to ground with a bleeder resistor to prevent activating the power switch with output leakage current.

Figure 3. Error Amp Configuration

Figure 4. Current Sense Circuit

Peak current (IS) is determined by the formula:

1.0V I S ( MAX ) = ----------RS

A small RC filter may be required to suppress switch transients.

UC3842/UC3843/UC3844/UC3845

Figure 5. Oscillator Waveforms and Maximum Duty Cycle

Oscillator timing capacitor, CT, is charged by VREF through RT and discharged by an internal current source. During the discharge time, the internal clock signal blanks the output to the low state. Selection of RT and CT therefore determines both oscillator frequency and maximum duty cycle. Charge and discharge times are determined by the formulas: tc = 0.55 RT CT

0.0063RT 2.7 t D = R T C T I n --------------------------------------- 0.0063R T 4

Frequency, then, is: f=(tc + td)-1

1.8 ForRT > 5K ,f = -------------RT CT

Figure 6. Oscillator Dead Time & Frequency

Figure 7. Timing Resistance vs Frequency

(Deadtime vs CT RT > 5k)

Figure 8. Shutdown Techniques

UC3842/UC3843/UC3844/UC3845

Shutdown of the UC3842 can be accomplished by two methods; either raise pin 3 above 1V or pull pin 1 below a voltage two diode drops above ground. Either method causes the output of the PWM comparator to be high (refer to block diagram). The PWM latch is reset dominant so that the output will remain low until the next clock cycle after the shutdown condition at pins 1 and/or 3 is removed. In one example, an externally latched shutdown may be accomplished by adding an SCR which will be reset by cycling VCC below the lower UVLO threshold. At this point the reference turns off, allowing the SCR to reset.

UC3842/UC3843

Figure 9. Slope Compensation

A fraction of the oscillator ramp can be resistively summed with the current sense signal to provide slope compensation for converters requiring duty cycles over 50%. Note that capacitor, CT, forms a filter with R2 to suppress the leading edge switch spikes.

Temperature (C) Figure 10. Temperature Drift (Vref)

Temperature (C) Figure 11. Temperature Drift (Ist)

Temperature (C) Figure 12. Temperature Drift (Icc)

UC3842/UC3843/UC3844/UC3845

Mechanical Dimensions

Package

8-DIP

1.524 0.10 0.018 0.004 0.060 0.004 0.46 0.10

6.40 0.20 0.252 0.008

#1

#8

#4

#5

9.20 0.20 0.362 0.008

9.60 MAX 0.378

0.79 ) 0.031

5.08 MAX 0.200 7.62 0.300 3.40 0.20 0.134 0.008

3.30 0.30 0.130 0.012 0.33 MIN 0.013

0.25 0.05

+0.10

0~15

0.010 0.002

+0.004

2.54 0.100

UC3842/UC3843/UC3844/UC3845

Mechanical Dimensions (Continued)

Package

8-SOP

MIN 1.55 0.20 0.061 0.008 0.1~0.25 0.004~0.001

#1

#8 4.92 0.20 0.194 0.008 5.13 MAX 0.202

( #4 #5 6.00 0.30 0.236 0.012

+0.10 0.15 -0.05 +0.004 0.006 -0.002

0.56 ) 0.022 1.80 MAX 0.071 MAX0.10 MAX0.004 3.95 0.20 0.156 0.008 5.72 0.225 0.50 0.20 0.020 0.008

0~

1.27 0.050

0.41 0.10 0.016 0.004

UC3842/UC3843/UC3844/UC3845

Mechanical Dimensions (Continued)

Package

14-SOP

MIN 1.55 0.10 0.061 0.004 0.05 0.002

#1

#14

8.70 MAX 0.343

8.56 0.20 0.337 0.008

#7 6.00 0.30 0.236 0.012

#8

1.80 MAX 0.071

+0.10 0.20 -0.05 +0.004 0.008 -0.002

3.95 0.20 0.156 0.008

0.60 0.20 0.024 0.008

5.72 0.225

10

0~

MAX0.10 MAX0.004

1.27 0.050

+0.10 0.406 -0.05 +0.004 0.016 -0.002

0.47 ) 0.019

UC3842/UC3843/UC3844/UC3845

Ordering Information

Product Number UC3842N UC3843N UC3844N UC3845N UC3842D1 UC3843D1 UC3844D1 UC3845D1 UC3842D UC3843D UC3844D UC3845D 14-SOP 8-SOP 0 ~ + 70C 8-DIP Package Operating Temperature

11

UC3842/UC3843/UC3844/UC3845

DISCLAIMER FAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY PRODUCTS HEREIN TO IMPROVE RELIABILITY, FUNCTION OR DESIGN. FAIRCHILD DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN; NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS. LIFE SUPPORT POLICY FAIRCHILDS PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD SEMICONDUCTOR CORPORATION. As used herein: 1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury of the user.

www.fairchildsemi.com 2/19/02 0.0m 001 Stock#DSxxxxxxxx 2002 Fairchild Semiconductor Corporation

2. A critical component in any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

This datasheet has been download from: www.datasheetcatalog.com Datasheets for electronics components.

Vous aimerez peut-être aussi

- Schematic Conversor Booster Vari├бvel, entrada 12V sa├нda 5 ├а 48V com CI UC3843 fvmlDocument1 pageSchematic Conversor Booster Vari├бvel, entrada 12V sa├нda 5 ├а 48V com CI UC3843 fvmlMarcelo Rodrigues Barbosa100% (1)

- Sony KLV-40S200ADocument120 pagesSony KLV-40S200AClaudio BarrosPas encore d'évaluation

- LCD Color TV: KLV-23S200A KLV-32S200A KLV-26S200A KLV-40S200ADocument48 pagesLCD Color TV: KLV-23S200A KLV-32S200A KLV-26S200A KLV-40S200Aphillip2chang6539Pas encore d'évaluation

- LG-Component Level Repair Y-Z Board IPMDocument3 pagesLG-Component Level Repair Y-Z Board IPMcaseysamPas encore d'évaluation

- Stepper 23bb h202 14Document9 pagesStepper 23bb h202 14niltonces100% (1)

- AMS1117-5.0-Adjustable and Fixed Voltage Regulators de 1 ADocument8 pagesAMS1117-5.0-Adjustable and Fixed Voltage Regulators de 1 AKrista Tran100% (1)

- Kirisun PT8100-Service-ManualDocument35 pagesKirisun PT8100-Service-ManualRobertino100% (1)

- BuckBoost SEPIC CV CC 5-30V 5A 150W TL494 - 0.1.4 - STABLEDocument5 pagesBuckBoost SEPIC CV CC 5-30V 5A 150W TL494 - 0.1.4 - STABLELibroLivro100% (1)

- Sony Bravia KDL LCD TV Error Codes PDFDocument16 pagesSony Bravia KDL LCD TV Error Codes PDFMilton MedinaPas encore d'évaluation

- Beta 3 B118a Sigma Active Subwoofer Speaker SystemDocument4 pagesBeta 3 B118a Sigma Active Subwoofer Speaker SystemGabriel0% (1)

- Guia de FlybackDocument84 pagesGuia de FlybackEulides RomeroPas encore d'évaluation

- ICE250A Datasheet Full Rev 8Document15 pagesICE250A Datasheet Full Rev 8Johs316Pas encore d'évaluation

- Mobile Phone DetectorDocument3 pagesMobile Phone DetectorSuvashish GautamPas encore d'évaluation

- Mobile Communications Product GuideDocument2 pagesMobile Communications Product GuideЖељко Гелић100% (1)

- Stetsom TH41204120 R1a S01Document1 pageStetsom TH41204120 R1a S01Everson CorreaPas encore d'évaluation

- LECTURE 8 Induction Machines 02Document132 pagesLECTURE 8 Induction Machines 02MINH Nguyễn TuấnPas encore d'évaluation

- Válvula KCG 03Document11 pagesVálvula KCG 03CristianPas encore d'évaluation

- BN44-00249C Pwi1902ss (A) (U101 FSFM260, U1 Oz9938 - B1, U2 Fan431a)Document3 pagesBN44-00249C Pwi1902ss (A) (U101 FSFM260, U1 Oz9938 - B1, U2 Fan431a)Leandro PalmeiraPas encore d'évaluation

- PFC and Driver Circuit SchematicDocument3 pagesPFC and Driver Circuit SchematicPablo Acapulco GuerreroPas encore d'évaluation

- Schematic - Receptor Oc Fet - 2022!05!03Document1 pageSchematic - Receptor Oc Fet - 2022!05!03Doni SouzaPas encore d'évaluation

- Data Sheet BD 9270Document5 pagesData Sheet BD 9270senilsonPas encore d'évaluation

- 3 Axis TB6560 3.5A Stepper Motor Driver Board Manual PDFDocument10 pages3 Axis TB6560 3.5A Stepper Motor Driver Board Manual PDFNisar AhmedPas encore d'évaluation

- Sony Tv Error Codes 4 BlinksDocument4 pagesSony Tv Error Codes 4 BlinksUhwe SeinPas encore d'évaluation

- PIC16F84 Based LC MeterDocument3 pagesPIC16F84 Based LC MeterPravin Bhole100% (1)

- UC3843 DatasheetDocument13 pagesUC3843 DatasheetBigbrain99Pas encore d'évaluation

- Datasheet Fairchild UC3843Document7 pagesDatasheet Fairchild UC3843Tina JohnsonPas encore d'évaluation

- KA3842BDocument12 pagesKA3842BLucio Sortija LuquePas encore d'évaluation

- UC3845ANDocument15 pagesUC3845ANMiloud ChouguiPas encore d'évaluation

- UC2842A/3A/4A/5A UC3842A/3A/4A/5A: High Performance Current Mode PWM ControllerDocument16 pagesUC2842A/3A/4A/5A UC3842A/3A/4A/5A: High Performance Current Mode PWM ControllerCortés BernaPas encore d'évaluation

- MC34063ADocument15 pagesMC34063AAlfredo Valencia RodriguezPas encore d'évaluation

- Uc3843a PDFDocument8 pagesUc3843a PDFKang JadiJaya OtodidakPas encore d'évaluation

- UC2842B/3B/4B/5B UC3842B/3B/4B/5B: High Performance Current Mode PWM ControllerDocument15 pagesUC2842B/3B/4B/5B UC3842B/3B/4B/5B: High Performance Current Mode PWM ControllertoajuicePas encore d'évaluation

- Uc3842b 3843BDocument10 pagesUc3842b 3843Bbob75Pas encore d'évaluation

- Uc3842 Monitor Power Supply Regulator IcDocument7 pagesUc3842 Monitor Power Supply Regulator IcJoseph Sidhom SnadaPas encore d'évaluation

- MC34063AMDocument16 pagesMC34063AMSajjad4434Pas encore d'évaluation

- Uc284xa Uc384xaDocument16 pagesUc284xa Uc384xayusufwpPas encore d'évaluation

- LM555 Timer: General Description FeaturesDocument12 pagesLM555 Timer: General Description FeaturesMark J A. OkyoPas encore d'évaluation

- MC34063A, MC33063A, NCV33063A 1.5 A, Step Up/Down/ Inverting Switching RegulatorsDocument13 pagesMC34063A, MC33063A, NCV33063A 1.5 A, Step Up/Down/ Inverting Switching RegulatorszocanPas encore d'évaluation

- UC3842A/UC3843A: SMPS ControllerDocument8 pagesUC3842A/UC3843A: SMPS ControllerjosephsnadaPas encore d'évaluation

- Lm555 555c TimerDocument12 pagesLm555 555c TimerAlexis Orellana VediaPas encore d'évaluation

- LM555 Timer: Literature Number: SNAS548BDocument14 pagesLM555 Timer: Literature Number: SNAS548BKenly WallPas encore d'évaluation

- MC34063A, MC33063A, NCV33063A 1.5 A, Step Up/Down/ Inverting Switching RegulatorsDocument14 pagesMC34063A, MC33063A, NCV33063A 1.5 A, Step Up/Down/ Inverting Switching RegulatorsVũ TưởngPas encore d'évaluation

- Uc3844 DDocument16 pagesUc3844 DankurmalviyaPas encore d'évaluation

- Mc1455-d Timer IcDocument11 pagesMc1455-d Timer IcDecker JamesPas encore d'évaluation

- Ap 34063Document10 pagesAp 34063Hoang LePas encore d'évaluation

- 8205Document16 pages8205sonytinPas encore d'évaluation

- MC1455Document13 pagesMC1455eduardolsPas encore d'évaluation

- Current Mode PWM Controller: Features DescriptionDocument9 pagesCurrent Mode PWM Controller: Features DescriptionJozo ĆurčićPas encore d'évaluation

- SG3525A Pulse Width Modulator Control Circuit: 1% and The ErrorDocument10 pagesSG3525A Pulse Width Modulator Control Circuit: 1% and The ErrorJayesh SuryavanshiPas encore d'évaluation

- LMC555 CMOS Timer: General Description FeaturesDocument10 pagesLMC555 CMOS Timer: General Description FeaturesJeremy ObriotPas encore d'évaluation

- Uc3844 DDocument16 pagesUc3844 DFaisalMalikPas encore d'évaluation

- Uc2577 AdjDocument14 pagesUc2577 AdjChandranoola RajuPas encore d'évaluation

- LMC555 CMOS Timer: General Description FeaturesDocument12 pagesLMC555 CMOS Timer: General Description FeaturesNicolas FontanaPas encore d'évaluation

- IRG4BC30K-S: Features Features Features Features FeaturesDocument8 pagesIRG4BC30K-S: Features Features Features Features FeaturesRafael MonzonPas encore d'évaluation

- SG3524 SMPS Control Circuit: Description Pin ConfigurationDocument5 pagesSG3524 SMPS Control Circuit: Description Pin ConfigurationNiko OlnicasaPas encore d'évaluation

- IC 3842 para FonteDocument8 pagesIC 3842 para FonteTomNedscPas encore d'évaluation

- Tda 4601Document8 pagesTda 4601Mirko AleksicPas encore d'évaluation

- Isolated Flyback Switching Regulator W - 9V OutputDocument16 pagesIsolated Flyback Switching Regulator W - 9V OutputCasey DialPas encore d'évaluation

- Moc3023 PDFDocument7 pagesMoc3023 PDFEricko JustopoPas encore d'évaluation

- CA3059, CA3079: Description FeaturesDocument12 pagesCA3059, CA3079: Description FeaturesMiltongrimi GrimilPas encore d'évaluation

- 056-155 Redundant MSCDocument2 pages056-155 Redundant MSCroozbehxoxPas encore d'évaluation

- Ee 791 Drives Lab MaualDocument39 pagesEe 791 Drives Lab MaualSiddhartha Ghosh100% (1)

- Genset - Parallel Scheme - enDocument36 pagesGenset - Parallel Scheme - enNguyễn Bá DũngPas encore d'évaluation

- 056-054 DSE8x10 in Fixed Export (Base Load)Document4 pages056-054 DSE8x10 in Fixed Export (Base Load)hariana100% (1)

- Esr PDFDocument6 pagesEsr PDFsatyaPas encore d'évaluation

- SMT Devices Series Overview QFP (Quad Flat Packages, Gullwing Leads)Document6 pagesSMT Devices Series Overview QFP (Quad Flat Packages, Gullwing Leads)Marius GandraburPas encore d'évaluation

- FBs PLC Catalog enDocument28 pagesFBs PLC Catalog enroozbehxoxPas encore d'évaluation

- Dse7110 Mkii Dse7120 Mkii Data SheetDocument2 pagesDse7110 Mkii Dse7120 Mkii Data Sheetmnvijaybabu100% (1)

- Eam-110 Gac To Cummins Qsx15 Interface ... - Huegli TechDocument3 pagesEam-110 Gac To Cummins Qsx15 Interface ... - Huegli TechroozbehxoxPas encore d'évaluation

- DMO465R DatasheetDocument34 pagesDMO465R DatasheetMoisés Maidana100% (1)

- EAM110 GAC To Cummins QST Interface Module: PowerDocument3 pagesEAM110 GAC To Cummins QST Interface Module: PowerroozbehxoxPas encore d'évaluation

- Datasheet - HK Bo8032a 1219966Document1 pageDatasheet - HK Bo8032a 1219966roozbehxoxPas encore d'évaluation

- Flyer Xchange 16s e 100412.3Document9 pagesFlyer Xchange 16s e 100412.3Ranjit Marimuthu100% (2)

- LS Inverter iG5A ManualDocument181 pagesLS Inverter iG5A ManualSusovit Dwa100% (10)

- Application Manual: Keb Combivert F5-Basic / General 2.3Document334 pagesApplication Manual: Keb Combivert F5-Basic / General 2.3Anoop KumarPas encore d'évaluation

- Alternators and Starter Motors 2003 PDFDocument106 pagesAlternators and Starter Motors 2003 PDFjovopavlovic100% (4)

- H8S 2240Document818 pagesH8S 2240roozbehxoxPas encore d'évaluation

- FDS 4000 PDFDocument74 pagesFDS 4000 PDFMr.K ch100% (1)

- Capacitor AluminumDocument433 pagesCapacitor AluminumroozbehxoxPas encore d'évaluation

- Generator Sizing Guide: Technical Data TD00405018EDocument16 pagesGenerator Sizing Guide: Technical Data TD00405018EComsip400Pas encore d'évaluation

- Leroy Somer ALTERNATORDocument18 pagesLeroy Somer ALTERNATORroozbehxoxPas encore d'évaluation

- ECU List 7 0 0 Global Guide r3Document419 pagesECU List 7 0 0 Global Guide r3Satrio Ongis Nade75% (4)

- 1011-2011 TRAINING MANUAL Deutz Engine 999 0512Document141 pages1011-2011 TRAINING MANUAL Deutz Engine 999 0512Anangtri Wahyudi96% (28)

- BP12864CDocument1 pageBP12864CroozbehxoxPas encore d'évaluation

- IL NT AMF 2 2 Reference Guide r5 PDFDocument146 pagesIL NT AMF 2 2 Reference Guide r5 PDFvasilimertzaniPas encore d'évaluation

- Generator Sets Installation GuideDocument216 pagesGenerator Sets Installation Guidezinmerford92% (26)

- XGT Panel HW Manual XP10 Eng V1.2Document221 pagesXGT Panel HW Manual XP10 Eng V1.2roozbehxoxPas encore d'évaluation

- Ug40d L PDFDocument63 pagesUg40d L PDFSaasiPas encore d'évaluation

- Volvo Penta TAD734GEDocument19 pagesVolvo Penta TAD734GERomulo Oliveira Araujo100% (2)

- 21823.0 Appendix RBC1100 - LX449 V1 - 0Document8 pages21823.0 Appendix RBC1100 - LX449 V1 - 0roozbehxoxPas encore d'évaluation

- AES Lecture 1 - IntroductionDocument20 pagesAES Lecture 1 - IntroductionJagwant PanesarPas encore d'évaluation

- Certification Handbook - LinkedinDocument14 pagesCertification Handbook - LinkedinVinay KumarPas encore d'évaluation

- Operating System Assignment 4-Dos CommandsDocument7 pagesOperating System Assignment 4-Dos CommandsJayashree WawhalPas encore d'évaluation

- Easy Temperature Sensing With Raspberry PiDocument3 pagesEasy Temperature Sensing With Raspberry PiJay JPas encore d'évaluation

- Pentair Intellibrite 5g Color Led Pool Installation ManualDocument32 pagesPentair Intellibrite 5g Color Led Pool Installation ManualZahidul HasanPas encore d'évaluation

- Maneuvers Multi-EngineDocument1 pageManeuvers Multi-EngineELAC2Pas encore d'évaluation

- Computer Viruses: A Problem Management: Ian LeitchDocument4 pagesComputer Viruses: A Problem Management: Ian LeitchAlex KraemerPas encore d'évaluation

- Jeff Lee ResuméDocument1 pageJeff Lee ResuméAnonymous ElaFnh6nPas encore d'évaluation

- 821pneumatic Gear Transmission For Two Wheeler PDFDocument6 pages821pneumatic Gear Transmission For Two Wheeler PDFNithinPas encore d'évaluation

- How To Get Started With Artificial Intelligence: A Guide For EnterprisesDocument17 pagesHow To Get Started With Artificial Intelligence: A Guide For Enterprisesbal_thakrePas encore d'évaluation

- Airport Baggage HandlerDocument4 pagesAirport Baggage HandlerAyÒúß ĐḡPas encore d'évaluation

- Pre-Grading Test - Part 1Document3 pagesPre-Grading Test - Part 1Frank BozPas encore d'évaluation

- Excel Opening From VB6Document1 pageExcel Opening From VB6Sachin DhawadPas encore d'évaluation

- Craftsman c459 52833 Snow Blower 56Document56 pagesCraftsman c459 52833 Snow Blower 56Rick HenbidPas encore d'évaluation

- ASME B16.36-96 Bridas de OrificioDocument11 pagesASME B16.36-96 Bridas de OrificioLuis MoralesPas encore d'évaluation

- MAYADocument564 pagesMAYADwissamenPas encore d'évaluation

- Sample Customer ReportsDocument21 pagesSample Customer ReportsSuhail100% (1)

- DMVPN TutorialDocument10 pagesDMVPN TutorialwahyuabadiPas encore d'évaluation

- User Manual: UPS5000-E - (25 kVA-125 kVA) - FMDocument261 pagesUser Manual: UPS5000-E - (25 kVA-125 kVA) - FMjintoPas encore d'évaluation

- Photodetectors and Solar CellsDocument11 pagesPhotodetectors and Solar CellsavecafePas encore d'évaluation

- 50hz - gcs16lrg - 0700 LennoxDocument16 pages50hz - gcs16lrg - 0700 Lennoxnvr735iPas encore d'évaluation

- Technology and Science in Ancient Civilizations PDFDocument276 pagesTechnology and Science in Ancient Civilizations PDFjuanan6967% (3)

- Draft Indian Standard for Testing Marine Diesel EnginesDocument17 pagesDraft Indian Standard for Testing Marine Diesel EnginesRajan Bhandari100% (1)

- 03 Creating Weldment ProfileDocument4 pages03 Creating Weldment Profilesachin patilPas encore d'évaluation

- AES - Voice Coil Impedance As A Function of Frequency and DisplacementDocument19 pagesAES - Voice Coil Impedance As A Function of Frequency and DisplacementTinginio PantisPas encore d'évaluation

- PVK Pump Features SummaryDocument99 pagesPVK Pump Features SummarySebastiao DuartePas encore d'évaluation

- v72 PCB ManualDocument99 pagesv72 PCB ManualJuan M. CórdovaPas encore d'évaluation

- 014-2 ATLAS COPCO Parts List FD65 CAQ168961 - CAQ201806 ATLAS CAPCO AIR DRYER PDFDocument26 pages014-2 ATLAS COPCO Parts List FD65 CAQ168961 - CAQ201806 ATLAS CAPCO AIR DRYER PDFCristiTancu100% (1)

- Advik Report On PythonDocument49 pagesAdvik Report On PythonPrints BindingsPas encore d'évaluation

- SMT Soldering Guidelines: Cautions For Surface Mount Relay InstallationDocument2 pagesSMT Soldering Guidelines: Cautions For Surface Mount Relay InstallationfreddyesfreddyPas encore d'évaluation