Académique Documents

Professionnel Documents

Culture Documents

Lab4 Nand Schem Sim

Transféré par

raghuippiliDescription originale:

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

Lab4 Nand Schem Sim

Transféré par

raghuippiliDroits d'auteur :

Formats disponibles

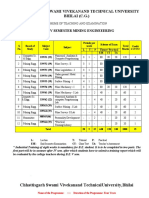

ECE 126 Logic Gate Creation: 2 input NAND Gate Schematic + Test Bench

Created at GWU by Anis Nurashikin Nordin & Thomas Farmer Objectives: Create a schematic for a 2 input NAND gate Create a symbol for a 2 input NAND gate Create a test bench for a 2 input NAND gate, that allows for transient simulation to verify functionality of NAND gate Create a test bench for a 2 input NAND gate, that allows for a swept DC analysis Create a layout for a 2 input NAND gate Create an AND gate using Inverter (from Lab 3) with NAND gate (from this lab) Assumptions: Student has successfully completed Lab 1, 2, and 3 Part 1: Creating NAND Schematic 1. Login to workstation and start cadence 2. From the Library Manager, click on your DIGITAL library o Choose File->New->Cell View o Fill in the form: o Library Name: Digital o Cell: nand2 o View: schematic o Type: schematic o Application: Schematics-L 3. Instance parts: pmos4, nmos4, vdd, gnd, to create the following schematic

For now, use minimum sizes for W/L of each transistor, later you will adjust them

You must rotate the PMOS and NMOS SIDEWAYS by doing the following:

Before Rotate

After Rotate

(notice, current flow direction is still the same)

o o o o

Menu: Edit->rotate or press the letter r Click Sideways Note the current flow direction after you rotate is still correct! (this is important) You can also rotate the input/output pins as well

4. Check and save schematic, make sure there are no warnings/errors

Part 2: Creating NAND Symbol 1. In the schematic editor, from the menu choose: Create->Cellview->From Cell View o Accept the defaults and press OK o The symbol editor appears 2. Press the delete key and click on the green box and red box in the editor o Do NOT delete the PINS or labels for the PINS, if you do, close the window and DO not save, simply restart from step 1 above 3. Create the following symbol:

From the menu choose: Create->Shape->Line, draw the left, top and bottom lines

o o

Choose Arc shape to draw the Arc of the NAND gate Choose the Circle shape to draw the circle of the NAND gate

4. Save and close the symbol 5. Save and close the schematic

Part 3: Creating the Functional Test Bench 1. From the Library Manager, click on your DIGITAL library o Choose File->New->Cell View o Fill in the form: o Library Name: Digital o Cell: nand2_tb o View: schematic o Type: schematic o Application: Schematics-L 2. Instance parts: 1 vdd, 4 gnds, 2 vpulse, 1 10pF capacitor, and your NAND gate, to create the following schematic:

3. Add wire names to the input and output wires: 1. From the menu, choose: Create->Wire Name 2. Type the letter A then click on the wire you wish to name 3. Repeat this process for wires: B and OUT

4. This gives names to your nets, as opposed to the random net7 type names 5. This is very helpful when you are viewing your simulated results

4. Select each Pulse Input, press the letter q and set the vpulse properties as follows:

vpulse attached to A

vpulse attached to B

5. 6. 7. 8.

Notice the overlapping periods in the figures above Set the VDC (for VDD) voltage to 5V Set the capacitor to 10pF Save the schematic, and perform a transient analysis as follows: From the menu, choose: Launch->ADE-L Ensure that you use the Spectre simulator Choose Analysis type to be: transient lasting for 150u seconds (notice: thats about 4 cycles of vpulse B) Plot the signals of Nets A, B, and OUT (from the schematic) as shown below (now you see why we labeled the wires) Run the simulation

When the resultant graph appears, choose from the menu: Axis->Strips to separate the signals

Is it working? Look at the graph for A, and B, when they are at 5V, this indicates a logical 1. When it is at 0 volts, this indicates a logical 0. Write out the truth table for a 2 input NAND gate. See if the logic values for the OUT net match up with your expectations.

9. Once everything is working, save the STATE of the simulator and call it: nand2_functional_test 10. Close the simulator and schematic

Part 4: Creating the VTC Test Bench 1. From the Library Manager, click on your DIGITAL library Choose File->New->Cell View Fill in the form: o Library Name: Digital o Cell: nand2_tb o View: schematic_vtc o Type: schematic o Application: Schematics-L By using this View Name, you may see the following error message:

Answer YES to this error. It is occurring because were putting 2 schematics under 1 cell name

2. Instance parts: (1) vdd, 3 gnds, (2) vdcs, (1) 10pF capacitor, and your NAND gate, to create the following schematic:

o o

Tip: You can copy and paste most of this stuff from your other test bench: o Select everything in your old schematic o Press c and point at the selected components o Then in your new schematic, point where you want the copy to be put Add Wire Names: IN and OUT (do NOT use A, B, OUT as before) Set the DC voltage of the VDC attached to both inputs of the NAND gate, to 0

Why have we tied the inputs together??? -if you look at the schematic, tie the inputs together in your mind, and youll see weve just turned our NAND gate into an inverter! -were now going to size the pmos and nmos just as we did in lab2 to obtain a midpoint on the VTC graph

3. Click on the NAND symbol, press the letter X to descend into the schematic view o Make sure you use capitol X o Set the Width of both PMOS transistors to a variable named: w_p o Set the Width of both NMOS transistors to a variable named: w_n o Save the schematic o Press the letter b to return to the test bench view 4. Open up the simulator, use Spectre, and create a DC analysis o Choose the sweep variable to be a Component Parameter and select the DC input to your NAND gate as the component to be varied, from 0 to 5 volts as follows: o If you have forgotten these steps, see Lab 2 for detailed instructions

Your components may have different names, so dont just fill in the form, select from the schematic

5. Copy the Variables you setup from the cell view: o From the menu, choose: Variables->Copy From Cell View o Give them default values by clicking on them: o w_p=1.5u o w_n=1.5u 6. Choose the OUT Net to be plotted o This will plot the Output net vs. the swept component (the input!)

7. Your simulation should look like this:

8. Run the simulation and youll see the following output:

The problem is that this VTC curve doesnt have X=Y=2.5 (midpoint), the PMOS and NMOS are not sized properly for optimum performance o How to size them: o In Lab 2b, you were shown how to perform a parametric analysis. o Perform a parametric analysis, leave w_n=1.5u and vary w_p If that doesnt work, fix w_p=1.5u and vary w_n o Once midpoint is achieved, go back and update your schematic with the proper sizes o What is the ratio? How much bigger (or smaller) is the NMOS than the PMOS? Any theories on why this is? It will eventually be a HW question o In the simulator window, assign the optimum values for w_n and w_p 9. Save the STATE of the simulator, calling it: nand2_vtc 10. Save the schematic and exit, rerun the simulation from part 3 to see if timing has changed! o

Part 5: Creating the VTC Test Bench 1. From the Library Manager, click on your DIGITAL library Choose File->New->Cell View Fill in the form: o Library Name: Digital o Cell: nand2 o View: layout o Type: layout o Application: Layout L 2. When the layout editor comes up, press the letter i to instance the following cells NCSU_TechLib_ami06->pmos->layout NCSU_TechLib_ami06->nmos->layout 3. Place the nmos & pmos in your editor as follows:

The distance between them is not important, you will change them later based on the DRC rules Press the keys: <shift> f and this will fill in the outlined instances you see on the right in the figures above. To put it back to the outlined view, you may press <ctrl> f This is a shortcut way to drawing the nmos & pmos, they are special layout cells called: parameterized cells, because we can change their attributes

4. Click on the PMOS device, press the letter q to bring up its attributes Click on the Parameter button Change the Multiplier field equal: 2 This indicates you want 2 PMOS devices Make the width & length the same as the width & length from your schematic Press OK Repeat this process on the NMOS device

5. After updating both the PMOS and NMOS devices, your layout should look as follows. Notice the width & length are exactly as set in the parameter box above (W=1.5u L=.6u)

6. Instance (using the letter I) the following parameterized cells to create the body contacts for the PMOS & NMOS devices: NCSU_TechLib_ami06->ptap->layout NCSU_TechLib_ami06->ntap->layout Place the taps as you see below.

Outlined view (press <ctrl> f )

Filled-in view (press <shift> f)

A n-tap taps the n-well, forming a low ohmic contact to the n-well, typically called the body contact for the pmos device. A p-tap taps the p-substrate, forming a low ohmic contact to the p-substrate, typically this is called the body contact for the nmos device. These taps are also parameterized cells, and you can increase the # of contacts to the body of the device by changing appropriate parameter. As an example, select the n-tap device, press the letter q Change the columns of contacts field to read 5 instead of 1. Press OK, and you see you now have 5 contacts to the n-well as shown on the right in the figure below.

For the remainder of this example, Ive set mine to 1, but you may wish for more contacts to the body, to ensure the n-well is at a common voltage potential

7. Connect the gates of the PMOS and NMOS devices by using the rectangle tool (pressing the letter r), to draw a rectangle of poly, as follows:

8. Draw a rectangle of Metal-1 to connect the PMOS sources to the body contact for the PMOS devices as follows:

9. Whenever poly crosses over an active area, a gate & drain are created. Which is source & which is drain is determined by how we electrically connect the terminals. Notice in the figure below that by placing this Metal-1 contact to the body terminal, we have assigned the source & drain for the PMOS devices:

B1 S1 B1 B2 S2 S1

B2 S2

D1

D2 D1 D2

Notice the Sources overlap

Shows Source, Drain, & Body of each PMOS

10. Perform the same step, connecting the drain of the last NMOS device, to the body terminal (the p-tap):

11. Connect the drain of the first PMOS device to the drain of the first NMOS device using metal1 as follows:

12. Remember, the drain & source of an NMOS or PMOS device are interchangeable. It is the voltage we apply across them that forces the terminals to behave as the drain or the source. We have assigned the drains and sources for the NMOS devices by virtue of how weve connected them:

D1 B1 D2 B2 S2 D1 S1 D2 S1

S2

B2

Shows source, drain, body of each NMOS

B1

Notice S1 & D2 are electrically connected

13. Connect the drain of the 2nd PMOS device to the drain of the 1st PMOS device & 1st NMOS device as follows:

14. From the menu, choose Verify->DRC, ensure that you have no DRC errors:

15. If you do have DRC errors, you must work to resolve them prior to going to the next step. 16. Once you have no DRC errors, place the input pins, and voltage supply jumpers as follows:

The A & B pins are of type INPUT on the poly-layer The OUT pin is of type OUTPUT on the metal-1 layer The vdd! and gnd! Pins are of type JUMPER on the metal-1 layer

17. Save the layout, then run the DRC check again, ensure 0 DRC violations 18. From the menu choose: Verify->Extract, remember to set the switch: Extract Parasitic Caps

19. Ensure the extraction has 0 errors from the CIW window.

20. After ensuring there are 0 errors, close the layout, and open the extracted view from the Library Manager:

Outlined View

Filled in View (press <shift> f)

21. Press <shift> f, then click on the drains of the PMOS device, ensure the proper terminal pins are being highlighted. Double check the extraction, see if the transistors are the correct size and wired as corrected.

22. From the menu, choose: Verify->LVS, populate your form as follows: (if a warning comes up, choose FORM CONTENTS)

23. Press the RUN button, then look at the OUTPUT & verify that the output is error free and that the netlists of the schematic and layout match

Your output may not be exactly as it is above, but the netlists must match regardless.

24. Open the schematic view of the NAND gate, from the LVS window, back-annotate the parasitics to the schematic:

25. After adding the parasitics to the layout, re-simulate the NAND device and check the transient operation noting the effects of the parasitics.

Vous aimerez peut-être aussi

- Digital LED Thermometer with Microcontroller AVR ATtiny13D'EverandDigital LED Thermometer with Microcontroller AVR ATtiny13Évaluation : 5 sur 5 étoiles5/5 (1)

- Projects With Microcontrollers And PICCD'EverandProjects With Microcontrollers And PICCÉvaluation : 5 sur 5 étoiles5/5 (1)

- Laboratory 8 (For Honors Students) Introduction To 45 NM Process in Cadence 6Document10 pagesLaboratory 8 (For Honors Students) Introduction To 45 NM Process in Cadence 6eng.daborPas encore d'évaluation

- Lab 2 CharacteristicsCurvesMosfetDocument10 pagesLab 2 CharacteristicsCurvesMosfetyiyej11346Pas encore d'évaluation

- OrCAD PsSpice TutorialDocument7 pagesOrCAD PsSpice TutorialAlberto BufteaPas encore d'évaluation

- ECD LabDocument35 pagesECD LabRakesh kumarPas encore d'évaluation

- Vlsid RecordDocument52 pagesVlsid RecordLohit ReddyPas encore d'évaluation

- Lab 1Document6 pagesLab 1Fawad KhanPas encore d'évaluation

- Plot The DC Characteristics / 5 Regions of A CMOS InverterDocument7 pagesPlot The DC Characteristics / 5 Regions of A CMOS InverterSaurabh PriyadarshiPas encore d'évaluation

- EE6312-SPRING 2012-Cadence TutorialDocument18 pagesEE6312-SPRING 2012-Cadence TutorialWestern777Pas encore d'évaluation

- ADS TutorialDocument2 pagesADS TutorialrezaPas encore d'évaluation

- Nmos and Pmos PspiceDocument15 pagesNmos and Pmos PspiceshreenandanraoPas encore d'évaluation

- Cadence TutorialDocument19 pagesCadence Tutorialsuri1991Pas encore d'évaluation

- Cadence Design Tutorial 1Document52 pagesCadence Design Tutorial 1విజయ్ క్రిష్ణPas encore d'évaluation

- B.Tech, Ece Vlsi Design Lab: Part-A List of Experiments: S.No. Name of The ExperimentDocument103 pagesB.Tech, Ece Vlsi Design Lab: Part-A List of Experiments: S.No. Name of The ExperimentMohammedAbdulAzeemPas encore d'évaluation

- 0 Laboratory Exercise 1 Electric VLSI ToolDocument11 pages0 Laboratory Exercise 1 Electric VLSI ToolJustine Roy PunzalanPas encore d'évaluation

- Pspice Orcad TutorialDocument22 pagesPspice Orcad Tutorialอาร์มซ่า ทีนซ๋าPas encore d'évaluation

- Experiment 2 VLSIDocument3 pagesExperiment 2 VLSIRadhie NoahPas encore d'évaluation

- Layout Manual - CMOS Inverter - Exp 3Document22 pagesLayout Manual - CMOS Inverter - Exp 3ApoorvaPas encore d'évaluation

- Frequency Response of A CMOS Common-Source Amplifier: Experiment # 5Document10 pagesFrequency Response of A CMOS Common-Source Amplifier: Experiment # 5Md. Sadique SheikhPas encore d'évaluation

- Ltspice Tutorial: ObjectivesDocument22 pagesLtspice Tutorial: ObjectivesMd Kafiul IslamPas encore d'évaluation

- Cad Exp ManualDocument23 pagesCad Exp ManualRavindra KumarPas encore d'évaluation

- Vlsi Exp 1Document6 pagesVlsi Exp 1Sravani KadaruPas encore d'évaluation

- VLSI LAB Record-FormatDocument5 pagesVLSI LAB Record-Formatsrinija pallerlaPas encore d'évaluation

- Analog Circuit Simulation Using VirtuosoDocument17 pagesAnalog Circuit Simulation Using Virtuosohideeponhere@gmail.comPas encore d'évaluation

- Tanner Lab Manual (S-Edit and L-Edit)Document22 pagesTanner Lab Manual (S-Edit and L-Edit)sandeep_sggsPas encore d'évaluation

- EE115C - Digital Electronic Circuits Tutorial 1.2: Getting Familiar With Technology, MOS IV CharacteristicsDocument16 pagesEE115C - Digital Electronic Circuits Tutorial 1.2: Getting Familiar With Technology, MOS IV CharacteristicsAhmed EdrisPas encore d'évaluation

- P Spice PrimerDocument30 pagesP Spice PrimervinyrosePas encore d'évaluation

- Tanner ManualDocument44 pagesTanner ManualSanthameena Muthuramalingam100% (1)

- Orcad 9.2 Lite Edition Getting Started GuideDocument7 pagesOrcad 9.2 Lite Edition Getting Started GuideCloud WindPas encore d'évaluation

- Vlsi Laboratory: List of ExperimentsDocument49 pagesVlsi Laboratory: List of ExperimentssantoshPas encore d'évaluation

- PSpice16 6 TutorialDocument20 pagesPSpice16 6 TutorialAmbili MuraliPas encore d'évaluation

- Analog and Digital VLSI DesignDocument16 pagesAnalog and Digital VLSI DesignSkvkPas encore d'évaluation

- Vlsi Lab Manual FinalDocument26 pagesVlsi Lab Manual FinalAshish SharmaPas encore d'évaluation

- Exp No 1Document6 pagesExp No 1Jeevitha ECEPas encore d'évaluation

- Military Institute of Science and TechnologyDocument10 pagesMilitary Institute of Science and TechnologyNishat Farha SharmiPas encore d'évaluation

- Analog Lab Cadence Procedure PDFDocument18 pagesAnalog Lab Cadence Procedure PDFKavyashreeMPas encore d'évaluation

- EEE111 Multisim ManualDocument14 pagesEEE111 Multisim ManualSHADOW manPas encore d'évaluation

- VLSI TutorialDocument16 pagesVLSI Tutorialthanos_3333Pas encore d'évaluation

- Cadence Basic SimulationDocument10 pagesCadence Basic SimulationLarry FredsellPas encore d'évaluation

- Pspice Tutorial Stanford UniversityDocument4 pagesPspice Tutorial Stanford UniversitySaif AhmedPas encore d'évaluation

- Orcad 9.2 Lite Edition Getting Started GuideDocument6 pagesOrcad 9.2 Lite Edition Getting Started GuideHung NguyênPas encore d'évaluation

- Express PCB Tutorial: Entering The Schematic Into ExpressschDocument35 pagesExpress PCB Tutorial: Entering The Schematic Into Expressschgyuvaraj10100% (1)

- Exp 6 Half AdderDocument7 pagesExp 6 Half AdderKrishna PremPas encore d'évaluation

- OrCAD PspiceDocument20 pagesOrCAD PspiceDavid Sergio QuispePas encore d'évaluation

- Lab 5 Multisim TutorialDocument9 pagesLab 5 Multisim TutorialMuhammad UbaidPas encore d'évaluation

- Laboratory Exercise 4 Cmos Inverter LayoutDocument10 pagesLaboratory Exercise 4 Cmos Inverter Layoutapi-3696675Pas encore d'évaluation

- Lab1 - Vlsi EceDocument19 pagesLab1 - Vlsi EceMichelleCYLPas encore d'évaluation

- Amplifier Simulation Tutorial Design Kit: Cadence 0.18μm CMOS PDK (gpdk180) (Cadence Version 6.1.5)Document41 pagesAmplifier Simulation Tutorial Design Kit: Cadence 0.18μm CMOS PDK (gpdk180) (Cadence Version 6.1.5)Nishant YadavPas encore d'évaluation

- Orcad 10.0 TutorialDocument24 pagesOrcad 10.0 TutorialNava DivyaPas encore d'évaluation

- Lab ManualDocument19 pagesLab Manualaesha fahmyPas encore d'évaluation

- C Programming for the Pc the Mac and the Arduino Microcontroller SystemD'EverandC Programming for the Pc the Mac and the Arduino Microcontroller SystemPas encore d'évaluation

- Arduino Measurements in Science: Advanced Techniques and Data ProjectsD'EverandArduino Measurements in Science: Advanced Techniques and Data ProjectsPas encore d'évaluation

- PIC Projects and Applications using C: A Project-based ApproachD'EverandPIC Projects and Applications using C: A Project-based ApproachÉvaluation : 4 sur 5 étoiles4/5 (2)

- Linear IC Applications: A Designer's HandbookD'EverandLinear IC Applications: A Designer's HandbookÉvaluation : 4 sur 5 étoiles4/5 (1)

- Lab 3: CMOS NOR Gate: Circuit Design and Layout: RequirementsDocument3 pagesLab 3: CMOS NOR Gate: Circuit Design and Layout: RequirementsraghuippiliPas encore d'évaluation

- Course File Final Heena A DigitalDocument23 pagesCourse File Final Heena A DigitalraghuippiliPas encore d'évaluation

- Course File Final Heena A DigitalDocument23 pagesCourse File Final Heena A DigitalraghuippiliPas encore d'évaluation

- C08 Transport ProtocolsDocument19 pagesC08 Transport ProtocolsraghuippiliPas encore d'évaluation

- Movie Ticket RachaDocument1 pageMovie Ticket RacharaghuippiliPas encore d'évaluation

- VAMSI Kumar SRAMfinalDocument28 pagesVAMSI Kumar SRAMfinalraghuippiliPas encore d'évaluation

- Analysis of Slot Coupled HDocument7 pagesAnalysis of Slot Coupled HraghuippiliPas encore d'évaluation

- 555 TimerDocument5 pages555 TimerraghuippiliPas encore d'évaluation

- A New Approach To Minimize Leakage Power in Nano-Scale Vlsi Logic CircuitsDocument3 pagesA New Approach To Minimize Leakage Power in Nano-Scale Vlsi Logic CircuitsraghuippiliPas encore d'évaluation

- RT Procedure GeneralDocument18 pagesRT Procedure GeneralvsnaiduqcPas encore d'évaluation

- Lecture 3-1: HFSS 3D Design Setup: Introduction To ANSYS HFSSDocument40 pagesLecture 3-1: HFSS 3D Design Setup: Introduction To ANSYS HFSSRicardo MichelinPas encore d'évaluation

- Anionic PolymerisationDocument3 pagesAnionic PolymerisationChayanAnandPas encore d'évaluation

- Jenway 74 76 Series BrochureDocument6 pagesJenway 74 76 Series BrochureSadik OunisPas encore d'évaluation

- For Online Practice Exam Visit Us atDocument12 pagesFor Online Practice Exam Visit Us atscribd scribdPas encore d'évaluation

- 01 Cleveland Ruth 1997 PDFDocument21 pages01 Cleveland Ruth 1997 PDFMarianne Zanon ZotinPas encore d'évaluation

- Alexandre Grothendieck (1928-2014) Germany, FranceDocument13 pagesAlexandre Grothendieck (1928-2014) Germany, FranceDer CruzPas encore d'évaluation

- Prediction and Visualization of Supersonic Nozzle Ows Using OpenfoamDocument22 pagesPrediction and Visualization of Supersonic Nozzle Ows Using OpenfoamSai Manohar RamachandranPas encore d'évaluation

- Finite Element Analysis of Steel CordDocument6 pagesFinite Element Analysis of Steel CordSanjiv Kumar SinghPas encore d'évaluation

- BroombastickDocument3 pagesBroombastickAllen SornitPas encore d'évaluation

- Pengaruh Kandungan Frekuensi Gempa Terhadap Simpangan Dan Drift Ratio 2 Arah Struktur Bangunan Set-Back Bertingkat BanyakDocument9 pagesPengaruh Kandungan Frekuensi Gempa Terhadap Simpangan Dan Drift Ratio 2 Arah Struktur Bangunan Set-Back Bertingkat BanyakIvan MuhammadPas encore d'évaluation

- General Principles of Measurement SystemsDocument21 pagesGeneral Principles of Measurement SystemsChelseaPas encore d'évaluation

- En 132011 3 2015 2019 PDFDocument68 pagesEn 132011 3 2015 2019 PDFPrem Anand100% (2)

- AQA GCSE Chemistry AnswersDocument14 pagesAQA GCSE Chemistry AnswersErvin MetushiPas encore d'évaluation

- Cuff ManometerDocument1 pageCuff ManometerAlejandro Cardona100% (1)

- 2nd Sessional Test - Physics For Engineers-Bph-106Document1 page2nd Sessional Test - Physics For Engineers-Bph-106Saurabh Arya RspPas encore d'évaluation

- Mine Machinery-1 SyllabusDocument3 pagesMine Machinery-1 SyllabusrrathorePas encore d'évaluation

- MKN Hansdampf Cge12 eDocument2 pagesMKN Hansdampf Cge12 eRumen PavlovPas encore d'évaluation

- LG Lx-U250a Lxs-U250Document55 pagesLG Lx-U250a Lxs-U250remanuel18Pas encore d'évaluation

- Vibration Analysis, Control and Optimum Accelerometer Placement For Successful Vibrations TestsDocument44 pagesVibration Analysis, Control and Optimum Accelerometer Placement For Successful Vibrations TestsVyankatesh AshtekarPas encore d'évaluation

- Aakash FSTDocument9 pagesAakash FSTchitu20% (5)

- MASERDocument23 pagesMASERMuzzamil ShaikhPas encore d'évaluation

- Analytical Chemistry Basic ConceptsDocument12 pagesAnalytical Chemistry Basic ConceptsNino Jay FabrosPas encore d'évaluation

- (IS) Conditioner For (IS) RVDT Sensor 690210266 (IS) : SensorexDocument2 pages(IS) Conditioner For (IS) RVDT Sensor 690210266 (IS) : SensorexShakir SarvaiyaPas encore d'évaluation

- White Paper - Hairline Cracking Within Concrete Block WallsDocument7 pagesWhite Paper - Hairline Cracking Within Concrete Block WallsBirju ThakkarPas encore d'évaluation

- Line List DAR TBCDocument3 pagesLine List DAR TBChafizszul AmirushamPas encore d'évaluation

- Dvp-Es2 Ss2 Sa2 Sx2-Program o en 20110302Document14 pagesDvp-Es2 Ss2 Sa2 Sx2-Program o en 20110302yasinPas encore d'évaluation

- Asadur RahmanDocument48 pagesAsadur Rahmanah waPas encore d'évaluation

- CEG 4011 S15 TibbettsDocument5 pagesCEG 4011 S15 TibbettsGeotekers ItenasPas encore d'évaluation

- Integration Atmospheric Stability CFD Modeling MeteodynWT For Wind Resource Assessment AEP Validation Real Case Wind FarmDocument1 pageIntegration Atmospheric Stability CFD Modeling MeteodynWT For Wind Resource Assessment AEP Validation Real Case Wind FarmMeteodyn_EnergyPas encore d'évaluation