Académique Documents

Professionnel Documents

Culture Documents

06239684

Transféré par

megarebelCopyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

06239684

Transféré par

megarebelDroits d'auteur :

Formats disponibles

Standards

Managing Complex Boundary-Scan Operations

Bill Eklow Cisco Systems, Inc.

h THE

IEEE 1149.1 Standard for Test Access Port and Boundary-Scan Architecture was approved and released in 1990. Since that time, there have been two supplements and one revision to the standard. A second revision is currently in process. The 1149.1 standard was originally developed to address board level test access issues while at the same time enabling access to test logic inside the device. As technology has scaled over the last 20+ years, component and board level density and complexity have grown significantly. A new class of defects (Timing, Power, Signal Integrity) has also become more prevalent and much more difficult to detect. All of this has led to a preponderance of embedded test instruments which can augment ATE coverage and test time capabilities. These instruments include built-in memory, logic, and I/O test engines; temperature and voltage monitors; debug instruments such as: logic analyzers, scopes, and trace buffers; IP test wrappers to partition and provide direct test access to IP blocks. The 1149.1 Test Access Port has become much more prominent as THE access port to this preponderance of test instruments. Unfortunately, programming these test instruments through the test access port was/is an ad hoc process which was/is usually not well defined. Simple board level testing through the boundary register has become more complex as well. Resetting/Initializing components may now involve a series of operations that include: sequenced bring up of power domains, setting up PLLs and program-

ming of I/Os. The 1149.1 working group has also identified the need to safely transition between a functional mode and a test mode. Real life examples of damage done by blind transitions have been presented by Ken Parker at ITC 2011. These new complexities have led to the proposal of a new standard (IEEE P1687) and several enhancements to the current revision of the 1149.1 standard. Both drafts are scheduled to go to ballot later this year. The remainder of this column will address the hardware and software efforts of both working groups to deal with the complexity described earlier.

Efficient access to embedded test instruments

Given the multitude of embedded test instruments, it is critical that there be a standardized way to describe the logistical (how do I access that instrument?) and functional (how do I operate that instrument?) characteristics of each instrument so that tools providers can automate test development for these embedded instruments. The IEEE P1687 Standard for Access and Control of Instrumentation Embedded Within a Semiconductor Device proposes to provide a standardized architecture for accessing embedded test instruments. This architecture is comprised of three elements: an instrument interface specification consisting of standard signals (clocks, data, and control) used to control and observe P1687 instruments; a description language that documents how instruments are connected to the TAP controller (through a P1687 network); and a procedural language that documents the operation of the instruments.

Digital Object Identifier 10.1109/MDT.2012.2187859 Date of current version: 26 June 2012.

100

0740-7475/12/$31.00 B 2012 IEEE

Copublished by the IEEE CEDA, IEEE CASS, and IEEE SSCS

IEEE Design & Test of Computers

P1687 starts by defining an instrument as a black box with signals (ports) that are host facing (the host drives inputs and receives outputs). In its simplest form, this instrument could be an 1149.1 TDR, whose outputs are controlling the instrument and whose inputs are observing the instrument. The ports, in this case, would be the typical 1149.1 inputs/ outputs to the TDR from the TAP controller (TDI, Capture, Update, Shift . . .) and from the TDR to the TAP (TDO). An Instrument Connectivity Language(ICL) maps those ports back to the TAP controller through a series of configurable networks. In essence, describing the access path to the instrument. A Procedural Description Language (PDL) describes the sequence of operations that need to be performed on the ports in order to execute specific functions. The ICL and PDL allow for an instrument to be described functionally at an atomic level and then mapped through the component hierarchy to the component boundary. This remapping (retargeting) is a key component of the P1687 standard, allowing instrument operation to be remapped both inside the component and possibly at a higher level (board/ system). Functionality can be described as simple writes and reads, however, the working group is augmenting the PDL to allow for more complex operations which may be time bound or may require some decision-making as part of the function.

Some of the new features proposed in the revised standard include:

h

Enhanced board level, boundary-scan test capabilities

Evolving component level technology has imposed new requirements on boundary-scan (TAP) based testing, including: complex reset sequences; test initialization which may include configuring IO parameters; the ability to safely transition from test mode to functional mode; the ability to maintain the integrity of the boundary scan test logic in light of varying power requirements/availability; and component/die level traceability based on die ID. Its clear that the most significant changes to the 1149.1 standard are driven by the need to ensure that the test logic and functional logic are set to the correct (safe) state before, during, and after the execution of the boundary-scan test. Accomplishing this task is not as straightforward as in the past. Similar to IEEE P1687, 1149.1 addresses these requirements through a combination of hardware capabilities and a procedural language to document the more complex functions.

A new reset instruction which allows test logic to assert resets to the (nontest) functional logic through the TAP controller. This test initiated reset ensures that the functional logic on the device can be put into a safe state after testing has been completed, without the need to cycle power or activate an external reset. A Test-Mode Persistence Controller is added to block any unintended excursions from test mode to functional mode, again ensuring that the device can be kept in a safe state before, during and after testing. New instructions have also been added to activate and deactivate the Test-Mode Persistence Controller. A pair of optional instructions that enable initialization/configuration of the component prior to test. One instruction (INIT_SETUP) allows configuration data to be stored, while another instruction (INIT_RUN) applies the stored data to the corresponding logic (typically I/Os, but initialization data can be applied to any logic in the device in order to ensure correct and safe performance during test mode). New rules have been added which allow segmenting of Test Data Registers (TDR) and bypassing inactive segments. The segmenting and bypassing of inactive segments maintains the integrity of the TDR if parts of the TDR pass through a power domain which may be powered off during the loading/unloading of data into the TDR. Note that the new revision of 1149.1 also addresses control of power domains. An ECIDCODE instruction which enables storing and access to component Die ID information. The use of Die ID information is gaining relevance as traceability and data driven manufacturing are becoming more prominent through the supply chain.

My Comments: The new features described earlier go a long way in ensuring that test logic can operate in an efficient, deterministic, and nondestructive manner during testing, and while transitioning between test mode and functional mode. However, these solutions to complex problems involve a certain amount of complexity themselves. This complexity has been a significant and time

March/April 2012

101

Standards

consuming task for both working groups to overcome. The inclusion of a Procedural Description Language in both standards has also led to some work to ensure that there is consistency between the two standards on the intent, effect and syntax of the procedural descriptions. The result of the two standards should, however, be a comprehensive solution to component level and board level test and debug. Please note that several features in both standards were not covered in this column. For more information on the IEEE 1149.1 working group and new revision, please go to the following: http:// grouper.ieee.org/groups/1149/1, and for more information on the IEEE P1687 standard, please go to: http://grouper.ieee.org/groups/1687. It is also impor-

tant to note that both standards are intending to go to ballet before the end of this year. Finally, it is important to note that the IEEE 1500 and its programming language, IEEE 1450.6 (CTL) also have had a significant impact on managing test complexity at the embedded Core/IP level. They will be covered in a later column. h

Bill Eklow is a Distinguished Engineer at Cisco Systems.

h Direct questions and comments about this article

to Bill Eklow, Cisco Systems, Inc., 80 W. Tasman Drive, San Jose, CA 95134, USA; beklow@ cisco.com.

102

IEEE Design & Test of Computers

Vous aimerez peut-être aussi

- GK MCQ: Science and Tech QuestionsDocument4 pagesGK MCQ: Science and Tech QuestionsmegarebelPas encore d'évaluation

- Economics MCQ PDFDocument36 pagesEconomics MCQ PDFNamrata Srivastava75% (4)

- GK MCQ: Chemistry: Gurudwara Road Model Town, Hisar 9729327755Document24 pagesGK MCQ: Chemistry: Gurudwara Road Model Town, Hisar 9729327755megarebelPas encore d'évaluation

- r09 Mobile ComputingDocument1 pager09 Mobile ComputingmegarebelPas encore d'évaluation

- R09-Optical Communication TechnologyDocument1 pageR09-Optical Communication TechnologymegarebelPas encore d'évaluation

- GK MCQ: Biology:: Gurudwara Road Model Town, Hisar 9729327755Document38 pagesGK MCQ: Biology:: Gurudwara Road Model Town, Hisar 9729327755megarebelPas encore d'évaluation

- Iibf Admit Card 510337423Document4 pagesIibf Admit Card 510337423megarebelPas encore d'évaluation

- R09-Optical Communications TechnologyDocument1 pageR09-Optical Communications TechnologymegarebelPas encore d'évaluation

- CA-One Liner Revision-NotesDocument20 pagesCA-One Liner Revision-NotesmegarebelPas encore d'évaluation

- Nr-Network Security and CryptographyDocument1 pageNr-Network Security and CryptographymegarebelPas encore d'évaluation

- NR Mobile ComputingDocument1 pageNR Mobile ComputingmegarebelPas encore d'évaluation

- R09-Coding Theory and TechniquesDocument2 pagesR09-Coding Theory and TechniquesmegarebelPas encore d'évaluation

- Revised M.tech r13 RegulationsDocument9 pagesRevised M.tech r13 RegulationsmegarebelPas encore d'évaluation

- R09-Mobile Computing TechnologiesDocument1 pageR09-Mobile Computing TechnologiesmegarebelPas encore d'évaluation

- R09-Network Security and CryptographyDocument1 pageR09-Network Security and CryptographymegarebelPas encore d'évaluation

- XAT2009 Question Paper With Detailed SolutionsDocument0 pageXAT2009 Question Paper With Detailed SolutionsWajahat Ali MirzaPas encore d'évaluation

- R09-Wireless Communications and NetworksDocument1 pageR09-Wireless Communications and NetworksmegarebelPas encore d'évaluation

- R09-Network Security and CryptographyDocument1 pageR09-Network Security and CryptographymegarebelPas encore d'évaluation

- R09-Coding Theory and TechniquesDocument2 pagesR09-Coding Theory and TechniquesmegarebelPas encore d'évaluation

- Revised M.tech r13 RegulationsDocument9 pagesRevised M.tech r13 RegulationsmegarebelPas encore d'évaluation

- R09-Coding Theory and TechniquesDocument1 pageR09-Coding Theory and TechniquesmegarebelPas encore d'évaluation

- L-1 The Earth-A Living Planet - l-1 The Earth-A Living PlanetDocument20 pagesL-1 The Earth-A Living Planet - l-1 The Earth-A Living PlanetrockkPas encore d'évaluation

- R09-Wireless Communications and NetworksDocument1 pageR09-Wireless Communications and NetworksmegarebelPas encore d'évaluation

- Coding Theory and Techniques NotesDocument6 pagesCoding Theory and Techniques Notesmegarebel100% (2)

- JNTU TELECOMMUNICATION SWITCHING SYSTEMS AND NETWORKS EXAMDocument1 pageJNTU TELECOMMUNICATION SWITCHING SYSTEMS AND NETWORKS EXAMmegarebelPas encore d'évaluation

- C Interview Questions - TechPreparationDocument16 pagesC Interview Questions - TechPreparationchrisp83% (6)

- 5531xzxzr09-Optical Communications TechnologyDocument1 page5531xzxzr09-Optical Communications TechnologyPaul NathanPas encore d'évaluation

- Human Relationships at Work 1 The Untapped FrontierDocument4 pagesHuman Relationships at Work 1 The Untapped FrontiermegarebelPas encore d'évaluation

- GouldnerDocument21 pagesGouldnerEmilio GiaccioPas encore d'évaluation

- C LanguageDocument91 pagesC LanguageRan JeetPas encore d'évaluation

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeD'EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeÉvaluation : 4 sur 5 étoiles4/5 (5784)

- The Yellow House: A Memoir (2019 National Book Award Winner)D'EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Évaluation : 4 sur 5 étoiles4/5 (98)

- Never Split the Difference: Negotiating As If Your Life Depended On ItD'EverandNever Split the Difference: Negotiating As If Your Life Depended On ItÉvaluation : 4.5 sur 5 étoiles4.5/5 (838)

- Shoe Dog: A Memoir by the Creator of NikeD'EverandShoe Dog: A Memoir by the Creator of NikeÉvaluation : 4.5 sur 5 étoiles4.5/5 (537)

- The Emperor of All Maladies: A Biography of CancerD'EverandThe Emperor of All Maladies: A Biography of CancerÉvaluation : 4.5 sur 5 étoiles4.5/5 (271)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceD'EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceÉvaluation : 4 sur 5 étoiles4/5 (890)

- The Little Book of Hygge: Danish Secrets to Happy LivingD'EverandThe Little Book of Hygge: Danish Secrets to Happy LivingÉvaluation : 3.5 sur 5 étoiles3.5/5 (399)

- Team of Rivals: The Political Genius of Abraham LincolnD'EverandTeam of Rivals: The Political Genius of Abraham LincolnÉvaluation : 4.5 sur 5 étoiles4.5/5 (234)

- Grit: The Power of Passion and PerseveranceD'EverandGrit: The Power of Passion and PerseveranceÉvaluation : 4 sur 5 étoiles4/5 (587)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaD'EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaÉvaluation : 4.5 sur 5 étoiles4.5/5 (265)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryD'EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryÉvaluation : 3.5 sur 5 étoiles3.5/5 (231)

- On Fire: The (Burning) Case for a Green New DealD'EverandOn Fire: The (Burning) Case for a Green New DealÉvaluation : 4 sur 5 étoiles4/5 (72)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureD'EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureÉvaluation : 4.5 sur 5 étoiles4.5/5 (474)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersD'EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersÉvaluation : 4.5 sur 5 étoiles4.5/5 (344)

- The Unwinding: An Inner History of the New AmericaD'EverandThe Unwinding: An Inner History of the New AmericaÉvaluation : 4 sur 5 étoiles4/5 (45)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyD'EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyÉvaluation : 3.5 sur 5 étoiles3.5/5 (2219)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreD'EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreÉvaluation : 4 sur 5 étoiles4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)D'EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Évaluation : 4.5 sur 5 étoiles4.5/5 (119)

- Her Body and Other Parties: StoriesD'EverandHer Body and Other Parties: StoriesÉvaluation : 4 sur 5 étoiles4/5 (821)

- Display Keyboard - VVVVDocument3 pagesDisplay Keyboard - VVVVYungaro David Santalla AquimPas encore d'évaluation

- Backing Up and Restoring A Hyperion Essbase DatabaseDocument11 pagesBacking Up and Restoring A Hyperion Essbase DatabaseSreedhar ThatipallyPas encore d'évaluation

- Ethernet Networking Tutorial PDFDocument2 pagesEthernet Networking Tutorial PDFKariPas encore d'évaluation

- BPM Analysis TechniquesDocument6 pagesBPM Analysis Techniquesjustinbui85Pas encore d'évaluation

- Software Testing On E-Learning Madrasahs Using Blackbox TestingDocument9 pagesSoftware Testing On E-Learning Madrasahs Using Blackbox TestingomanPas encore d'évaluation

- Mod Menu Crash 2023 07 18-05 19 45Document3 pagesMod Menu Crash 2023 07 18-05 19 45Arianna Medrano muñizPas encore d'évaluation

- LPADocument16 pagesLPABhaskar AmbikapathyPas encore d'évaluation

- Docker Notes - 2023Document7 pagesDocker Notes - 2023suresh chaudharyPas encore d'évaluation

- Determining Suitability of Database Functionality and ScalabilityDocument27 pagesDetermining Suitability of Database Functionality and Scalabilitydemisew0% (1)

- Wirebit AOC VersionfinalDocument14 pagesWirebit AOC Versionfinalm69632679Pas encore d'évaluation

- Activity 1 - Introduction L Creating A ProjectDocument2 pagesActivity 1 - Introduction L Creating A ProjectAriana JeonPas encore d'évaluation

- Nordic Thingy 53 Data SheetDocument2 pagesNordic Thingy 53 Data SheetTerence Jhon TabonPas encore d'évaluation

- SQL Injection Cheat Sheet PDFDocument1 pageSQL Injection Cheat Sheet PDFJob GoPas encore d'évaluation

- Corel DrawDocument23 pagesCorel DrawananthakrishnanPas encore d'évaluation

- Lab 1 Introduction To Linux Environment and C CompilerDocument6 pagesLab 1 Introduction To Linux Environment and C Compilersyazaa syazaaPas encore d'évaluation

- Novell Groupwise: Troubleshooting: 2 Solutions To Common ProblemsDocument107 pagesNovell Groupwise: Troubleshooting: 2 Solutions To Common ProblemsEnriquePhoenixPas encore d'évaluation

- New Distributor RetrationDocument2 pagesNew Distributor RetrationPamela Acosta GerraPas encore d'évaluation

- Gallino and Sons Truckin MANTA PDFDocument2 pagesGallino and Sons Truckin MANTA PDFBrooklyn ConfuciusPas encore d'évaluation

- How To Create Signed Based Reclassification in Group ReportingDocument9 pagesHow To Create Signed Based Reclassification in Group ReportingJose EximenoPas encore d'évaluation

- Patch Management Checklist - SafetyCultureDocument3 pagesPatch Management Checklist - SafetyCultureDa Li Chu7JPas encore d'évaluation

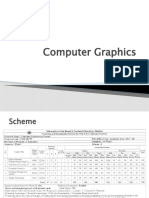

- Computer Graphics: Unit 1Document61 pagesComputer Graphics: Unit 1Kamini SalunkhePas encore d'évaluation

- Questions For Late Bloomers:: CBSE Ques. No. Chapter / Topic Marks Distribution of Marks Question WiseDocument12 pagesQuestions For Late Bloomers:: CBSE Ques. No. Chapter / Topic Marks Distribution of Marks Question WiseanshPas encore d'évaluation

- Question Paper For JTO Phase-I Data Communication: Fill in The Blanks/ Short Answer questions/True/False TypeDocument3 pagesQuestion Paper For JTO Phase-I Data Communication: Fill in The Blanks/ Short Answer questions/True/False Typerockingprad6066Pas encore d'évaluation

- Toshiba e Studio 206/256/306/356/406/456Document134 pagesToshiba e Studio 206/256/306/356/406/456Wangeesa Mihindupriya100% (4)

- Internet Programming With Delphi (Marco Cantu)Document14 pagesInternet Programming With Delphi (Marco Cantu)nadutPas encore d'évaluation

- 514 Advances in Core ImageDocument126 pages514 Advances in Core ImageDiamond LewisPas encore d'évaluation

- Oracle Hospitality OPERA Property Management: Workstation Setup Guide Release 5.5.0.24+Document42 pagesOracle Hospitality OPERA Property Management: Workstation Setup Guide Release 5.5.0.24+Ko Ko AungPas encore d'évaluation

- CSEC Jan 2011 Paper 1Document8 pagesCSEC Jan 2011 Paper 1R.D. KhanPas encore d'évaluation

- Mathematics As A Tool: Coding Theory: Math & Physics DepartmentDocument28 pagesMathematics As A Tool: Coding Theory: Math & Physics DepartmentTawki BakiPas encore d'évaluation

- Wi-Fi CERTIFIED Location OrientationDocument56 pagesWi-Fi CERTIFIED Location Orientationketu89Pas encore d'évaluation