Académique Documents

Professionnel Documents

Culture Documents

Post-Processing Your OVM/UVM Simulation Results

Transféré par

Gudipalii Ravi KumarTitre original

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

Post-Processing Your OVM/UVM Simulation Results

Transféré par

Gudipalii Ravi KumarDroits d'auteur :

Formats disponibles

Post-Processing Your OVM/UVM Simulation Results

Cadence Incisive Enterprise Simulator provides advanced debug capabilities through SimVision, which enables users to visualize the convergence of the SystemVerilog testbench and the design under test (DUT). SimVision offers SystemVerilog Universal Verification Methodology (UVM)/Open Verification Methodology (OVM) users the ability to post-process and provides a broad set of advanced features to this audience.

Introduction

Contents

Introduction ................................. 1 Preparing for Post-Process Debug ..................... 3 Using Saved Data for Post-Processing ............................ 4 Accessing Instance-Specific Data .................. 4 Accessing Class Objects in the Class Browser ..................... 6 Other Verification Methodologies ............................ 6 Learning More ............................. 7

Many users of SystemVerilog have relied upon $display statements for obtaining debug information for their verification testbenches. However, this approach takes debug back two decades. Starting in the 9.2 version of Cadence Incisive Enterprise Simulator, this is no longer required. You can take advantage of the advanced debug capabilities provided by SimVision to both interactively debug and post-process your verification environments. By using this new approach, you can visualize the convergence of your SystemVerilog testbench and the design under test (DUT), even if that DUT contains Verilog, VHDL, and SystemC code. This transaction level of abstraction allows the verification engineer and the design engineer to more easily discuss the design and testbench intent, which enables a more efficient path to Silicon Realization.1 SimVision supports the two most common use models for debug. The first use model is to perform interactive simulation with SimVision to display simulation results, set break points, and interact with the DUT while running the simulation. The other common use model is to run simulation in batch mode, record data to a waveform database, and then analyze the results after simulation is complete. This latter use model presents challenges when trying to post-process results when the DUT is being driven by a class-based verification environment, such as the Open Verification Methodology (OVM) or Universal Verification Methodology (UVM). In a traditional module-based testbench environment, the hierarchy of the design and verification testbench is known at time zero since the modulebased environment is elaborated into the simulation image. OVM/UVM, like other class-based verification environments, are quasi-static. This means that

For more information on Silicon Realization, please refer to the whitepaper on http://www.eda360.com.

Post-Processing Your OVM/UVM Simulation Results

the verification hierarchy does not exist until it is constructed during runtime simulation, and once constructed, the verification hierarchy does not change. Since it does not exist until constructed, the simulation image created during elaboration does not contain the verification environment hierarchy. SimVision takes advantage of the quasi-static nature of OVM/UVM to display the verification hierarchy along with the design hierarchy. This hierarchy is available after the build phase of the OVM/UVM environment. Figure 1 shows the verification hierarchy at time zero, before the UVM build phase is complete. You will notice that uvm _ top _ levels does not have any children.

Figure 1: UVM Hierarchy Prior to Construction

Figure 2 shows the hierarchy after the build phase. In this image, uvm _ top _ levels has children and displays the quasi-static verification hierarchy.

Figure 2: UVM Hierarchy After Construction

www.cadence.com

Post-Processing Your OVM/UVM Simulation Results

Preparing for Post-Process Debug

Currently, objects cannot be probed until they are created. In order to probe the verification hierarchy to a waveform database, the build phase must be complete (as shown in Figure 2). Both OVM and UVM supply Tcl commands in simulation that allow you to stop at the end of the build phase. To reach this point, issue the following commands: For UVM: uvm _ phase stop _ at run run For OVM: ovm _ phase stop _ at run run The first command creates a breakpoint to stop at the beginning of the run phase. This is immediately after completing the end _ of _ elaboration phase of the OVM/UVM environment. The run command advances simulation to the breakpoint set in the first command. After the run command, the verification hierarchy is constructed. You can now access the quasi-static hierarchy and perform operations on the dynamically created data. There are two operations of importance for you. The first is to probe the verification hierarchy. The second is to create a snapshot (after the build phase) of the simulation image that contains the quasi-static verification hierarchy. To probe the hierarchy, issue the following command: For UVM: probe -create -shm worklib.uvm _ pkg::uvm _ top _ levels -depth all For OVM: probe -create -shm worklib.ovm _ pkg::ovm _ top _ levels -depth all This probes the entire verification hierarchy to a waveform database. If you have not already created a waveform database, a default database called ncsim.shm is created. Now you will want to save a simulation snapshot to use during post-processing. To do this, issue the following commands: run -clean save -simulation debug The run clean command makes sure that the simulation is in a state that can be saved to disk. The save simulation command creates a saved snapshot image called debug. Now you can run simulation to completion. All of these steps can be automated by using the input command script capability to irun. To do this for UVM, create the following command script: uvm _ phase -stop _ at run run probe -create -shm worklib.uvm _ pkg::uvm _ top _ levels -depth all run -clean save -simulation debug run If you save this into a Tcl script called debug.tcl, it can be added to the irun command line, as follows: irun <irun options> -input debug.tcl

www.cadence.com

Post-Processing Your OVM/UVM Simulation Results

Upon completion of simulation, all of the data necessary for viewing the verification environment in a postprocessing mode is now ready. The necessary data is the debug.tcl file, the ncsim.shm database, and the postconstruction simulation snapshot. If additional probes are required for full debug, they can be added to the debug. tcl file. It should be noted that probing the scope containing the OVM/UVM top level will not include the dynamic hierarchy. In order for the dynamic hierarchy to be recorded to the database, you must explicitly probe it as in the above example.

Using Saved Data for Post-Processing

To get the post-processing debug environment with SimVision, the snapshot must be used along with the waveform database. To make sure you have the correct snapshot name, use the ncls utility with the -snapshot option to get a listing of your snapshots. If you ran simulation with irun and saved the snapshot as listed in the previous section, the snapshot name will be worklib.debug:sv. You then use this on the SimVision command line along with the waveform database, as follows: simvision snapshot worklib.debug:sv ncsim.shm This starts SimVision with the saved debug snapshot loaded and the waveform data recorded to the SHM database overlaid on the snapshot hierarchy. This allows you to view the design and testbench hierarchy, the class inheritance hierarchy, the recorded signal hierarchy including transactions recorded from OVM/UVM, and source with values annotated for instances of class objects.

Accessing Instance-Specific Data

Once the snapshot and database are loaded, you can see the OVM/UVM top level listed in the Design Browser window. Due to current limitations, the OVM/UVM instance hierarchy does not display in the scope tree, as it does in interactive simulation, but all of the data is available. To access this, simply select the OVM/UVM top level, and in the right-hand signal list, expand uvm_top_levels/ovm_top_levels to access the OVM/UVM components. Figure 3 shows the UVM component hierarchy expanded in the signal list portion of the Design Browser window.

Figure 3: UVM Hierarchy Expanded in Signal List in Post-Process Mode

You can now select a component and display the waveform for it, and send the instance to the Source Browser to view instance-specific source value annotation. You can also select data members from an object and display the data members in the source as well. This will show the instance in the source window with the declaration line of the data member highlighted. Figure 4 shows a component displayed in the waveform window with the object referenced by the bus monitor expanded to show the data members of the object.

www.cadence.com

Post-Processing Your OVM/UVM Simulation Results

Figure 4: Bus Monitor Displayed in Waveforms with Object Expanded

When viewing an object in the source, you can enable source value annotation to display values for data members of that object instance. In Figure 5, the source for the bus monitor instance is displayed.

Figure 5: Bus Monitor Instance with Value Annotation

Notice that line 131 is highlighted. This is because the data member named data was selected in the waveform prior to sending it to the Source Browser.

www.cadence.com

Post-Processing Your OVM/UVM Simulation Results

Accessing Class Objects in the Class Browser

You can view the class inheritance hierarchy by using the Class Browser sidebar. When viewing this in a postprocess mode, any instance of a selected class definition is displayed in the Objects column of the sidebar. Selecting an instance in this column displays that instance in the source window. You can also access the Class Browser sidebar in the Design Browser window. In Figure 6, the Class Browser sidebar is displayed with an instance of the bus monitor selected. This shows the instance in the source region with value annotation for data members of that instance.

Figure 6: Object from Class Browser Displayed in Source

Other Verification Methodologies

The steps described above are specific to the supported OVM/UVM. For other methodologies, a similar use model would apply. For this you would have to: Run simulation past the verification environment construction phase Save a simulation snapshot to create the debug snapshot Probe the verification hierarchy, as follows: probe create shm <path to verification hierarchy root> -depth all This would result in a waveform database that contains the objects created in the quasi-static verification hierarchy and data that it generates. When post-processing this data, SimVision should be invoked with both the snapshot saved after construction and the waveform database that was generated. You can then traverse the design hierarchy to find the root of the verification environment, and access the verification hierarchy components from this root in the Design Browser signal list. You can also view the inheritance hierarchy and select instances of classes for display in waveforms and source.

www.cadence.com

Post-Processing Your OVM/UVM Simulation Results

Learning More

SimVision offers SystemVerilog OVM/UVM users a broad set of advanced features beyond the ability to postprocess. A great way to become familiar with these is to either schedule a lunch-and-learn session with your local account team or access the SimVision workshop in the Incisive Verification Kit. The Incisive Verification Kit is supplied with the Incisive Enterprise Simulator XL starting with the 9.2 release. When you access the Kit, you will find a reference design and verification environment that will allow you to explore SystemVerilog class debug, tracing of dynamic objects, OVM/UVM-specific features, key Tcl commands, instructions on how to access the automatic transaction recording, using the stripe charts, using the heap analysis, and TLM debug. For information on installing and using the Incisive Verification Kit, please refer to the Incisive Verification Kits Getting Started manual online or contact your local support engineer.

Cadence is transforming the global electronics industry through a vision called EDA360. With an application-driven approach to design, our software, hardware, IP, and services help customers realize silicon, SoCs, and complete systems efficiently and profitably. www.cadence.com

2011 Cadence Design Systems, Inc. All rights reserved. Cadence and the Cadence logo are registered trademarks of Cadence Design Systems, Inc., All rights reserved. Cadence and the Cadence logo are registered trademarks of Cadence Design Systems, Inc., All rights reserved. Cadence and the Cadence logo are registered trademarks of Cadence Design Systems, Inc. 21761 12/11 MK/DM/PDF

Vous aimerez peut-être aussi

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryD'EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryÉvaluation : 3.5 sur 5 étoiles3.5/5 (231)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)D'EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Évaluation : 4.5 sur 5 étoiles4.5/5 (120)

- Grit: The Power of Passion and PerseveranceD'EverandGrit: The Power of Passion and PerseveranceÉvaluation : 4 sur 5 étoiles4/5 (588)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaD'EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaÉvaluation : 4.5 sur 5 étoiles4.5/5 (266)

- The Little Book of Hygge: Danish Secrets to Happy LivingD'EverandThe Little Book of Hygge: Danish Secrets to Happy LivingÉvaluation : 3.5 sur 5 étoiles3.5/5 (399)

- Never Split the Difference: Negotiating As If Your Life Depended On ItD'EverandNever Split the Difference: Negotiating As If Your Life Depended On ItÉvaluation : 4.5 sur 5 étoiles4.5/5 (838)

- Shoe Dog: A Memoir by the Creator of NikeD'EverandShoe Dog: A Memoir by the Creator of NikeÉvaluation : 4.5 sur 5 étoiles4.5/5 (537)

- The Emperor of All Maladies: A Biography of CancerD'EverandThe Emperor of All Maladies: A Biography of CancerÉvaluation : 4.5 sur 5 étoiles4.5/5 (271)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeD'EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeÉvaluation : 4 sur 5 étoiles4/5 (5794)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyD'EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyÉvaluation : 3.5 sur 5 étoiles3.5/5 (2259)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersD'EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersÉvaluation : 4.5 sur 5 étoiles4.5/5 (344)

- Team of Rivals: The Political Genius of Abraham LincolnD'EverandTeam of Rivals: The Political Genius of Abraham LincolnÉvaluation : 4.5 sur 5 étoiles4.5/5 (234)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreD'EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreÉvaluation : 4 sur 5 étoiles4/5 (1090)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceD'EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceÉvaluation : 4 sur 5 étoiles4/5 (895)

- Her Body and Other Parties: StoriesD'EverandHer Body and Other Parties: StoriesÉvaluation : 4 sur 5 étoiles4/5 (821)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureD'EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureÉvaluation : 4.5 sur 5 étoiles4.5/5 (474)

- The Unwinding: An Inner History of the New AmericaD'EverandThe Unwinding: An Inner History of the New AmericaÉvaluation : 4 sur 5 étoiles4/5 (45)

- The Yellow House: A Memoir (2019 National Book Award Winner)D'EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Évaluation : 4 sur 5 étoiles4/5 (98)

- On Fire: The (Burning) Case for a Green New DealD'EverandOn Fire: The (Burning) Case for a Green New DealÉvaluation : 4 sur 5 étoiles4/5 (73)

- Hawk RoostingDocument11 pagesHawk RoostingMOKIBUL ISLAM MOKIPSPas encore d'évaluation

- Abstract - Freezing Point Depression Is ADocument5 pagesAbstract - Freezing Point Depression Is AMinahPas encore d'évaluation

- ESL BOOKS - IELTS Academic Writing Task 1 Vocabulary by ESL Fluency - PreviewDocument7 pagesESL BOOKS - IELTS Academic Writing Task 1 Vocabulary by ESL Fluency - Previewanirudh modhalavalasaPas encore d'évaluation

- Program - PPEPPD 2019 ConferenceDocument3 pagesProgram - PPEPPD 2019 ConferenceLuis FollegattiPas encore d'évaluation

- Green ManagementDocument58 pagesGreen ManagementRavish ChaudhryPas encore d'évaluation

- Engineering Council of South Africa: 1 PurposeDocument5 pagesEngineering Council of South Africa: 1 Purpose2liePas encore d'évaluation

- PTE Self Study - Lfib v3.0Document57 pagesPTE Self Study - Lfib v3.0Jewel AhmedPas encore d'évaluation

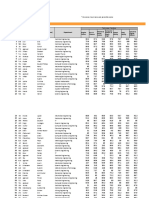

- Innoventure List of Short Listed CandidatesDocument69 pagesInnoventure List of Short Listed CandidatesgovindmalhotraPas encore d'évaluation

- Application For Bir Number: Board of Inland RevenueDocument2 pagesApplication For Bir Number: Board of Inland Revenuedinesh007Pas encore d'évaluation

- Chimney Design UnlineDocument9 pagesChimney Design Unlinemsn sastryPas encore d'évaluation

- Project Demo On Pet Shop: Group Members: Muhammad Talha Malik Shamook Saad Muhammad HamzaDocument10 pagesProject Demo On Pet Shop: Group Members: Muhammad Talha Malik Shamook Saad Muhammad HamzaRaja Saad0% (1)

- Finding The Right Place On The Map: Central and Eastern European Media Change in A Global PerspectiveDocument306 pagesFinding The Right Place On The Map: Central and Eastern European Media Change in A Global PerspectiveIntellect BooksPas encore d'évaluation

- Practice Revision Questions Number SystemsDocument1 pagePractice Revision Questions Number SystemsRavi Prasaath IXPas encore d'évaluation

- Session ManagementDocument4 pagesSession ManagementahamedyaseenPas encore d'évaluation

- Diamondfreezemel32r E82eenDocument11 pagesDiamondfreezemel32r E82eenGILI RELIABILITYPas encore d'évaluation

- Waqas Ahmed C.VDocument2 pagesWaqas Ahmed C.VWAQAS AHMEDPas encore d'évaluation

- ExtPascal Advanced Configuration Complete Eng v4Document31 pagesExtPascal Advanced Configuration Complete Eng v4jofreezePas encore d'évaluation

- Lip Prints: IntroductionDocument4 pagesLip Prints: Introductionkaran desaiPas encore d'évaluation

- Unity FlowchartDocument1 pageUnity Flowchartcippolippo123Pas encore d'évaluation

- How To Use SQL Servers Extended Events and Notifications White Paper 24902Document20 pagesHow To Use SQL Servers Extended Events and Notifications White Paper 24902Santosh KadamPas encore d'évaluation

- Nonverbal Communication (BAS105 UNIT-4)Document16 pagesNonverbal Communication (BAS105 UNIT-4)sachinnonofficialmailPas encore d'évaluation

- Operating Temperature Considerations and Performance PDFDocument12 pagesOperating Temperature Considerations and Performance PDFccprado1Pas encore d'évaluation

- Things To Remember When Writing Your Conference Proposal AbstractDocument2 pagesThings To Remember When Writing Your Conference Proposal AbstractBalizkoa BadaezpadakoaPas encore d'évaluation

- WEEK8 VI MAPARAAN WHLP Q2 - March1 4 2021Document8 pagesWEEK8 VI MAPARAAN WHLP Q2 - March1 4 2021Arjay M. VirayPas encore d'évaluation

- Ad For Natbps WB PDFDocument7 pagesAd For Natbps WB PDFrajpal singhPas encore d'évaluation

- Tables Log ActivatedDocument575 pagesTables Log ActivateddcdiasPas encore d'évaluation

- Fall 2011 COP 3223 (C Programming) Syllabus: Will Provide The Specifics To His SectionDocument5 pagesFall 2011 COP 3223 (C Programming) Syllabus: Will Provide The Specifics To His SectionSarah WilliamsPas encore d'évaluation

- Synthesis of Isoamyl AcetateDocument3 pagesSynthesis of Isoamyl AcetateClaire TiongsonPas encore d'évaluation

- Structural Dynamics: 10/11/2017 Dynamic Analysis 1Document110 pagesStructural Dynamics: 10/11/2017 Dynamic Analysis 1Mohammed Essam ShatnawiPas encore d'évaluation

- NSF Science and Engineering Indicators 2014Document600 pagesNSF Science and Engineering Indicators 2014Adrian ArizmendiPas encore d'évaluation