Académique Documents

Professionnel Documents

Culture Documents

HSSN Assignment

Transféré par

Peace Peazman PeasCopyright

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

HSSN Assignment

Transféré par

Peace Peazman PeasDroits d'auteur :

HSSN individual assgn 2011

INDIVIDUAL ASSIGNMENT TECHNOLOGY PARK MALAYSIA HARDWARE SOFTWARE SYSTEMS AND NETWORKS-(CT014-3-1) INTAKE : UC2F1107IT NAME : K.T.B TP022209 WEIGHTAGE : 50%

1|Page

HSSN individual assgn 2011 Contents

TABLE OF FIGURES ........................................................................................................................................ 3 GANTT CHART ............................................................................................................................................... 4 ABSTRACT...................................................................................................................................................... 5 INTRODUCTION ............................................................................................................................................. 6 CHAPTERS/SECTIONS .................................................................................................................................... 7 Section 1: Operating systems ................................................................................................................... 7 Creation and handling of threads in Unix ............................................................................................. 7 Types of scheduling mechanisms.......................................................................................................... 8 Pre-emptive vs Non-preemptive algorithms ........................................................................................ 8 Section2: Registers .................................................................................................................................. 10 Reasons for registers........................................................................................................................... 10 Register size ........................................................................................................................................ 10 Types of registers ................................................................................................................................ 10 CONCLUSION............................................................................................................................................... 13 FREQUENTLY ASKED QUESTIONS (FAQ)...................................................................................................... 14 LIMITATIONS/EXTENSIONS ......................................................................................................................... 15 APPENDIX .................................................................................................................................................... 16 Memory management ........................................................................................................................ 16 REERENCES .................................................................................................................................................. 21

2|Page

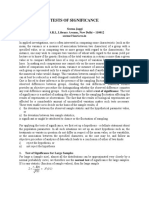

HSSN individual assgn 2011 TABLE OF FIGURES

Figure i.0 : inside the computer .................................................................................................................. 16 Figure ii: The central processing Unit ......................................................................................................... 17 Figure iii:Process state diagram .................................................................................................................. 17 Figure iv : PCB.............................................................................................................................................. 18 Figure v : Cache and registers ..................................................................................................................... 18 Figure vi : Register types ............................................................................................................................. 19 Figure vii : inside the 8086 CPU .................................................................................................................. 19

3|Page

HSSN individual assgn 2011 GANTT CHART

4|Page

HSSN individual assgn 2011 ABSTRACT

I would like to share some knowledge I have about the UNIX operating system process control management. Areas discussed in this documentation include among other; the scheduling mechanisms employed in UNIX, creation and handling of processes it even extends to cover on problems faced and their solutions. Besides that, this report will cover the computer systems architecture usage of registers in modern computers. Areas discussed would be reasons for registers, types of registers, register size and a few other topics.

5|Page

HSSN individual assgn 2011 INTRODUCTION

We use computers more often in our lives that they becoming our daily part of life. Many of us use computers to carry out our daily activities, but most of us dont know how the computer process/threads management operates. Many also dont know of computer registers and their uses. People dont even bother to know this things as they believe its technicians staff hence even if their computer displays a small error they seek technician intervention which comes at a cost. In this report I will be addressing this issue, this report is about operating systems and computer systems architecture. Under operating systems I will be focusing on process control management on UNIX operating system .it is a multitasking, multi-user computer operating system that was first developed in assembly language. Since it began to escape from AT&T's Bell Laboratories in the early 1970's, the success of the UNIX operating system has led to many different versions: recipients of the (at that time free) UNIX system code all began developing their own different versions in their own, different, ways for use and sale. Universities, research institutes, government bodies and computer companies all began using the powerful UNIX system to develop many of the technologies which today are part of a UNIX system. UNIX was created in the late 1960s, in an effort to provide a multiuser, multitasking system for use by programmers. The philosophy behind the design of UNIX was to provide simple, yet powerful utilities that could be pieced together in a flexible manner to perform a wide variety of tasks. It comprises three parts: The kernel, the standard utility programs, and the system configuration files. I looked into registers under the systems architecture and how they operate. The word register itself refers to a collection of records kept in one place but in computer terms it refers to temporary storage locations used to hold data and instructions executed in the central processing unit. Registers are located in the processor not in RAM as they are memory locations themselves

6|Page

HSSN individual assgn 2011 CHAPTERS/SECTIONS

Section 1: Operating systems

The term process or processing describes the action of taking something through an established and usually routine set of procedures or steps to convert it from one form to another. In computing, a process is an instance of a computer program that is being executed .A process control management is how software applications are executed in a computer it is carried out by the operating system. In this report, I would be discussing about process control management in Unix-Linux operating system. Processes are given small CPU time slices by an algorithm that reduces to round robin for CPU-bound jobs, although there is a priority scheme. There's no preemption of one process by another when running in kernel mode. A process may relinquish the CPU because it's waiting for I/O (including I/O due to page faults) or because its time slice has expired. Every process has a scheduling priority associated with it; the lower the numerical priority, the more likely is the process to run. Processes are created; When the system boots; by the actions of another process, by the actions of a user, by the actions of a batch manager

Creation and handling of threads in Unix

Processes terminate; normally exit, voluntarily on an error, involuntarily on an error, terminated (killed) by the actions a user or a process. UNIX maintains the information about a process in two areas: the process table and the user area, or u area. The user area of a process is located at the upper end of the process's address space and is accessible only when running in kernel mode. It contains a pointer to the process table entry; signal settings, the descriptor table, current working directory, unmasks setting. It may be swapped to disk. Only a few system commands are needed when implementing a process control in UNIX. They are: int getpid();int getppid();int fork();int exit(int);int wait(int*);int exec(); fork is the call which is used to create a new process The basic unit of software that the operating system deals with in scheduling the work done by the processor is either a process or a thread, depending on the operating system. Each process is represented in the operating system as a process control block see (figure 1.3) below

7|Page

HSSN individual assgn 2011

Types of scheduling mechanisms

A scheduling algorithm is the algorithm which dictates how much CPU time is allocated to Processes and Threads. Scheduling algorithms aim to achieve fairness, efficiency, maximizing throughput and minimizing turnaround time. The main reason for CPU scheduling is to utilize its resources 100% to never let it be idle, another reason is the need for processes to perform I/O operations in the normal course of computation. Since I/O operations ordinarily require orders of magnitude more time to complete than do CPU instructions, multiprogramming systems allocate the CPU to another process whenever a process invokes an I/O operation. There are quite a number of scheduling algorithms and they can be categorized into two being pre-emptive and non pre-emptive algorithms.

Pre-emptive vs Non-preemptive algorithms

Preemptive algorithms

are driven by the notion of prioritized computation. The process

with the highest priority should always be the one currently using the processor. If a process is currently using the processor and a new process with a higher priority enters, the ready list, the process on the processor should be removed and returned to the ready list until it is once again the highest-priority process in the system. Processes releases CPU upon receiving a command. Some of the pre-emptive algorithms examples are; round robin, multilevel queue and multilevel feedback queue. In round robin the ready queue is treated like a circular queue and kept as a FIFO; With MLQ, each process is permanently assigned to one queue based on type, priority etc. In multilevel feedback queue processes are separated by CPU burst time.

Non pre-emptive algorithms are designed so that once a process enters the running state (is allowed a process); it is not removed from the processor until it has completed its service time. Some of the examples are; shortest job first (SJF), first come first serve (FCFS) also known as first in first out (FIFO) and priorities. FIFO strategy assigns priority to processes in the order in which they request the processor. The process that requests the CPU first is allocated the CPU first. When a process comes in, add its PCB to the tail of ready queue. When running process terminates, dequeue the process (PCB) at head of ready queue and run it. In priority scheduling, processes are allocated to the CPU on the basis of an externally assigned priority. The key to the performance of priority scheduling

8|Page

HSSN individual assgn 2011

is in choosing priorities for the processes. Lastly SJF maintain the ready queue in order of increasing job lengths So far pre-emptive algorithms proves to be the best as compared to non pre-emptive algorithms in my own point of view as they allocate less waiting time for process threads

9|Page

HSSN individual assgn 2011

Section2: Registers

Reasons for registers

A register is temporary high speed storage located in the CPU that holds the data the processor is currently working on. Most modern computer processors contain more than one kind of registers. Register is a special- purpose memory. This memory is vital for moving data in and out of the main memory and to process the data. When CPU executes the instructions, there is a transfer of information between various units of the computer system. CPU uses these registers to handle the process of execution effectively and efficiently. They are a part of the central processing unit but cannot be considered as a part of main memory. They can hold only one piece of data at a time. Registers receive the information, hold it temporarily and pass it on as directed by the control unit.

Register size

Various members of the 80x 86 families have different register sizes. The number of registers that a CPU has and the size of each (number of bits) help determine the power and speed of a CPU Registers are normally measured by the number of bits they can hold, for example, an "8bit register" or a "32-bit register". Understanding the size of registers and the data that you can place in them is very important when using assembler. A 32-bit Intel or compatible processor has three native data sizes that can be used by the normal integral instructions, BYTE, WORD, and DWORD corresponding to 8-bit, 16-bit and 32-bit.

Types of registers

Modern x86 computer processors have eight 32-bit general purpose registers, as depicted in Figure 4: register types. Registers work under the direction of the control unit to accept, hold, and transfer instructions or data and perform arithmetic or logical comparisons at high speed. The control unit uses a data storage register the way a store owner uses a cash register as a temporary, convenient place to store what is used in transactions. A central processing unit contains different kinds of registers that can be classified accordingly to their content or instructions that operate in them. There are eight(8) general purpose registers in most modern processors namely; Base Register (EBX), Counter Register (ECX),Data Register (EDX),Source Index (ESI),Destination Index (EDI), Base Pointer (EBP),Stack Pointer (ESP),The accumulator

10 | P a g e

HSSN individual assgn 2011

register (EAX) refer figure 2.2: Inside the 8086 CPU below. Here is the purpose of each register explained in detail Accumulators are registers that can be used for arithmetic, logical, shift, rotate, or other similar operations. Early computers had only one accumulator by default. There were related special purpose registers that contained the source data for an accumulator. Accumulators were replaced with data registers and general purpose registers. They reappeared in the first microprocessors. The instruction set gives the accumulator special preference as a calculation registers. For example, all nine basic operations (ADD, ADC, AND, CMP, OR, SBB, SUB, TEST, and XOR) have special one-byte opcodes for operations between the accumulator and a constant. Specialized operations, such as multiplication, division, sign extension, and BCD correction can only occur in the accumulator. Address registers store the addresses of specific memory locations. Often many integer and logic operations can be performed on address registers directly (to allow for computation of addresses). Data registers are used for temporary scratch storage of data, as well as for data manipulations (arithmetic, logic, etc.). The data register, EDX, is most closely tied to the accumulator. Instructions that deal with over sized data items, the data register are the 64-bit extension of the accumulator in a way. Index registers are used to provide more flexibility in addressing modes, allowing the programmer to create a memory address by combining an address register with the contents of an index register (with displacements, increments, decrements, and other options). In some processors, there are specific index registers (or just one index register) that can only be used only for that purpose. In some processors, any data register, address register, or general register (or some combination of the three) can be used as an index register. Program counter, the program counter points to the memory location that stores the next executable instruction. Branching is implemented by making changes to the program counter. Usually software only indirectly changes the program counter (for example, a

11 | P a g e

HSSN individual assgn 2011

JUMP instruction will insert the operand into the program counter). An assembler has a location counter, which is an internal pointer to the address (first byte) of the next location in storage (for instructions, data areas, constants, etc.) while the source code is being converted into object code. Base registers are used to segment memory. Effective addresses are computed by adding the contents of the base or segment register to the rest of the effective address computation. In some processors, any register can serve as a base register. In some processors, there are specific base or segment registers that can only be used for that purpose. In some processors with multiple base or segment registers, each base or segment register is used for different kinds of memory accesses (such as a segment register for data accesses and a different segment register for program accesses). In 16-bit mode, the base register, EBX, acts as a general-purpose pointer. Besides the specialized ESI, EDI, and EBP registers

12 | P a g e

HSSN individual assgn 2011

CONCLUSION

The eight general-purpose registers in the x86 processor family each have a unique purpose. Each register has special instructions and opcodes which make fulfilling this purpose more convenient or efficient. The UNIX operating system handles its programs with a very memory efficient memory management system. It is able to run large programs without the need to have large physical memory which is the Random Access Memory (RAM). This in turn, will benefit the users of the UNIX operating system. This is because firstly, the user does not have to buy larger RAM which can be expensive. Secondly, the user will be able to run more programs simultaneously as the UNIX operating system has the ability to manage many programs and processes well ineffectively

13 | P a g e

HSSN individual assgn 2011 FREQUENTLY ASKED QUESTIONS (FAQ)

1. What are different types of CPU registers? 2. What is the advantage of using a CPU register for temporary data? 3. How does a CPU use the registers? 4. What is the main purpose of registers? 5. What CPU scheduling algorithm is used by UNIX? 6. How are processes created in Unix operating system 7. What are properties of a CPU scheduling algorithm to be best suited for real time scheduling? 8. What is real time processing? 9. What are processes or threads? 10. What does fork() do in UNIX?

14 | P a g e

HSSN individual assgn 2011 LIMITATIONS/EXTENSIONS

The registers in a standard CPU is considered as volatile memory. When there is sudden power cut, then the data stored in the registers will be lost. Limitations 1. Size of Random Access Memory When a program is run, it will occupy space on the RAM. Because of its fixed amount of RAM in computer, only a limited amount of programs are able to be run at one time. Even though, the user will be able to upgrade the RAM, the user might still be limited to the amount of RAM the operating system can detect due to its32 bit.2. 2. Size of Virtual Memory The amount of virtual memory in the operating system is limited to the amount allocated. Although user has the ability to manipulate the amount of virtual memory, it is still limited by the space in the disk.3. 3. Speed of Random Access Memory Even though it may take a the CPU a very small amount of time to carry out its instruction cycle, the computer will be slowed down by the time it take the information that is already processed to be retrieved by the RAM

15 | P a g e

HSSN individual assgn 2011 APPENDIX

Memory management

Figure i.0 : inside the computer

16 | P a g e

HSSN individual assgn 2011

Figure ii: The central processing Unit

Figure iii:Process state diagram

Pointer to parent process Pointer area to child process

17 | P a g e

HSSN individual assgn 2011

Process state Program counter Register save area Memory limits Priority information Accounting information Pointer to files and other I/O resources

Figure iv : PCB

Figure v : Cache and registers

18 | P a g e

HSSN individual assgn 2011

Figure vi : Register types

Figure vii : inside the 8086 CPU

19 | P a g e

HSSN individual assgn 2011

20 | P a g e

HSSN individual assgn 2011 REERENCES

HowStuffWorks "Types of Computer Memory". 2011. HowStuffWorks "Types of Computer Memory". [ONLINE] Available at: http://

http://computer.howstuffworks.com/computer-memory2.htm. [Accessed 30 August 2011]. The Art of Picking Intel Registers. 2011. The Art of Picking Intel Registers. [ONLINE] Available at:http://www.swansontec.com/sregisters.html. [Accessed 02 September 2011]. Cooling, J.E. Software Design for Real-Time Systems. Chapman & Hall, London, UK: 1995. Stallings, William. Operating Systems: Internals and Design Principles. Upper Saddle River, NJ: Prentice Hall, 1998. What is UNIX? 2011. What is UNIX? [ONLINE] Available

at:http://www.unix.org/what_is_unix.html. [Accessed 10 September 2011]. Process Control in UNIX. 2011. Process Control in UNIX. [ONLINE] Available at: http://cs.oberlin.edu/~jdonalds/341/lecture05.html. [Accessed 10 September 2011] Operating Systems: CPU Scheduling. 2011. Operating Systems : CPU Scheduling. [ONLINE] Available

at:http://www1bpt.bridgeport.edu/sed/projects/cs503/Spring_2001/kode/os/schedulin g.htm#context1. [Accessed 10 September 2011] Scheduling in the 4.2BSD Unix OS. 2011. Scheduling in the 4.2BSD Unix OS. [ONLINE] Available at:http://www.cim.mcgill.ca/~franco/OpSys-304-427/lecturenotes/node46.html. [Accessed 10 September 2011] Operating Systems : CPU Scheduling. 2011. Operating Systems : CPU Scheduling. [ONLINE] Available

at:http://www1bpt.bridgeport.edu/sed/projects/cs503/Spring_2001/kode/os/schedulin g.htm#npVsP. [Accessed 10 September 2011]

21 | P a g e

Vous aimerez peut-être aussi

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)D'EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Évaluation : 4.5 sur 5 étoiles4.5/5 (119)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaD'EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaÉvaluation : 4.5 sur 5 étoiles4.5/5 (265)

- The Little Book of Hygge: Danish Secrets to Happy LivingD'EverandThe Little Book of Hygge: Danish Secrets to Happy LivingÉvaluation : 3.5 sur 5 étoiles3.5/5 (399)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryD'EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryÉvaluation : 3.5 sur 5 étoiles3.5/5 (231)

- Grit: The Power of Passion and PerseveranceD'EverandGrit: The Power of Passion and PerseveranceÉvaluation : 4 sur 5 étoiles4/5 (587)

- Never Split the Difference: Negotiating As If Your Life Depended On ItD'EverandNever Split the Difference: Negotiating As If Your Life Depended On ItÉvaluation : 4.5 sur 5 étoiles4.5/5 (838)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeD'EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeÉvaluation : 4 sur 5 étoiles4/5 (5794)

- Team of Rivals: The Political Genius of Abraham LincolnD'EverandTeam of Rivals: The Political Genius of Abraham LincolnÉvaluation : 4.5 sur 5 étoiles4.5/5 (234)

- Shoe Dog: A Memoir by the Creator of NikeD'EverandShoe Dog: A Memoir by the Creator of NikeÉvaluation : 4.5 sur 5 étoiles4.5/5 (537)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyD'EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyÉvaluation : 3.5 sur 5 étoiles3.5/5 (2219)

- The Emperor of All Maladies: A Biography of CancerD'EverandThe Emperor of All Maladies: A Biography of CancerÉvaluation : 4.5 sur 5 étoiles4.5/5 (271)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreD'EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreÉvaluation : 4 sur 5 étoiles4/5 (1090)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersD'EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersÉvaluation : 4.5 sur 5 étoiles4.5/5 (344)

- Her Body and Other Parties: StoriesD'EverandHer Body and Other Parties: StoriesÉvaluation : 4 sur 5 étoiles4/5 (821)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceD'EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceÉvaluation : 4 sur 5 étoiles4/5 (894)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureD'EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureÉvaluation : 4.5 sur 5 étoiles4.5/5 (474)

- The Unwinding: An Inner History of the New AmericaD'EverandThe Unwinding: An Inner History of the New AmericaÉvaluation : 4 sur 5 étoiles4/5 (45)

- The Yellow House: A Memoir (2019 National Book Award Winner)D'EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Évaluation : 4 sur 5 étoiles4/5 (98)

- Overhead Water Tank Structural AnalysisDocument28 pagesOverhead Water Tank Structural Analysiscollins unanka100% (3)

- On Fire: The (Burning) Case for a Green New DealD'EverandOn Fire: The (Burning) Case for a Green New DealÉvaluation : 4 sur 5 étoiles4/5 (73)

- Dball-Gm5 en Ig Cp20110328aDocument18 pagesDball-Gm5 en Ig Cp20110328aMichael MartinezPas encore d'évaluation

- Love Your Design Getting Started GuideDocument14 pagesLove Your Design Getting Started GuideOnalevel100% (9)

- Internal Controls and Risk Management: Learning ObjectivesDocument24 pagesInternal Controls and Risk Management: Learning ObjectivesRamil SagubanPas encore d'évaluation

- 5 Tests of Significance SeemaDocument8 pages5 Tests of Significance SeemaFinance dmsrdePas encore d'évaluation

- Alaris 8210 and 8220 SpO2 Module Service ManualDocument63 pagesAlaris 8210 and 8220 SpO2 Module Service ManualNaveen Kumar TiwaryPas encore d'évaluation

- Philippine Popular Culture in HEIsDocument9 pagesPhilippine Popular Culture in HEIsNokie TunayPas encore d'évaluation

- Understanding Otdr Understanding-otdr-po-fop-tm-aePo Fop TM AeDocument1 pageUnderstanding Otdr Understanding-otdr-po-fop-tm-aePo Fop TM AeAgus RiyadiPas encore d'évaluation

- The Ethological Study of Glossifungites Ichnofacies in The Modern & Miocene Mahakam Delta, IndonesiaDocument4 pagesThe Ethological Study of Glossifungites Ichnofacies in The Modern & Miocene Mahakam Delta, IndonesiaEry Arifullah100% (1)

- Radiograph Evaluation ChecklistDocument2 pagesRadiograph Evaluation ChecklistZulfadli Haron100% (1)

- Packing, Transportation and Marketing of Ornamental FishesDocument16 pagesPacking, Transportation and Marketing of Ornamental Fishesraj kiranPas encore d'évaluation

- Transportation Geotechnics: Tirupan Mandal, James M. Tinjum, Tuncer B. EdilDocument11 pagesTransportation Geotechnics: Tirupan Mandal, James M. Tinjum, Tuncer B. EdilDaniel Juan De Dios OchoaPas encore d'évaluation

- Amber ToolsDocument309 pagesAmber ToolshkmydreamsPas encore d'évaluation

- Materials For Oxygen ServicesDocument4 pagesMaterials For Oxygen Services陳文鴻Pas encore d'évaluation

- Senior Design Projects 201-2020 - For Website - MEDocument5 pagesSenior Design Projects 201-2020 - For Website - MEYujbvhujgPas encore d'évaluation

- Employees' Job Satisfaction and Organizational Performance A Case of KSRTCDocument4 pagesEmployees' Job Satisfaction and Organizational Performance A Case of KSRTCEditor IJTSRDPas encore d'évaluation

- Mindfulness With Collegiate Gymnasts - Effects On Flow, Stress and Overall Mindfulness LevelsNicholas P. Cherupa,, Zeljka VidicDocument13 pagesMindfulness With Collegiate Gymnasts - Effects On Flow, Stress and Overall Mindfulness LevelsNicholas P. Cherupa,, Zeljka VidicGABRIELPas encore d'évaluation

- SOP Questionnaire GREDocument4 pagesSOP Questionnaire GREYuvraj GuptaPas encore d'évaluation

- Proposed - TIA - 1392 - NFPA - 221Document2 pagesProposed - TIA - 1392 - NFPA - 221Junior TorrejónPas encore d'évaluation

- 4.3 Structural Analysis 4.3.1 ModellingDocument8 pages4.3 Structural Analysis 4.3.1 Modellingdavid ROBALINOPas encore d'évaluation

- Manufacturing Processes (ME361) Lecture 13: Instructor: Shantanu BhattacharyaDocument28 pagesManufacturing Processes (ME361) Lecture 13: Instructor: Shantanu BhattacharyaSahil SundaPas encore d'évaluation

- Rules For Assigning Activity Points: Apj Abdul Kalam Technological UniversityDocument6 pagesRules For Assigning Activity Points: Apj Abdul Kalam Technological UniversityAnonymous KyLhn6Pas encore d'évaluation

- WORK ORDER TITLEDocument2 pagesWORK ORDER TITLEDesign V-Tork ControlsPas encore d'évaluation

- HR MasterlistDocument6 pagesHR MasterlistLeychelle AnnPas encore d'évaluation

- Syllabus Agri 2015Document248 pagesSyllabus Agri 2015parvathivignesh279Pas encore d'évaluation

- MST 2 ReviewerDocument4 pagesMST 2 ReviewerAizha NarioPas encore d'évaluation

- ISO 17000 2004 Terms & DefintionsDocument6 pagesISO 17000 2004 Terms & DefintionsSelvaraj SimiyonPas encore d'évaluation

- G String v5 User ManualDocument53 pagesG String v5 User ManualFarid MawardiPas encore d'évaluation

- Develop Network Monitoring System IP Subnet CalculatorDocument23 pagesDevelop Network Monitoring System IP Subnet CalculatorabiramanPas encore d'évaluation