Académique Documents

Professionnel Documents

Culture Documents

Laboratorio 5 Mapas de Karnaugh

Transféré par

Yesenia Jaime RoaCopyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

Laboratorio 5 Mapas de Karnaugh

Transféré par

Yesenia Jaime RoaDroits d'auteur :

Formats disponibles

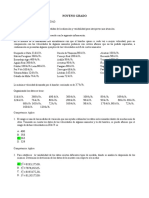

MAPA DE KARNAUGH

Para este laboratorio usamos 4 resistencias de 220 y compuertas, 7432 OR 7404 NOT 7408 AND AND La compuerta AND produce la multiplicacin lgica AND: esto es: la salida es 1 si la entrada A y la entrada B estn ambas en el binario 1: de otra manera, la salida es 0. OR La compuerta OR produce la funcin sumadora, esto es, la salida es 1 si la entrada A o la entrada B o ambas entradas son 1; de otra manera, la salida es 0. NOT El circuito NOT es un inversor que invierte el nivel lgico de una seal binaria. Produce el NOT, o funcin complementaria. COMPUERTAS LOGICAS Una compuerta lgica es un circuito lgico cuya operacin puede ser definida por una funcin del lgebra lgica. DISPLAY Perifrico de visualizacin de datos. Aunque se utiliza en ocasiones para referirse a la pantalla del monitor, su uso est ms ligado a los visores de caracteres de pequeo tamao. MAPA DE KARNAUGH El mapa de Karnaugh es un mtodo grfico que se utiliza para simplificar una ecuacin lgica para convertir una tabla de verdad a su circuito lgico correspondiente en un proceso simple y ordenado. TABLA DE LA VERDAD 8421 # X1 X2 X3 X4 0 0 0 0 0 1 0 0 0 1 2 0 0 1 0 3 0 0 1 1 4 0 1 0 0 5 0 1 0 1 6 0 1 1 0 7 0 1 1 1 8 1 0 0 0 9 1 0 0 1 DISPLAY A

1 0 1 1 0 1 1 1 1 1

B

1 1 1 1 1 0 0 1 1 1

C

1 1 0 1 1 1 1 1 1 1

D

1 0 1 1 0 1 1 0 1 1

E

1 0 1 0 0 0 1 0 1 0

F

1 0 0 0 1 1 1 0 1 1

G

0 0 1 1 1 1 1 0 1 1

TABLA A X1X2/X3X4 0 0 0 1 1 1 1 0

0 1 0 X 1

0 0 0 1 X 1

1 1 1 1 X X

1 1 1 1 X X

TABLA B X1X2/X3X4 0 0 0 1 1 1 1 0

0 1 1 X 1

0 0 1 0 X 1

1 1 1 1 X X

1 1 1 0 X X

TABLA C X1X2/X3X4 0 0 0 1 1 1 1 0

0 1 1 X 1

0 0 1 1 X 1

1 1 1 1 X X

1 1 0 1 X X

TABLA D X1X2/X3X4 0 0 0 1 1 1 1 0

0 1 0 X 1

0 0 0 1 X 1

1 1 1 0 X X

1 1 1 1 X X

TABLA E X1X2/X3X4 0 0 0 1 1 1 1 0

0 1 0 X 1

0 0 0 0 X 0

1 1 0 0 X X

1 1 1 1 X X

TABLA F X1X2/X3X4 0 0 0 1 1 1 1 0

0 1 1 X 1

0 0 0 1 X 1

1 1 1 0 X X

1 1 1 1 X X

TABLA G X1X2/X3X4 0 0 0 1 1 1 1 0

0 1 0 X 1

0 0 0 0 X 0

1 1 0 0 X X

1 1 1 1 X X

INTRODUCCION Cuando se tiene una funcin lgica con su tabla de verdad y se desea implementar esa funcin de la manera ms econmica posible se utiliza el mapa de karnaugh y con base a ello se puede hacer el diseo de este laboratorio.Esto es equivalente a resolver las simplificaciones por teoremas; Los mapas de Karnaugh pueden aplicarse a dos, tres, cuatro y cinco variables. Para ms variables, la simplificacin resulta tan complicada que conviene en ese caso utilizar teoremas mejor. Para efectos de clase, veremos las simplificaciones de dos, tres y cuatro variables.

OBJETIVOS Por medio de los mapas de karnaugh y simplificacin por mtodo de ley de Morgan y algebra booleana deseamos hacer un circuito de un display de 7 segmentos y con base a ello aprender a disear.

CONCLUSIONES Se diseo el circuito del display de 7 segmentos por medio de los mapas de karnaugh y simplificacin por mtodo de ley de Morgan y algebra booleana se obtuvo los nmeros del 19 por medio de cambios en el dip switch anteriormente vistos en las tablas de la verdad y por medio del diagrama del SG del display. Gracias al mapa de karnaugh aprendimos a simplificar de una manera sencilla y a disear circuitos y poder hacer los montajes en protoboard.

BIBLIOGRAFIA http://www.abcdatos.com/tutoriales/tutorial/l5820.html http://www.mastermagazine.info/termino/4686.php http://www.unicrom.com/Dig_mapa-karnaugh.asp

LABORATORIO # 3

Presentado a: Guillermo Leyva

Presentado por: Yecenia Jaime Roa Daniel Herrera Andres Ramirez

COMPUERTAS LOGICAS Bogot D.C 1 de septiembre del 2010

Vous aimerez peut-être aussi

- Contador Con Flip-FlopDocument19 pagesContador Con Flip-FlopMiguel Angel CasiquePas encore d'évaluation

- Flip Flop ContadorDocument9 pagesFlip Flop ContadorAndrésCabreraSoriaPas encore d'évaluation

- Mapas de KarnaughDocument7 pagesMapas de KarnaughBlanca GarcoiaPas encore d'évaluation

- Contadores MonolíticosDocument15 pagesContadores MonolíticosJean Carlo ArrietaPas encore d'évaluation

- Flip FlopDocument4 pagesFlip FlopErick Esteban NarvaezPas encore d'évaluation

- Implementacion Del Minesweeper Con Un Tablero de LedsDocument16 pagesImplementacion Del Minesweeper Con Un Tablero de LedsRenzo Moscoso BasalduaPas encore d'évaluation

- PracticaDocument12 pagesPracticaIsa RochaPas encore d'évaluation

- Divisor de Frecuencia y Contador de RizoDocument2 pagesDivisor de Frecuencia y Contador de RizoEddy Fernando Queca CadizPas encore d'évaluation

- Un Circuito Secuencial Puede Entenderse Simplemente Como Un Circuito Combinacional en El Cuallas Salidas Dependen Tanto de Las Entradas Como de Las Salidas en Instantes AnterioresDocument5 pagesUn Circuito Secuencial Puede Entenderse Simplemente Como Un Circuito Combinacional en El Cuallas Salidas Dependen Tanto de Las Entradas Como de Las Salidas en Instantes AnterioresNeiry FrancoPas encore d'évaluation

- Electronica Diagramas Circuitos - Cargador para Baterías NiMH de FloteDocument2 pagesElectronica Diagramas Circuitos - Cargador para Baterías NiMH de FloteCarlos RamosPas encore d'évaluation

- El Flip FlopDocument17 pagesEl Flip FlopLuigi Jair Torres MirandaPas encore d'évaluation

- Los Flip FlopDocument18 pagesLos Flip FloproxanaPas encore d'évaluation

- Mapas de KarnaughDocument7 pagesMapas de KarnaughNathaly Freire LopezPas encore d'évaluation

- El Lenguaje Ensamblador Del PIC16F84A PDFDocument20 pagesEl Lenguaje Ensamblador Del PIC16F84A PDFregistrogsPas encore d'évaluation

- Puertos de I/O Pic16f877Document30 pagesPuertos de I/O Pic16f877anon_376202896Pas encore d'évaluation

- Laboratorio Flip FlopDocument3 pagesLaboratorio Flip FlopVykthor LópezPas encore d'évaluation

- Comandos PicDocument49 pagesComandos PicEmilio Salazar HernandezPas encore d'évaluation

- Práctica 5 - Flip-Flops, Contadores Síncronos - 1Document2 pagesPráctica 5 - Flip-Flops, Contadores Síncronos - 1Juan Camilo GonzalesPas encore d'évaluation

- Bies TableDocument37 pagesBies TableLuz Karina Lopez SaavedraPas encore d'évaluation

- PRACTICA 2 Sistemas Digitales IIDocument5 pagesPRACTICA 2 Sistemas Digitales IIArmando Alvarado YucraPas encore d'évaluation

- Diferencia Entre Los Tipos de Fl¡p-Flop y LatchDocument15 pagesDiferencia Entre Los Tipos de Fl¡p-Flop y LatchOvanio MolinaPas encore d'évaluation

- Set de Instrucciones Microcontrolador PICDocument16 pagesSet de Instrucciones Microcontrolador PICCristian GasconPas encore d'évaluation

- Proyecto de Arquitectura de ComputadorasDocument9 pagesProyecto de Arquitectura de ComputadorasfabriickdPas encore d'évaluation

- Semana 03 Mapas de KarnaughDocument22 pagesSemana 03 Mapas de KarnaughAndy Samanez RiveraPas encore d'évaluation

- FLIP FlopsDocument9 pagesFLIP FlopsDelfino OlivaresPas encore d'évaluation

- Diseño Contadores SíncronosDocument5 pagesDiseño Contadores SíncronosNirza Carolina Torres BlancoPas encore d'évaluation

- Ensayo de Sistemas DigitalesDocument7 pagesEnsayo de Sistemas DigitalesIgnacio Moreno0% (1)

- Fli-Flops, Registros y ContadoresDocument15 pagesFli-Flops, Registros y ContadoresOmar XocaPas encore d'évaluation

- Curso HC908 Flash Parte IIDocument23 pagesCurso HC908 Flash Parte IIEnrique Julian ConchaPas encore d'évaluation

- Guia Flip Flop VHDLDocument16 pagesGuia Flip Flop VHDLViridiana Fernandez CarreonPas encore d'évaluation

- Módulo ADC Del Pic16f877Document14 pagesMódulo ADC Del Pic16f877Roberto ArredondoPas encore d'évaluation

- Contadores Flip-FlopDocument3 pagesContadores Flip-FlopLaura Georgina Barragán RodríguezPas encore d'évaluation

- Lenguaje C Orientado A Microcontroladores Rev 1Document42 pagesLenguaje C Orientado A Microcontroladores Rev 1David Shure XivPas encore d'évaluation

- Contadores y RegistrosDocument19 pagesContadores y RegistrosElymar91Pas encore d'évaluation

- T Lab #03. Laboratorio Diseño Digital - 030218Document34 pagesT Lab #03. Laboratorio Diseño Digital - 030218luis carrasquelPas encore d'évaluation

- DSP Tiva C Usac Ingenieria Comunicaciones 4Document6 pagesDSP Tiva C Usac Ingenieria Comunicaciones 4Samayoa JosePas encore d'évaluation

- 7 Dispositivos Integrados PDFDocument105 pages7 Dispositivos Integrados PDFcchristt2584Pas encore d'évaluation

- Diseño circuitos hidráulicos GRAFCETDocument8 pagesDiseño circuitos hidráulicos GRAFCETroomelPas encore d'évaluation

- Práctica 8 FlipFlop JKDocument6 pagesPráctica 8 FlipFlop JKEdgar PinalesPas encore d'évaluation

- Notas Del PIC16F84Document132 pagesNotas Del PIC16F84Thecar DarkPas encore d'évaluation

- Diseño de circuitos neumáticos mediante método cascadaDocument145 pagesDiseño de circuitos neumáticos mediante método cascadaDarcooPas encore d'évaluation

- Aplicaciones Basicas DSP320F2812 PDFDocument222 pagesAplicaciones Basicas DSP320F2812 PDFGiovanni José Huacasi SupoPas encore d'évaluation

- Circuitos Digitales SecuencialesDocument7 pagesCircuitos Digitales SecuencialesJose Martinez EstradaPas encore d'évaluation

- Contador de MooreDocument6 pagesContador de MooreErnesto VásquezPas encore d'évaluation

- Diseño de Un Contador Sincronico Con Flip PDFDocument8 pagesDiseño de Un Contador Sincronico Con Flip PDFFrancisco Flores LunaPas encore d'évaluation

- Mapas de KarnaughDocument10 pagesMapas de KarnaughCarlos CastilloPas encore d'évaluation

- Pantalla LCDDocument30 pagesPantalla LCDWalter RiveroPas encore d'évaluation

- Diseño Flip FlopDocument8 pagesDiseño Flip FlopLuis GonzálezPas encore d'évaluation

- Informe 08 - Pds FdatoolDocument28 pagesInforme 08 - Pds FdatoolBrayan Omar GonzalesPas encore d'évaluation

- Registros Del PIC16F84ADocument15 pagesRegistros Del PIC16F84AMiller Stiven Espinosa MuñozPas encore d'évaluation

- Flip Flop JKDocument6 pagesFlip Flop JKMigue PicazoPas encore d'évaluation

- Codificadores, DecodificadoresDocument41 pagesCodificadores, DecodificadoresJose Manuel Sillet DelgadoPas encore d'évaluation

- Tema 6 Teclado Digital DecimalDocument4 pagesTema 6 Teclado Digital Decimal2mercedesPas encore d'évaluation

- Flip FlopDocument9 pagesFlip FloppaulinodosantosPas encore d'évaluation

- Trabajo Practico Flip-Flops y Circuitos Secuenciales PDFDocument10 pagesTrabajo Practico Flip-Flops y Circuitos Secuenciales PDFDonaldo Leonel Vargas AnguloPas encore d'évaluation

- Digital - Palabra PDFDocument7 pagesDigital - Palabra PDFJuan Antonio Clemente GonzalezPas encore d'évaluation

- Implementación Mapas KarnaughDocument8 pagesImplementación Mapas KarnaughCarlitos YenerisPas encore d'évaluation

- Laboratorio 1 Circuitos LogicosDocument11 pagesLaboratorio 1 Circuitos LogicosJuanes JecoPas encore d'évaluation

- Informe Circuitos CombinacionalesDocument6 pagesInforme Circuitos CombinacionalesJorge Martinez GómezPas encore d'évaluation

- ADQUISICIÓN DE SWITCHES INDUSTRIALES PARA FIBRA ÓPTICADocument70 pagesADQUISICIÓN DE SWITCHES INDUSTRIALES PARA FIBRA ÓPTICAYesenia Jaime RoaPas encore d'évaluation

- RE. Re. ExigenciasDocument1 pageRE. Re. ExigenciasYesenia Jaime RoaPas encore d'évaluation

- Taller 2Document4 pagesTaller 2Yesenia Jaime RoaPas encore d'évaluation

- Taller 2Document4 pagesTaller 2Yesenia Jaime RoaPas encore d'évaluation

- Flujo de Caja - Luis-David - PesimistaDocument5 pagesFlujo de Caja - Luis-David - PesimistaYesenia Jaime RoaPas encore d'évaluation

- Taller Sistemas de PotenciaDocument2 pagesTaller Sistemas de PotenciaYesenia Jaime RoaPas encore d'évaluation

- Spring y CrepesDocument2 pagesSpring y CrepesYesenia Jaime RoaPas encore d'évaluation

- Resumen de Superposicion y TransformacionDocument5 pagesResumen de Superposicion y TransformacionYesenia Jaime RoaPas encore d'évaluation

- Taller AntenasDocument2 pagesTaller AntenasYesenia Jaime RoaPas encore d'évaluation

- Feminismo y PeronismoDocument242 pagesFeminismo y PeronismoAlberto FlorianPas encore d'évaluation

- Detalles Experimentalesy ConclusionesDocument5 pagesDetalles Experimentalesy ConclusionesJuan LaurentePas encore d'évaluation

- Las Otras Verdades Del TDAHDocument16 pagesLas Otras Verdades Del TDAHRamoncito77Pas encore d'évaluation

- Trabajo de La Cultura Taina y DominicanaDocument28 pagesTrabajo de La Cultura Taina y DominicanaBhakti RPas encore d'évaluation

- Especialidad de Arte de Contar HistoriaDocument2 pagesEspecialidad de Arte de Contar HistoriaViviana CalderonPas encore d'évaluation

- Preterito Pluscuamperfecto IndicativoDocument4 pagesPreterito Pluscuamperfecto Indicativocr_carlosPas encore d'évaluation

- 150 Preguntas JuegoDocument8 pages150 Preguntas JuegoLuis NarvaezPas encore d'évaluation

- Clase 5-La-Gramatica-1Document30 pagesClase 5-La-Gramatica-1AaronPas encore d'évaluation

- Religion La Oveja PerdidaDocument6 pagesReligion La Oveja PerdidaShirley Prissila Castro Ortiz100% (2)

- Cloud Strife, SOLDIER - Una Experiencia en Final Fantasy VII RemakeDocument16 pagesCloud Strife, SOLDIER - Una Experiencia en Final Fantasy VII RemakeMelissa CabasPas encore d'évaluation

- Enfoque de GéneroDocument13 pagesEnfoque de GéneroMaximus TomayllaPas encore d'évaluation

- Cardesin - La Misión Del Artista PDFDocument20 pagesCardesin - La Misión Del Artista PDFOrdoñez Amador Ana LuciaPas encore d'évaluation

- Desarriollo y Ha Unidad 4Document11 pagesDesarriollo y Ha Unidad 4Marylu GonzalezPas encore d'évaluation

- Mapa Gerencia y AdministracionDocument3 pagesMapa Gerencia y AdministracionGianella Guerra CruzPas encore d'évaluation

- Auditoría Del Ciclo de Ventas Y CobranzaDocument4 pagesAuditoría Del Ciclo de Ventas Y CobranzaGreisy Berroa100% (7)

- Contaminación Del Rio YuracyacuDocument4 pagesContaminación Del Rio YuracyacuAnonymous PF1YlZ100% (3)

- Pasaportes DiplomáticosDocument14 pagesPasaportes Diplomáticoswelni canarioPas encore d'évaluation

- Tesis Estudio de Pre Factibilidad para La para La Impelentacion de Un Restaurante de Pollo A La Brasas - UnlockedDocument371 pagesTesis Estudio de Pre Factibilidad para La para La Impelentacion de Un Restaurante de Pollo A La Brasas - UnlockedJaime Huaracha Velasquez100% (1)

- Legalidad y Autencidad Del Elemento Material ProbatorioDocument2 pagesLegalidad y Autencidad Del Elemento Material ProbatoriovictorPas encore d'évaluation

- Jesús nos invita a ser mejores personasDocument2 pagesJesús nos invita a ser mejores personasJhamil LopezPas encore d'évaluation

- Tesis Cú Sánchez Alma PatriciaDocument133 pagesTesis Cú Sánchez Alma PatriciaArleking No ExistePas encore d'évaluation

- Teoricos de Todo El Año Desgrabados de Psicopatología IDocument82 pagesTeoricos de Todo El Año Desgrabados de Psicopatología IJuanDualibePas encore d'évaluation

- Espacio AzorínDocument19 pagesEspacio AzorínJorge UrrutiaPas encore d'évaluation

- 1 CacuDocument26 pages1 CacuJorge Quispe RodasPas encore d'évaluation

- AcentuaciónDocument24 pagesAcentuaciónJph LibePas encore d'évaluation

- ConsecuenciasDocument2 pagesConsecuenciasMilgros AbramontePas encore d'évaluation

- Proyecto DeporteDocument5 pagesProyecto DeporteMarisa AlarconPas encore d'évaluation

- Quiz 14 Medidas de Variabilidad Nov 6Document2 pagesQuiz 14 Medidas de Variabilidad Nov 6Henry Lazaro CanoPas encore d'évaluation

- Las FARC-EP. El PCCC y El Movimiento BolivarianoDocument17 pagesLas FARC-EP. El PCCC y El Movimiento BolivarianoJorge Andrés Cortés Molina100% (1)

- Consejos para Vivir CastidadDocument1 pageConsejos para Vivir CastidadEdwan RojasPas encore d'évaluation