Académique Documents

Professionnel Documents

Culture Documents

Asm

Transféré par

SIRISHASIRIICopyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

Asm

Transféré par

SIRISHASIRIIDroits d'auteur :

Formats disponibles

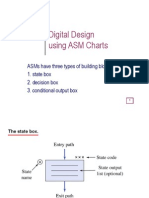

Chap 1 Digital Deisgn with ASM Chart

ASM Chart: Algorithmic staate chart can describe the behavior of the hardware with the step-by-step operations in precise units of time. 1.1 State Machine Charts

Fig. 1 Comonets of an ASM chart

Fig. 2 Example 1 of an ASM Block

Z1=A+BC=A+ABC

Fig. 3 Example 3 of an ASM Block (a) Parallel form

(b) Serial form

Fig. 4 Example 4 of an ASM

ASM charts composed only of rectangles and diamonds are said to describe Moore machines. ASM charts that also include ovals are said to describe Mealy machines.

Fig. 5 ASM with multi-bit output

Fig. 6 ASM with register transfer

Fig. 7 ASM with Decision

Fig. external status ASM Input

ASM

with

Fig. 9 Two ways to test multi-bit input ASM Outputs 1. External command outputs : Fig. 2

(a) External data input

(b) External status inputs

or Fig. 3. 2. External data outputs : register transfer as shown in Fig. 4. Conversion of a State Graph to an SM Chart

(a) State graph

(b) Equivalent ASM chart

(c) Timing Chart for ASM chart Fig. 10 An example of conversion Top-down design Pure behavioral example : childish division algorithm r1 = x; r2 = 0; while (r1>= y) { r1 =r1 y; r2 = r2 + 1; }

Fig. 11 Block diagram

A software algorithm can be translated into an ASM with the following rules: 1. Each assignment statement is written by itself in RTN in a unique rectangle that is not followed by a diamond. 2. Each if or while is translated into an empty rectangle with a diamond to implement the decision.

(a) Algorithmic state machine

(b) The ASM operation for x = 5 and y = 7

(c) The ASM operation for x = 14 and y = 7 Fig. 12 ASM for

software paradign (COMUTE1 at top)

(a) Algorithmic state machine

(b) The ASM operation for x = 14 and y = 7 Fig. 13 ASM for software paradign (COMUTE1 at top)

Eliminating state TEST

(a) Algorithmic state machine

(b) the ASM operation Fig. 14 Incorrect four-state division machine

(a) Algorithmic state machine

(b) the ASM operation Fig. 15 Correct four-state divison machine

(a) Algorithmic state machine

(b) the ASM operation Fig. 16 Incorrect user

interface (throws quotient away)

(a) Algorithmic state machine

(b) the ASM operation Fig. 17 Saving quotient in r3

Fig. 18 Handling quotient of zero

(a) Algorithmic state machine

(b) The operation for x = 14 and y = 7 Fig. 19 Incorrect rearrangement of states

(a) Algorithmic state machine

(b) The operation for x = 14 and y = 7 Fig. 20 Incorrect parallelization attempt

(a) Algorithmic state machine

(b) The operation for x = 14 and y = 7

(C) The operation for x = 7 and y = 7

(C) The operation for x = 5 and y = 7 Fig. 21 Correct parallelization

(b) The operation for x = 5 and y = 7 Fig. 22 Goto-less two-state childish division ASM

Fig. 23 Equivalent to figure 22 The hardware design from ASM

Fig. 24 System diagram

First hardware design

* ALU is inspired by the 74**181, PASSB is 101010 and DFFERENCE is 011001. Fig. 25 First methodical architecture

ns = ~ps&pb|ps&(rlgey|pb), ldr1 = 1, clrr2 = ~ps, incr2 = ps, ldr3 = ps, muxctr1 = ps, aluctr1[5] = ~ps, aluctr1[4] = ps, aluctr1[3] = 1, aluctr1[2] = 0, aluctr1[1] = ~ps, aluctr1[0] = ps, ready = ~ps.

Fig. 26 The 1st mixed ASM corresponding to figures 22 and 25

Fig. 27 The 2nd mixed ASM corresponding to figures 22 and 25

Second hardware design

Fig. 28 Central architecture design

IDLE 000, INIT 001, TEST 010, COMPUTE1 011, COMPUTE2 100.

Fig. 29 Mixed ASM corresponding to figure 12 and 28

Methodical versus central ALU architectures Central ALU What does computation? One ALU

Methodical Registers themselves or registers tied to dedicated muxes and ALUs Only one register All kinds Many Faster Higher

What ALU output connects to? What kind of register? Number of <- per clock cycle Speed Cost

Every register Enabled One Slower Lower

Homework 1: Dice game (Digital system design using VHDL) The rules of the game are as follows: (1) After the first roll of the dice, the player wins if the sum is 7 or 11. The player loses if the sum is 2, 3, or 12. Otherwise, the sum the player obtained on the first roll is referred to as a point, and he or she must roll the dice again. (2) On the second or subsequent roll of the dice, the player wins if the sum equals the point, and he or she loses if the sum is 7. Otherwise, the player must roll again until he or she finally wins or loses. The block diagram for dice game:

The algorithm flowchart and ASM chart for dice game

State graph for dice game controller:

Dice game with test bench

ASM chart for dice game test:

Vous aimerez peut-être aussi

- Asm ChartsDocument36 pagesAsm Chartskritika03Pas encore d'évaluation

- Chuong03 RegisterTransferSpecificationAndDesignDocument52 pagesChuong03 RegisterTransferSpecificationAndDesignHiếu NguyễnPas encore d'évaluation

- Ise324 Fundamentals of Modern Manufacturing Systems Final Exam 05.06.2011Document5 pagesIse324 Fundamentals of Modern Manufacturing Systems Final Exam 05.06.2011Mintu BoruahPas encore d'évaluation

- Design Problem Matlab Project TFDocument19 pagesDesign Problem Matlab Project TFhumayun azizPas encore d'évaluation

- PDFDocument24 pagesPDFOlga Joy Labajo GerastaPas encore d'évaluation

- Introduction To MATLABDocument30 pagesIntroduction To MATLABTrí Minh CaoPas encore d'évaluation

- ANSYS Function BuilderDocument3 pagesANSYS Function Buildermsb78Pas encore d'évaluation

- Antenna Azimuth Position Control System Modelling, AnalysisDocument30 pagesAntenna Azimuth Position Control System Modelling, AnalysisMbongeni Maxwell100% (3)

- MC0072 Sem3 Feb 2011 SmuDocument38 pagesMC0072 Sem3 Feb 2011 SmuNitin SivachPas encore d'évaluation

- Aaoc C321 642 C 2009 1Document2 pagesAaoc C321 642 C 2009 1Tushar GuptaPas encore d'évaluation

- The Speed Control of PMSMDocument5 pagesThe Speed Control of PMSMMehmet KırgözoğluPas encore d'évaluation

- Control Engineering MCQDocument4 pagesControl Engineering MCQZahid Yousuf0% (1)

- Sample CSE370 Final Exam Questions: Logic MinimizationDocument8 pagesSample CSE370 Final Exam Questions: Logic MinimizationQaseem HussainPas encore d'évaluation

- 9A02503 Control SystemsDocument4 pages9A02503 Control SystemssivabharathamurthyPas encore d'évaluation

- CA Assignment IIDocument9 pagesCA Assignment IISomesh ThakurPas encore d'évaluation

- Assignment 1 Design of Lead Compensator: ECTE942 Computer Controlled System: Assignment 1Document10 pagesAssignment 1 Design of Lead Compensator: ECTE942 Computer Controlled System: Assignment 1suryolPas encore d'évaluation

- Switching Theory and Logic DesignDocument6 pagesSwitching Theory and Logic DesignVijay MPas encore d'évaluation

- 21 - 2010 - Nov - R09 - STLDDocument8 pages21 - 2010 - Nov - R09 - STLDvasuvlsiPas encore d'évaluation

- Digital Design Using ASM ChartsDocument13 pagesDigital Design Using ASM ChartsswapnabojanapallyPas encore d'évaluation

- Oscillator Ads DesignDocument22 pagesOscillator Ads DesignayoubmalkiPas encore d'évaluation

- Asm 1Document5 pagesAsm 1Jagan RajendiranPas encore d'évaluation

- Digital 16 Marks.Document4 pagesDigital 16 Marks.Saranya PrabhuPas encore d'évaluation

- 09-Logic Design With ASM Chart-11-07Document58 pages09-Logic Design With ASM Chart-11-07Sandeep ChaudharyPas encore d'évaluation

- 07A4EC09 SWITCHINGTHEORYANDLOGICDESIGNfrDocument8 pages07A4EC09 SWITCHINGTHEORYANDLOGICDESIGNfrObula ReddyPas encore d'évaluation

- H Mechatronics All 2010Document32 pagesH Mechatronics All 2010zjtePas encore d'évaluation

- Week-4a Built in FunctionsDocument21 pagesWeek-4a Built in FunctionsKenanPas encore d'évaluation

- Sequence Generator To Derive 8-Phase Variable Reluctance Stepper MotorDocument15 pagesSequence Generator To Derive 8-Phase Variable Reluctance Stepper Motorgyty1043Pas encore d'évaluation

- ECE448 S12 In-Class MidtermDocument3 pagesECE448 S12 In-Class Midtermbilalhabib2001Pas encore d'évaluation

- 9A04401 Switching Theory & Logic DesignDocument4 pages9A04401 Switching Theory & Logic DesignsivabharathamurthyPas encore d'évaluation

- Chapter 7 HW Solution: Review QuestionsDocument7 pagesChapter 7 HW Solution: Review QuestionsAamir AltafPas encore d'évaluation

- PRO2 - 03e Instructions With REAL NumbersDocument7 pagesPRO2 - 03e Instructions With REAL NumbersSamehibrahemPas encore d'évaluation

- F Capacitor, Find The Appropriate Value ofDocument2 pagesF Capacitor, Find The Appropriate Value ofJoginder YadavPas encore d'évaluation

- TSExamples PDFDocument9 pagesTSExamples PDFKhalilPas encore d'évaluation

- Chap5&6. HWDocument11 pagesChap5&6. HWJesse Isaac McCallPas encore d'évaluation

- Digital System Design Question PaperDocument1 pageDigital System Design Question Papermujju433100% (1)

- ObjectArx AutocadDocument20 pagesObjectArx Autocadecobo243075Pas encore d'évaluation

- Finite State Machine Design: Prith Banerjee Ece C03 Advanced Digital Design Spring 1998Document47 pagesFinite State Machine Design: Prith Banerjee Ece C03 Advanced Digital Design Spring 1998VIKRAMPas encore d'évaluation

- Unit - 2 Central Processing Unit TOPIC 1: General Register OrganizationDocument13 pagesUnit - 2 Central Processing Unit TOPIC 1: General Register OrganizationRam Prasad GudiwadaPas encore d'évaluation

- Group Assignment 1Document3 pagesGroup Assignment 1geofrey fungoPas encore d'évaluation

- AE61Document4 pagesAE61Anima SenPas encore d'évaluation

- DSPAADocument2 pagesDSPAAsendilksPas encore d'évaluation

- 21 - 2011 - Dec - R09 - STLDDocument8 pages21 - 2011 - Dec - R09 - STLDvasuvlsiPas encore d'évaluation

- Introduccion Matlab EmilyDocument99 pagesIntroduccion Matlab EmilyGeorgina Violet RamirezPas encore d'évaluation

- Motor Drive With Flexible Shaft Control SystemDocument32 pagesMotor Drive With Flexible Shaft Control Systemعدي القهالي100% (2)

- Laboratory Exercise 11: Implementing Algorithms in HardwareDocument3 pagesLaboratory Exercise 11: Implementing Algorithms in HardwareTuân PhạmPas encore d'évaluation

- STLD 2009 RegularDocument4 pagesSTLD 2009 RegularrangerPas encore d'évaluation

- CSD Practical MannualDocument35 pagesCSD Practical MannualitsurturnPas encore d'évaluation

- 2 Year System Dynamics Sheet 6Document4 pages2 Year System Dynamics Sheet 6Yasser BahaaPas encore d'évaluation

- hw7 SolDocument5 pageshw7 SolIvanildo Gomes100% (1)

- MCS 012Document5 pagesMCS 012S.M. FarhanPas encore d'évaluation

- Optimal and Pid Controller For Controlling CameraDocument10 pagesOptimal and Pid Controller For Controlling CameraaliramezanidehajPas encore d'évaluation

- Feedback and Control Systems Lab ManualDocument72 pagesFeedback and Control Systems Lab Manualmamaw231Pas encore d'évaluation

- TE 2003&2008 PatternDocument623 pagesTE 2003&2008 PatternAshashwatmePas encore d'évaluation

- EXp2 SC19B158Document5 pagesEXp2 SC19B158Abeer KhatriPas encore d'évaluation

- Feedback Control Systems: Dr. Basil Hamed Electrical Engineering Islamic University of GazaDocument43 pagesFeedback Control Systems: Dr. Basil Hamed Electrical Engineering Islamic University of GazaSalmaanCadeXaajiPas encore d'évaluation

- Advanced Digital Systems DesignDocument12 pagesAdvanced Digital Systems DesignlawrencerajasekaranPas encore d'évaluation

- Online Tutorial - PROCESS DYNAMICS AND NUMERICAL METHODS by Kunal KaranDocument5 pagesOnline Tutorial - PROCESS DYNAMICS AND NUMERICAL METHODS by Kunal KaranSIRISHASIRIIPas encore d'évaluation

- Online Tutorial - PROCESS DYNAMICS AND NUMERICAL METHODS by Kunal KaranDocument5 pagesOnline Tutorial - PROCESS DYNAMICS AND NUMERICAL METHODS by Kunal KaranSIRISHASIRIIPas encore d'évaluation

- 04658475Document6 pages04658475SIRISHASIRIIPas encore d'évaluation

- QPSK Modulation and Error Correcting CodesDocument21 pagesQPSK Modulation and Error Correcting CodesSIRISHASIRIIPas encore d'évaluation

- Multi Rate 1Document22 pagesMulti Rate 1pra_zara2637Pas encore d'évaluation

- GRE Word ThesaurusDocument137 pagesGRE Word ThesaurusPhanidhar GubbalaPas encore d'évaluation

- The History of The Automobile: By: RohitDocument32 pagesThe History of The Automobile: By: RohitSIRISHASIRIIPas encore d'évaluation

- Top 10 Countries by Quality of Overall InfrastructureDocument1 pageTop 10 Countries by Quality of Overall InfrastructureSIRISHASIRIIPas encore d'évaluation

- Should We Expect To Feel As If We Understand Consciousness?: Mark C. PriceDocument12 pagesShould We Expect To Feel As If We Understand Consciousness?: Mark C. PriceSIRISHASIRIIPas encore d'évaluation

- Lecture Notes: Lecture 2.4: Basic DC-DC ConverterDocument3 pagesLecture Notes: Lecture 2.4: Basic DC-DC Converteralawi747594Pas encore d'évaluation

- Introduction To Networks - Module Practice and QuizDocument4 pagesIntroduction To Networks - Module Practice and QuizFaical BitamPas encore d'évaluation

- 3GPP TR - 125942v110000pDocument137 pages3GPP TR - 125942v110000ppontoeengenhariaPas encore d'évaluation

- Series Resonance - GATE Study Material in PDFDocument6 pagesSeries Resonance - GATE Study Material in PDFTestbook BlogPas encore d'évaluation

- User Manual PE-6000Document32 pagesUser Manual PE-6000kaung kyel zin aung zaw moePas encore d'évaluation

- An Interleaved High-Power Flyback Inverter For Photovoltaic ApplicationsDocument14 pagesAn Interleaved High-Power Flyback Inverter For Photovoltaic ApplicationsBastianHerreraBugueñoPas encore d'évaluation

- Stem Creator Manual English PDFDocument53 pagesStem Creator Manual English PDFDaniel SantiagoPas encore d'évaluation

- Uk Fat 2017Document178 pagesUk Fat 2017Christopher J MillsPas encore d'évaluation

- M3000ADocument10 pagesM3000AAdacia Mineiro Lima100% (1)

- ConnectorsDocument268 pagesConnectorsAdrian GeambasuPas encore d'évaluation

- Execution Unit (EU) : Instruction Queue, and The Instruction Pointer. It Has The Task of Making Sure That The BusDocument10 pagesExecution Unit (EU) : Instruction Queue, and The Instruction Pointer. It Has The Task of Making Sure That The BusPradeep RanaPas encore d'évaluation

- Catalogo Q2 2022Document668 pagesCatalogo Q2 2022iperlux7Pas encore d'évaluation

- Luobinsen High Power Charger 150-240kWDocument1 pageLuobinsen High Power Charger 150-240kWJuan Manuel RamírezPas encore d'évaluation

- Tpa3110d2 PDFDocument36 pagesTpa3110d2 PDFAndres AlegriaPas encore d'évaluation

- Data Communications and Computer NetworkDocument68 pagesData Communications and Computer NetworkBarnababas BeyenePas encore d'évaluation

- Recording Electric Guitars & Bass Guitars PDFDocument5 pagesRecording Electric Guitars & Bass Guitars PDFATekneciPas encore d'évaluation

- Do-254 WPDocument10 pagesDo-254 WPMazen OmerPas encore d'évaluation

- 850 Fast Secure Redundant CommunicationsDocument2 pages850 Fast Secure Redundant CommunicationsamruthkiranbabujiPas encore d'évaluation

- List of Abbreviations-A320Document58 pagesList of Abbreviations-A320Midun Mohan100% (1)

- AminoVU Amigo 7X DatasheetDocument4 pagesAminoVU Amigo 7X DatasheetMartinPas encore d'évaluation

- SFRA User GuideDocument133 pagesSFRA User Guideqweasdzxc122222100% (1)

- 100 Baset Crossover CableDocument7 pages100 Baset Crossover CableBeker BojanPas encore d'évaluation

- TECDIS Checklist en Rev 2 - 4Document10 pagesTECDIS Checklist en Rev 2 - 4ArjunroyEdwardPas encore d'évaluation

- Design Engineering ProjectDocument25 pagesDesign Engineering ProjectEngineers worldPas encore d'évaluation

- Quiz QuestionDocument1 pageQuiz QuestionmehediPas encore d'évaluation

- Diris Digiware Ac Multi Circuit Power Metering and Monitoring System Installation and Operating Manual 2023-05-542875 enDocument124 pagesDiris Digiware Ac Multi Circuit Power Metering and Monitoring System Installation and Operating Manual 2023-05-542875 enJames K. BitokPas encore d'évaluation

- Design of Circularly-Polarized Patch Antennas Using CST MICROWAVE STUDIODocument5 pagesDesign of Circularly-Polarized Patch Antennas Using CST MICROWAVE STUDIOMahdy Rahman0% (1)

- Chap.4 - Nonpilot Distance ProtectionDocument18 pagesChap.4 - Nonpilot Distance ProtectionJulios Charl Panuncialman TagupaPas encore d'évaluation

- Stpa 003Document25 pagesStpa 003Noel Alejandro Cordova RangelPas encore d'évaluation

- "ZNR" Transient/Surge Absorbers: Recommended Applications FeaturesDocument20 pages"ZNR" Transient/Surge Absorbers: Recommended Applications FeaturesFacundo FernandezPas encore d'évaluation