Académique Documents

Professionnel Documents

Culture Documents

Tema 5

Transféré par

Pablo Antonio Briones MaldonadoTitre original

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

Tema 5

Transféré par

Pablo Antonio Briones MaldonadoDroits d'auteur :

Formats disponibles

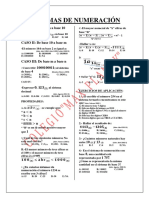

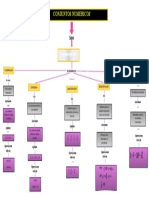

TECNOLOGA DE COMPUTADORES.

CURSO 2007/08 Inocente Snchez Ciudad

TEMA 5: SISTEMAS ARITMTICOS Y LGICOS.

5.1. Sumadores binarios.

Casi todo se hace con sumas: sumas, restas, productos, ... Concepto de acarreo. 5.1.1. Semisumador. Half Adder (HA). Entradas de 1 bit y salida SUMA y ACARREO.

Ai 0 0 1 1

Bi 0 1 0 1

Ci+1 0 0 0 1

Si 0 1 1 0

C i +1 = Ai Bi S i = Ai Bi

5.1.2. Sumador completo de 1 bit. Full Adder (FA). Como el semisumador, pero adems con entrada de acarreo.

Ai 0 0 0 0 1 1 1 1

Bi 0 0 1 1 0 0 1 1

Ci 0 1 0 1 0 1 0 1

Ci+1 0 0 0 1 0 1 1 1

Si 0 1 1 0 1 0 0 1 C i +1 = ( Ai Bi )C i + Ai Bi

C i +1 = ( Ai + Bi )C i + Ai Bi o bien S i = Ai Bi C i

C i +1 S i indica, codificado en binario, el resultado de la operacin y tambin el nmero de unos que hay en la terna de bits Ai , Bi y C i .

Se puede observar que el nmero binario compuesto por

Ai Bi Ci

SUMADOR ELEMENTAL O COMPLETO DE 1 BIT

Si Ci+1

FA

Considerando que el semisumador es un bloque que realiza la operacin XOR de dos variables y la operacin AND de las mismas variables, se puede construir un sumador completo de 1 bit a partir de dos semisumadores y una puerta OR segn la figura adjunta:

Tema 5: Sistemas aritmticos y lgicos 1

TECNOLOGA DE COMPUTADORES. CURSO 2007/08 Inocente Snchez Ciudad

Ai Bi

SEMISUMADOR

Ai Bi

Ci

SEMISUMADOR

Ai Bi Ci Si ( Ai Bi ) Ci

Ci

Ai Bi Si 0 0 1 1 0 0 1 1 Ci 0 1 0 1 0 1 0 1 Ci+1 0 1 1 1 0 0 0 1 Ri 0 1 1 0 1 0 0 1

Resultado

PUERTA OR

Ci+1

Restador de un bit. Se puede definir directamente la resta binario segn la siguiente tabla:

Mi 0 0 0 0 1 1 1 1

0 -1 -1 -2 +1 0 0 -1

Se puede observar que el resultado de la operacin est expresado en complemento a dos con los bits Ci+1 Ri

De igual forma se podra encontrar un sencillo circuito realizado con puertas para llevar a cabo esta funcin elemental de resta. 5.1.3. Sumador paralelo con acarreo serie. Usando n sumadores completos de 1 bis se construye un sumador completo de n bits. An-1 Cn Bn-1 Cn-1 A2 B2 A1 B1 A0 B0

FA

C3

C2

C1

C0

FA

FA

FA

Sn

Sn-1

S2

S1

S0

Si ts es el tiempo para realizar una suma y tc el tiempo para realizar un acarreo, resulta:

Dato en Tiempo

S0 ts

C1 tc

S1 ts + tc

C2 2 tc

Sn-1 Sn = Cn ts + (n-1) tc n ts

Inconveniente: necesita que acten los anteriores sumadores para que pueda actuar uno en particular. Se acumulan los retardos de propagacin.

Tema 5: Sistemas aritmticos y lgicos 2

TECNOLOGA DE COMPUTADORES. CURSO 2007/08 Inocente Snchez Ciudad

5.1.4. Sumador de arrastre anticipado. Los acarreos se generan en paralelo (simultneamente) con los resultados, evitando el problema de propagacin serie de los sumadores vistos anteriormente. Por tanto, estos sumadores son ms rpidos que los de acarreo serie. Teniendo en cuenta que el sumador total cumple las siguientes ecuaciones:

S i = Ai Bi C i C i +1 = ( Ai Bi ) Ci + Ai Bi = Pi Ci + Gi

Llamamos Pi al llamado trmino Propagador y Gi el llamado trmino Generador, definidos por:

Pi = Ai Bi y Gi = Ai Bi

Particularizando la expresin

C i +1 = Pi C i + Gi para i = 0, 1, 2, y 3 queda:

C1 = P0 C 0 + G0 C 2 = P1 C1 + G1 = P1 ( P0 C 0 + G0 ) + G1 = P1 P0 C 0 + P1 G0 + G1

C 3 = P2 P1 P0 C 0 + P2 P1 G 0 + P2 G1 + G 2

C 4 = P3 P2 P1 P0 C 0 + P3 P2 P1 G0 + P3 P2 G1 + P3 G2 + G3

Las salidas dependen de los datos de entradas y acarreos. Los acarreos dependen de los trminos propagadores y generadores. Los trminos propagadores y generadores dependen slo de los datos de entrada. Por tanto, las salidas dependen slo de los datos de entrada y otros que se obtienen directamente de stos, y todos se conocen desde el primer momento.

Tema 5: Sistemas aritmticos y lgicos 3

TECNOLOGA DE COMPUTADORES. CURSO 2007/08 Inocente Snchez Ciudad

ECUACIONES:

S i = Pi C i Pi = Ai Bi

Gi = Ai Bi

C1 = P0 C 0 + G0 C 2 = P1 P0 C 0 + P1 G0 + G1 C 3 = P2 P1 P0 C 0 + P2 P1 G0 + P2 G1 + G 2

C 4 = P3 P2 P1 P0 C0 + P3 P2 P1 G0 + P3 P2 G1 + P3 G2 + G3

C i +1 = Pi C i + Gi

Sumador de arrastre anticipado

Tema 5: Sistemas aritmticos y lgicos 4

TECNOLOGA DE COMPUTADORES. CURSO 2007/08 Inocente Snchez Ciudad

5.1.5. Sumador / Restador. Si S/R=0 la operacin es una suma. Las puertas XOR dejan pasar el dato sin ms. Si S/R=1, las puertas XOR invierten el dato de B, con lo que obtiene el complemento a 1, y, adems, introduce un 1 en el acarreo C0 para tener el complemento a 2. A3 A2 A1 A0 B3 B2 B1 B0

S/R

XOR XOR XOR XOR Si S/R = 0 Di = Bi

A3 C1

A2

A1

A0

D3

D2

D1

D0

SUMADOR COMPLETO DE 4 BITS

S3 S2 S1 S0 C0

Si S/R = 1 __ Di = Bi

S4

S3

S2

S1

S0

5.1.6. Sumador BCD. A3 A2 A1 A0 B3 B2 B1 B0

SUMADOR COMPLETO DE 4 BITS

C1 P3 P2 P1 P0 C0

CIRCUITO COMBINACIONAL 0 ACARREO 3 2 1 0 3 2 1 0 0

SUMADOR COMPLETO DE 4 BITS

S3 para:

S2

S1

S0

El circuito combinacional detecta que la suma es superior a 9 y da una seal que sirve a la vez

Tema 5: Sistemas aritmticos y lgicos 5

TECNOLOGA DE COMPUTADORES. CURSO 2007/08 Inocente Snchez Ciudad 1) Activar el acarreo posterior. 2) Restar 10 (o sumar 6, ya que los 4 bits menos significativos son los mismos) al nmero que d como salida el sumador de 4 bits si la suma est entre 10 y 15, ambos incluidos, o sumar el nmero 6 a los 4 bits que salen del primer sumador si la suma est entre 16 y 19. Puede parecer que es igual sumar 6 que restar 10. No, hay una diferencia de 16, pero si a un nmero en binario se le suma 16 (10000), los 4 bits menos significativos del resultado son los mismos, igual que si en decimal le sumamos a un nmero 10.000, las 4 ltimas cifras no cambian. La salida de acarreo del segundo sumador completo de 4 bits es irrelevante. El diseo de dicho circuito responde a la siguiente tabla de verdad:

0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 31

cuya solucin es:

C1 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 1 1 1 1 1 1

P3 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 0 0 0 0 0 1

P2 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1 0 0 0 0 1 1

P1 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 0 1

P0 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1

ACARREO 0 0 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 1 1 X X X X

ACARREO = C1 + P3 P1 + P3 P2

Los casos comprendidos entre 20 y 31, ambos incluidos, no se darn nunca, ya que el mayor nmero posible resulta de sumar 9 + 9 + 1 = 19, en el caso de sumar los mayores dgitos BCD y suponiendo entrada de acarreo de una etapa anterior.

Tema 5: Sistemas aritmticos y lgicos 6

TECNOLOGA DE COMPUTADORES. CURSO 2007/08 Inocente Snchez Ciudad

5.2. Multiplicador combinacional.

La multiplicacin aritmtica binaria coincide con el producto lgico. El resultado es 1 slo cuando ambos operando son 1. El algoritmo de multiplicacin utilizado en base decimal es tambin aplicable a base binaria. Ejemplo:

1 1 0 0 1 1 1 0 1 x 1 1 0 0 1 0 0 0 0 0 1 1 0 0 1 1 1 0 0 1 1 0 1 0 0 0 1 0 1

1 1 0 0 1 1 1 0 1 x 1 1 0 0 1 0 0 0 0 0 ------------0 1 1 0 0 1 1 1 0 0 1 -------------1 1 1 1 1 0 1 1 1 0 0 1 ---------------1 0 1 0 0 0 1 0 1

25 13 x 75 25 325

Sumas totales de 1 bit

Sumas parciales de 4 bits

Segn que las sumas parciales se realicen de golpe o por partes, hay dos circuitos que implementan esta operacin: uno con sumadores completos de 1 bit y otro con sumadores completos de varios bits, respectivamente.

Tema 5: Sistemas aritmticos y lgicos 7

TECNOLOGA DE COMPUTADORES. CURSO 2007/08 Inocente Snchez Ciudad

Multiplicador haciendo sumas totales con 1 bit

Tema 5: Sistemas aritmticos y lgicos 8

TECNOLOGA DE COMPUTADORES. CURSO 2007/08 Inocente Snchez Ciudad

Multiplicador haciendo sumas parciales de 4 bits

Tema 5: Sistemas aritmticos y lgicos 9

TECNOLOGA DE COMPUTADORES. CURSO 2007/08 Inocente Snchez Ciudad

5.3. Mdulos Lgicos.

5.3.1. Comparadores.

a1 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1

a0 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1

b1 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1

b0 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1

Z1 0 0 0 0 1 0 0 0 1 1 0 0 1 1 1 0

Z2 1 0 0 0 0 1 0 0 0 0 1 0 0 0 0 1

Z3 0 1 1 1 0 0 1 1 0 0 0 1 0 0 0 0

a1 a0

A>B Z1 A=B

COMPARADOR

b1 b0 A<B

Z2 Z3

Compara dos nmeros y segn cul sea mayor, o si son iguales, activa una salida, dejando desactivadas las otras dos

Se pueden hacer comparadores de nmeros binarios de 4 bits usando comparadores de 2 bits. Para ello, hay que tener en cuenta que al comparar dos nmeros de 4 bits, los dos bits ms significativos determinan cul de los dos nmeros es mayor, independientemente de los otros dos. Esto tambin ocurre en base 10. De la comparacin de dos nmeros A y B de 4 bits se pueden obtener los siguientes casos: A es mayor que B si los dos bits ms significativos de A son mayores que los dos bits ms significativos de B, independientemente de los dos bits menos significativos, o, si siendo iguales los dos bits ms significativos, los dos bits menos significativos de A son mayores que los dos bits menos significativos de B. A es igual que B si los dos bits ms significativos de A son iguales que los dos bits ms significativos de B, y, adems, los dos bits menos significativos de A son iguales que los dos bits menos significativos de B. A es menor que B si los dos bits ms significativos de A son menores que los dos bits ms significativos de B, independientemente de los dos bits menos significativos, o, si siendo iguales los dos bits ms significativos, los dos bits menos significativos de A son menores que los dos bits menos significativos de B. Si llamamos Z1M, Z2M y Z3M a las salidas A>B, A=B y A<B, respectivamente, del comparador de los bits ms significativos y Z1L, Z2L y Z3L a las salidas A>B, A=B y A<B, respectivamente, del comparador de los bits menos significativos, las salidas Z1 (A>B), Z2 (A=B) y Z3 (A<B), se pueden expresar como:

Z1 = Z1M + Z 2 M Z1L Z 2 = Z 2M Z 2 L Z 3 = Z 3M + Z 2 M Z 3 L

Un comparador de 4 bits con comparadores de 2 bits se puede construir de la siguiente forma:

Tema 5: Sistemas aritmticos y lgicos 10

TECNOLOGA DE COMPUTADORES. CURSO 2007/08 Inocente Snchez Ciudad

a3 a2

b3 b2

Z1M COMPARADOR DE Z2M NMEROS DE 2 BITS Z3M

A>B

A=B

a1 a0

Z1L COMPARADOR DE Z2L NMEROS DE 2 BITS Z3L Comparador de 4 bits con dos comparadores de 2 bits Los circuitos integrados comparadores pueden tener entradas >, =, < que transmiten el resultado de la entrada a la salida cuando las palabras de bits a comparar son iguales. Esto se utiliza para realizar comparaciones de un gran nmero de bits a partir de comparadores ms pequeos, colocndolos en cascada.

A<B

b1 b0

5.3.2. Detectores y generadores de paridad. Generador de paridad.

x1 0 0 0 0 1 1 1 1

x2 0 0 1 1 0 0 1 1

X3 0 1 0 1 0 1 0 1

P 0 1 1 0 1 0 0 1

I 1 0 0 1 0 1 1 0

x1 x2 x3

GENERADOR DE PARIDAD PAR

x1 x2 x3

GENERADOR DE PARIDAD IMPAR

P = x1 x 2 x3

I = x1 x2 x3

Los bits de paridad constituyen una informacin redundante que sirve para detectar errores en 1 bit. Si el bit de paridad es el correcto, no ha habido error. Si algn bit se cambia de valor, el bit de paridad da resultado incorrecto, ha habido un error, aunque no se sabe en qu bit. Sin embargo, la comprobacin de paridad no detecta error si se cambian dos bits. Si el bit errneo es el propio bit de paridad, sin que haya error en el resto de los bits, detecta error cuando en realidad no lo ha habido.

Tema 5: Sistemas aritmticos y lgicos 11

TECNOLOGA DE COMPUTADORES. CURSO 2007/08 Inocente Snchez Ciudad

Detector de paridad.

x1 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1

x2 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1

x3 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1

x4 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1

P 1 0 0 1 0 1 1 0 0 1 1 0 1 0 0 1

I 0 1 1 0 1 0 0 1 1 0 0 1 0 1 1 0

x1 x2 x3

GENERADOR DE PARIDAD DESCONOCIDA

x4

x1 x2 x3

DETECTOR DE PARIDAD

P = x1 x 2 x3 x 4

5.3.3. Conversores de cdigos.

I = x1 x 2 x3 x 4

a1 a2 . . . . an

CONVERSOR DE CDIGO

b1 b2 . . . . bm

Ejemplo: veamos un conversor de BCD a display de 7 segmentos

Tema 5: Sistemas aritmticos y lgicos 12

TECNOLOGA DE COMPUTADORES. CURSO 2007/08 Inocente Snchez Ciudad

a A

CONVERSOR DE CDIGO

a b c d e e f d g c f g b

BCD

A DISPLAY DE

7

D

SEGMENTOS

D 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1

C 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1

B 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1

A 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1

a 1 0 1 1 0 1 1 1 1 1 0 0 0 0 0 0

b 1 1 1 1 1 0 0 1 1 1 0 0 0 0 0 0

c 1 1 0 1 1 1 1 1 1 1 0 0 0 0 0 0

d 1 0 1 1 0 1 1 0 1 0 0 0 0 0 0 0

e 1 0 1 0 0 0 1 0 1 0 0 0 0 0 0 0

f 1 0 0 0 1 1 1 0 1 1 0 0 0 0 0 0

g 0 0 1 1 1 1 1 0 1 1 0 0 0 0 0 0

Se puede hacer un conversor de cdigo usando una pareja de mdulos: Decodificador y Codificador. Los cdigos pueden tener distinto nmero de bits. Ejemplo: convertir el cdigo A en el cdigo B segn la tabla adjunta:

Cdigo A

X1 0 0 1 1 X0 0 1 0 1

Cdigo B

Y1 0 1 1 0 Y0 1 0 1 0

X0

DEC 2x4

X1 1

0 1 2 3

1 2 3 0

COD 4x2

Y0

Y1

Puede ocurrir que los dos cdigos no tengan el mismo nmero de bits. Lo vemos en este otro ejemplo: convertir el cdigo A en el cdigo B segn la tabla adjunta: Tema 5: Sistemas aritmticos y lgicos 13

TECNOLOGA DE COMPUTADORES. CURSO 2007/08 Inocente Snchez Ciudad

Cdigo A

X1 0 0 1 1 X0 0 1 0 1 S3 0 0 0 1

Cdigo B

S2 0 0 1 1 S1 0 1 0 1 S0 1 0 1 0

X0

0 1

DEC 2x4

X1 1

2 3

0 1 2 3 4 COD 5 16x4 . . 14 15

0 1 2 3

S0 S1

S2 S3

Hay circuitos integrados que realizan conversiones de cdigos BCD binario y viceversa. Ejemplo: el circuito integrado 74184 convierte 6 bits BCD (4 de menos peso y 2 de ms peso, es decir, el mayor nmero que se puede representar es el 39) en binario de 6 bits. Por ejemplo, 110011, que representara al 33, lo convierte a 33 en binario, que es 100001. Por el contrario, el circuito 74185 convierte un nmero binario de 6 bits en dos BCD (con 8 bits); por ejemplo, el nmero 50, que en binario sera 110010, lo expresa como 0101 0000. Otro ejemplo de conversor de cdigo es un conversor de 4 bits (siendo G3 y B3 los bits ms significativos de los cdigos Gray y binario, respectivamente) que cambia un cdigo binario puro en Gray y viceversa. Se rige por las siguientes ecuaciones:

G3 = B3 G 2 = B3 B2 G1 = B2 B1 G0 = B1 B0

B3 = G3

B2 = G3 G2 = B3 G2 B1 = B2 G1 = G3 G 2 G1

B0 = B1 G0 = G3 G2 G1 G0

Tema 5: Sistemas aritmticos y lgicos 14

TECNOLOGA DE COMPUTADORES. CURSO 2007/08 Inocente Snchez Ciudad

5.4. Unidad Aritmtica-Lgica combinacional elemental.

Se trata de disear una ALU con las siguientes caractersticas: Datos de 4 bits, A y B, 4 lneas de seleccin S3 hasta S0 para controlar la operacin de la siguiente forma

S3=0 (LGICA) S2 S1 0 0 1 1 0 1 0 1 Operacin A and B A or B NOT A A xor B S2 0 0 0 0 1 1 1 1

S3=1 (ARITMTICA) S1 0 0 1 1 0 0 1 1 S0 0 1 0 1 0 1 0 1 Operacin A A A A A A A A + B + B + 1 - 1 (sumando 1111+1) (sumando 0000+0) + 1 - B 1 B

Diagrama de bloques

Tema 5: Sistemas aritmticos y lgicos 15

TECNOLOGA DE COMPUTADORES. CURSO 2007/08 Inocente Snchez Ciudad

Tema 5: Sistemas aritmticos y lgicos 16

TECNOLOGA DE COMPUTADORES. CURSO 2007/08 Inocente Snchez Ciudad

Tema 5: Sistemas aritmticos y lgicos 17

TECNOLOGA DE COMPUTADORES. CURSO 2007/08 Inocente Snchez Ciudad Se puede observar que C 0 = S 0 . Qu hay que sumarle a A en funcin de S2 y S1?

b3

b2

b1

b0

S2 S1

BLOQUE B

d3 d2 d1 d0

La operacin a realizar por el Bloque B segn las seales de control S2 y S1 es: S2 0 0 1 1 S1 0 1 0 1 SUMAR

B

1111 0000

que, desarrolada, se puede expresar como: S2 S1

0 0 0 0 1 1 1 1

0 0 1 1 0 0 1 1

bi 0 1 0 1 0 1 0 1

di 0 1 1 1 0 0 1 0 d i puede expresarse en funcin de las variables S 2 , S1 y bi de la forma

en donde la funcin booleana

d i = S 2 bi + S1 bi

Tema 5: Sistemas aritmticos y lgicos 18

TECNOLOGA DE COMPUTADORES. CURSO 2007/08 Inocente Snchez Ciudad

EJERCICIOS PROPUESTOS.

1) Dados tres nmeros binarios de 4 bits, A, B y C, codificados en binario natural, disear un circuito que realice la suma de A con el mayor de B y C. Si B = C, el resultado debe ser A. Para ello usar sumadores binarios y comparadores y las puertas lgicas que sean necesarias. 2) Un sistema digital con dos seales de control C1 y C0 tiene en su entrada 3 buses (*) A, B y C de 4, 3 y 3 bits, respectivamente. A representa un nmero expresado en BCD exceso 3, B representa un nmero en binario natural y C representa un nmero en binario natural. La salida del sistema es un bus de 4 bits segn la tabla: C1 C0 0 0 1 1 0 1 0 1 SALIDA Todos ceros A codificado en binario natural La mitad de B (si es impar, la parte entera de la mitad) El doble de C

Disear el circuito usando slo multiplexores y un sumador completo de 4 bits, y explicando la solucin del diseo.

A B C C1 C0

(*) NOTA: Un bus es un conjunto de lneas cada una de las cuales lleva informacin de 1 bit. 3) Se dispone de una ALU descrita en la tabla adjunta con tres entradas S2,S1,S0 que seleccionan la funcin a realizar y una cuarta entrada M que distingue si la funcin es lgica o aritmtica. Disear un circuito que realice las cuatro funciones siguientes de forma secuencial y cclica:

F1 = A + B ;

F2 = A + B ;

F 3 = ( A + B ) MAS ( AB ) ;

F 4 = A B con las siguientes

herramientas. Se dispone siempre de una ALU y de mdulos contadores necesarios). NOTA: "MAS" significa SUMA ARITMTICA, mientras que "+" significa SUMA LGICA. El signo "-" es la resta aritmtica. ENTRADA DE DATOS

A S2 S1

SALIDA S0 M

1) Con puertas lgicas. 2) Con mdulos combinacionales: decodificadores y codificadores. Tema 5: Sistemas aritmticos y lgicos 19

TECNOLOGA DE COMPUTADORES. CURSO 2007/08 Inocente Snchez Ciudad

Descripcin del funcionamiento de la ALU S2 S1 S0 0 0 0 0 0...1 0 1 0 0 1 1 1 0 0 1 0 1 1 1 0 1 1 1 M=1 Funciones Lgicas

F=A F = ( A + B) F = AB F =0 F = ( AB ) F=B F = A B F = AB

F=A F = A+ B

M=0 Funciones Aritmticas

F = A+ B F = A 1 F = ( A) MAS ( AB ) F = ( A + B ) MAS ( AB ) F = A B 1 F = AB 1

4) Se trata de disear una Unidad Aritmtico Lgica con las siguientes caractersticas: las entradas sern dos nmeros A (a1,a0) y B (b1,b0) de 2 bits cada uno. Las salidas sern 4 lneas S3, S2, S1, S0 ms dos lneas adicionales F1 y F0. El funcionamiento es: Si A > B , en las lneas S3, S2, S1, S0 estar el producto aritmtico de A y B, siendo F1 = 1 y F0 = 0. Si A = B la salida ser igual que en el caso anterior salvo que F1 = 0. Si F1 = 0 y F0 = 1. NOTA: (+ es la suma lgica, es el producto lgico).

A < B , S 3 = a1 + b1 , S 2 = a 0 b0 , S1 = (a1 + b0 ) , y S 0 = a0 b1 , siendo

a1

F1 F0

M

E

a0

UNIDAD ARITMTICO LGICA A DISEAR

S3 S2 b1 S1 b0 S0

DISPLAY DE 7 SEGMENTOS

1. Encontrar la tabla de verdad que resuelve el problema (0,4 puntos). 2. Implementar las funciones con los elementos solicitados: F1 usando slo puertas NAND. (0,3 puntos). F0 como suma de productos. (0,2 puntos). S3 usando slo puertas NOR. (0,3 puntos). S2 como producto de sumas. (0,2 puntos). S1 con un DEC 4x16 con salidas activas a nivel alto. (0,2 puntos). S0 con un MUX 8x1. (0,2 puntos). 3. Contenido del bloque M sabiendo que el nmero se debe ver cuando la operacin realizada haya sido una multiplicacin aritmtica, siendo E la seal de habilitacin, activa a nivel bajo. Tema 5: Sistemas aritmticos y lgicos 20

Vous aimerez peut-être aussi

- Unidad 1. Infraestructura CorporativaDocument60 pagesUnidad 1. Infraestructura CorporativaPablo Antonio Briones MaldonadoPas encore d'évaluation

- Unidad 1. Introducción A La Auditoría InformáticaDocument35 pagesUnidad 1. Introducción A La Auditoría Informáticashaft_197Pas encore d'évaluation

- Unidad 3. MicrocontroladoresDocument64 pagesUnidad 3. MicrocontroladoresPablo Antonio Briones Maldonado100% (2)

- Unidad 2. Disponibilidad y ConfiabilidadDocument73 pagesUnidad 2. Disponibilidad y ConfiabilidadPablo Antonio Briones MaldonadoPas encore d'évaluation

- Unidad 3. Transformaciones Integrales Transformadas de LaplaceDocument28 pagesUnidad 3. Transformaciones Integrales Transformadas de LaplacePablo Antonio Briones MaldonadoPas encore d'évaluation

- Unidad 3. Enrutamiento Por ProtocolosDocument7 pagesUnidad 3. Enrutamiento Por ProtocolosPablo Antonio Briones MaldonadoPas encore d'évaluation

- Unidad 1. Fundamentos de La Economía DigitalDocument52 pagesUnidad 1. Fundamentos de La Economía DigitalPablo Antonio Briones Maldonado100% (2)

- Configurar Un Firewall Lógico (Evidencia Unidad2)Document27 pagesConfigurar Un Firewall Lógico (Evidencia Unidad2)Pablo Antonio Briones MaldonadoPas encore d'évaluation

- 03 LMS y LCMS Funcionalidades y BeneficiosDocument3 pages03 LMS y LCMS Funcionalidades y BeneficiosPablo Antonio Briones MaldonadoPas encore d'évaluation

- Unidad 1. Redes de Área Amplia (WAN)Document37 pagesUnidad 1. Redes de Área Amplia (WAN)Pablo Antonio Briones MaldonadoPas encore d'évaluation

- Seguridad Por Niveles v-001Document709 pagesSeguridad Por Niveles v-001Jesus BelinchonPas encore d'évaluation

- Unidad 2. MultiprocesamientoDocument51 pagesUnidad 2. MultiprocesamientoPablo Antonio Briones MaldonadoPas encore d'évaluation

- IPSecDocument80 pagesIPSecPablo Antonio Briones MaldonadoPas encore d'évaluation

- Unidad 3. Seguridad de Las ComunicacionesDocument8 pagesUnidad 3. Seguridad de Las ComunicacionesPablo Antonio Briones MaldonadoPas encore d'évaluation

- Ecuaciones Diferenciales. Unidad 1. Ecuaciones de Primer Orden. UNADM.Document23 pagesEcuaciones Diferenciales. Unidad 1. Ecuaciones de Primer Orden. UNADM.Raúl Márquez Garza33% (3)

- Hernandez Los Señores Del Narco PDFDocument299 pagesHernandez Los Señores Del Narco PDFAlicia48Pas encore d'évaluation

- 05a TelematicaDocument5 pages05a TelematicaPablo Antonio Briones MaldonadoPas encore d'évaluation

- Tutorial Crocodile TechnologyDocument38 pagesTutorial Crocodile TechnologyPablo Antonio Briones MaldonadoPas encore d'évaluation

- Palabras Homófona, Homógrafas y ParónimasDocument4 pagesPalabras Homófona, Homógrafas y ParónimasAnahi Mariana Napa Yactayo100% (2)

- Convertir Números de Un Sistema Numérico en OtroDocument16 pagesConvertir Números de Un Sistema Numérico en OtroRoberto OsorioPas encore d'évaluation

- 00 - Formación de PalabrasDocument7 pages00 - Formación de PalabrasAndrea CarrascoPas encore d'évaluation

- Tema 1Document2 pagesTema 1Estiv Edwin Saldaña SuárezPas encore d'évaluation

- El Léxico de La Lengua EspañolaDocument10 pagesEl Léxico de La Lengua EspañolaGibranMtzPas encore d'évaluation

- EJERCICIO de MORFOLOGÍA Sustantivo y Adjetivo Con SoluciónDocument2 pagesEJERCICIO de MORFOLOGÍA Sustantivo y Adjetivo Con SoluciónElena MurciaPas encore d'évaluation

- Guia 2 Matematicas 5-03Document6 pagesGuia 2 Matematicas 5-03Tianna CardenasPas encore d'évaluation

- 08-11-2021-Resolvemos Problemas de Adición y Sustracción Con Números Decimales Hasta Las Centésimas.Document8 pages08-11-2021-Resolvemos Problemas de Adición y Sustracción Con Números Decimales Hasta Las Centésimas.MagdaElizabethTordoyaBaez100% (1)

- Curso de Numerologia Gratis - El Karma Segun El Mes de NacimientoDocument16 pagesCurso de Numerologia Gratis - El Karma Segun El Mes de NacimientoHelen JuárezPas encore d'évaluation

- Valor PosicionalDocument7 pagesValor PosicionalLuz Milawilches VeraPas encore d'évaluation

- Sistemas de Numeración ConamatDocument2 pagesSistemas de Numeración ConamatYOLKATANIAPas encore d'évaluation

- Prueba DIA 2022Document5 pagesPrueba DIA 2022María Isolina MonardesPas encore d'évaluation

- Ejercicios de Conversion de Sistemas NumericosDocument7 pagesEjercicios de Conversion de Sistemas Numericosvolpesinc9167Pas encore d'évaluation

- Las Fracciones Convenciones 1Document20 pagesLas Fracciones Convenciones 1SantoPas encore d'évaluation

- Matemáticas 7°, Guia 3 2° PeriodoDocument6 pagesMatemáticas 7°, Guia 3 2° PeriodonicollePas encore d'évaluation

- Ab 0 AbDocument2 pagesAb 0 AbcarlosPas encore d'évaluation

- Cifras SignificativasDocument7 pagesCifras SignificativasRolando Felipe Tapia MoyanoPas encore d'évaluation

- Definiciones Sistema NumericosDocument3 pagesDefiniciones Sistema NumericosOSCAR ADOLFO BOLIVAR GUERREROPas encore d'évaluation

- Sistema BinarioDocument25 pagesSistema BinarioJohanna MorenoPas encore d'évaluation

- El Signo Lingüístico y Las Relaciones SemánticasDocument17 pagesEl Signo Lingüístico y Las Relaciones SemánticasEd´eSpAPas encore d'évaluation

- Corrector Ejercicios Del Tema 4Document3 pagesCorrector Ejercicios Del Tema 4jose luis100% (1)

- El Español en El MundoDocument5 pagesEl Español en El MundoPTPantita33 FGPas encore d'évaluation

- Sistema de NumeracionDocument4 pagesSistema de NumeracionJuan Julio Miguel Diaz LazoPas encore d'évaluation

- 17 Ejercicios de Fracciones para Estudiantes de Primero de SecundariaDocument11 pages17 Ejercicios de Fracciones para Estudiantes de Primero de SecundariaJavierParionaCardenasPas encore d'évaluation

- Decimal EsDocument6 pagesDecimal Esjackie383Pas encore d'évaluation

- Ejercicios SI, Y, O AnidadosDocument26 pagesEjercicios SI, Y, O AnidadosSergio A Plaza MPas encore d'évaluation

- Notacion CientificaDocument10 pagesNotacion CientificaGustavo Jarpa UPas encore d'évaluation

- Segundo Año Razonamiento MateDocument8 pagesSegundo Año Razonamiento MateHector Rojas RiosPas encore d'évaluation

- Actividades de Aplicación Notación CientíficaDocument5 pagesActividades de Aplicación Notación CientíficaPatricia Rolon VargasPas encore d'évaluation

- Esquema de Conjuntos NumericosDocument1 pageEsquema de Conjuntos NumericosMayen Hernandez RamirezPas encore d'évaluation