Académique Documents

Professionnel Documents

Culture Documents

Pipelined Mul

Transféré par

Sanjay ChCopyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

Pipelined Mul

Transféré par

Sanjay ChDroits d'auteur :

Formats disponibles

library IEEE; use IEEE.std_logic_1164.

all; entity register_64 is port(clk : in std_logic; clear : in std_logic; input : in std_logic_vector (63 downto 0); output : out std_logic_vector (63 downto 0) ); end entity register_64; architecture behavior of register_64 is begin -- behavior reg_64: process(clk, clear) begin if clear='1' then -- only once output <= (others=>'0'); elsif clk'event and clk='1' then output <= input after 100 ps; end if; end process reg_64; end architecture behavior; -- of register_64 library IEEE; use IEEE.std_logic_1164.all; entity register_32 is port(clk : in std_logic; clear : in std_logic; input : in std_logic_vector (31 downto 0); output : out std_logic_vector (31 downto 0) ); end entity register_32; architecture behavior of register_32 is begin -- behavior reg_32: process(clk, clear) begin if clear='1' then -- only once output <= (others=>'0'); elsif clk'event and clk='1' then output <= input after 100 ps; end if; end process reg_32; end architecture behavior; -- of register_32 library IEEE; use IEEE.std_logic_1164.all; entity madd is port(c : in s : in b : in a : in sum : out cout : out end entity madd; -- multiplying full adder stage std_logic; -- one input, think carry in std_logic; -- one input, think previous sum std_logic; -- multiplier bit std_logic; -- multiplicand bit std_logic; -- carry save sum out std_logic); -- carry save carry out

architecture circuits of madd is -- multiplying full adder stage signal ab: std_logic; -- one bit of a times one bit of b begin

ab <= a and b; -- logic could be reduced, yet probably circuit designed sum <= (ab and s and c) or (ab and not s and not c) or (not ab and s and not c) or (not ab and not s and c) after 1 ps; cout <= (ab and s) or (ab and c) or (s and c) after 1 ps; end architecture circuits; -- of madd library IEEE; use IEEE.std_logic_1164.all; entity pipemul port(clk: in a : in b : in p : out end pipemul; is -- 32 x 32 = 64 std_logic; std_logic_vector(31 std_logic_vector(31 std_logic_vector(63 bit unsigned product multiplier -- new value each rising clock downto 0); -- multiplicand downto 0); -- multiplier downto 0)); -- product

architecture circuits of pipemul is constant N : integer := 31; -- last row number constant NS : integer := 8; -- number of stages, 4 rows each stage type arr is array(0 to N) of std_logic_vector(N downto 0); signal s : arr; -- partial temp sums signal c : arr; -- partial temp carries type parr is array(0 to NS) of std_logic_vector(63 downto 0); signal pin : parr; -- pipeline register input partial product signal pout : parr; -- pipeline register output partial product type aarr is array(0 to NS) of std_logic_vector(31 downto 0); signal ain : aarr; -- pipeline register input multiplicand a signal aout : aarr; -- pipeline register output multiplicand a signal bin : aarr; -- pipeline register input multiplier b signal bout : aarr; -- pipeline register output multiplier b signal tcin : aarr; -- pipeline register input temp carry signal tcout : aarr; -- pipeline register output temp carry signal clear : std_logic := '1'; -- one time clear begin -- circuits of pipemul clear <= '0' after 10 ps; -- registers greg: for j in 0 to NS generate pregj: entity WORK.register_64 aregj: entity WORK.register_32 bregj: entity WORK.register_32 cregj: entity WORK.register_32 end generate greg; pin(0) <= (others => '0'); tcin(0) <= (others => '0'); ain(0) <= a; bin(0) <= b;

port port port port -----

map(clk, map(clk, map(clk, map(clk,

clear, clear, clear, clear,

pin(j), ain(j), bin(j), tcin(j),

pout(j)); aout(j)); bout(j)); tcout(j));

initial partial product initial temp carry changes when a or b changes put on aout, bout, pout, tcout at clk

-- pass along multiplicand and multiplier mpy: for j in 0 to NS-1 generate ain(j+1) <= aout(j); -- wiring bin(j+1) <= bout(j); -- wiring end generate mpy; -- the internal part of the multiplier is nested generate -- the four levels of madd between stages must be coded -- stages

gmaddi: for i in 0 to NS-1 generate gmaddj: for j in 0 to N-1 generate maddj1: entity WORK.madd port map (pout(i)(j+4*i), tcout(i)(j), bout(i)(4*i), aout(i)(j), s(4*i)(j), c(4*i)(j)); maddj2: entity WORK.madd port map (s(4*i)(j+1), c(4*i)(j), bout(i)(4*i+1), aout(i)(j), s(4*i+1)(j), c(4*i+1)(j)); maddj3: entity WORK.madd port map (s(4*i+1)(j+1), c(4*i+1)(j), bout(i)(4*i+2), aout(i)(j), s(4*i+2)(j), c(4*i+2)(j)); maddj4: entity WORK.madd port map (s(4*i+2)(j+1), c(4*i+2)(j), bout(i)(4*i+3), aout(i)(j), s(4*i+3)(j), tcin(i+1)(j)); end generate gmaddj; gmaddjn: for j in N to N generate -- special left side maddj1n: entity WORK.madd port map (pout(i)(j+4*i), tcout(i)(j), bout(i)(4*i), aout(i)(j), s(4*i)(j), c(4*i)(j)); maddj2n: entity WORK.madd port map ('0', c(4*i)(j), bout(i)(4*i+1), aout(i)(j), s(4*i+1)(j), c(4*i+1)(j)); maddj3n: entity WORK.madd port map ('0', c(4*i+1)(j), bout(i)(4*i+2), aout(i)(j), s(4*i+2)(j), c(4*i+2)(j)); maddj4n: entity WORK.madd port map ('0', c(4*i+2)(j), bout(i)(4*i+3), aout(i)(j), s(4*i+3)(j), tcin(i+1)(j)); end generate gmaddjn; pin(i+1)(4*i-1 downto 0) <= pout(i)(4*i-1 downto 0); -- pass previous pin(i+1)(4*i ) <= s(4*i)(0); -- new bottom product bits pin(i+1)(4*i+1) <= s(4*i+1)(0); pin(i+1)(4*i+2) <= s(4*i+2)(0); pin(i+1)(4*i+3) <= s(4*i+3)(0); pmid: for j in 1 to N generate pin (i+1)(j+4*i+3) <= s(4*i+3)(j); end generate pmid; pin(i+1)(63 downto 4*i+35) <= pout(i)(63 downto 4*i+35); end generate gmaddi; addl: entity Work.add32 port map(pout(NS)(63 downto 32),tcout(NS),'0', p(63 downto 32), open); -- connect outputs p(31 downto 0) <= pout(NS)(31 downto 0); end architecture circuits;

Vous aimerez peut-être aussi

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeD'EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeÉvaluation : 4 sur 5 étoiles4/5 (5794)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreD'EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreÉvaluation : 4 sur 5 étoiles4/5 (1090)

- Never Split the Difference: Negotiating As If Your Life Depended On ItD'EverandNever Split the Difference: Negotiating As If Your Life Depended On ItÉvaluation : 4.5 sur 5 étoiles4.5/5 (838)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceD'EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceÉvaluation : 4 sur 5 étoiles4/5 (895)

- Grit: The Power of Passion and PerseveranceD'EverandGrit: The Power of Passion and PerseveranceÉvaluation : 4 sur 5 étoiles4/5 (588)

- Shoe Dog: A Memoir by the Creator of NikeD'EverandShoe Dog: A Memoir by the Creator of NikeÉvaluation : 4.5 sur 5 étoiles4.5/5 (537)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersD'EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersÉvaluation : 4.5 sur 5 étoiles4.5/5 (345)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureD'EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureÉvaluation : 4.5 sur 5 étoiles4.5/5 (474)

- Her Body and Other Parties: StoriesD'EverandHer Body and Other Parties: StoriesÉvaluation : 4 sur 5 étoiles4/5 (821)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)D'EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Évaluation : 4.5 sur 5 étoiles4.5/5 (121)

- The Emperor of All Maladies: A Biography of CancerD'EverandThe Emperor of All Maladies: A Biography of CancerÉvaluation : 4.5 sur 5 étoiles4.5/5 (271)

- The Little Book of Hygge: Danish Secrets to Happy LivingD'EverandThe Little Book of Hygge: Danish Secrets to Happy LivingÉvaluation : 3.5 sur 5 étoiles3.5/5 (400)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyD'EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyÉvaluation : 3.5 sur 5 étoiles3.5/5 (2259)

- The Yellow House: A Memoir (2019 National Book Award Winner)D'EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Évaluation : 4 sur 5 étoiles4/5 (98)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaD'EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaÉvaluation : 4.5 sur 5 étoiles4.5/5 (266)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryD'EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryÉvaluation : 3.5 sur 5 étoiles3.5/5 (231)

- Team of Rivals: The Political Genius of Abraham LincolnD'EverandTeam of Rivals: The Political Genius of Abraham LincolnÉvaluation : 4.5 sur 5 étoiles4.5/5 (234)

- On Fire: The (Burning) Case for a Green New DealD'EverandOn Fire: The (Burning) Case for a Green New DealÉvaluation : 4 sur 5 étoiles4/5 (74)

- The Unwinding: An Inner History of the New AmericaD'EverandThe Unwinding: An Inner History of the New AmericaÉvaluation : 4 sur 5 étoiles4/5 (45)

- 012-NetNumen U31 R22 Northbound Interface User Guide (SNMP Interface)Document61 pages012-NetNumen U31 R22 Northbound Interface User Guide (SNMP Interface)buts101100% (5)

- Duckademy LFI-RFI How LFI and RFI WorkDocument42 pagesDuckademy LFI-RFI How LFI and RFI WorkKlentiB.ÇukariPas encore d'évaluation

- Sram 2nd PhaseDocument26 pagesSram 2nd PhaseSanjay ChPas encore d'évaluation

- List of Figures: Figure No. Page NoDocument4 pagesList of Figures: Figure No. Page NoSanjay ChPas encore d'évaluation

- Double Edge Triggered Feedback Flip-Flop: S. H. Rasouli, A. Amirabadi, A. S. Seyedi and A. Afzali-KushaDocument31 pagesDouble Edge Triggered Feedback Flip-Flop: S. H. Rasouli, A. Amirabadi, A. S. Seyedi and A. Afzali-KushaSanjay ChPas encore d'évaluation

- Chapter 1Document10 pagesChapter 1Sanjay ChPas encore d'évaluation

- SMS Based Device Control: Sagar MundadaDocument4 pagesSMS Based Device Control: Sagar MundadaSanjay ChPas encore d'évaluation

- Design of High Speed Six Transistor Full Adder Using A Novel Two Transistor XOR GatesDocument5 pagesDesign of High Speed Six Transistor Full Adder Using A Novel Two Transistor XOR GatesSanjay ChPas encore d'évaluation

- Android (Operating System) : Kaloyan Beshev F39786Document14 pagesAndroid (Operating System) : Kaloyan Beshev F39786Sanjay ChPas encore d'évaluation

- Rafati Iscas00Document1 pageRafati Iscas00Sanjay ChPas encore d'évaluation

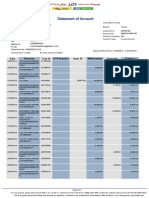

- Statement of Account: Date Tran Id Remarks UTR Number Instr. ID Withdrawals Deposits BalanceDocument8 pagesStatement of Account: Date Tran Id Remarks UTR Number Instr. ID Withdrawals Deposits Balancedinesh namdeoPas encore d'évaluation

- CCNA Exploration 2 - Module 4 Exam Answers Version 4.0Document3 pagesCCNA Exploration 2 - Module 4 Exam Answers Version 4.0fun kollaPas encore d'évaluation

- An Introduction To MQTT For Complete BeginnersDocument22 pagesAn Introduction To MQTT For Complete BeginnerskarchecovPas encore d'évaluation

- Practice Test A1Document7 pagesPractice Test A1Khang Nguyen TienPas encore d'évaluation

- Green Mode Power Switch For Valley Switching Converter - Low EMI and High Efficiency FSQ0365, FSQ0265, FSQ0165, FSQ321Document22 pagesGreen Mode Power Switch For Valley Switching Converter - Low EMI and High Efficiency FSQ0365, FSQ0265, FSQ0165, FSQ321Mekkati MekkatiPas encore d'évaluation

- SSA TrainingDocument48 pagesSSA TrainingStats TutorPas encore d'évaluation

- STBDDI3725: Product Data SheetDocument5 pagesSTBDDI3725: Product Data SheetMatheus AlvesPas encore d'évaluation

- Clayoo User's GuideDocument200 pagesClayoo User's Guideronald patiño100% (1)

- Table of Contents For Computer Architecture: A Minimalist PerspectiveDocument6 pagesTable of Contents For Computer Architecture: A Minimalist PerspectiveWilliam GilreathPas encore d'évaluation

- Andhra Pradesh State Board of Technical Education and Training, AP Sbtet Diploma c16 Exam Results June 2019 FromDocument1 pageAndhra Pradesh State Board of Technical Education and Training, AP Sbtet Diploma c16 Exam Results June 2019 FromCharan PrasadPas encore d'évaluation

- Journal of Business Research: Enrico Battisti, Simona Alfiero, Erasmia LeonidouDocument13 pagesJournal of Business Research: Enrico Battisti, Simona Alfiero, Erasmia LeonidoualwiPas encore d'évaluation

- Covenant UniversityDocument5 pagesCovenant UniversityWilkie MofePas encore d'évaluation

- HUAWEI - SD-WAN SolutionDocument235 pagesHUAWEI - SD-WAN Solutionbuafac10Pas encore d'évaluation

- CV-Sushil GuptaDocument3 pagesCV-Sushil Guptaanurag_bahety6067Pas encore d'évaluation

- Part III WirelessDocument130 pagesPart III WirelessRalph Laurence G VisayaPas encore d'évaluation

- Red Hat Enterprise Linux-6-6.8 Release Notes-En-UsDocument65 pagesRed Hat Enterprise Linux-6-6.8 Release Notes-En-Uskamel najjarPas encore d'évaluation

- Cost Benefit AnalysisDocument3 pagesCost Benefit AnalysisSaimo MghasePas encore d'évaluation

- MP Unit-3Document24 pagesMP Unit-3SARTHAK PANWARPas encore d'évaluation

- MANUAL Sbm100whi 00 Dfu AenDocument10 pagesMANUAL Sbm100whi 00 Dfu AenMary Carmen Andreu MerinoPas encore d'évaluation

- Annual Exam COMPUTER SC Class XIDocument8 pagesAnnual Exam COMPUTER SC Class XIST JOSEPH'S SCHOOLPas encore d'évaluation

- 6305ele S1L1Document33 pages6305ele S1L1M Moiz IlyasPas encore d'évaluation

- Binomial DistributionDocument3 pagesBinomial DistributionelminvaldezPas encore d'évaluation

- Practical-8: Write A Mobile Application That Creates Alarm ClockDocument7 pagesPractical-8: Write A Mobile Application That Creates Alarm Clockjhyter54rdPas encore d'évaluation

- Design of PLC Based Automatic Flat Bottle Label Adjuster: Olorunda, P. A. and Adetunde, I. ADocument5 pagesDesign of PLC Based Automatic Flat Bottle Label Adjuster: Olorunda, P. A. and Adetunde, I. AManiPas encore d'évaluation

- Rockwell Automation TechED 2018 - PR26 - Endress+HauserDocument33 pagesRockwell Automation TechED 2018 - PR26 - Endress+HauserAlex Rivas100% (1)

- Field Visit PresentationDocument33 pagesField Visit PresentationNib IndranilPas encore d'évaluation

- User Guide - JMB - JT0250003-01 (50-238Z-GB-5B-FGKUP-UK) - JMB-MAN-0007 versWEBDocument28 pagesUser Guide - JMB - JT0250003-01 (50-238Z-GB-5B-FGKUP-UK) - JMB-MAN-0007 versWEBBOUZANAS DIMITRIOSPas encore d'évaluation

- Full Karding Tut 2020Document3 pagesFull Karding Tut 2020Hillson David100% (1)