Académique Documents

Professionnel Documents

Culture Documents

Diff Pairs - Behzad Razavi Lecture Notes

Transféré par

hsharghiDescription originale:

Titre original

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

Diff Pairs - Behzad Razavi Lecture Notes

Transféré par

hsharghiDroits d'auteur :

Formats disponibles

EE215A Fall 11

B. Razavi HO #2

Differential Amplifiers

Differential & Single-Ended Operation - A single-ended signal is taken with respect to a fixed potential (usually ground). - A differential signal is taken between two nodes that have equal and opposite signals with respect to a common mode voltage and also equal impedances to a fixed potential (usually ground).

Why Differential? o Rejection of common-mode disturbance: supply noise, etc.

o Rejection of coupling & feed through from other sources:

24

EE215A Fall 11

B. Razavi HO #2

o Reduction of coupling to other circuits;

o Maximum voltage swing almost twice that in single-ended operation; o Even-order distortion suppressed (discussed later); o Biasing is easier. Basic Differential Pair

- Quantitative Analysis Differential Behavior:

Where does the maximum small-signal gain occur?

25

EE215A Fall 11

B. Razavi HO #2

Common-Mode Behavior:

Observations: The small-signal gain drops as the difference between Vin1 and Vin2 increases. The input and output common-mode levels must be chosen carefully. The current source requires some voltage so as to exhibit a high output impedance. How large can the output swings be?

- Quantitative Analysis

26

EE215A Fall 11

B. Razavi HO #2

Note: If neglect sub-threshold behavior, for some Vin1 - Vin2 one transistor completely turns off. This occurs for a differential input of :

This can be related to the overdrive at equilibrium: To achieve a wider linear range for Vin1 - Vin2, need greater (equilibrium) overdrive. For a given bias current, this translates to lower transconductance for each device. How does the input-output characteristic change as W changes?

Small-Signal Analysis Method I Treat circuit as cascade of two stages and use superposition.

For VY,

27

EE215A Fall 11

B. Razavi HO #2

Method II If the circuit is perfectly symmetric and Vin1 and Vin2 change by equal and opposite amounts from equilibrium, then we can use the concept of half circuit. Lemma In the following symmetric circuit, if Vin1 changes from V0 to V0+V and Vin2 changes from V0 to V0-V, then Vx does not change.

From another point of view, one transistor wants to pull Vx up while the other wants to pull it down. => Vx can be grounded.

28

EE215A Fall 11

B. Razavi HO #2

What if Vin1 and Vin2 are not exactly differential?

Use superposition to find the effect of differential and common-mode signals. Other Types of Loads

Calculate the voltage headroom requirement and small-signal gain.

How do we increase the gain of diff pair with current source loads?

29

EE215A Fall 11

B. Razavi HO #2

Common-Mode Response Case I : Symmteric Circuit

Case II: Asymmetric Circuit

Effect of load resistance mismatch:

30

EE215A Fall 11

B. Razavi HO #2

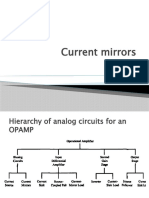

Current Mirrors & Active Loads

In analog design (and sometimes digital design), we may need to generate many well-defined bias currents. For example:

Each current source can be realized as:

If we apply a self-defined voltage to the gate or the base, the current is NOT well-defined. In MOSFETs, VTH can vary by tens of millivolts from wafer to wafer, causing significant error. Better approach:

31

EE215A Fall 11

B. Razavi HO #2

So, all we need to generate is one reference current. IREF is established by precision bandgap techniques or sometimes provides externally.

Example:

Cascode Current Mirrors Channel-length modulation causes error if the voltage across the diodeconnected device is not equal to VDS of current sources.

32

EE215A Fall 11

B. Razavi HO #2

To suppress this effect, we can use cascodes:

What is the minimum allowable voltage across the current source? Example:

Low-Voltage Cascode

How to generate Vb?

33

EE215A Fall 11

B. Razavi HO #2

Active Load with Current Mirror Suppose we need a high-gain differential amplifier with single-ended output:

What is the voltage gain? Active Load:

34

EE215A Fall 11

B. Razavi HO #2

Large-Signal Behavior:

Small-Signal Behavior:

35

EE215A Fall 11

B. Razavi HO #2

What is the dc output voltage in equilibrium? How do we increase the voltage gain? Common-Mode Rejection

What is the common-mode gain?

Thus, even if the circuit is perfectly symmetric, CMRR is not infinite.

36

EE215A Fall 11

B. Razavi HO #2

In practice, random mismatches between the two sides result in a finite CMRR.

37

Vous aimerez peut-être aussi

- Analog IC Design With Low-Dropout RegulatorsDocument373 pagesAnalog IC Design With Low-Dropout RegulatorsHoang le Huy67% (3)

- VLSI Interview Questions With Answers - Ebook - VLSI Design Interview Questions With Answers - Ebook PDFDocument4 pagesVLSI Interview Questions With Answers - Ebook - VLSI Design Interview Questions With Answers - Ebook PDFnaveen silveri50% (4)

- Behzad Razavi Microelectronics NotesDocument394 pagesBehzad Razavi Microelectronics NotesSuprateek vermaPas encore d'évaluation

- Hardware Modelling Using VerilogDocument15 pagesHardware Modelling Using VerilogYogesh Tiwari25% (4)

- CMOS Analog Circuit Design (Allen-2016)Document1 412 pagesCMOS Analog Circuit Design (Allen-2016)curliph0% (1)

- Fundamentals of MicroelectronicsDocument394 pagesFundamentals of Microelectronicsomidsf100% (2)

- Razavi Analog CMOS SolutionDocument328 pagesRazavi Analog CMOS SolutionCunzhu Xǔ78% (9)

- Analog Layout Design (Industrial Training)Document10 pagesAnalog Layout Design (Industrial Training)Shivaksh SharmaPas encore d'évaluation

- Eetop - CN ADC LayoutDocument199 pagesEetop - CN ADC LayoutVishnuGundaPas encore d'évaluation

- VLSI Design Questions With AnswersDocument5 pagesVLSI Design Questions With Answersmani_vlsi100% (4)

- Chapters 8 OscillatorDocument134 pagesChapters 8 OscillatorTspi RitzelPas encore d'évaluation

- Design of Integrated Circuits For Optical Communications by Behzad RazaviDocument381 pagesDesign of Integrated Circuits For Optical Communications by Behzad RazaviJM Happy GorospePas encore d'évaluation

- Cad/Cam Softwares: A Presentaton OnDocument35 pagesCad/Cam Softwares: A Presentaton OnVaibhav AroraPas encore d'évaluation

- GSL Hi-Temp Operation Manual-0217-Gl - Tube FurnaceDocument36 pagesGSL Hi-Temp Operation Manual-0217-Gl - Tube FurnacehcaPas encore d'évaluation

- ScaleIO Fundamentals MR 1WN SIOFUN - Student GuideDocument74 pagesScaleIO Fundamentals MR 1WN SIOFUN - Student GuideReinaldo GuzmanPas encore d'évaluation

- Digital System Design Using VerilogDocument55 pagesDigital System Design Using VerilogAditya PatilPas encore d'évaluation

- Phillip Allen Short Course NotesDocument633 pagesPhillip Allen Short Course NotesGunwant Chaudhari100% (2)

- Behzad Razavi Fundamentals of Microelectronics Solution ManualDocument8 pagesBehzad Razavi Fundamentals of Microelectronics Solution ManualKaranPas encore d'évaluation

- CMOS Logic Design Using Cadence VirtuosoDocument36 pagesCMOS Logic Design Using Cadence VirtuosoSandeep MishraPas encore d'évaluation

- Embedded Systems Using 8051 MicrocontrollerDocument36 pagesEmbedded Systems Using 8051 MicrocontrollervineetchachraPas encore d'évaluation

- CMOS Interview QuestionsDocument52 pagesCMOS Interview QuestionsKAMARUDHEEN KP100% (1)

- Clock Domain Crossing & Asynchronous FIFODocument40 pagesClock Domain Crossing & Asynchronous FIFOPronadeep Bora100% (1)

- 1.vlsi Design NotesDocument115 pages1.vlsi Design Notesyuvaraaj aletiPas encore d'évaluation

- Basic Analog Layout TrainingDocument41 pagesBasic Analog Layout TrainingNguyen HungPas encore d'évaluation

- Two Stage CMOS Op Amp - Seid PDFDocument79 pagesTwo Stage CMOS Op Amp - Seid PDFTayachew BerhanPas encore d'évaluation

- Cmos Analog Ic Design Problems and SolutionsDocument206 pagesCmos Analog Ic Design Problems and SolutionsEdsel Silva100% (1)

- Vlsi Design Study Notes12Document37 pagesVlsi Design Study Notes12gpuonline100% (1)

- Analog Circuits: GATE EC Topic Wise QuestionsDocument50 pagesAnalog Circuits: GATE EC Topic Wise Questionsdeepthi1993100% (1)

- SEL 4283 Analog CMOS IC Design Single Stage Amplifiers: Small Signal Model 1Document52 pagesSEL 4283 Analog CMOS IC Design Single Stage Amplifiers: Small Signal Model 1jitendraPas encore d'évaluation

- CMOS Inverter Design Using CadenceDocument3 pagesCMOS Inverter Design Using CadenceVikas YerramPas encore d'évaluation

- Opamp RazaviDocument33 pagesOpamp Razavivikramkolanu100% (1)

- Verilog ADocument38 pagesVerilog ASridhar ChandrasekaranPas encore d'évaluation

- Analog Lab Mannual 613Document95 pagesAnalog Lab Mannual 613Metreprashant PmmPas encore d'évaluation

- Vlsi Design Question Bank EEC 703Document10 pagesVlsi Design Question Bank EEC 703selvi0412Pas encore d'évaluation

- Digital Electronics - Crack SeriesDocument31 pagesDigital Electronics - Crack Seriesdeepanece100% (1)

- ASIC Design: Prabhavathi P Associate Professor Dept. of ECE, BNMITDocument203 pagesASIC Design: Prabhavathi P Associate Professor Dept. of ECE, BNMITPrabhavathi ParameshwarappaPas encore d'évaluation

- OTA DesignDocument18 pagesOTA DesignAnandPas encore d'évaluation

- Microcontroller & RISC Architecture (2 Marks - Question Bank)Document61 pagesMicrocontroller & RISC Architecture (2 Marks - Question Bank)Dr. N.Shanmugasundaram100% (3)

- Analog-To-Digital Conversion Btech IIIDocument50 pagesAnalog-To-Digital Conversion Btech IIILisa BhagatPas encore d'évaluation

- Body Effect: What Do You Need To Know To Understand This Topic?Document4 pagesBody Effect: What Do You Need To Know To Understand This Topic?Rohith RajPas encore d'évaluation

- Analog Layout Design: Kanazawa University Microelectronics Research Lab. Akio KitagawaDocument48 pagesAnalog Layout Design: Kanazawa University Microelectronics Research Lab. Akio Kitagawaaminkhan83Pas encore d'évaluation

- FinfetDocument25 pagesFinfetkumarbsnsp89% (9)

- Analog Layout UTLDocument3 pagesAnalog Layout UTLDr. Sampatrao L PinjarePas encore d'évaluation

- Verilog AMS TutorialDocument29 pagesVerilog AMS TutorialSiva KrishnaPas encore d'évaluation

- From RTL To GDS Using Synopsys Flow Within Less Then 10 WeeksDocument15 pagesFrom RTL To GDS Using Synopsys Flow Within Less Then 10 WeeksLohitPas encore d'évaluation

- Analog Filter Design PDFDocument69 pagesAnalog Filter Design PDFGlan DevadhasPas encore d'évaluation

- MOSFETDocument13 pagesMOSFETMarkCabalunaPas encore d'évaluation

- Second Order EffectsDocument40 pagesSecond Order EffectsDhiraj Kumar100% (2)

- Chapter3 Rabaey MOS Capacitances OnlyDocument19 pagesChapter3 Rabaey MOS Capacitances OnlyRaheetha AhmedPas encore d'évaluation

- Cmos Digital Circuits - BookDocument56 pagesCmos Digital Circuits - BookHelder Nascimento100% (1)

- CMOS Analog Design Lecture Notes Rev 1.5L - 02!06!11Document371 pagesCMOS Analog Design Lecture Notes Rev 1.5L - 02!06!11Anonymous uspYoqEPas encore d'évaluation

- Design of Analog FIltersDocument7 pagesDesign of Analog FIltersparshuram kumarPas encore d'évaluation

- Supply 3Document34 pagesSupply 3david reyesPas encore d'évaluation

- Linear Variable Differential Transformer LVDTDocument8 pagesLinear Variable Differential Transformer LVDTRakesh MahajanPas encore d'évaluation

- Current MirrorsDocument76 pagesCurrent MirrorsSHRIDHAR N100% (1)

- Unit 2Document6 pagesUnit 2ShanilDayalanPas encore d'évaluation

- TransformersDocument36 pagesTransformersdurgaraoPas encore d'évaluation

- P E Lab FinalDocument63 pagesP E Lab FinalARVIND100% (1)

- Diode CktsDocument30 pagesDiode CktsUday RaiPas encore d'évaluation

- Lecture - 5: DC-AC Converters: Ug - ProgramDocument54 pagesLecture - 5: DC-AC Converters: Ug - ProgramArife AbdulkerimPas encore d'évaluation

- Gtu Micro Processor PracticalDocument79 pagesGtu Micro Processor Practicalbaba100% (1)

- Army AcronymDocument311 pagesArmy AcronymRadenkoKuzmanovic100% (1)

- Power Plant Manual 1Document8 pagesPower Plant Manual 1Khoirul WaladPas encore d'évaluation

- CUSTOM - PLL in FormsDocument10 pagesCUSTOM - PLL in FormsBhargi111Pas encore d'évaluation

- Result MBTDocument40 pagesResult MBTAnkush R KrishnaPas encore d'évaluation

- EAS6800+ High Quality Composite Video Encoder/Synchronizer and Analog Audio DemultiplexerDocument90 pagesEAS6800+ High Quality Composite Video Encoder/Synchronizer and Analog Audio DemultiplexerTechne PhobosPas encore d'évaluation

- NAP Form 10 PDFDocument2 pagesNAP Form 10 PDFjoseph judahPas encore d'évaluation

- Best Lesson PlanDocument4 pagesBest Lesson Planapi-398545121Pas encore d'évaluation

- Stilo Servo Electric PDFDocument7 pagesStilo Servo Electric PDFManu Alex100% (1)

- NCPDP Pharmacy Drug ClaimsDocument8 pagesNCPDP Pharmacy Drug ClaimskallepalliPas encore d'évaluation

- FitTrack BloodLinkDocument7 pagesFitTrack BloodLinkInternational Journal of Innovative Science and Research TechnologyPas encore d'évaluation

- Ipm650 PDFDocument5 pagesIpm650 PDFJAHDLPas encore d'évaluation

- Sample Exam Paper - ITC506-19Document5 pagesSample Exam Paper - ITC506-19AhmedPas encore d'évaluation

- Module 2 Quiz Section A Chapter 1 - SolutionDocument29 pagesModule 2 Quiz Section A Chapter 1 - SolutionSaad RashidPas encore d'évaluation

- Introduction To Vlsi Circuits and Systems John P UyemuraDocument1 pageIntroduction To Vlsi Circuits and Systems John P UyemuramgowtaamPas encore d'évaluation

- Elipar 3m in Healthcare, Lab, and Life Science Equipment Search Result EbayDocument1 pageElipar 3m in Healthcare, Lab, and Life Science Equipment Search Result EbayABRAHAM LEONARDO PAZ GUZMANPas encore d'évaluation

- Mechanical Au 3-1Document10 pagesMechanical Au 3-1Venkata Sai Kumar NunnaPas encore d'évaluation

- Ebook Kubernetes PDFDocument26 pagesEbook Kubernetes PDFmostafahassanPas encore d'évaluation

- Proposal Project PrintingDocument13 pagesProposal Project PrintinglodewPas encore d'évaluation

- What Are Application Security RisksDocument3 pagesWhat Are Application Security RisksSrinivasan KrishnanPas encore d'évaluation

- On Chain Finance ReportDocument7 pagesOn Chain Finance ReportSivasankaran KannanPas encore d'évaluation

- DELL Latitude D420 COMPAL LA-3071P Rev 1.0 SchematicsDocument59 pagesDELL Latitude D420 COMPAL LA-3071P Rev 1.0 SchematicsviniciusvbfPas encore d'évaluation

- Romney Ais14 CH 16 General Ledger and Reporting SystemDocument11 pagesRomney Ais14 CH 16 General Ledger and Reporting SystemHabteweld EdluPas encore d'évaluation

- Harvard Apparatus, Model 44 Syringe Pump User ManualDocument56 pagesHarvard Apparatus, Model 44 Syringe Pump User ManualthynameisraymondPas encore d'évaluation

- Open Source Software Notice 800885Document51 pagesOpen Source Software Notice 800885mohamedzerhouniPas encore d'évaluation

- SEO Cheat SheetDocument5 pagesSEO Cheat SheetIvona Ivkovic100% (2)

- Control System Applied Principles of ControlDocument23 pagesControl System Applied Principles of ControlAngelus Vincent GuilalasPas encore d'évaluation