Académique Documents

Professionnel Documents

Culture Documents

Floating Point Multiplier With The Use of Alu

Transféré par

bindu_ankuTitre original

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

Floating Point Multiplier With The Use of Alu

Transféré par

bindu_ankuDroits d'auteur :

Formats disponibles

32 Bit Floating Point Arithmetic Logic Unit ALU Design and Simulation

Shuchita Pare*1

shuchi786@gmail.com Shuchita Pare, Electronics & Comm. Dept Abstract- A floating point arithmetic and logic unit design using pipelining is proposed. By using pipeline with ALU design, ALU provides a high performance. With pipelining concept ALU execute multiple instructions simultaneously. Floating point ALU unit is formed by combination of arithmetic modules (addition, subtraction, multiplication, division), logical operation module (AND, OR, NOT). Each module is divided into sub-module. Bits selection determines which operation takes place at a particular time. The design is and validated using vhdl simulation in the xilinx12.1i software. Keywords - ALU - Arithmetic Logic Unit, TopDown Design, Validation, Floating Point, TestVector. I. INTRODUCTION: In recent years, Floating-point numbers are widely adopted in many applications due to its high dynamic range and good robustness against quantization errors, capabilities. Fixed point arithmetic implementation of numbers is acceptable as long as the degree of performance degradation is tolerable for a particular application under consideration whereas, Floating-point representation is able to retain its resolution and accuracy. IEEE specified standard for floatingpoint representation known as IEEE 754 in 1985.This standard makes floating-point representation for digital systems platformindependent so that data can be interchanged freely among different digital systems. IEEE 754 [1] standard presents two different floating point formats, Binary interchange format and Decimal interchange format. This paper focuses only on single precision normalized binary interchange format. The IEEE 754 single precision binary format representation consists of a one bit sign, an eight bit exponent, and a twenty three bit fraction Mantissa. Arithmetic logical unit or ALU is a combinational network that perform arithmetic and logical operation on the data. It is a building block of CPU. In order to perform computation inputs data is given to the ALU and a code from the control unit

Dr. Rita Jain*2

ritajain_bpl@yahoo.com Dr. Rita Jain, Electronics & Comm. Dept indicating which operation to perform. Its output is the result of the computation. The ALU with floating point operations is called a FPU. Pipelines are widely used to improve the performance of digital system, it is used to increase system throughput. The fundamental idea is to divide the processing of a computer instruction into a series of independent steps. Pipelining helps each step to carry data at once and each step is connected to the next so that at no time machine is idle and after few steps output is available at each clock execution. Implementing pipeline requires various phases of floating point operations be separated and be pipelined into sequential stages. we proposed floating point ALU design, for describing and simulating design we used VHDL, in order to ease the description, verification, simulation and hardware realization. VHDL is a widely adopted standard and has numerous capabilities that are suited for designs of this sort.

II. MATERIAL & METHODOLOGY

This paper focuses on the design of floating point ALU using pipelining technique in vhdl environment. This Design follows 32 bit single precision IEEE 754 standards. Floating point representations supporting the four basic arithmetic operations; addition, subtraction, multiplication, division and logical operation are described in this section. In order to design ALU using VHDL the Specifications for a 32-bit single precision floatingpoint ALU design are: 1. Input 'A', 'B', and output 'Results' are 32-bit binary floating-point (single precision). 2. Operands A and B operate as follows: A (operation) B = Results Where operation can be addition, subtraction, multiplication, division and logical. 3. 'Selection' a 3-bit input signal that selects ALU operation and operate as shown in table 1

Selection 000 001 010 011 100 101 110 111

Operation No operation Invert Anding ORing Addition Substraction Multiplication Division

multiplexer and multiplexer. De-multiplexer with the help of selection bit determines which task is to be performed. After the completion of the task, output and status signal are send to multiplexer where they combined with the other output from corresponding module to produce output result. Clock is specifically given rather than tied permanently each module, to save the power. Since only the selected functional modules need clock signal. III. FLOATING POINT ADDITION SUBSTRACTION MODULE: In floating point addition (or subtraction), the exponents of the two floating point operands must be equalize. So in the adder/subtracter unit, the exponent of the smaller number is incremented such that both exponents are equal and the mantissa of the small number is then shifted right 'n' times where 'n' is the difference between the large and small exponents. After the addition/subtraction operation is performed, the resultant mantissa is normalized using the LOD method. The LOD detects the most significant '1' by counting the number of zeros (nz) before the most significant '1'. The mantissa is then shifted left 'nz' times. Due to the excess shifting required before and after the addition/subtraction operation in the prenormalization of the smaller number and the post normalization of the resultant mantissa respectively. To increase the maximum operating speed of the adder/subtracter unit all the shift operations in the pre-normalization and post normalization steps were performed through barrel shifting. Barrel shifting has the advantage of shifting the data by any number of bits in one operation which makes barrel shifting suitable for the shifting operations required in the adder/subtracter unit that can be a shift by any number between 1 and 253 depending on the difference between the exponents of the input operands. LOD Floating Point Adder/Subtracter Unit. The general block diagram of the floating point adder/subtracter module is illustrated in Fig. 2. Its general structure is similar to that introduced in [2] and [5]. The proposed design has the following main modules:

Table 1: Selection Bit 4. 'Status' a 4-bit output signals. It notifies the state of the arithmetic results as follows:

Status Normal operation Overflow Underflow Result zero

0000 0001 0010 0100

Table 2: Status 5. Only the module that is selected using a demultiplexer apply the clock cycle and saves it. 6. Concurrent processes are used to allow processes to run in parallel, hence pipelining.

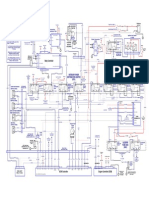

Fig 1. Top view of ALU design ALU operations are divided into six smaller modules: addition, subtraction, multiplication, division, logical and is controlled though de-

Fig 2. Block Diagram of Adder/Subtracter

Adder/Subtracter Module: 1) Unpack: The sign, exponent and mantissa of both operands are separated. A flag, aequalb flag, is set if both inputs are equal. The aequalb flag will be used if the effective operation, determined in the adder/subtracter module, was subtraction to set a flag indicating a zero output. This prevents unnecessary addition/subtraction and pre normalization operations from taking place. 2) Swap: Inputs are swapped if necessary such that operand A carries the larger floating point number and operand B is the smaller operand to be prenormalized. A swap flag is set if the operands were swapped to be used in determining the effective operation in the adder/subtracter module. 3) Zero Detect: An appropriate flag is set if one or both input operands is a zero. This helps avoid unnecessary calculations and normalizations when a zero operand is detected. The resultant exponent and the difference between the two exponents are determined here. 4) Pre-normalize: The smaller mantissa, of operand B, is pre-normalized, that is it's shifted by the difference between the two input exponents. Three extra bits the guard bit, the round bit, and the sticky bit are added to both mantissas to increase the accuracy of the performed operation (addition or subtraction) and to be used in the rounding process. Sticky bit is the logical "Or"ing of any bits that are dropped during the pre-normalization of operand B. 5) Adder/Subtracter: The effective operation to be performed is calculated according to the signs of operands A & B, the input operation and the swap flag. The effective operation is performed and the zero flag is updated if the effective operation is subtraction and the aequalb flag is set. 6) Post Normalize: The resultant mantissa is normalized after the leading one is detected using the LOD method. The resultant exponent is adjusted accordingly. 7) Rounding: The resultant mantissa is rounded using the REN technique. The final output is given in IEEE format. IV. FLOATING POINT MULTIPLIER MODULE: In floating point numbers, multiplication of two numbers is basically performed through adding their exponents and multiplying their mantissas. Multiplier Module: Floating point multiplier unit block diagram is illustrated in Fig. 3. Its general structure is similar to that introduced in [7] and [8]. The proposed design has the following main modules:

Fig 3: Block Diagram of Multiplier 1) Zero Detect: It is used to set a zero flag when any of the input operands is zero. This avoids unnecessary calculations throughout the multiplier module when a zero input is applied. The sign, exponent and mantissa of each input operand are separated to be manipulated differently throughout the multiplier module. To prepare the mantissas for the multiplication operation, the dropped implied bit of each mantissa is set to 1. 2) Add Exponents: To determine the resultant exponent, the exponents are added and a 127 bias is subtracted. The bias subtraction compensates for the bias having been added in both exponents. The result is fit into a 10 bit exponent to allow checking for overflow or underflow in the post multiply normalization step. Since the 8 bit exponent of a single precision floating point number is an unsigned number, the 10th bit set to '1' indicates an underflow. An overflow is detected when the 10th bit is '0' and the 9th bit is '1'. Fig.3. Block Diagram of Floating Point Multiplier Module 3) Block Multiplier: Multiplies the two 24 bit mantissa of operands A and B. the bottle neck of the design is the 24*24 bit multiplier used to calculate the resulting 48 bit mantissa. To increase the maximum operating speed of the multiplier, the proposed design breaks up the 24*24 bit multiplication of operands A and B into nine 8*8 bit multiplications where each mantissa is sliced into three 8-bit slices such that A=A2A1A0 B=B2B1B0. Then, B0 is multiplied in A2, A1 and A0. Each of these three 8*8 bit multiplications gives a 16 bit result. The three 16 bit results are properly manipulated to give a 32 bit result Ro of the 24*8 bits multiplication operation (i.e. A*B0). In a similar manner B1 and B2 are multiplied in A2, A1 and A0 to give R1 and R2. R1 and R2 are properly shifted to be added to R0 thus giving the 48 bit result mantissa. The result sign is determined through a simple XOR operation. 4) Post Normalize: The implied bit is located and dropped. The 48 bit mantissa from the multiplication operation is then truncated to a 26 bit mantissa which are the 23 bits assigned for the mantissa along with three extra bits to increase the accuracy of the rounding process. These three extra bits are the guard, round and sticky bits. The guard

and round bits are just an extension added to the mantissa to allow for extra precision. Sticky bit is the logical "Or"ing of all the truncated bits. The exponent is adjusted and checked for overflow or underflow and the appropriate flag is set accordingly. 5) Rounding: The 26 bit resultant mantissa is rounded to a 23 bits using the REN technique. After rounding, the exponent is checked again for possible overflow. Finally, the sign, exponent and mantissa are appended together to give the single precision floating point multiplication result in the IEEE format along with the overflow and underflow flags. V. FLOATING POINT DIVISION MODULE: Process of multiplication and division is almost same only difference lies is, for division exponent of two operand are subtracted and their significant are divided. If the result lies outside the permitted range normalization is required. VI. RESULT: The design code of single precision 32 bit floating point arithmetic and logic unit is simulated using test bench and verified the output. In the fig 4 shows simulated waveform of operations performed in test bench are addition, subtraction, division and logical operation successfully.

form entire unit. Proposed Floating point ALU is successfully designed, implemented and tested on simulating design with several test vectors. Currently we are working on further research work that will reduce hardware complexity in terms of synthesis and fully download the code on SPARTNA 3 FPGA. VIII. REFERENCES [1] IEEE standards board, IEEE standard for Binary Floating Point Arithmetic, New York: IEEE,1985. [2] Ibne Reaz Mamu Bin, Pipeline Floating Point ALU Design using VHDL, ICSE 2002 Proc. 2002, Malaysia 2002 [3] Malik ali,A study on the floating-point adder in FPGAS IEEE CCECE/CCGEI, Ottawa, May

2006

[4] M. Daumas, C. Finot, "Division of Floating Point Expansions with an Application to the Computation of the Determinant, Journal of Universal Computer Science, Vol. 1 No.6, pp 323-338, June 1999. [5] Singh Rajit Ram, Tiwari Asish, VHDL environment for floating point Arithmetic Logic Unit ALU design and simulation, International Conference on Communication Systems and Network Technology, 2011

Fig 4. Top view of ALU design VII. CONCLUSION A 32 bit Floating point ALU is designed using pipelining concept. Here in addition with basic operation such as addition, subtraction, multiplication, division on ALU other operation are also described such as logical operation etc. Because of which the capability of ALU increases. Coding is performed in top down approach. Each sub-module is designed separately in VHDL environment. Sub-module were then connected to

Vous aimerez peut-être aussi

- 32 Bit Multiplication and Division ALU Design Based On RISC StructureDocument4 pages32 Bit Multiplication and Division ALU Design Based On RISC StructureVishnu Kumar NadarPas encore d'évaluation

- Introduction to the simulation of power plants for EBSILON®Professional Version 15D'EverandIntroduction to the simulation of power plants for EBSILON®Professional Version 15Pas encore d'évaluation

- Design and Implementation of Floating Point ALU With Parity Generator Using Verilog HDLDocument6 pagesDesign and Implementation of Floating Point ALU With Parity Generator Using Verilog HDLIOSRjournalPas encore d'évaluation

- Hacks To Crush Plc Program Fast & Efficiently Everytime... : Coding, Simulating & Testing Programmable Logic Controller With ExamplesD'EverandHacks To Crush Plc Program Fast & Efficiently Everytime... : Coding, Simulating & Testing Programmable Logic Controller With ExamplesÉvaluation : 5 sur 5 étoiles5/5 (1)

- Design and Implementation of Reconfigurable Alu On FpgaDocument4 pagesDesign and Implementation of Reconfigurable Alu On FpgajeetendrasidhiPas encore d'évaluation

- Preliminary Specifications: Programmed Data Processor Model Three (PDP-3) October, 1960D'EverandPreliminary Specifications: Programmed Data Processor Model Three (PDP-3) October, 1960Pas encore d'évaluation

- Lab 6Document11 pagesLab 6vivek2mbPas encore d'évaluation

- Digital Differential Analysers: International Series of Monographs on Electronics and InstrumentationD'EverandDigital Differential Analysers: International Series of Monographs on Electronics and InstrumentationPas encore d'évaluation

- Assignment Unit 3 - With AnswerDocument6 pagesAssignment Unit 3 - With AnswereuanaresPas encore d'évaluation

- Synthesis of Single Precision Floating Point ALU: Department of Electronics and Communication EngineeringDocument20 pagesSynthesis of Single Precision Floating Point ALU: Department of Electronics and Communication EngineeringNagendra PrasadPas encore d'évaluation

- Irjet V5i3295 PDFDocument3 pagesIrjet V5i3295 PDFchaitanya sPas encore d'évaluation

- 32 Bit Floating Point ALUDocument7 pages32 Bit Floating Point ALUBalachandarVetrivelan80% (5)

- S7 Calculation FunctionsDocument27 pagesS7 Calculation Functionsplim5ollPas encore d'évaluation

- Project Report About MultipliersDocument62 pagesProject Report About Multiplierssenthilvl80% (5)

- ALU MISSDV0716 G.kaladhar Design PlanDocument16 pagesALU MISSDV0716 G.kaladhar Design Plangourishettikaladhar562Pas encore d'évaluation

- Lab 1Document9 pagesLab 1Chinmayi AvasaralaPas encore d'évaluation

- Chapter 4 PLC ProgrammingDocument100 pagesChapter 4 PLC ProgrammingMuhd Izwan Ikhmal RosliPas encore d'évaluation

- 2377 0 Pap APCCAS06 LXY ModMulInvDocument4 pages2377 0 Pap APCCAS06 LXY ModMulInvraj_rajesh_6Pas encore d'évaluation

- Emailing Fourth Module - IAMDocument35 pagesEmailing Fourth Module - IAMBhbPas encore d'évaluation

- Design & Simulation of 32-Bit Floating Point AluDocument3 pagesDesign & Simulation of 32-Bit Floating Point AluVikas PakhretiaPas encore d'évaluation

- Unit 21799p P.L.C. IIDocument18 pagesUnit 21799p P.L.C. IIcataicePas encore d'évaluation

- PLC and SCADADocument77 pagesPLC and SCADAIshwari GhulePas encore d'évaluation

- B1 Group3Document13 pagesB1 Group3Kausar ParvejPas encore d'évaluation

- Implementation of A High Speed Single Precision Floating Point Unit Using VerilogDocument5 pagesImplementation of A High Speed Single Precision Floating Point Unit Using VerilogVikas PakhretiaPas encore d'évaluation

- Cacho, KathleenJoyC. (ESD FE)Document5 pagesCacho, KathleenJoyC. (ESD FE)KATHLEEN JOY CACHOPas encore d'évaluation

- ELEC 470 Project Report Dongpu JinDocument25 pagesELEC 470 Project Report Dongpu JinJubayer Al-mahmod TxffuzPas encore d'évaluation

- Design of Efficient Multiplier Using VHDLDocument50 pagesDesign of Efficient Multiplier Using VHDLNagendra KashyapPas encore d'évaluation

- Implementation of Binary To Floating Point Converter Using HDLDocument41 pagesImplementation of Binary To Floating Point Converter Using HDLSujan KumarPas encore d'évaluation

- VHDL Microproject ReportDocument15 pagesVHDL Microproject ReportHitesh TumsarePas encore d'évaluation

- D 32-CPU: Esign of A Bit Single CycleDocument11 pagesD 32-CPU: Esign of A Bit Single CycleAritra GuptaPas encore d'évaluation

- Chapter 1Document8 pagesChapter 1NIKHIL PUJARIPas encore d'évaluation

- 10 1 1 961 4530 PDFDocument5 pages10 1 1 961 4530 PDFAnju BalaPas encore d'évaluation

- ITCL01EDocument2 pagesITCL01EDan Mitchelle CanoPas encore d'évaluation

- VHDL Implementation of 8-Bit ALU: Arshabha AryaDocument7 pagesVHDL Implementation of 8-Bit ALU: Arshabha Aryamohammad aidilPas encore d'évaluation

- Design of 8 Bit Alu Using Microwind 3.1Document6 pagesDesign of 8 Bit Alu Using Microwind 3.1ijaert100% (1)

- Allen Bradley PLC ProgrammingDocument44 pagesAllen Bradley PLC ProgrammingEduardo Luna91% (11)

- Chapter 2 Hardware and Software Design IssuesDocument12 pagesChapter 2 Hardware and Software Design IssuespurushresthaPas encore d'évaluation

- Digital CalenderDocument5 pagesDigital CalenderSARATH SASIPas encore d'évaluation

- Iteces 2 5 3Document5 pagesIteces 2 5 3Bhaskar GPas encore d'évaluation

- Floating Point Arithmetic Unit Using VerilogDocument6 pagesFloating Point Arithmetic Unit Using Verilognamdt10% (1)

- Algorithm and DesignDocument6 pagesAlgorithm and DesignhaigshaiPas encore d'évaluation

- PLC Ladder Simulator PDFDocument15 pagesPLC Ladder Simulator PDFDonate DonatePas encore d'évaluation

- Arithmetic and Logic Unit (ALU) PDFDocument13 pagesArithmetic and Logic Unit (ALU) PDFnathulalusaPas encore d'évaluation

- WEEK 13:: ObjectivesDocument35 pagesWEEK 13:: ObjectivesJohn Kenneth MantesPas encore d'évaluation

- Introduction To PLC Programming and Implementation-From Relay Logic To PLC LogicDocument2 pagesIntroduction To PLC Programming and Implementation-From Relay Logic To PLC LogicRitesh SharmaPas encore d'évaluation

- Advanced Diploma IN Computers, Electronics and CommunicationsDocument8 pagesAdvanced Diploma IN Computers, Electronics and CommunicationsKasun Rajitha MawellaPas encore d'évaluation

- DP 2 SolDocument14 pagesDP 2 Solchanuka469Pas encore d'évaluation

- Lecture 14: Let's Put Together A Manual Processor: Customer SpecificationDocument5 pagesLecture 14: Let's Put Together A Manual Processor: Customer SpecificationrinobiPas encore d'évaluation

- 1.1 MotivationDocument95 pages1.1 MotivationVijayPas encore d'évaluation

- Computer Architecture - Project 03Document20 pagesComputer Architecture - Project 03daiyan87Pas encore d'évaluation

- Virtex Power Estimator User Guide: Application NoteDocument5 pagesVirtex Power Estimator User Guide: Application NotefusionmasterPas encore d'évaluation

- Simulink Model Controllers Ee371 Control Systems Tech NoteDocument3 pagesSimulink Model Controllers Ee371 Control Systems Tech NoteShaheer DurraniPas encore d'évaluation

- FPGA Based 32 Bit ALU For Automatic Antenna Control Unit SM - Adnan21@Document5 pagesFPGA Based 32 Bit ALU For Automatic Antenna Control Unit SM - Adnan21@Edwin GeraldPas encore d'évaluation

- Cpu DesignDocument11 pagesCpu DesignnatyPas encore d'évaluation

- Lab 5 Counters and Shift RegistersDocument8 pagesLab 5 Counters and Shift RegistersAhmed Razi UllahPas encore d'évaluation

- Floating Point ProcessorDocument5 pagesFloating Point Processormoha7178Pas encore d'évaluation

- Ladder Logic Symbols - 4Document9 pagesLadder Logic Symbols - 4BILLYPas encore d'évaluation

- DSD Lab 06Document9 pagesDSD Lab 06Mohib HaroonPas encore d'évaluation

- 5EC3-01: Computer Architecture: UNIT-2Document17 pages5EC3-01: Computer Architecture: UNIT-2Himanshi SainiPas encore d'évaluation

- Intelligent Pollution Control SystemDocument39 pagesIntelligent Pollution Control Systembindu_ankuPas encore d'évaluation

- Floating PointDocument3 pagesFloating Pointbindu_ankuPas encore d'évaluation

- I 2 CDocument59 pagesI 2 Cbindu_ankuPas encore d'évaluation

- Floating Point MultiplierDocument35 pagesFloating Point Multiplierbindu_ankuPas encore d'évaluation

- Swing Door Installation ManualDocument28 pagesSwing Door Installation Manualmararuly biliyantoPas encore d'évaluation

- Keller: P T T S 21 RDocument2 pagesKeller: P T T S 21 RAmal AntonyPas encore d'évaluation

- HR Wallingford-009 - Wave - GaugeDocument2 pagesHR Wallingford-009 - Wave - GaugeSutanto HadiPas encore d'évaluation

- IPFCDocument6 pagesIPFCsabarnadhkPas encore d'évaluation

- Dold TimerDocument19 pagesDold TimerHemraj Singh RautelaPas encore d'évaluation

- Ceina Optical Metro 5100 5200 For Service Providers DSDocument5 pagesCeina Optical Metro 5100 5200 For Service Providers DSMohd ImranPas encore d'évaluation

- Cbse 12th 2019 Physics Answer Key Solution 55 2 1 by Govt PDFDocument21 pagesCbse 12th 2019 Physics Answer Key Solution 55 2 1 by Govt PDFbhabesh acharyaPas encore d'évaluation

- Smart Home Automation Based On Iot Using Arduino Mega: Abstract-In The Advancement of TechnologiesDocument4 pagesSmart Home Automation Based On Iot Using Arduino Mega: Abstract-In The Advancement of TechnologiesUdupiSri groupPas encore d'évaluation

- Introduction About VFDDocument3 pagesIntroduction About VFDHuzaifa WasimPas encore d'évaluation

- Confidential: Service ManualDocument108 pagesConfidential: Service Manualmrservice7782100% (1)

- BEDIA Level MonitoringDocument29 pagesBEDIA Level Monitoringm_najmanPas encore d'évaluation

- Modulation Compression in Next Generation RAN: Air Interface and Fronthaul Trade-OffsDocument7 pagesModulation Compression in Next Generation RAN: Air Interface and Fronthaul Trade-Offsfalcon032Pas encore d'évaluation

- Data Sheet: TDA1310ADocument17 pagesData Sheet: TDA1310ARogerio E. SantoPas encore d'évaluation

- Physics Investigatory ProjectDocument15 pagesPhysics Investigatory Projecttdycfgjdyjf82% (11)

- ME1117 (Pb-Free) : 1A Low Dropout Voltage RegulatorDocument9 pagesME1117 (Pb-Free) : 1A Low Dropout Voltage RegulatorGeovanny SanJuanPas encore d'évaluation

- Bose SoundLink Revolve - ManualDocument590 pagesBose SoundLink Revolve - ManualPhilippe PeetermansPas encore d'évaluation

- LonWorks Design Guide BRDocument14 pagesLonWorks Design Guide BRasifaliabidPas encore d'évaluation

- Icon Pro StarDocument1 pageIcon Pro Staramateur123456100% (1)

- DDR TI GuidelinesDocument41 pagesDDR TI Guidelinesnusha aPas encore d'évaluation

- Huawei BTS3900A Installation Guide V1.0Document29 pagesHuawei BTS3900A Installation Guide V1.0Ganidu Rochana100% (2)

- Broadband Networks Prof. Dr. Abhay Karandikar Electrical Engineering Department Indian Institute of Technology, Bombay Lecture - 29 Voice Over IPDocument22 pagesBroadband Networks Prof. Dr. Abhay Karandikar Electrical Engineering Department Indian Institute of Technology, Bombay Lecture - 29 Voice Over IPKrishna GhimirePas encore d'évaluation

- A Broadband 10-43-GHz High-Gain LNA MMICDocument4 pagesA Broadband 10-43-GHz High-Gain LNA MMICسري صالحPas encore d'évaluation

- Ed Mini ProjectDocument5 pagesEd Mini ProjectShivanshu TripathiPas encore d'évaluation

- LV Cable TestsDocument18 pagesLV Cable TestsEbrahim ArzaniPas encore d'évaluation

- Atasheet en 201508 T58I-E-02 Rev3 2Document17 pagesAtasheet en 201508 T58I-E-02 Rev3 2deri mardiPas encore d'évaluation

- FORTRAN Based ApproachDocument22 pagesFORTRAN Based ApproachGS EKTAPas encore d'évaluation

- Phase Failure RelayDocument2 pagesPhase Failure RelayAnonymous w63sFQiQPas encore d'évaluation

- Copy Tripping and Control of Impulse GeneratorDocument14 pagesCopy Tripping and Control of Impulse Generatorrare machinePas encore d'évaluation

- Homework Assignment #1 (Due Tuesday August 30th)Document19 pagesHomework Assignment #1 (Due Tuesday August 30th)NaniPas encore d'évaluation

- Unlock Any Roku Device: Watch Shows, TV, & Download AppsD'EverandUnlock Any Roku Device: Watch Shows, TV, & Download AppsPas encore d'évaluation

- Chip War: The Quest to Dominate the World's Most Critical TechnologyD'EverandChip War: The Quest to Dominate the World's Most Critical TechnologyÉvaluation : 4.5 sur 5 étoiles4.5/5 (227)

- CompTIA Security+ All-in-One Exam Guide, Sixth Edition (Exam SY0-601)D'EverandCompTIA Security+ All-in-One Exam Guide, Sixth Edition (Exam SY0-601)Évaluation : 5 sur 5 étoiles5/5 (1)

- Computer Science: A Concise IntroductionD'EverandComputer Science: A Concise IntroductionÉvaluation : 4.5 sur 5 étoiles4.5/5 (14)

- Chip War: The Fight for the World's Most Critical TechnologyD'EverandChip War: The Fight for the World's Most Critical TechnologyÉvaluation : 4.5 sur 5 étoiles4.5/5 (82)

- iPhone X Hacks, Tips and Tricks: Discover 101 Awesome Tips and Tricks for iPhone XS, XS Max and iPhone XD'EverandiPhone X Hacks, Tips and Tricks: Discover 101 Awesome Tips and Tricks for iPhone XS, XS Max and iPhone XÉvaluation : 3 sur 5 étoiles3/5 (2)

- CompTIA A+ Complete Review Guide: Core 1 Exam 220-1101 and Core 2 Exam 220-1102D'EverandCompTIA A+ Complete Review Guide: Core 1 Exam 220-1101 and Core 2 Exam 220-1102Évaluation : 5 sur 5 étoiles5/5 (2)

- CompTIA A+ Complete Practice Tests: Core 1 Exam 220-1101 and Core 2 Exam 220-1102D'EverandCompTIA A+ Complete Practice Tests: Core 1 Exam 220-1101 and Core 2 Exam 220-1102Pas encore d'évaluation

- Amazon Echo Manual Guide : Top 30 Hacks And Secrets To Master Amazon Echo & Alexa For Beginners: The Blokehead Success SeriesD'EverandAmazon Echo Manual Guide : Top 30 Hacks And Secrets To Master Amazon Echo & Alexa For Beginners: The Blokehead Success SeriesPas encore d'évaluation

- Amazon Web Services (AWS) Interview Questions and AnswersD'EverandAmazon Web Services (AWS) Interview Questions and AnswersÉvaluation : 4.5 sur 5 étoiles4.5/5 (3)

- Mastering IoT For Industrial Environments: Unlock the IoT Landscape for Industrial Environments with Industry 4.0, Covering Architecture, Protocols like MQTT, and Advancements with ESP-IDFD'EverandMastering IoT For Industrial Environments: Unlock the IoT Landscape for Industrial Environments with Industry 4.0, Covering Architecture, Protocols like MQTT, and Advancements with ESP-IDFPas encore d'évaluation

- Programming with STM32: Getting Started with the Nucleo Board and C/C++D'EverandProgramming with STM32: Getting Started with the Nucleo Board and C/C++Évaluation : 3.5 sur 5 étoiles3.5/5 (3)

- Hacking With Linux 2020:A Complete Beginners Guide to the World of Hacking Using Linux - Explore the Methods and Tools of Ethical Hacking with LinuxD'EverandHacking With Linux 2020:A Complete Beginners Guide to the World of Hacking Using Linux - Explore the Methods and Tools of Ethical Hacking with LinuxPas encore d'évaluation

- Windows 10 Mastery: The Complete User Guide to Learn Windows 10 from Beginner to ExpertD'EverandWindows 10 Mastery: The Complete User Guide to Learn Windows 10 from Beginner to ExpertÉvaluation : 3.5 sur 5 étoiles3.5/5 (6)

- iPhone 14 Guide for Seniors: Unlocking Seamless Simplicity for the Golden Generation with Step-by-Step ScreenshotsD'EverandiPhone 14 Guide for Seniors: Unlocking Seamless Simplicity for the Golden Generation with Step-by-Step ScreenshotsÉvaluation : 5 sur 5 étoiles5/5 (2)

- Raspberry Pi Retro Gaming: Build Consoles and Arcade Cabinets to Play Your Favorite Classic GamesD'EverandRaspberry Pi Retro Gaming: Build Consoles and Arcade Cabinets to Play Your Favorite Classic GamesPas encore d'évaluation

- How to Jailbreak Roku: Unlock Roku, Roku Stick, Roku Ultra, Roku Express, Roku TV with Kodi Step by Step GuideD'EverandHow to Jailbreak Roku: Unlock Roku, Roku Stick, Roku Ultra, Roku Express, Roku TV with Kodi Step by Step GuideÉvaluation : 1 sur 5 étoiles1/5 (1)

- CompTIA A+ Complete Review Guide: Exam Core 1 220-1001 and Exam Core 2 220-1002D'EverandCompTIA A+ Complete Review Guide: Exam Core 1 220-1001 and Exam Core 2 220-1002Évaluation : 5 sur 5 étoiles5/5 (1)

- iPhone Unlocked for the Non-Tech Savvy: Color Images & Illustrated Instructions to Simplify the Smartphone Use for Beginners & Seniors [COLOR EDITION]D'EverandiPhone Unlocked for the Non-Tech Savvy: Color Images & Illustrated Instructions to Simplify the Smartphone Use for Beginners & Seniors [COLOR EDITION]Évaluation : 5 sur 5 étoiles5/5 (2)

- Real-Time UML Workshop for Embedded SystemsD'EverandReal-Time UML Workshop for Embedded SystemsÉvaluation : 3.5 sur 5 étoiles3.5/5 (2)

- Raspberry Pi for Python Programmers Cookbook - Second EditionD'EverandRaspberry Pi for Python Programmers Cookbook - Second EditionPas encore d'évaluation

- How To Market Mobile Apps: Your Step By Step Guide To Marketing Mobile AppsD'EverandHow To Market Mobile Apps: Your Step By Step Guide To Marketing Mobile AppsPas encore d'évaluation

- Essential iPhone X iOS 12 Edition: The Illustrated Guide to Using iPhone XD'EverandEssential iPhone X iOS 12 Edition: The Illustrated Guide to Using iPhone XÉvaluation : 5 sur 5 étoiles5/5 (1)

![iPhone Unlocked for the Non-Tech Savvy: Color Images & Illustrated Instructions to Simplify the Smartphone Use for Beginners & Seniors [COLOR EDITION]](https://imgv2-2-f.scribdassets.com/img/audiobook_square_badge/728318688/198x198/f3385cbfef/1714829744?v=1)