Académique Documents

Professionnel Documents

Culture Documents

Informe #2

Transféré par

Fer FloresTitre original

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

Informe #2

Transféré par

Fer FloresDroits d'auteur :

Formats disponibles

[ESCRIBA EL NOMBRE DE LA COMPAA]

SISTEMAS DIGITALES II

INFORME DE LABORATORIO 2

[Escriba el nombre del autor] 04/03/2013

SISTEMAS DIGITALES II LABORATORIO

INFORME N 2

1. OBJETIVO.Esta prctica tiene como objetivo el verificar el funcionamiento de un contador que es implementado utilizando Flip Flops JK. 2. MARCO TEORICO.Generalidades Siendo los Flip-Flop las unidades bsicas de todos los sistemas secuenciales, existen cuatro tipos: el RS, el JK, el T y el D. Y los ltimos tres se implementan del primero pudindose con posterioridad con cualquiera de los resultados confeccionar quienquiera de los restantes. Todos pueden ser de dos tipos, a saber: Flip-Flop activado por nivel (FF-AN) o bien Flip-Flop maestro-esclavo (FF-ME). El primero recibe su nombre por actuar meramente con los "niveles" de amplitud 0-1, en cambio el segundo son dos FF-AN combinados de tal manera que uno "hace caso" al otro. Un circuito flip-flop puede mantener un estado binario indefinidamente (Siempre y cuando se le este suministrando potencia al circuito) hasta que se cambie por una seal de entrada para cambiar estados. La principal diferencia entre varios tipos de flip-flops es el numero de entradas que poseen y la manera en la cual las entradas afecten el estado binario. Circuito bsico de un flip-flop Se menciono que un circuito flip-flop puede estar formado por dos compuertas NAND o dos compuertas NOR. Estas construcciones se muestran en los diagramas lgicos de las figuras. Cada circuito forma un flip-flop bsico del cual se pueden construir uno mas complicado. La conexin de acoplamiento intercruzado de la salida de una compuerta a la entrada de la otra constituye un camino de retroalimentacin. Por esta razn, loscircuitos se clasifican como circuitos secuenciales asincrnicos. Cada flip-flop tiene dos salidas, Q y Q y dos entradas S (set) y R (reset). Este tipo de flip-flop se llama Flip-Flop RS acoplado directamente o bloqueador SR (SR latch). Las letras R y S son las iniciales de los nombres en ingls de las entradas (reset, set). Flip-Flop JK Un flip-flop JK es un refinamiento del flip-flop SR en el sentido que la condicin indeterminada del tipo SR se define en el tipo JK. Las entradas J y K se comportan como las entradas S y R para iniciar y reinicia el flip-flop, respectivamente. Cuando las entradas J y K son ambas iguales a 1, una transicin de reloj alterna las salidas del flip-flop a su estado complementario. Su unidad bsica se dibuja a continuacin que, como acta por "niveles" de amplitud (0-1) recibe el nombre de Flip-Flop JK activado por nivel (FF-JK-AN). Cuando no se especifica este detalle es del tipo Flip-Flop JK maestro-esclavo (FF-JK-ME). Su ecuacin y tabla de funcionamiento son

SISTEMAS DIGITALES II LABORATORIO

Q = J q* + K* q

Se da detalle de su confeccin lgica a partir del FF-RS-AN.

y si simplificamos por ejemplo usando Veich-Karnaugh

R=Kq S = J q* resulta el circuito

SISTEMAS DIGITALES II LABORATORIO

Flip-flop JK Un flip-flop JK es un refinamiento del flip-flop RS ya que el estado independiente del termino RS se define en el tipo JK. Las entradas J y K se comportan como las entradas R y S para poner a uno o cero (set o reset) al flip-flop (ntese que en el flip-flop JK la entrada J se usa para la entrada de puesta a uno y la letra K para la entrada de puesta a cero). Cuando ambas entradas se aplican a J y K simultneamente, el flip-flop cambia a su estado de complemento, esto es, si Q=1 cambia a Q=0 y viceversa. Un flip-flop sincronizado se muestra en la figura anterior. La salida Q se aplica con K y CP a una compuerta AND de tal manera que el flip-flop se ponga a cero (clear) durante un pulso de reloj solamente si Q fue 1 previamente. De manera similar la salida Q se aplica a J y CP a una compuerta AND de tal manera que el flip-flop se ponga a uno con un pulso de reloj, solamente si Q fue 1 previamente. Flip-flop JK temporizado Como se muestra en la tabla caracterstica de la figura, el flip-flop JK se comporta como un flip-flop RS excepto cuando J y K sean ambos 1. Cuando J y K sean 1, el pulso de reloj se transmite a travs de una compuerta AND solamente; aquella cuya entrada se conecta a la salida del flip-flop la cual es al presente igual a 1. As, si Q=1, la salida de la compuerta AND superior se convertir en 1 una vez que se aplique un pulso de reloj y el flip-flop se ponga a cero. Si Q=1 la salida de la compuerta AND se convierte en 1 y el flip-flop se pone a uno. En cualquier caso, el estado de salida del flip-flop se complementa. Las entradas en el smbolo grfico para el flip-flop JK deben marcarse con una J (debajo de Q) y K (debajo de Q). La ecuacin caracterstica se da en la figura y se deduce del mapa de la tabla caracterstica. Ntese que debido a la conexin de retroalimentacin del flip-flop JK, la seal CP que permanece en 1 (mientras que J=K=1) causar transiciones repetidas y continuas de las salidas despus que las salidas hayan sido completadas. Para evitar esta operacin indeseable, los pulsos de reloj deben de tener un tiempo de duracin que es menor que la demora de propagacin a travs del flip-flop. Esta es una restriccin, ya que la operacin del circuito depende del ancho de los pulsos. Por esta razn los flip-flops JK nunca se construyen como se muestra en la figura. La restriccin del ancho del pulso puede ser eliminada con un maestro esclavo o una construccin activada por flanco de la manera discutida en la siguiente seccin. El mismo razonamiento se aplica al flip-flop T presentado a continuacin.

SISTEMAS DIGITALES II LABORATORIO

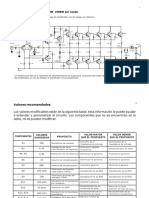

3. DESARROLLO DEL LABORATORIO.3.1. CIRCUITOS IMPLEMENTADOS: CONTADOR DIVISOR ASNCRONO DE DOS BITS

CONTADOR DIVISOR SNCRONO DE TRES BITS

CONTADOR DE DECADAS ASNCRONO

SISTEMAS DIGITALES II LABORATORIO

3.2. TABLAS: CONTADOR DIVISOR ASNCRONO DE DOS BITS CLK Flanco de bajada Flanco de bajada Flanco de bajada Flanco de bajada Q0 0 0 1 1 Q1 0 1 0 1 BINARIO 0 1 2 3

CONTADOR DIVISOR SNCRONO DE TRES BITS CLK Flanco de bajada Flanco de bajada Flanco de bajada Flanco de bajada Flanco de bajada Flanco de bajada Flanco de bajada Flanco de bajada Q0 0 0 0 0 1 1 1 1 Q1 0 0 1 1 0 0 1 1 Q2 0 1 0 1 0 1 0 1 BINARIO 0 1 2 3 4 5 6 7

CONTADOR DE DECADAS ASNCRONO CLK Flanco de bajada Flanco de bajada Flanco de bajada Flanco de bajada Flanco de bajada Flanco de bajada Flanco de bajada Flanco de bajada Flanco de bajada Flanco de bajada Flanco de bajada Flanco de bajada Flanco de bajada Flanco de bajada Flanco de bajada Flanco de bajada Q0 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 Q1 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1 Q2 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 Q3 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 BINARIO 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15

SISTEMAS DIGITALES II LABORATORIO

3.3. CALCULOS: R1= 1k R2= 22k C=

10nF

Este tipo de funcionamiento se caracteriza por una salida con forma de onda cuadrada (o rectangular) continua de ancho predefinido por el diseador del circuito. El esquema de conexin es el que se muestra. La seal de salida tiene un nivel alto por un tiempo t1 y un nivel bajo por un tiempo t2. La duracin de estos tiempos dependen de los valores de R1, R2 y C, segn las frmulas siguientes: ( ) ( ( y ( ) La frecuencia con que la seal de salida oscila est dada por la frmula: ) )

( el perodo es simplemente:

Si se requiere una seal cuadrada donde el ciclo de trabajo D sea del 50%, es decir que el tiempo t1 sea igual al tiempo t2, es necesario aadir un diodo en paralelo con R2 segn se muestra en la figura. Ya que, segn las frmulas, para hacer sera necesario que R1 fuera cero, lo cual en la prctica no funcionara. CORRECCIN: Para realizar un ciclo de trabajo igual al 50% se necesita colocar el resistor R1 entre la fuente de alimentacin y la terminal 7; desde la terminal 7 hacia el condensador se coloca un diodo con el nodo apuntando hacia el condensador, despus de esto se coloca un diodo con el ctodo del lado del condensador seguido del resistor R2 y este conjunto de

SISTEMAS DIGITALES II LABORATORIO

diodo y resistor en paralelo con el primer diodo, adems de esto los valores de los resistores R1 y R2 tienen que ser de la misma magnitud.

4. CONCLUSIONES.Se logr identificar la funcionalidad de un flip flop JK con flacos de bajada. Con la ayuda del DATA SHEET se arm los circuitos pedidos por el docente de laboratorio. Calibrar con suma precisin el RELOJ ya que con este integrado se podr identificar precisamente los cambios de los circuitos armados.

Vous aimerez peut-être aussi

- Perfil Momentum WheelsDocument1 pagePerfil Momentum WheelsFer FloresPas encore d'évaluation

- Apuntes de Introducción A La AdministraciónDocument34 pagesApuntes de Introducción A La AdministraciónFer FloresPas encore d'évaluation

- Ejercicios Básico en LabviewDocument14 pagesEjercicios Básico en LabviewFer FloresPas encore d'évaluation

- Laboratorio #6 6782530LPDocument4 pagesLaboratorio #6 6782530LPFer FloresPas encore d'évaluation

- LABORATORIO#2Document9 pagesLABORATORIO#2Fer FloresPas encore d'évaluation

- Comunicación Por RF Con MicrocontroladorDocument12 pagesComunicación Por RF Con MicrocontroladorFer FloresPas encore d'évaluation

- Redes IndustrialesDocument11 pagesRedes IndustrialesFer FloresPas encore d'évaluation

- Investigacion#1Document6 pagesInvestigacion#1Fer FloresPas encore d'évaluation

- Apuntamiento de Antena SatelitalDocument15 pagesApuntamiento de Antena SatelitalFer FloresPas encore d'évaluation

- Preinforme ControlDocument10 pagesPreinforme ControlFer FloresPas encore d'évaluation

- Ingeniería en Sistemas Electrónicos 8vo SemestreDocument17 pagesIngeniería en Sistemas Electrónicos 8vo SemestreFer FloresPas encore d'évaluation

- LABORATORIO#4Document9 pagesLABORATORIO#4Fer FloresPas encore d'évaluation

- Aplicaciones en Sistema Operativo AndroidDocument3 pagesAplicaciones en Sistema Operativo AndroidFer FloresPas encore d'évaluation

- Sistemas de Control IDocument17 pagesSistemas de Control IFer FloresPas encore d'évaluation

- LABORATORIO#3Document13 pagesLABORATORIO#3Fer FloresPas encore d'évaluation

- Preparación de artículos para publicaciones del IEEEDocument7 pagesPreparación de artículos para publicaciones del IEEEAndrés SuárezPas encore d'évaluation

- TareaDocument5 pagesTareaFer FloresPas encore d'évaluation

- Macro Econom I ADocument2 pagesMacro Econom I AFer FloresPas encore d'évaluation

- Teclado MatricialDocument2 pagesTeclado MatricialFer FloresPas encore d'évaluation

- Respuesta de Frecuencias AltasDocument3 pagesRespuesta de Frecuencias AltasFer FloresPas encore d'évaluation

- ApuntesDocument33 pagesApuntesFer FloresPas encore d'évaluation

- Investigacion#1Document16 pagesInvestigacion#1Fer FloresPas encore d'évaluation

- Filtros Activos PDFDocument9 pagesFiltros Activos PDFFer FloresPas encore d'évaluation

- Preinforme o Informe # 1 Filtros PasivosDocument20 pagesPreinforme o Informe # 1 Filtros PasivosFer FloresPas encore d'évaluation

- Filtros Activos PDFDocument9 pagesFiltros Activos PDFFer FloresPas encore d'évaluation

- Watchdog WDTDocument2 pagesWatchdog WDTFer FloresPas encore d'évaluation

- Filtros Activos PDFDocument9 pagesFiltros Activos PDFFer FloresPas encore d'évaluation

- Teoria de Display de 7 SegmentosDocument3 pagesTeoria de Display de 7 SegmentosFer FloresPas encore d'évaluation

- Datos LaboDocument6 pagesDatos LaboFer FloresPas encore d'évaluation

- Instrucciones de DireccionamientoDocument6 pagesInstrucciones de DireccionamientoFer FloresPas encore d'évaluation

- Consola de Programación: Cuadros de Maniobra Edel Advanced K2Document49 pagesConsola de Programación: Cuadros de Maniobra Edel Advanced K2Ruben NabalPas encore d'évaluation

- Normalización NTC para Empalme y Conectorizacion de Fibra Optica Transmision Om - OsDocument16 pagesNormalización NTC para Empalme y Conectorizacion de Fibra Optica Transmision Om - OssergioPas encore d'évaluation

- Manual Cargador de Pilas AA AAA y Cuadrada 9V Steren 903-210Document2 pagesManual Cargador de Pilas AA AAA y Cuadrada 9V Steren 903-210KhrimshaktPas encore d'évaluation

- LMSAT Manual EspaolDocument18 pagesLMSAT Manual EspaolJose Luis Moran ChinchayPas encore d'évaluation

- Guia N°4-Labresol-PwmDocument3 pagesGuia N°4-Labresol-PwmEdson BarrazaPas encore d'évaluation

- Fundamentos Diseño y Simulacion de Antenas Parte 1Document13 pagesFundamentos Diseño y Simulacion de Antenas Parte 1Franklin AntonioPas encore d'évaluation

- Amp Estero 1000w PDFDocument15 pagesAmp Estero 1000w PDFLilianitaRizoPas encore d'évaluation

- S15A - Sistemas Embebidos - Arduino - MecatronicaDocument49 pagesS15A - Sistemas Embebidos - Arduino - MecatronicaJorge GaelPas encore d'évaluation

- Codif-decodif-multi-demultiDocument9 pagesCodif-decodif-multi-demultisergio alvarezPas encore d'évaluation

- Laboratorio-07 Circuitos Temporizadores Aplicaciones BásicasDocument17 pagesLaboratorio-07 Circuitos Temporizadores Aplicaciones BásicasCésar Vilchez SilvaPas encore d'évaluation

- INVESTIGACION Circuito Timer 555Document8 pagesINVESTIGACION Circuito Timer 555Miguel Angel Velazquez CamposPas encore d'évaluation

- Practica 5 LinealDocument11 pagesPractica 5 LinealSandy Depp0% (1)

- Ee 112 Syllabus 2017 2Document6 pagesEe 112 Syllabus 2017 2anthonyal11Pas encore d'évaluation

- Multiplexación SDH y SONETDocument30 pagesMultiplexación SDH y SONETAcosta HectorPas encore d'évaluation

- Lab #3 Circuitos DigitalesDocument4 pagesLab #3 Circuitos Digitalessergio perezPas encore d'évaluation

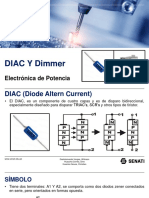

- Diac y DimmerDocument13 pagesDiac y DimmerUlt DincyclistPas encore d'évaluation

- MicrocontroladoresDocument19 pagesMicrocontroladoresJamesBIXD100% (1)

- Qdoc - Tips Informe 13 Instrumentacion IndustrialDocument34 pagesQdoc - Tips Informe 13 Instrumentacion Industrialalexander jimenezPas encore d'évaluation

- Rele de ProteccionDocument408 pagesRele de ProteccionDario SalinasPas encore d'évaluation

- MegafoniaDocument17 pagesMegafoniaEmmanuelSanzPas encore d'évaluation

- Lab 2 AutomatizaciónDocument6 pagesLab 2 AutomatizaciónJHOJAN ARLEY VARELA CARABALIPas encore d'évaluation

- Cap5 Pu18Document29 pagesCap5 Pu18Sabrina RepettoPas encore d'évaluation

- Panasonic DMP BD75Document34 pagesPanasonic DMP BD75shareatorPas encore d'évaluation

- Cualificación y certificación de redes para garantizar el rendimientoDocument4 pagesCualificación y certificación de redes para garantizar el rendimientoEduard José Acosta BuelvasPas encore d'évaluation

- Control DigitalDocument48 pagesControl DigitalEsgar Ivan Paucar JaboPas encore d'évaluation

- 07 TweeterDocument4 pages07 Tweeter01100% (1)

- Epi Laboratorio Citro B Quiquisola Viza Kevin Jaime 6Document9 pagesEpi Laboratorio Citro B Quiquisola Viza Kevin Jaime 6Steep HachePas encore d'évaluation

- Lista de Precios Pctintas 18 Mayo-CDocument9 pagesLista de Precios Pctintas 18 Mayo-CJuank MonsalvePas encore d'évaluation

- Andreina BbeDocument9 pagesAndreina Bberuben perniaPas encore d'évaluation

- Especificaciones Tecnicas 05082019Document103 pagesEspecificaciones Tecnicas 05082019Nestor ValentinoPas encore d'évaluation