Académique Documents

Professionnel Documents

Culture Documents

Low voltage CMOS Schmitt Trigger in 0.18μm technology: Faiz Arith, M.Idzdihar.Idris, M.N.Shah Zainudin, S. A. M. Chachuli

Titre original

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

Low voltage CMOS Schmitt Trigger in 0.18μm technology: Faiz Arith, M.Idzdihar.Idris, M.N.Shah Zainudin, S. A. M. Chachuli

Droits d'auteur :

Formats disponibles

IOSR Journal of Engineering (IOSRJEN) e-ISSN: 2250-3021, p-ISSN: 2278-8719 Vol. 3, Issue 3 (March.

2013), ||V2|| PP 08-15

Low voltage CMOS Schmitt Trigger in 0.18m technology

1

Faiz Arith, 2M.Idzdihar.Idris, 3M.N.Shah Zainudin, 4S. A. M. Chachuli

Faculty of Electronic and Computer Engineering Universiti Teknikal Malaysia Melaka Hang Tuah Jaya 76100 Durian Tunggal, Melaka, Malaysia

Abstract: This paper presents the effect of source voltage on performance of proposed Schmitt Trigger circuit. The proposed circuit was designed based on Conventional Schmitt Trigger by manipulating the arrangement of transistors and the width-length ratio. The simulation results have been carried out based on Mentor Graphics software in term of propagation delay. The circuit layout has been designed and checked by using design rule check (DRC) and layout versus schematic (LVS) method. From these results, the proposed full swing CMOS Schmitt Trigger was able to operate at low voltage (0.8V-1.5V) Keywords: DRC, LVS, mentor graphic, schmitt trigger, width-length ratio.

I. INTRODUCTION

The Schmitt Trigger circuit is widely used in analogue and digital circuit to solve the noise problem. Beside that this circuit is widely design in various styles in order to drive the load with fast switching, low power dissipation and low-supply voltage, especially for high capacitive load problem [1]. Conventional Schmitt Trigger is shown in Fig. 1 and the detail design is presented in [2] where the switching thresholds are dependent on the ratio of NMOS and PMOS. However, this circuit will exhibit racing phenomena after the transition starts. Therefore in this paper, we proposed CMOS Schmitt Trigger circuit which is capable to operate in low voltage (0.8V-1.5V) at high capacitance, less propagation delay and stable hysteresis width. By lowering the supply voltage is an effective method to achieve low power operation [3]-[4].

Figure 1: The Conventional Schmitt Trigger 1.1. CIRCUIT DESCRIPTION The proposed Schmitt Trigger [5] is shown in Fig. 2 and is categorized into two parts which is Part 1 and Part 2. Similarly to Conventional Schmitt Trigger, the proposed circuit is formed by a combination of two sub-circuit, P sub-circuit (which consists of P1, P2 and P3) and N sub-circuit (which consists of N1, N2 and N3). There is no direct connection between the source voltage and ground as P sub-circuit is connected to the path between the source voltage and output while the N sub-circuit is connected between the path of output and ground. Therefore, there is no static power consumption due to no direct path between source voltage and ground.

www.iosrjen.org

8|Page

Low voltage CMOS Schmitt Trigger in 0.18m technology

Figure 2: The Proposed Schmitt Trigger Part 1 of the proposed circuit forms a NAND gate is designed according to De Morgan`s Theorem. Two PMOS (P1 and P2) are formed by a parallel connection while two NMOS (N1 and N2) are formed by a series connection. By designing the PMOS in parallel, the resistance of the P sub-circuit will be reduced by halves. Thus, the propagation delay can be reduced as shown in equation (1).

(1) It is preferably to reduce PMOS delay because delay is more concentrated to PMOS due to high mobility of PMOS compare to NMOS. Part 2 of the Proposed Schmitt Trigger consists of a PMOS, (P3) and a NMOS, (N3) where both the MOSFET is directly connected through the gate terminal of each. The P3 act as pull up while the N3 act as a pull down for the output at each case. The sizings of the transistor are set by locating the minimum component path of each sub-circuit. Each of the transistors is sized accordingly to their arrangement. For transistors that are in series, they are scaled by factor of 2 each while transistors in parallel are scaled by a factor of 1each. The PMOS and NMOS ratio is set according to equation 2 with the effective length, (for 0.18 technologies).

(2) It is recommended to widen the PMOS transistor to allow the resistance matches the pull down NMOS device. Typically, [6].Therefore, the ratio is set to be three maximize the noise margin and to create a circuit with symmetrical voltage-transfer characteristic (VTC). By increasing the width of PMOS, it moves the switching threshold voltage towards , which makes the hysteresis width more rectangles which are desirable in a Schmitt Trigger design. When the input is low, only the P sub-circuit will be considered and causes the output to be high (equal to ). During this condition, both P1 and P2 are on, but P3 is off (because as P3`s source voltage and gate voltage is equal). Therefore, the output voltage is pull to . When the input increases to , N1 and N2 is turned on while is off. Thus, the output voltage is pull down to GND. 1.2 MENTOR GRAPHICS Today, ICs are fabricated with multimillion transistors and increasingly more metal layers as well as more routing on each layer. Their performance is determined by logic, interconnection, and other contributors.

www.iosrjen.org

9|Page

Low voltage CMOS Schmitt Trigger in 0.18m technology

Interconnects have become the most crucial especially, in deep and very deep submicron designs, where it can easily account for up to 90% of the global signal delay in a chip. Metal line parasitic resistances, capacitances, inductances, substrate losses from metal to ground and proximity effects, all lead to signal distortion, energy dissipation, voltage shifts, cross-talk, noise, and undesirable delays. Mentor Graphics has developed the IC Station Tool Suite, a complete IC design flow, from schematic capture to physical layout and verification. Thus, this software is the most suitable for ensuring immediate access to essential data and supports multiple hardware platforms that can make computing environment choices based on unique cost and performance needs. Besides, it also accurately predict the circuit performance, high performance, fast, and scalable interconnect models is necessary at all stages of the circuit analysis. ADK3 is an ASIC Design Kit for Mentor Graphic design tools that enables a designer to prepare an IC design which qualifies to be fabricated. There are 2 main tools in ADK3: Design Architect IC ( DA-IC) IC Station

II. METHODOLOGY

Design Architect-IC (DA-IC) is a full schematic capture application with a multilevel environment designed to optimize the creation of integrated circuits. DA-IC is used to create and simulate analog, RF, and mixed signal schematic designs. DA-IC provides an open architecture which allows to customize the application to fit specific needs. Fig. 3 shows the flow chart of Design Architect . Start

Design schematic

Check schematic

Generate symbol

Check symbol

Simulatio n

Run eldo

Error

Wave forms No error LVS

Simulation results

Prep for layout

Figure 3: Design Architect flow chart

III. RESULTS AND DISCUSSION

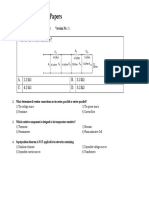

Three designs (1st, 2nd and 3rd Design) are simulated with technologies using Mentor Graphic software. The 1st Design represent the Conventional Schmitt Trigger with the ratio of transistor is set according to [7], 2nd Design represent the Conventional Schmitt Trigger with the ratio of transistor are set similarly with the 3rd Design which is the proposed Schmitt Trigger. The respective transistor dimensions for the three designs are shown in Table 1. The comparison is made in term of propagation delay.

www.iosrjen.org

10 | P a g e

Low voltage CMOS Schmitt Trigger in 0.18m technology

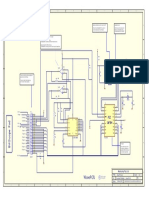

The proposed schematic circuit is designed and checked by using Mentor Graphic software. The wire connection is connected and all the parameter such as voltage, width and effective length is settled as shown in Fig. 4. The test bench as shown in Fig. 5 is designed including the other external schematic circuit support parts. For base line, the source voltage is set to be 0.8V. The results are view as waveform to verify the performance of schematic circuit. Fig. 6-9 shows the circuit simulation result of 0.8V, 1.0V, 1.2V and 1.5V. The results show that the proposed Schmitt Trigger is successfully operated and can be used in low source voltage operation condition [8]. The compilation of the simulation results is shown in Fig. 10. The propagation delays are less in high voltage source compare to low voltage due to the transistor effective resistance and wire.

Figure 4: Schematic Circuit

www.iosrjen.org

11 | P a g e

Low voltage CMOS Schmitt Trigger in 0.18m technology

Figure 5: Test Bench

Figure 6: Simulation result (0.8V)

Figure 7: Simulation results (1.0V)

www.iosrjen.org

12 | P a g e

Low voltage CMOS Schmitt Trigger in 0.18m technology

Figure 8: Simulation results (1.2V)

Figure 9: Simulation results (1.5V)

Figure 10: Compilation of simulation results

www.iosrjen.org

13 | P a g e

Low voltage CMOS Schmitt Trigger in 0.18m technology

The comparison of the propagation delay between those designs is showed in Fig 11 [9]. These results show that the 3rd design (proposed circuit) is the best circuit in low source voltage in term of propagation delay.

Figure 11: Comparison of Propagation Delay Then, circuit layout is designed according to the schematic circuit that has been created before as shown in Fig. 12. Circuit stick diagram is created as a base line to design the layout. The layout is checked by using DRC (Design Rule Check). Fundamentally, these design rules represent the physical limits of the manufacturing process. Fig. 13 shows the DRC successful result. Finally both schematic circuit and layout been checked by using LVS (Layout Versus Schematic) in term of connectivity, sizing and to identify any extra component that is needed. Fig. 14 shows that the combination of both schematic circuits and layout is confirmed and exactly suitable to be sending to be manufacture in industry.

Figure 12: Circuit Layout

Figure 13: Layout DRC simulation results

www.iosrjen.org

14 | P a g e

Low voltage CMOS Schmitt Trigger in 0.18m technology

Figure 14: Layout LVS simulation result

IV. CONCLUSION

A new proposed CMOS Schmitt Trigger is presented which is capable to function under low voltage as much as 0.8V. The circuit gives less propagation delay compare to the conventional circuit. The proposed circuit passed the DRC (Design Rule Check) and LVS (Layout Versus Schematic) checking method. Therefore the circuit is successfully implemented and confirmed to be manufactured in the industry.

REFERENCES

[1] Dejhan, K.; Tooprakai, P.; Rerkmaneewan, T.; Soonyeekan, C.; , "A high-speed direct bootstrapped CMOS Schmitt trigger circuit," IEEE International Conference on Semiconductor Electronics ICSE 2004. vol., no., pp. 4 pp., 7-9 Dec. 2004. Filanovsky, I.M.; Baltes, H.; "CMOS Schmitt trigger design," Circuits and Systems I: IEEE Transactions on Fundamental Theory and Applications, vol.41, no.1, pp.46-49, Jan 1994. Kulkarni, J.P.; Roy, K.; , "Ultralow-Voltage Process-Variation-Tolerant Schmitt-Trigger-Based SRAM Design," IEEE Transactions on Very Large Scale Integration (VLSI) Systems , vol.20, no.2, pp.319-332, Feb. 2012. Lotze, N.; Manoli, Y.; "A 62 mV CMOS Standard-Cell-Based Design Technique Using Schmitt-Trigger Logic," IEEE Journal of Solid-State Circuits, vol.47, no.1, pp.47-60, Jan. 2012. R. Sapawi R.L.S Chee, S. K. Sahari, S. Sulaili, Simulation of CMOS Schmitt Trigger, Asia-Pasific Conference on Applied Electromagnetics, 4-6 December 2007, Melaka. Rabaey J.M., A. Chandrakasan, Borivoje Nikolic, (2003). Digital Integrated circuits: A Design Perspective. 2nd Edition. New Jersey: Pearson Education. Wang, C.-S.; Yuan, S.-Y.; Kuo, S.-Y.; , "Full-swing BiCMOS Schmitt trigger," IEEE Proceedings Circuits, Devices and Systems, - , vol.144, no.5, pp.303-308, Oct 1997. Singhanath, P.; Suadet, A.; Kanjanop, A.; Thongleam, T.; Kuankid, S.; Kasemsuwan, V.; , "Low voltage adjustable CMOS Schmitt trigger," 2011 4th International Conference on Modeling, Simulation and Applied Optimization (ICMSAO), vol., no., pp.1-4, 19-21 April 2011. Sapawi, R.; Chee, R.L.S.; Sahari, S.K.; Julai, N.; , "Performance of CMOS Schmitt Trigger," International Conference on Computer and Communication Engineering ICCCE 2008. , vol., no., pp.1317-1320, 13-15 May 2008.

[2] [3]

[4] [5] [6] [7] [8]

[9]

www.iosrjen.org

15 | P a g e

Vous aimerez peut-être aussi

- Cmos Schmitt TriggerDocument6 pagesCmos Schmitt TriggerNESEGAPas encore d'évaluation

- Self Biased Cascode CM PDFDocument7 pagesSelf Biased Cascode CM PDFDhaval ShuklaPas encore d'évaluation

- Design of High Performance Dynamic CMOS Circuits in Deep Submicron TechnologyDocument15 pagesDesign of High Performance Dynamic CMOS Circuits in Deep Submicron TechnologyEeshwar Ram JPas encore d'évaluation

- A Low Power Schmitt Trigger Design Using SBT Technique in 180nm CMOS TechnologyDocument4 pagesA Low Power Schmitt Trigger Design Using SBT Technique in 180nm CMOS TechnologySowmya ReddyPas encore d'évaluation

- Design of Schmitt Trigger Circuits Using VTCMOS For Sub-Threshold CircuitsDocument7 pagesDesign of Schmitt Trigger Circuits Using VTCMOS For Sub-Threshold CircuitsBüşra AkyıldızPas encore d'évaluation

- Minimization Leakage Current of Full Adder Using Deep Sub-Micron CMOS TechniqueDocument7 pagesMinimization Leakage Current of Full Adder Using Deep Sub-Micron CMOS TechniqueInternational Journal of Application or Innovation in Engineering & ManagementPas encore d'évaluation

- Layout ExamplesDocument13 pagesLayout Examplesnazibhd786Pas encore d'évaluation

- Massachusetts Institute of Technology Department of Electrical Engineering and Computer ScienceDocument7 pagesMassachusetts Institute of Technology Department of Electrical Engineering and Computer ScienceFernando Sánchez HernándezPas encore d'évaluation

- AnalogDocument8 pagesAnalogAhmed F RahimPas encore d'évaluation

- Geometric Programming Based Power-Delay Optimization Using Transistor-Sizing For Submicron and Deep Submicron CMOS InverterDocument4 pagesGeometric Programming Based Power-Delay Optimization Using Transistor-Sizing For Submicron and Deep Submicron CMOS Invertersuchi87Pas encore d'évaluation

- Low Voltage Smart Temperature Sensor Front End: Abstract-In This Brief, A Low Voltage Low Power CMOSDocument5 pagesLow Voltage Smart Temperature Sensor Front End: Abstract-In This Brief, A Low Voltage Low Power CMOSBruno SilvaPas encore d'évaluation

- Dheeraj ReportDocument15 pagesDheeraj ReportGirdhar Gopal GautamPas encore d'évaluation

- Design and Analysis of Double Tail Comparator Using Adiabatic LogicDocument7 pagesDesign and Analysis of Double Tail Comparator Using Adiabatic LogicIJSTEPas encore d'évaluation

- Subthreshold Source-Coupled Logic Circuits For Ultra-Low-Power ApplicationsDocument12 pagesSubthreshold Source-Coupled Logic Circuits For Ultra-Low-Power ApplicationsSonu SangwanPas encore d'évaluation

- NTNU Project Report Designs Integrated Circuits CameraDocument41 pagesNTNU Project Report Designs Integrated Circuits CameraFilip SavicPas encore d'évaluation

- Low Swing Signaling Using A Dynamic Diode-Connected DriverDocument4 pagesLow Swing Signaling Using A Dynamic Diode-Connected DriverAkash RaykarPas encore d'évaluation

- Vlsi DesignDocument31 pagesVlsi Designajas777BPas encore d'évaluation

- Advanced low-power full-adder cell for low voltageDocument6 pagesAdvanced low-power full-adder cell for low voltagedurairajmary100% (1)

- CMOS Low-Power Analog Circuit DesignDocument55 pagesCMOS Low-Power Analog Circuit DesignRajesh_Nagaraj_9325Pas encore d'évaluation

- Double Tail Dynamic CompDocument10 pagesDouble Tail Dynamic CompBhura AnushaPas encore d'évaluation

- Analysis and Design of High Speed Low Power Comparator in ADCDocument6 pagesAnalysis and Design of High Speed Low Power Comparator in ADCNoReply ProgramPas encore d'évaluation

- Tri State InverterDocument18 pagesTri State InverterManasa Upadhyaya100% (1)

- Design of Low Power Efficient CMOS Dynamic Latch Comparator: A.Pravin, Dr.N.S.Murti Sarma, DR - Fazal Noor BashaDocument6 pagesDesign of Low Power Efficient CMOS Dynamic Latch Comparator: A.Pravin, Dr.N.S.Murti Sarma, DR - Fazal Noor BashaNoReply ProgramPas encore d'évaluation

- Design of An ADC Using High Precision Comparator With Time Domain Offset CancellationDocument4 pagesDesign of An ADC Using High Precision Comparator With Time Domain Offset CancellationijtetjournalPas encore d'évaluation

- Analysis of Cmos and Mtcmos Circuits Using 250 Nano Meter TechnologyDocument11 pagesAnalysis of Cmos and Mtcmos Circuits Using 250 Nano Meter TechnologyCS & ITPas encore d'évaluation

- DC-DC Buck Converter With Reduced Impact: SciencedirectDocument8 pagesDC-DC Buck Converter With Reduced Impact: SciencedirectClaudiu UdrescuPas encore d'évaluation

- Sensors 12 03587 PDFDocument18 pagesSensors 12 03587 PDFMuhammet AteşPas encore d'évaluation

- Implementation of High Speed 0.13 M CMOS Dynamic Latch ComparatorDocument3 pagesImplementation of High Speed 0.13 M CMOS Dynamic Latch ComparatorijsretPas encore d'évaluation

- Don Bosco Institute of Technology: Department of Electronics and Communication EngineeringDocument23 pagesDon Bosco Institute of Technology: Department of Electronics and Communication EngineeringSeema Shekarappa ChittakkiPas encore d'évaluation

- FISAC2 200907012 - PrajwalprabhuDocument22 pagesFISAC2 200907012 - PrajwalprabhuPrajwal PrabhuPas encore d'évaluation

- Linearity Enhancement of Operational Transconductance Amplifier Using SourceDocument7 pagesLinearity Enhancement of Operational Transconductance Amplifier Using SourceIAEME PublicationPas encore d'évaluation

- A Novel Method For Analysis of Power Consumption in VLSI Global InterconnectsDocument12 pagesA Novel Method For Analysis of Power Consumption in VLSI Global InterconnectsPranay KumarPas encore d'évaluation

- Dual Supply SchmittDocument5 pagesDual Supply SchmittReza RezaPas encore d'évaluation

- Ab 02601460148Document3 pagesAb 02601460148International Journal of computational Engineering research (IJCER)Pas encore d'évaluation

- Study of Differential Amplifier Using CMOS: AbstractDocument5 pagesStudy of Differential Amplifier Using CMOS: AbstractNiranjan DaradePas encore d'évaluation

- A 1.8Ghz Cmos: Low-Power Truly-Modular Programmable Divider in Standard TechnologyDocument4 pagesA 1.8Ghz Cmos: Low-Power Truly-Modular Programmable Divider in Standard TechnologyMuhammad_Swilam_2010Pas encore d'évaluation

- Speed-Power-Accuracy TradeoffDocument8 pagesSpeed-Power-Accuracy TradeoffbackspaceTABPas encore d'évaluation

- DTMOS-Based Low-Voltage and Low-Power Two-Stage OTA: March 2022Document6 pagesDTMOS-Based Low-Voltage and Low-Power Two-Stage OTA: March 2022Büşra AkyıldızPas encore d'évaluation

- Analysis and Mitigation of NBTI-Induced Performance Degradation For Power-Gated CircuitsDocument6 pagesAnalysis and Mitigation of NBTI-Induced Performance Degradation For Power-Gated Circuitsvedantgarg_28Pas encore d'évaluation

- Next Gen VLSI Circuits Delay ReductionDocument5 pagesNext Gen VLSI Circuits Delay ReductionsudhaaishPas encore d'évaluation

- Design and Analysis of Low Power Johnson Counter With Improved Performance Using MT-CMOS and Clock GatingDocument4 pagesDesign and Analysis of Low Power Johnson Counter With Improved Performance Using MT-CMOS and Clock GatingIJSTEPas encore d'évaluation

- Op Amp PaperDocument6 pagesOp Amp PaperSrinivasu IrlapatiPas encore d'évaluation

- Design and Optimization of ÷8/9 Divider in PLL Frequency Synthesizer With Dynamic Logic (E - TSPC)Document5 pagesDesign and Optimization of ÷8/9 Divider in PLL Frequency Synthesizer With Dynamic Logic (E - TSPC)himaja1Pas encore d'évaluation

- Analysis and Optimization of Active Power and Delay of 10T Full Adder Using Power Gating Technique at 45 NM TechnologyDocument7 pagesAnalysis and Optimization of Active Power and Delay of 10T Full Adder Using Power Gating Technique at 45 NM TechnologyInternational Organization of Scientific Research (IOSR)Pas encore d'évaluation

- DSP-Based Real-Time Implementation of AC-DC-AC Converter Using SPWM TechniqueDocument18 pagesDSP-Based Real-Time Implementation of AC-DC-AC Converter Using SPWM Techniquebalamurugan041992Pas encore d'évaluation

- Design and Implementation of Dynamic Track and Latch Comparator Using CMOS in 0.18um TechnologyDocument3 pagesDesign and Implementation of Dynamic Track and Latch Comparator Using CMOS in 0.18um TechnologyWARSE JournalsPas encore d'évaluation

- Design of Low Power 12-Bit Magnitude ComparatorDocument6 pagesDesign of Low Power 12-Bit Magnitude Comparatoreditor_ijtelPas encore d'évaluation

- Analysis of Energy Efficient PTL Based Full Adders Using Different Nanometer TechnologiesDocument6 pagesAnalysis of Energy Efficient PTL Based Full Adders Using Different Nanometer TechnologiesDwarakaManeekantaAddagiriPas encore d'évaluation

- CMOS ICDocument12 pagesCMOS ICsalikrishna405Pas encore d'évaluation

- Integrated Circuit Layout and Simulation: Prepared by Charles Sumion JKE Politeknik Kota KinabaluDocument16 pagesIntegrated Circuit Layout and Simulation: Prepared by Charles Sumion JKE Politeknik Kota KinabaluYazid Abdul HamidPas encore d'évaluation

- Low-Voltage Low-Power CMOS Voltage Reference Design MethodologyDocument11 pagesLow-Voltage Low-Power CMOS Voltage Reference Design MethodologyVenkatesh DonepudiPas encore d'évaluation

- A 1.8V 12-Bit 230-MS/s Pipeline ADC in 0.18 M CMOS TechnologyDocument4 pagesA 1.8V 12-Bit 230-MS/s Pipeline ADC in 0.18 M CMOS Technologyfaithfully_fatihPas encore d'évaluation

- Analog Circuit Sizing Using Adaptive Worst-Case Parameters SetsDocument5 pagesAnalog Circuit Sizing Using Adaptive Worst-Case Parameters SetswoshisimoxPas encore d'évaluation

- Low Power ThesisDocument6 pagesLow Power Thesistiffanybarbermobile100% (2)

- CMOS Inverter propagation delayDocument6 pagesCMOS Inverter propagation delayshashwatPas encore d'évaluation

- 05682957Document4 pages05682957Praveenkumar ViswanathanPas encore d'évaluation

- Analysis, Design, and Implementation of A High-Efficiency Full-Wave Rectifier in Standard CMOS TechnologyDocument11 pagesAnalysis, Design, and Implementation of A High-Efficiency Full-Wave Rectifier in Standard CMOS TechnologymohsinmanzoorPas encore d'évaluation

- High-Performance D/A-Converters: Application to Digital TransceiversD'EverandHigh-Performance D/A-Converters: Application to Digital TransceiversPas encore d'évaluation

- Solution Manual for 100 Genesys Design Examples: Second EditionD'EverandSolution Manual for 100 Genesys Design Examples: Second EditionPas encore d'évaluation

- MOS Integrated Circuit DesignD'EverandMOS Integrated Circuit DesignE. WolfendalePas encore d'évaluation

- MMSE Adaptive Receiver vs. Rake Receiver Performance Evaluation For UWB Signals Over Multipath Fading ChannelDocument13 pagesMMSE Adaptive Receiver vs. Rake Receiver Performance Evaluation For UWB Signals Over Multipath Fading ChannelIOSRJEN : hard copy, certificates, Call for Papers 2013, publishing of journalPas encore d'évaluation

- I 05815457Document4 pagesI 05815457IOSRJEN : hard copy, certificates, Call for Papers 2013, publishing of journalPas encore d'évaluation

- Random Fixed Point Theoremsin Metric Space: Balaji R Wadkar, Ramakant Bhardwaj, Basantkumar SinghDocument9 pagesRandom Fixed Point Theoremsin Metric Space: Balaji R Wadkar, Ramakant Bhardwaj, Basantkumar SinghIOSRJEN : hard copy, certificates, Call for Papers 2013, publishing of journalPas encore d'évaluation

- Application of The Multi-Curve Reconstruction Technology in Seismic InversionDocument4 pagesApplication of The Multi-Curve Reconstruction Technology in Seismic InversionIOSRJEN : hard copy, certificates, Call for Papers 2013, publishing of journalPas encore d'évaluation

- H 05814953Document5 pagesH 05814953IOSRJEN : hard copy, certificates, Call for Papers 2013, publishing of journalPas encore d'évaluation

- The Experimental Study On The Compatibility Relationship of Polymer and Oil LayerDocument5 pagesThe Experimental Study On The Compatibility Relationship of Polymer and Oil LayerIOSRJEN : hard copy, certificates, Call for Papers 2013, publishing of journalPas encore d'évaluation

- Study On Logging Interpretation Model and Its Application For Gaotaizi Reservoir of L OilfieldDocument6 pagesStudy On Logging Interpretation Model and Its Application For Gaotaizi Reservoir of L OilfieldIOSRJEN : hard copy, certificates, Call for Papers 2013, publishing of journalPas encore d'évaluation

- G 05913234Document3 pagesG 05913234IOSRJEN : hard copy, certificates, Call for Papers 2013, publishing of journalPas encore d'évaluation

- A 05910106Document6 pagesA 05910106IOSRJEN : hard copy, certificates, Call for Papers 2013, publishing of journalPas encore d'évaluation

- Effectiveness in Addressing The Sustainability and Environmental Issue Involving Use of Coal Ash As Partial Replacement of Cement in ConcreteDocument6 pagesEffectiveness in Addressing The Sustainability and Environmental Issue Involving Use of Coal Ash As Partial Replacement of Cement in ConcreteIOSRJEN : hard copy, certificates, Call for Papers 2013, publishing of journalPas encore d'évaluation

- G 05813848Document11 pagesG 05813848IOSRJEN : hard copy, certificates, Call for Papers 2013, publishing of journalPas encore d'évaluation

- The Identification of Lithologic Traps in Nanpu Sag D3 Member of Gaonan RegionDocument5 pagesThe Identification of Lithologic Traps in Nanpu Sag D3 Member of Gaonan RegionIOSRJEN : hard copy, certificates, Call for Papers 2013, publishing of journalPas encore d'évaluation

- Introduction To Accounting Professional Judgment ManipulationDocument3 pagesIntroduction To Accounting Professional Judgment ManipulationIOSRJEN : hard copy, certificates, Call for Papers 2013, publishing of journalPas encore d'évaluation

- "Sign Language Translator": Mr. Sangam Mhatre, Mrs. Siuli DasDocument4 pages"Sign Language Translator": Mr. Sangam Mhatre, Mrs. Siuli DasIOSRJEN : hard copy, certificates, Call for Papers 2013, publishing of journalPas encore d'évaluation

- Strength Properties of Commercially Produced Clay Bricks in Six Different Locations/ States in NigeriaDocument10 pagesStrength Properties of Commercially Produced Clay Bricks in Six Different Locations/ States in NigeriaIOSRJEN : hard copy, certificates, Call for Papers 2013, publishing of journalPas encore d'évaluation

- Validating The Theories of Urban Crime in The City of RaipurDocument10 pagesValidating The Theories of Urban Crime in The City of RaipurIOSRJEN : hard copy, certificates, Call for Papers 2013, publishing of journalPas encore d'évaluation

- Construction of Self-Regulated EFL Micro-Course Learning: Zhongwen LiuDocument4 pagesConstruction of Self-Regulated EFL Micro-Course Learning: Zhongwen LiuIOSRJEN : hard copy, certificates, Call for Papers 2013, publishing of journalPas encore d'évaluation

- A 05810107Document7 pagesA 05810107IOSRJEN : hard copy, certificates, Call for Papers 2013, publishing of journalPas encore d'évaluation

- B 05810814Document7 pagesB 05810814IOSRJEN : hard copy, certificates, Call for Papers 2013, publishing of journalPas encore d'évaluation

- Modeling and Design of Hybrid Power Plants: Ahmed KH A. E. AlkhezimDocument5 pagesModeling and Design of Hybrid Power Plants: Ahmed KH A. E. AlkhezimIOSRJEN : hard copy, certificates, Call for Papers 2013, publishing of journalPas encore d'évaluation

- Constructions Quality Versus Bad Components in Jordanian CementDocument3 pagesConstructions Quality Versus Bad Components in Jordanian CementIOSRJEN : hard copy, certificates, Call for Papers 2013, publishing of journalPas encore d'évaluation

- The Research of Source System On Chang 6 Sand Formation in Ansai OilfieldDocument5 pagesThe Research of Source System On Chang 6 Sand Formation in Ansai OilfieldIOSRJEN : hard copy, certificates, Call for Papers 2013, publishing of journalPas encore d'évaluation

- I 05745368Document16 pagesI 05745368IOSRJEN : hard copy, certificates, Call for Papers 2013, publishing of journalPas encore d'évaluation

- G 05743742Document6 pagesG 05743742IOSRJEN : hard copy, certificates, Call for Papers 2013, publishing of journalPas encore d'évaluation

- Assessment of The Life Quality of Urban Areas Residents (The Case Study of The City of Fahraj)Document6 pagesAssessment of The Life Quality of Urban Areas Residents (The Case Study of The City of Fahraj)IOSRJEN : hard copy, certificates, Call for Papers 2013, publishing of journalPas encore d'évaluation

- D 05741325Document13 pagesD 05741325IOSRJEN : hard copy, certificates, Call for Papers 2013, publishing of journalPas encore d'évaluation

- Detecting Spammers in Youtube: A Study To Find Spam Content in A Video PlatformDocument5 pagesDetecting Spammers in Youtube: A Study To Find Spam Content in A Video PlatformIOSRJEN : hard copy, certificates, Call for Papers 2013, publishing of journalPas encore d'évaluation

- C 05740912Document4 pagesC 05740912IOSRJEN : hard copy, certificates, Call for Papers 2013, publishing of journalPas encore d'évaluation

- DatasheetDocument6 pagesDatasheetSunil SuwarnkarPas encore d'évaluation

- Lab 2 PDFDocument3 pagesLab 2 PDFTawsif ahmedPas encore d'évaluation

- Kenwood Kvt-819 - 829 - 839 Monitor With DVD ReceiverDocument80 pagesKenwood Kvt-819 - 829 - 839 Monitor With DVD ReceiverpromexbrailaPas encore d'évaluation

- A Single-Channel 10-Bit 160 MSs SAR ADC in 65Document9 pagesA Single-Channel 10-Bit 160 MSs SAR ADC in 65Y chenPas encore d'évaluation

- Design of High Speed Pipeline ADC: Estec February 4-5, 2004Document29 pagesDesign of High Speed Pipeline ADC: Estec February 4-5, 2004Niamat KhanPas encore d'évaluation

- ADEDocument10 pagesADEashwinishettytpPas encore d'évaluation

- SchematicDocument1 pageSchematicDavid TorresPas encore d'évaluation

- MOSFET Grounded and Floating Resistor ExperimentDocument5 pagesMOSFET Grounded and Floating Resistor ExperimentKetan SharmaPas encore d'évaluation

- DACDocument33 pagesDACSamsuzzaman TutulPas encore d'évaluation

- ModifiedDocument15 pagesModifiedAkashdeep BhattacharjeePas encore d'évaluation

- Match Transistors for Circuits with <40mΩ MismatchDocument5 pagesMatch Transistors for Circuits with <40mΩ MismatchcrackintheshatPas encore d'évaluation

- CPLD and FpgaDocument28 pagesCPLD and FpgaUday KumarPas encore d'évaluation

- ICL7106, ICL7107: Features DescriptionDocument13 pagesICL7106, ICL7107: Features DescriptionAbdalhakeem AlturkyPas encore d'évaluation

- Put Question Paper (Ec-302)Document3 pagesPut Question Paper (Ec-302)Anonymous eWMnRr70qPas encore d'évaluation

- Unit 1 - DSDDocument95 pagesUnit 1 - DSDSaravanan MurugaiyanPas encore d'évaluation

- MCQ in Computer Fundamentals Part 2 ECE Board ExamDocument18 pagesMCQ in Computer Fundamentals Part 2 ECE Board ExamLuelson CordovaPas encore d'évaluation

- Example: Determine The Power Supplied by Each of The Sources, Independent and Dependent, inDocument6 pagesExample: Determine The Power Supplied by Each of The Sources, Independent and Dependent, inSakthivelraj SPas encore d'évaluation

- AC triggering of an SCR experimentDocument5 pagesAC triggering of an SCR experimentTrishia Marie TabagPas encore d'évaluation

- 74HC139Document9 pages74HC139jnax101Pas encore d'évaluation

- Question Papers: Examcode: Ece1 - 15 - B1 Version No: 1Document22 pagesQuestion Papers: Examcode: Ece1 - 15 - B1 Version No: 1sonuPas encore d'évaluation

- 555 Timer Monostable OperationDocument13 pages555 Timer Monostable OperationGrigore ManPas encore d'évaluation

- Op Amp ExpDocument23 pagesOp Amp Expram12_leoPas encore d'évaluation

- CND101 Lab 7Document24 pagesCND101 Lab 7Mostafa KhaledPas encore d'évaluation

- OTA Structures2Document13 pagesOTA Structures2Debopam DattaPas encore d'évaluation

- Circuit Analysis 2 - PS2Document5 pagesCircuit Analysis 2 - PS2BlueNova VortexPas encore d'évaluation

- Chapter Four Combinational Logic Circuits OutlinesDocument22 pagesChapter Four Combinational Logic Circuits Outlinesmift ademPas encore d'évaluation

- Sistem Kendali Digital - Week 2-1-1Document35 pagesSistem Kendali Digital - Week 2-1-1Dedi BobPas encore d'évaluation

- Ec503 PDFDocument2 pagesEc503 PDFSridhar Koneru VenkkatPas encore d'évaluation

- BFW10Document1 pageBFW10SarinPas encore d'évaluation

- LED Series Parallel Array Wizardled 3mmDocument4 pagesLED Series Parallel Array Wizardled 3mmalbertanton99Pas encore d'évaluation