Académique Documents

Professionnel Documents

Culture Documents

6116ASP20

Transféré par

BeNz BarrigaDescription originale:

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

6116ASP20

Transféré par

BeNz BarrigaDroits d'auteur :

Formats disponibles

6116A: 11/8/89 Revision: Monday, November 8, 1993

Features

D D D D D D D

Automatic powerdown when deselected CMOS for optimum speed/power High speed 20 ns Low active power 550 mW Low standby power 110 mW TTLcompatible inputs and outputs Capable of withstanding greater than 2001V electrostatic discharge

The CY6116A and CY6117A are high performance CMOS static RAMs orga nized as 2048 words by 8 bits. Easy memoryexpansionisprovidedbyanactive LOW chip enable (CE) and active LOW output enable (OE), and threestate driv ers. The CY6116A and CY6117A have an automatic powerdown feature, reducing the power consumption by 83% when de selected. Writingtothedeviceisaccomplishedwhen the chip enable (CE) and write enable (WE) inputs are both LOW. Data on the I/Opins(I/O0 throughI/O7)iswritteninto

Functional Description

the memory location specified on the ad dress pins (A0 through A10). Readingthedeviceisaccomplishedbytak ing chip enable (CE) and output enable (OE) LOW while write enable (WE) re mainsHIGH.Undertheseconditions,the contents of the memory location specified on the address pins will appear on the I/O pins. The I/O pins remain in highimpedance state when chip enable (CE) is HIGH or write enable (WE) is LOW. The CY6116A and CY6117A utilize a die coat to insure alpha immunity.

2K x 8 Static RAM

CY6116A CY6117A

Logic Block Diagram

A7 A6 A5 A4 A3 A2 A1 1 2 3 4 5 6 7 8 9 10 11 12 6116A

Pin Configurations

DIP/SOJ Top View

24 23 22 21 20 19 18 17 16 15 14 13 VCC A8 A9 WE OE A10 CE I/O7 I/O6 I/O5 I/O4 I/O3 A3 A2 NC NC A1 A0 I/O0 5 6 7 8 9 10 11 6116A 4 A4 A7 V CC

LCC Top View

A8 3 2 1 28 27 26 25 24 23 22 21 20 19 1213 14 151617 18 1 I/O 2 GND I/O 3 I/O 4 I/O 5 I/O 6 WE OE A10 NC NC CE I/O7 A9 6116A-3 A5 A6

I/O0

INPUT BUFFER

A0 I/O0 I/O1

GND ROW DECODER

A9 A8 A7 A6 A5 A4

I/O2

SENSE AMPS

6116A-2

128 x 16 x 8 ARRAY

I/O3

NC

NC

NC

NC

I/O5

4 A6 A5 A4 A3 A2 5 6 7 8 9 10 11 12 13

1 32 31 30 29 28 27 26 A8 A9 NC WE OE A10 CE I/O7 I/O6

CE WE COLUMN DECODER OE POWER DOWN

I/O6

6117A

I/O7

A1 A0 NC

A3

A2

A1

A0

6116A-1

I/O0

14 15 16 17 1819 20 GND NC I/O 4 I/O 5 I/O 1 I/O 2 I/O 3

NC

A7

I/O4

V CC

LCC Top View

25 24 23 22 21

I/O

A10

I/O1

I/O2

6116A-4

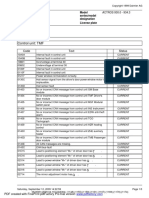

Selection Guide

Maximum Access Time (ns) Maximum Operating Current (mA) Maximum Standby Current (mA) Commercial Military Commercial Military

D

6116A-20 6117A-20

20 100

6116A-25 6117A-25

40/20

25 100 125 20 40

D

6116A-35 6117A-35

35 100 100 20 20

6116A-45 6117A-45

45 100 100 20 20

6116A-55 6117A-55

55 80 100 20 20

Cypress Semiconductor Corporation

3901 North First Street 1

San Jose

D CA 95134 D 408-943-2600 February 1988 - Revised December 1992

6116A: 11/8/89 Revision: Monday, November 8, 1993

CY6116A CY6117A

Maximum Ratings

(Above which the useful life may be impaired. For user guidelines, not tested.) Storage Temperature . . . . . . . . . . . . . . . . . . -65_C to +150_C Ambient Temperature with Power Applied . . . . . . . . . . . . . . . . . . . . . . . -55_C to +125_C Supply Voltage to Ground Potential (Pin 24 to Pin 12) . . . . . . . . . . . . . . . . . . . . . . . -0.5V to +7.0V DC Voltage Applied to Outputs in High Z State . . . . . . . . . . . . . . . . . . . . . . . . . -0.5V to +7.0V DC Input Voltage . . . . . . . . . . . . . . . . . . . . . . . -3.0V to +7.0V Output Current into Outputs (LOW) . . . . . . . . . . . . . . 20 mA

Electrical Characteristics

Static Discharge Voltage . . . . . . . . . . . . . . . . . . . . . . . >2001V (per MILSTD883, Method 3015) LatchUp Current . . . . . . . . . . . . . . . . . . . . . . . . . . . >200 mA

Operating Range

Ambient Range Temperature VCC

Commercial Military[1]

0_C to +70_C -55_C to +125_C

5V 10% 5V 10%

Over the Operating Range[2]

6116A-20 6117A-20 6116A-25, 35, 45 6117A-25, 35, 45 Min. Max. 6116A-55 6117A-55 Min. Max. Unit

Parameter

Description

Test Conditions

Min.

Max.

VOH VOL VIH VIL IIX IOZ IOS ICC

OutputHIGHVoltage VCC = Min., IOH = -4.0 mA Output LOW Voltage VCC = Min., IOL = 8.0 mA Input HIGH Voltage Input LOW Voltage[3] Input Load Current Output Leakage Current Output Short Circuit Current[4] VCC Operating p g S l Current C Supply Automatic CE P PowerDown D Current C - TTL Inputs Automatic CE PowerDown Current - CMOS Inputs GND < VI < VCC GND < VI < VCC, Output Disabled VCC = Max., VOUT = GND VCC = Max. A IOUT = 0 mA f = fMAX = 1/tRC Max. VCC, CE > VIH f = fMAX Com'l Mil 25 35, 45 Com'l Mil 25 35, 45, 55

2.4 0.4 2.2 -0.5 -10 -10 VCC 0.8 +10 +10 -300 100

2.4 0.4 2.2 -0.5 -10 -10 VCC 0.8 +10 +10 -300 100 125 100 40 20 40 20 20 20 20

2.4 0.4 2.2 -0.5 -10 -10 VCC 0.8 +10 +10 -300 80 100 20 20 20 20

V V V V

mA mA

mA mA

ISB1

mA

ISB2

Max. VCC, Com'l CE > VIH - 0.3V, VIN > VCC - 0.3V or VIN < 0.3V, Mil f=0

mA

Capacitance

[5]

Description Test Conditions Max. Unit

Parameter

CIN COUT

Notes:

Input Capacitance Output Capacitance

TA = 25_C, f = 1 MHz, VCC = 5.0V 5 0V

10 10

pF pF

1. 2. 3.

TA is the instant on" case temperature. See the last page of this specification for Group A subgroup testing in formation. VIL (min.) = -3.0V for pulse durations less than 30 ns.

4. 5.

Not more than 1 output should be shorted at one time. Duration of the short circuit should not exceed 30 seconds. Tested initially and after any design or process changes that may affect these parameters.

6116A: 11/8/89 Revision: Monday, November 8, 1993

CY6116A CY6117A

AC Test Loads and Waveforms

5V OUTPUT 30 pF INCLUDING JIG AND SCOPE Equivalent to:

R1 481W

5V OUTPUT 5 pF INCLUDING JIG AND SCOPE

R1 481W 3.0V R2 255W

(b)

R2 255W

(a)

GND

10% 5 ns

ALL INPUT PULSES 90% 90% 10% 5 ns

6116A-6

6116A-5

THVENIN EQUIVALENT 167W OUTPUT 1.73V

6116A-20 6117A-20 6116A-25 6117A-25 Min. Max. 6116A-35 6117A-35 Min. Max. 6116A-45 6117A-45 Min. Max. 6116A-55 6117A-55 Min. Max.

Switching Characteristics Over the Operating Range[2, 6]

Parameter READ CYCLE

tRC tAA tOHA tACE tDOE tLZOE tHZOE tLZCE tHZCE tPU tPD

Description

Min.

Max.

Unit

Read Cycle Time Address to Data Valid Data Hold from Address Change CE LOW to Data Valid OE LOW to Data Valid OE LOW to Low Z OE HIGH to High Z CE LOW to Low Z

[7]

20 20 5 20 10 3 8 5 8 0 20

25 25 5 25 12 3 10 5 10 0 20

35 35 5 35 15 3 12 5 15 0 20

45 45 5 45 20 3 15 5 15 0 25

55 55 5 55 25 3 20 5 20 0 25

ns ns ns ns ns ns ns ns ns ns ns

[8]

CE HIGH to High Z[7, 8 ] CE LOW to PowerUp CE HIGH to PowerDown

[9]

WRITE CYCLE

tWC tSCE tAW tHA tSA tPWE tSD tHD tHZWE tLZWE

Write Cycle Time CE LOW to Write End Address SetUp to Write End Address Hold from Write End Address SetUp to Write Start WE Pulse Width Data SetUp to Write End Data Hold from Write End WE LOW to High Z WE HIGH to Low Z

20 15 15 0 0 15 10 0 7 5

20 20 20 0 0 15 10 0 7 5

9.

25 25 25 0 0 20 15 0 10 5

40 30 30 0 0 20 15 0 15 5

50 40 40 0 0 25 25 0 20 5

ns ns ns ns ns ns ns ns ns ns

Notes: 6. Test conditions assume signal transition time of 5 ns or less, timing ref erence levels of 1.5V , input pulse levels of 0 to 3.0V , and output loading of the specified IOL/IOH and 30pF load capacitance.

7. tHZOE, tHZCE, and tHZWE are specified with CL = 5 pF as in part (b) of AC Test Loads. Transition is measured 500 mV from steady state voltage. At any given temperature and voltage condition, tHZCE is less than tLZCE for any given device.

The internal write time of the memory is defined by the overlap of CE LOW and WE LOW. Both signals must be LOW to initiate a write and either signal can terminate a write by going HIGH. The data input set up and hold timing should be referenced to the rising edge of the signal that terminates the write.

8.

6116A: 11/8/89 Revision: Monday, November 8, 1993

CY6116A CY6117A

Switching Waveforms

Read Cycle No. 1[10, 11]

tRC ADDRESS DATA OUT tOHA PREVIOUS DATA VALID tAA DATA VALID

6116A-7

Read Cycle No. 2[10, 12]

CE OE tACE tLZOE HIGH IMPEDANCE tLZCE tPU 50% tDOE

tRC

tHZOE tHZCE DATA VALID tPD 50%

DATA OUT VCC SUPPLY CURRENT

HIGH IMPEDANCE ICC ISB

6116A-8

Write Cycle No. 1 (WE Controlled)[9, 13]

tWC tSCE

ADDRESS CE tSA WE DATA IN DATA I/O

Notes:

10. 11. 12. WE is HIGH for read cycle. Device is continuously selected. OE, CE = VIL. Address valid prior to or coincident with CE transition LOW . 13. Data I/O pins enter highimpedance state, as shown, when OE is held LOW during write.

tAW

tPWE tSD DATA VALID tHZWE tHD

tHA

DATA UNDEFINED

tLZWE HIGH IMPEDANCE

6116A-9

6116A: 11/8/89 Revision: Monday, November 8, 1993

CY6116A CY6117A

Switching Waveforms (continued)

Write Cycle No. 2 (CE Controlled)[9, 13, 14]

tWC ADDRESS tSA CE tAW tPWE WE tHA tSCE

tSD DATA IN DATAIN VALID tHZWE DATA I/O

tHD

HIGH IMPEDANCE DATA UNDEFINED

6116A-10

Note: 14. If CE goes HIGH simultaneously with WE HIGH, the output remains in a highimpedance state.

Typical DC and AC Characteristics

NORMALIZED SUPPLY CURRENT vs. SUPPLY VOLTAGE

1.4

SB

OUTPUT SOURCE CURRENT (mA)

NORMALIZED SUPPLY CURRENT vs. AMBIENT TEMPERATURE

1.2

SB

OUTPUT SOURCE CURRENT vs. OUTPUT VOLTAGE

120 100 80 60 40 20 0 0.0 1.0 2.0 3.0 4.0 TA = 25_C VCC = 5.0V

NORMALIZED I CC, I

NORMALIZED I CC, I

1.2 1.0 0.8 0.6 0.4 0.2 0.0 4.0 4.5 5.0 5.5 6.0 ISB ICC

1.0 0.8

ICC

0.6 0.4 0.2 0.0 -55

VCC = 5.0V VIN = 5.0V ISB 25 125

SUPPLY VOLTAGE (V)

AMBIENT TEMPERATURE (_C)

OUTPUT VOLTAGE (V)

NORMALIZED ACCESS TIME vs. SUPPLY VOLTAGE

1.4 1.3 1.2 1.1 1.0 1.6

NORMALIZED ACCESS TIME vs. AMBIENT TEMPERATURE

OUTPUT SINK CURRENT (mA) 140 120 100 80 60 40 20 0 25 125

OUTPUT SINK CURRENT vs. OUTPUT VOLTAGE

NORMALIZED tAA

NORMALIZED tAA

1.4

1.2

TA = 25_C

VCC = 5.0V

TA = 25_C

1.0 VCC = 5.0V 0.8

0.9 0.8 4.0

4.5

5.0

5.5

6.0

0.6 -55

0.0

1.0

2.0

3.0

4.0

SUPPLY VOLTAGE (V)

AMBIENT TEMPERATURE (_C)

OUTPUT VOLTAGE (V)

6116A: 11/8/89 Revision: Monday, November 8, 1993

CY6116A CY6117A

Typical DC and AC Characteristics (continued)

TYPICAL POWERON CURRENT vs. SUPPLY VOLTAGE

3.0 2.5 DELTA t AA (ns) 2.0 1.5 1.0 0.5 0.0 0.0 1.0 2.0 3.0 4.0 5.0 30.0 25.0 20.0 15.0 10.0 5.0 0.0

TYPICAL ACCESS TIME CHANGE vs. OUTPUT LOADING

1.4 1.3 1.2 1.1 1.0

NORMALIZED ICC vs. CYCLE TIME

VCC = 5.0V VIN = 0.5V

TA = 25_C

VCC = 4.5V

NORMALIZED I CC

NORMALIZED I PO

TA = 25_C

0.9 0.8

200

400

600

800

1000

10

20

30

40

SUPPLY VOLTAGE (V)

CAPACITANCE (pF)

CYCLE FREQUENCY (MHz)

Ordering Information

Speed (ns)

20 25

Ordering Code

CY6116A-20PC CY6116A-25PC CY6116A-25DMB CY6116A-25LMB

Package Name

P11 P11 D12 L64 P11 D12 L64 P11 D12 L64 P11 D12 L64

Package Type

28Lead (300Mil) Molded DIP 28Lead (300Mil) Molded DIP 24Lead (600Mil) CerDIP 28Square Leadless Chip Carrier 28Lead (300Mil) Molded DIP 24Lead (600Mil) CerDIP 28Square Leadless Chip Carrier 28Lead (300Mil) Molded DIP 24Lead (600Mil) CerDIP 28Square Leadless Chip Carrier 28Lead (300Mil) Molded DIP 24Lead (600Mil) CerDIP 28Square Leadless Chip Carrier

Operating Range

Commercial Commercial Military

35

CY6116A-35PC CY6116A-35DMB CY6116A-35LMB

Commercial Military

45

CY6116A-45PC CY6116A-45DMB CY6116A-45LMB

Commercial Military

55

CY6116A-55PC CY6116A-55DMB CY6116A-55LMB

Commercial Military

Speed (ns)

35 45 55

Ordering Code

CY6117A35LMB CY6117A45LMB CY6117A55LMB

Package Name

L55 L55 L55

Package Type

32Pin Rectangular Leadless Chip Carrier 32Pin Rectangular Leadless Chip Carrier 32Pin Rectangular Leadless Chip Carrier

Operating Range

Military Military Military

6116A: 11/8/89 Revision: Monday, November 8, 1993

CY6116A CY6117A

MILITARY SPECIFICATIONS Group A Subgroup Testing DC Characteristics

Parameter Subgroups

VOH VOL VIH VIL Max. IIX IOZ ICC ISB

1, 2, 3 1, 2, 3 1, 2, 3 1, 2, 3 1, 2, 3 1, 2, 3 1, 2, 3 1, 2, 3

Switching Characteristics

Parameter READ CYCLE Subgroups

tRC tAA tOHA tACE tDOE tWC tSCE tAW tHA tSA tPWE tSD tHD

7, 8, 9, 10, 11 7, 8, 9, 10, 11 7, 8, 9, 10, 11 7, 8, 9, 10, 11 7, 8, 9, 10, 11 7, 8, 9, 10, 11 7, 8, 9, 10, 11 7, 8, 9, 10, 11 7, 8, 9, 10, 11 7, 8, 9, 10, 11 7, 8, 9, 10, 11 7, 8, 9, 10, 11 7, 8, 9, 10, 11

WRITE CYCLE

Document #: 38-00105-B

6116A: 11/8/89 Revision: Monday, November 8, 1993

CY6116A CY6117A

Package Diagrams

24Lead (600Mil) CerDIP D12

MIL-STD-1835 D-3 Config. A

32Pin Rectangular Leadless Chip Carrier L55

MIL-STD-1835 C-12

28Square Leadless Chip Carrier L64

MIL-STD-1835 C-4

6116A: 11/8/89 Revision: Monday, November 8, 1993

CY6116A CY6117A

Package Diagrams (continued)

24Lead (600Mil) Molded DIP P11

Cypress Semiconductor Corporation, 1992. The information contained herein is subject to change without notice.

Cypress Semiconductor Corporatio n assumes no responsibility for

the use of any circuitry other than circuitry embodied in a Cypress Semiconductor Corporation product. Nor does it convey or imply any license under pa tent or other rights. Cypress Semicon ductor does not authorize its products for use as critical components in lifesupport systems where a malfunction or failure of the product may reason ably be expected to result in significant injury to the user. The inclusion of Cypress Semiconductor products in lifesupport systems applications implies that the manufacturer assumes all risk of such use and in so doing indemnifies Cypress Semiconductor against all damages.

Vous aimerez peut-être aussi

- 000 0 Hy628100bllg 70Document9 pages000 0 Hy628100bllg 70Deepa DevarajPas encore d'évaluation

- 4M (512K X 8) Static Ram: Cy62148V MoblDocument9 pages4M (512K X 8) Static Ram: Cy62148V MoblAurelian ZaharescuPas encore d'évaluation

- Datasheet CY62146DV30LDocument11 pagesDatasheet CY62146DV30LedgarlibanioPas encore d'évaluation

- Datasheet Cy7c199Document13 pagesDatasheet Cy7c199m_manu8588Pas encore d'évaluation

- 74HC4852 (Driver Injector)Document16 pages74HC4852 (Driver Injector)el_george0079491Pas encore d'évaluation

- 32kx8bit CMOS SRAM: HY62256B SeriesDocument9 pages32kx8bit CMOS SRAM: HY62256B SeriesShiwam IsriePas encore d'évaluation

- Cy62146dv30 Ram NokiaDocument12 pagesCy62146dv30 Ram NokiaandersonbheringPas encore d'évaluation

- Document Title: GM76C256CDocument11 pagesDocument Title: GM76C256CFrenk EndyPas encore d'évaluation

- DS1270W 3.3V 16Mb Nonvolatile SRAM: Features Pin AssignmentDocument8 pagesDS1270W 3.3V 16Mb Nonvolatile SRAM: Features Pin AssignmentAndré CastroPas encore d'évaluation

- HY6264A - (I) Series: 8kx8bit CMOS SRAMDocument9 pagesHY6264A - (I) Series: 8kx8bit CMOS SRAMLexuanhoa ProPas encore d'évaluation

- SM 1994Document10 pagesSM 1994Jesus J. SalasPas encore d'évaluation

- MC34151 DDocument12 pagesMC34151 DMladen MuskinjaPas encore d'évaluation

- Cmos Sram K6T1008C2E Family: Document TitleDocument11 pagesCmos Sram K6T1008C2E Family: Document TitleOmar LeonPas encore d'évaluation

- HCF4026B: Decade Counter/Divider With Decoded 7-Segment Display Output and Display EnableDocument11 pagesHCF4026B: Decade Counter/Divider With Decoded 7-Segment Display Output and Display EnableBima Richardo SihombingPas encore d'évaluation

- ADC0803, ADC0804: 8-Bit, Microprocessor-Compatible, A/D Converters FeaturesDocument17 pagesADC0803, ADC0804: 8-Bit, Microprocessor-Compatible, A/D Converters FeaturesJorge Luis Castillo GuarachiPas encore d'évaluation

- ADC0803, ADC0804: 8-Bit, Microprocessor-Compatible, A/D Converters FeaturesDocument18 pagesADC0803, ADC0804: 8-Bit, Microprocessor-Compatible, A/D Converters FeaturesMarco MenezesPas encore d'évaluation

- 8K X 8 Bit Fast Static RAM MCM6264C: MotorolaDocument8 pages8K X 8 Bit Fast Static RAM MCM6264C: Motorolajackiie16Pas encore d'évaluation

- Dual D-Type Flip-Flop: Integrated CircuitsDocument8 pagesDual D-Type Flip-Flop: Integrated CircuitsRakesh Kumar DPas encore d'évaluation

- Cypress SRAM CY62256Document11 pagesCypress SRAM CY62256MicroemissionPas encore d'évaluation

- CA3161EDocument4 pagesCA3161EAlejandro Borrego DominguezPas encore d'évaluation

- CA3160Document19 pagesCA3160Brzata PticaPas encore d'évaluation

- IC-ON-LINE - CN In74hc164a 4331941Document6 pagesIC-ON-LINE - CN In74hc164a 4331941enriquevagoPas encore d'évaluation

- CDP 1802 Data Sheet 2Document7 pagesCDP 1802 Data Sheet 2DavePas encore d'évaluation

- Data SheetDocument14 pagesData SheetChathur Sajeewan BasuruPas encore d'évaluation

- 8-Bit Shift Register With Input Storage Registers (3-State) : Integrated CircuitsDocument14 pages8-Bit Shift Register With Input Storage Registers (3-State) : Integrated CircuitsskiziltoprakPas encore d'évaluation

- 4Mb-SRAM 512Kx1BDocument18 pages4Mb-SRAM 512Kx1BserjaniPas encore d'évaluation

- SN54HC573A, SN74HC573A Octal Transparent D-Type Latches With 3-State OutputsDocument7 pagesSN54HC573A, SN74HC573A Octal Transparent D-Type Latches With 3-State OutputsMadhukar PuliPas encore d'évaluation

- A5800 and A5801: Discontinued ProductDocument13 pagesA5800 and A5801: Discontinued Productitamar_123Pas encore d'évaluation

- Imprimir Datasheet 1Document14 pagesImprimir Datasheet 1Randy Siancas VelezPas encore d'évaluation

- Memoria Ram 6264Document14 pagesMemoria Ram 6264DOMINGOS ALADIRPas encore d'évaluation

- CD74HC238Document7 pagesCD74HC238roozbehxoxPas encore d'évaluation

- Ca3306 (A, C)Document17 pagesCa3306 (A, C)notaden1849Pas encore d'évaluation

- Ucn 5821 ADocument7 pagesUcn 5821 ACelso Conceição100% (1)

- 128K X 8 Static RAM: PreliminaryDocument8 pages128K X 8 Static RAM: PreliminaryRoozbeh BahmanyarPas encore d'évaluation

- CA3140Document20 pagesCA3140Brzata PticaPas encore d'évaluation

- HCF4094B: 8 Stage Shift and Store Bus Register With 3-State OutputsDocument13 pagesHCF4094B: 8 Stage Shift and Store Bus Register With 3-State Outputsjamesearl_cubillasPas encore d'évaluation

- A 6275 EatDocument12 pagesA 6275 Eatn_t_162Pas encore d'évaluation

- 93C66 Microwire EepromDocument13 pages93C66 Microwire EepromadrianramonPas encore d'évaluation

- Dap006 Dap6a DataDocument15 pagesDap006 Dap6a DataluisfeipezzPas encore d'évaluation

- 1.25, Dual SPST, CMOS Analog Switches: General Description FeaturesDocument12 pages1.25, Dual SPST, CMOS Analog Switches: General Description FeaturesStefan GlaserPas encore d'évaluation

- Synchronous Buck Multiphase Optimized LGA Power Block: Integrated Power Semiconductors, Drivers & PassivesDocument10 pagesSynchronous Buck Multiphase Optimized LGA Power Block: Integrated Power Semiconductors, Drivers & PassivesCengiz KayaPas encore d'évaluation

- Adc 0804 PDFDocument18 pagesAdc 0804 PDFCinthya VillenaPas encore d'évaluation

- ADC0802, ADC0803 ADC0804: Features DescriptionDocument17 pagesADC0802, ADC0803 ADC0804: Features DescriptionSuryananda PadmadinataPas encore d'évaluation

- IS61LV25616AL: 256K X 16 High Speed Asynchronous Cmos Static Ram With 3.3V SupplyDocument17 pagesIS61LV25616AL: 256K X 16 High Speed Asynchronous Cmos Static Ram With 3.3V SupplywarekinPas encore d'évaluation

- D D D D D D D D D D D: Description/ordering InformationDocument15 pagesD D D D D D D D D D D: Description/ordering InformationDomsPas encore d'évaluation

- TL 497 ADocument20 pagesTL 497 AJoaoPas encore d'évaluation

- EEPROMDocument16 pagesEEPROMTutankhalmoxePas encore d'évaluation

- HCF4094B: 8 Stage Shift and Store Bus Register With 3-State OutputsDocument13 pagesHCF4094B: 8 Stage Shift and Store Bus Register With 3-State OutputsakbarparlindunganPas encore d'évaluation

- 4-Mbit (256 K × 16) Static RAM: Features Functional DescriptionDocument18 pages4-Mbit (256 K × 16) Static RAM: Features Functional Descriptionprasanna_npPas encore d'évaluation

- Synchronous Presettable 4-Bit Counter: M B Order CodesDocument12 pagesSynchronous Presettable 4-Bit Counter: M B Order CodesMarimuthu RajPas encore d'évaluation

- Distributed byDocument42 pagesDistributed bydennyjoelPas encore d'évaluation

- DS1307 Real Time ClockDocument14 pagesDS1307 Real Time Clockpraveen_kodgirwarPas encore d'évaluation

- Datasheet SN74HC04 - Hex InversorDocument16 pagesDatasheet SN74HC04 - Hex InversorPablo CarvalhoPas encore d'évaluation

- Ca3140, Ca3140A: 4.5Mhz, Bimos Operational Amplifier With Mosfet Input/Bipolar Output FeaturesDocument19 pagesCa3140, Ca3140A: 4.5Mhz, Bimos Operational Amplifier With Mosfet Input/Bipolar Output FeaturesRicardo Teixeira de AbreuPas encore d'évaluation

- Chip Ca3098eDocument12 pagesChip Ca3098etopogigio240Pas encore d'évaluation

- ICL7106, ICL7107, ICL7106S, ICL7107S: 3 / Digit, LCD/LED Display, A/D ConvertersDocument17 pagesICL7106, ICL7107, ICL7106S, ICL7107S: 3 / Digit, LCD/LED Display, A/D ConvertersDave MartzPas encore d'évaluation

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2D'EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2Pas encore d'évaluation

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1D'EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Évaluation : 2.5 sur 5 étoiles2.5/5 (3)

- VSTPP Transformer Failures at VindhyachalDocument96 pagesVSTPP Transformer Failures at VindhyachalSam100% (1)

- Product Manual 26200 (Revision A) : Gas Turbine/Compressor ControlDocument48 pagesProduct Manual 26200 (Revision A) : Gas Turbine/Compressor ControlTaniadi SuriaPas encore d'évaluation

- SC440-P Four Inch Hydrocyclone 2016Document2 pagesSC440-P Four Inch Hydrocyclone 2016Tobias De SomerPas encore d'évaluation

- BOBCAT E26 7348752 SM PreviewDocument41 pagesBOBCAT E26 7348752 SM Previewmonica SoluguelPas encore d'évaluation

- Manson SDCDocument1 pageManson SDCrujanacPas encore d'évaluation

- CH 30Document41 pagesCH 30Antonio CortePas encore d'évaluation

- Abb CL-LMRDocument296 pagesAbb CL-LMRInajá FerreiraPas encore d'évaluation

- Current Fault Codes: Code Text StatusDocument3 pagesCurrent Fault Codes: Code Text StatusnaftaliPas encore d'évaluation

- MkIV Failure CodesDocument12 pagesMkIV Failure Codesjaypc1050% (2)

- Sample Maintenance Sheet: TrailerDocument2 pagesSample Maintenance Sheet: TrailerTrisPas encore d'évaluation

- DC MachinesDocument54 pagesDC MachinesPrashant ChinamalliPas encore d'évaluation

- Stryker FL28EX Hospital Bed - Service ManualDocument60 pagesStryker FL28EX Hospital Bed - Service ManualCristian Andres Araya CisternasPas encore d'évaluation

- X320 Select Series Tractor IntroductionDocument7 pagesX320 Select Series Tractor IntroductionYeison NavasPas encore d'évaluation

- BMW 3 G20 PHEV - en-GBDocument6 pagesBMW 3 G20 PHEV - en-GBDaniel MariPas encore d'évaluation

- BA SI 078 07 18 EN Motorpumpe Sigma X S1Cb EN PDFDocument120 pagesBA SI 078 07 18 EN Motorpumpe Sigma X S1Cb EN PDFmanoj_sitecPas encore d'évaluation

- GW56Document10 pagesGW56dave chaudhuryPas encore d'évaluation

- Catalogo Productos Merten Schneider KNX ISC02052EN - 2010Document95 pagesCatalogo Productos Merten Schneider KNX ISC02052EN - 2010jjjjPas encore d'évaluation

- Construction of An Automatic Change Over Switch (3.7kva)Document10 pagesConstruction of An Automatic Change Over Switch (3.7kva)AlexOdarteyBannermanPas encore d'évaluation

- Mercedes-Benz M254 Engine - Press ReleaseDocument4 pagesMercedes-Benz M254 Engine - Press Releasefransiscus_282501842Pas encore d'évaluation

- Set Rec Pic 827Document2 pagesSet Rec Pic 827Peter SalimPas encore d'évaluation

- MR ToolsDocument1 pageMR ToolsSainiRahulPas encore d'évaluation

- Smart Home 9504 PDFDocument28 pagesSmart Home 9504 PDFJefferson ClaytonPas encore d'évaluation

- Dell Thunderbolt Dock wd19tbs Data Sheet - Pdf.externalDocument5 pagesDell Thunderbolt Dock wd19tbs Data Sheet - Pdf.externalAndre Ant WilliamsPas encore d'évaluation

- Alto Mistral 2500, 4000Document46 pagesAlto Mistral 2500, 4000wacawaca100% (1)

- PDF Operator39s Manual Moba Matic 1 Can and Moba Mini Matic DLDocument73 pagesPDF Operator39s Manual Moba Matic 1 Can and Moba Mini Matic DLVitalii KrasnokutskiyPas encore d'évaluation

- 6042 Parts 8990467 02-22-12 ANSI EnglishDocument462 pages6042 Parts 8990467 02-22-12 ANSI EnglishwalmadasanPas encore d'évaluation

- Hino 700 Exhaust Brake-Engine Retarder WireingDocument2 pagesHino 700 Exhaust Brake-Engine Retarder Wireingg.shien5150100% (1)

- Dwelling Units - NEC Optional Method CalculationDocument40 pagesDwelling Units - NEC Optional Method CalculationignaciodominguezPas encore d'évaluation

- Despiece Hidrojet K310 1.994-680.0 PDFDocument12 pagesDespiece Hidrojet K310 1.994-680.0 PDFjose velascoPas encore d'évaluation

- Certificates FormatDocument10 pagesCertificates FormatJohn Christopher JusayanPas encore d'évaluation