Académique Documents

Professionnel Documents

Culture Documents

PLD Teoria Basica

Transféré par

Gabriela ArgumeTitre original

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

PLD Teoria Basica

Transféré par

Gabriela ArgumeDroits d'auteur :

Formats disponibles

Dispositivos Lgicos Programables

Introduccin

ATE-Universidad de Oviedo

Dispositivos Lgicos Programables

Posibilidades en Diseo Digital

1.- C.I. normalizados o estndar de funcin fija

De funcin fija y en diferentes escalas de integracin SSI: puertas, MSI: codificadores, decodificadores, contadores, ... LSI: Unidad Sncrona Asncrona de Recepcin Transmisin ,...

2.- Circuitos Digitales Configurables

Se puede modificar su funcin mediante la configuracin de las interconexiones internas existentes

3.- Circuitos de Aplicacin Especfica

Realizacin a medida de la aplicacin: Totalmente a medida (Custom) Empleando elementos o procesos estndar (Semicustom)

Introduccin

ATE-Universidad de Oviedo

Dispositivos Lgicos Programables

Circuitos Digitales Configurables (CDC) frente a la lgica cableada clsica Reduccin del tamao del circuito global Reduccin de costes Diseos flexibles y adaptables Proteccin del diseo Menores retardos de propagacin: ms velocidad Diseo mediante herramientas software Se pueden configurar con equipos de bajo coste CDC de Altera

Introduccin

ATE-Universidad de Oviedo

Dispositivos Lgicos Programables

Circuitos Digitales Configurables (CDCs)

Qu tienen?

Recursos lgicos (bloques)

Interconexiones configurables

Tendencias y tipos: Las interconexiones estn concentradas y en una organizacin matricial: Dispositivos Lgicos Programables (Programmable Logic Devices: PLD) Las interconexiones estn distribuidas: Conjuntos Configurables de Puertas (Field Programmable Gate Arrays: FPGA)

Introduccin

ATE-Universidad de Oviedo

Dispositivos Lgicos Programables

CDC (I): Dispositivos Lgicos Programables Bloque Lgico Bloque Lgico MATRIZ DE INTERCONEXIN

. ........... . . Bloque

Lgico

Bloque Lgico

. . ........... . Bloque

Lgico

Bloque Lgico

Tipos de PLDs:

Bsicos Avanzados Complejos

5

Introduccin

ATE-Universidad de Oviedo

Dispositivos Lgicos Programables

CDC (II): Conjuntos Configurables de Puertas (FPGAs)

Bloque Lgico

Bloque Lgico

Bloque Lgico

Bloque Lgico

Bloque Lgico

Bloque Lgico

Bloque Lgico

Bloque Lgico

Bloque Lgico

Introduccin

ATE-Universidad de Oviedo

Dispositivos Lgicos Programables

Los antecedentes: PAL, PLA y PROM Planteamiento inicial: combinacionales como suma de productos Se pueden configurar las entradas a las puertas AND y/o las de las puertas OR: Configurables las entradas de las AND y de las OR:

PLA FPLA

(Field Programmable Logic Array)

Configurables las entradas a las AND y fijas las entradas a las OR:

PAL

(Programmable Array Logic)

Fijas las entradas a las AND (todos los productos posibles) y programables las entradas a las OR:

PROM

(Programmable Read Only Memory)

ATE-Universidad de Oviedo

Introduccin

Dispositivos Lgicos Programables

1.- PLA

Configurables entradas a AND

3 Entradas

Configurables entradas a OR

(disponibles entradas y negadas)

No hay 2 puertas AND para todos los posibles trminos de la 1 forma cannica 3 Salidas (funciones distintas)

Introduccin

ATE-Universidad de Oviedo

Dispositivos Lgicos Programables

Notacin empleada en las conexiones: Slo para hacer ms simples y reducidos los esquemas No es una lnea comn a todas las entradas de la puerta

Esquema equivalente Esquema normal convencional

Introduccin

ATE-Universidad de Oviedo

Dispositivos Lgicos Programables

1.- PLA

OJO, esta no es la misma conexin!

Representacin simplificada equivalente

Introduccin

ATE-Universidad de Oviedo

10

Dispositivos Lgicos Programables

Entradas circuito

2.- PAL

Conexiones fijas entradas OR

No estn disponibles n las 2 salidas de todas las puertas AND

Conexiones programables entradas AND

Salidas circuito (hasta 4 funciones)

11

Introduccin

ATE-Universidad de Oviedo

Dispositivos Lgicos Programables

3.- PROM

Conexiones programables entradas OR

Hay disponibles n 2 puertas AND con todas las combinaciones posibles de las entradas

Conexiones fijas entradas AND

Introduccin

ATE-Universidad de Oviedo

12

Dispositivos Lgicos Programables

PLA: LAS DIFERENCIAS Configurable la matriz AND y OR Mayor nmero de conexiones a programar Mayor flexibilidad en la realizacin del circuito

Ms usadas

PAL: Configurables la matriz AND y fija la OR Menos conexiones a realizar La salida no es flexible Ocupan menos rea de Silicio y tienen menos retardo de propagacin PROM: Configurable la matriz OR y fija la AND Estn disponibles todas las combinaciones de las seales de entrada en su estado natural o complementado Se puede realizar cualquier circuito combinacional Se emplean para almacenar datos

Introduccin

ATE-Universidad de Oviedo

13

Dispositivos Lgicos Programables

Configuracin de las interconexiones:

!Con fusibles: Irreversibles y no reconfigurables Fueron los primeros en aparecer !Con transistores MOS reconfigurables (no voltiles) Borrables y reconfigurables: Borrables mediante luz ultravioleta Borrables elctricamente !Con transistores MOS y memoria activa esttica (voltiles) Se configura cada conexin mediante un biestable Al dejar de alimentar el circuito se pierde la configuracin

Introduccin

ATE-Universidad de Oviedo

14

Dispositivos Lgicos Programables

1.- Configuracin mediante fusibles

Ejemplo en tecnologa bipolar con diodos Inicialmente todos los fusibles intactos Eliminar la conexin: quemado del fusible No se puede recuperar la situacin inicial

Introduccin

ATE-Universidad de Oviedo

15

Dispositivos Lgicos Programables

2.- Conexiones mediante MOS reconfigurables Dispositivos MOS de Puerta Flotante

Drenador Puerta Puerta flotante Fuente Aislante (SiO2)

Puerta flotante sin carga: MOS controlable desde G

Puerta cargada: MOS en corte

Introduccin

ATE-Universidad de Oviedo

16

Dispositivos Lgicos Programables

Dispositivos MOS de puerta flotante: descargada y cargada

Puerta flotante descargada (conexin)

Puerta flotante cargada (desconexin)

La lnea vertical depende del estado de la horizontal

Introduccin

La lnea vertical no depende del estado de la horizontal

ATE-Universidad de Oviedo

17

Dispositivos Lgicos Programables

Borrado mediante radiacin UVA

es necesario que la luz llegue al Si (tienen una ventana de cristal)

Borrado: electrones escapan de puerta flotante

Grabacin

Borrado mediante impulsos elctricos

Borrado: descarga de la puerta flotante

Grabacin

Introduccin

ATE-Universidad de Oviedo

18

Dispositivos Lgicos Programables

3.- Configuracin mediante SRAM

Seleccin celda: Xi = 1 Yj = 1 Biestable con transistores

Fila xi

La configuracin debe almacenarse en un sistema externo: memoria no voltil o cargarse dinmicamente

Columna Yj

Introduccin

ATE-Universidad de Oviedo

19

Vous aimerez peut-être aussi

- Taller 2 Física de OndasDocument12 pagesTaller 2 Física de OndasCarlos Eduardo Rios DiazPas encore d'évaluation

- Metodo de CholeskyDocument5 pagesMetodo de CholeskyGabriela ArgumePas encore d'évaluation

- Practica 9.6.2Document8 pagesPractica 9.6.2Hebert MolinaPas encore d'évaluation

- Base de Datos 3Document27 pagesBase de Datos 3Gabriela ArgumePas encore d'évaluation

- Los Procesos Del NegocioDocument16 pagesLos Procesos Del NegocioGabriela ArgumePas encore d'évaluation

- 3 LAB Creación ObjetosDocument19 pages3 LAB Creación ObjetosGabriela ArgumePas encore d'évaluation

- 01-5-2 Configuracion Basica Del RouterDocument9 pages01-5-2 Configuracion Basica Del Router_jalveRPas encore d'évaluation

- Base de Datos 2Document33 pagesBase de Datos 2Gabriela ArgumePas encore d'évaluation

- Manual Ensamblador 8086Document17 pagesManual Ensamblador 8086Mario R. Cianone100% (1)

- 05 Metodo AlgebraicoDocument34 pages05 Metodo AlgebraicoGabriela ArgumePas encore d'évaluation

- Cableado de Red y Configuracion Basica de Un RouterDocument28 pagesCableado de Red y Configuracion Basica de Un RouterMakokhanPas encore d'évaluation

- Ejercicio PLD CombinacionalDocument1 pageEjercicio PLD CombinacionalGabriela ArgumePas encore d'évaluation

- 01-5-2 Configuracion Basica Del RouterDocument9 pages01-5-2 Configuracion Basica Del Router_jalveRPas encore d'évaluation

- 04-6-1 Practica de Laboratorio para La Interpretacion de La Tabla de EnrutamientoDocument5 pages04-6-1 Practica de Laboratorio para La Interpretacion de La Tabla de EnrutamientoGabriela ArgumePas encore d'évaluation

- Cableado de Red y Configuracion Basica de Un RouterDocument28 pagesCableado de Red y Configuracion Basica de Un RouterMakokhanPas encore d'évaluation

- Fresadora WordDocument9 pagesFresadora WordmigzaidaPas encore d'évaluation

- NT-CR-F07 Declaración de Confidencialidad Auditorias 20201214Document3 pagesNT-CR-F07 Declaración de Confidencialidad Auditorias 20201214Jose RomeroPas encore d'évaluation

- Manual CTVDocument21 pagesManual CTVvaleriaPas encore d'évaluation

- Tarifa PTAR Sipe SipeDocument28 pagesTarifa PTAR Sipe SipeMiguel Angel Galvez TerrazasPas encore d'évaluation

- Tipos de Fallas ElectricasDocument5 pagesTipos de Fallas ElectricasEver Maunas WidmerPas encore d'évaluation

- Manual Del Estudiante C175 PDFDocument66 pagesManual Del Estudiante C175 PDFMiky Gomez100% (2)

- ADocument13 pagesATommyPas encore d'évaluation

- Gráficas CombinadasDocument4 pagesGráficas CombinadasLuis SantamaríaPas encore d'évaluation

- Bittorrent Sync: Sincronización Ilimitada y Gratis de ArchivosDocument6 pagesBittorrent Sync: Sincronización Ilimitada y Gratis de ArchivosCesar PachónPas encore d'évaluation

- Ciencias Basicas Lab 2Document15 pagesCiencias Basicas Lab 2Fabrizio AmayaPas encore d'évaluation

- Compuertas LógicasDocument10 pagesCompuertas LógicasMary Flor Pashanasi AmasifuenPas encore d'évaluation

- 2015 MAY - Procedimiento de Relubricacion de Rodamientos PDFDocument2 pages2015 MAY - Procedimiento de Relubricacion de Rodamientos PDFjesushuamantunagrandPas encore d'évaluation

- Primer Taller de HidráulicaDocument5 pagesPrimer Taller de HidráulicaANDRESPas encore d'évaluation

- Reactores Dimensiones VariablesDocument20 pagesReactores Dimensiones VariablesLAMESTICA100% (1)

- MUADocument21 pagesMUAGrey's GarcíaPas encore d'évaluation

- Informe de Laboratorio TriacDocument6 pagesInforme de Laboratorio TriacRicardo Soto100% (1)

- Metodo Mapo PDFDocument10 pagesMetodo Mapo PDFAngelica Maria Garzon ForeroPas encore d'évaluation

- Media Queries en CSSDocument7 pagesMedia Queries en CSSzoltak0% (1)

- Oxidacion de Un Clavo de HierroDocument4 pagesOxidacion de Un Clavo de HierroAnonymous UzHl7gYkoPas encore d'évaluation

- Nitrogeno en PlatanoDocument5 pagesNitrogeno en Platanoapi-3772331100% (4)

- Informe TeodolitoDocument20 pagesInforme TeodolitoAlex Quiliche33% (3)

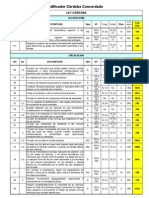

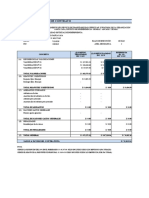

- Codificador Córdoba ConcordadoDocument17 pagesCodificador Córdoba ConcordadokovalyanziPas encore d'évaluation

- Malla de Puesta A TierraDocument32 pagesMalla de Puesta A TierraSofía Zuluaga Gallego100% (1)

- Puesto de Salud La Union-A-02Document1 pagePuesto de Salud La Union-A-02DanielJaraAbantoPas encore d'évaluation

- Actividad 4 Ingenieria MetodosDocument8 pagesActividad 4 Ingenieria MetodosCarolina MartinezPas encore d'évaluation

- Liquidacion Santa CasaDocument24 pagesLiquidacion Santa CasaMarco GuimarayPas encore d'évaluation

- Gas TransbolivianoDocument11 pagesGas TransbolivianoAmparo Zulema Calzada ApazaPas encore d'évaluation

- INGENIERIA DE DETALLE Parte 4Document20 pagesINGENIERIA DE DETALLE Parte 4Marysabel SanchezPas encore d'évaluation

- MEMORIA EXPLICATIVA 2021 FinalDocument81 pagesMEMORIA EXPLICATIVA 2021 Finaldavid rojasPas encore d'évaluation