Académique Documents

Professionnel Documents

Culture Documents

BST Thin Film Capacitor

Transféré par

Keng Goy PlungpongpanCopyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

BST Thin Film Capacitor

Transféré par

Keng Goy PlungpongpanDroits d'auteur :

Formats disponibles

TECHNICAL

PA P E R

Barium Strontium Titanate Thin-Film MultiLayer Capacitors

By Thomas A. Bernacki, Ivoyl P. Koutsaroff and Charles Divita Gennum Corporation

Introduction Miniaturization requirements for hearing-aids and other biomedical applications necessitate the use of advanced packaging and integrated passive technologies. One compound making this possible is Barium Strontium Titanate, (Ba, Sr)TiO3, (BST) [1]. Manufactured on silicon or ceramic wafers, BST capacitors offer high capacitance density, high frequency performance, and the ability to provide exceptional tunability for voltage tunable high frequency applications. Configured into multi-layer capacitor (MLC) arrays, a customized network of capacitors with different values, properties and performance characteristics can be manufactured on the same capacitor chip, offering a higher level of miniaturization, flexibility and performance than conventional discrete capacitors. These customized capacitor networks offer many benefits: A single placement step for all capacitors. Utilizing flip-chip to connect the capacitor chip directly to active ICs, capacitors can be connected in close proximity to critical IC nodes with minimal parasitics. Designers are not restricted to industry standard capacitance values. With profiles as low as 5mils (125microns) , volumetric capacitance densities can be significantly higher than discrete solutions. Ultra-low loss routing between multiple chips and I/Os can be incorporated, with the capacitor chip serving as a carrier in a multi-chip module.

The capacitor is defined by patterning each layer in sequence from the top down, until the entire mesa structure is defined. Following capacitor definition, inter-layer dielectric (ILD) is deposited over the entire wafer surface and cured at high temperatures. Vias are formed in the ILD by standard photolithography

Capacitor Manufacturing The process flow utilized to manufacture BST capacitors is outlined below: The BST multi-layer capacitor thin-film technology is based on a mesa-type process [1]. Alternating layers of Pt and BST are deposited on a silicon or alumina substrate to form a four-layer capacitor stack. BST films are deposited by metalorganic decomposition (MOD) or RF reactive sputtering. PASSIVE COMPONENT INDUSTRY SEPTEMBER/OCTOBER 2004 11

TECHNICAL

PA P E R

serving as routing between multiple active devices (ICs), to and from I/O pads, and functioning as I/O pads. Figure 4 shows a capacitor network of 23 capacitors with a total capacitance of 740nF, 54 I/O pads, and the associated interconnect, in a 3x5mm chip. The capacitors range in size from 1nF to 150nF. Tolerances on the capacitors are excellent, so no trimming or binning is utilized. Capacitor matching (the percent difference between capacitors The BST capacitor of identical designs on the same die) is process in full-scale guaranteed better than 1%. Overall high volume manufactolerance is guaranteed to be better turing yields approxithan 10%. mately 90%. 4-inch Time-domain dielectric breakdown wafers typically contain (TDDB) studies indicate the between 400 and 5000 capacitors have lifetimes of greater dice, depending on the than 10 years under a continuous Figure 1: Cross-Section of Multi-layer Thin-Film BST design [Figure 3]. bias of 3.3V. Over this time, the Capacitor Designs have incapacitors experience no fatigue or cluded as few as one aging. This is because only the capacitor to as many as twenty-three BST Capacitor Performance paraelectric phase of the dielectric on a single die. The capacitor chips material is utilized (no ferroelectric are designed concurrently with active BST capacitors have high capacibehavior is observed in the material). ICs to ensure optimal electrical pertance densities. In a four-layer BST caBST capacitors in the pF range formance and packaging ease. The pacitor on alumina ceramic substrate, have found use in high frequency circapacitor chips include low loss thinthe total capacitance density can be in cuits as well. BST is primarily utilized film interconnect on many products, the range of 144 to 256nF/mm2, dein high frequency circuits to take ad pending on the deposition method vantage of tunability, but used. While not in fill scale manufacby modifying the comturing at the moment, six-layer strucposition of the BST, tuntures have also been demonstrated, ability can be decreased increasing total capacitance density to to provide a high quality 384nF/mm2. factor. For a device with Utilizing standard wafer thinning decreased voltage tuntechniques, the capacitor dice can be ability, Q factors of over thinned to 4mils (100 microns). It has 200 have been achieved been shown that resulting volumetric at 1GHz, and over 160 at 3GHz. For these capacitors, tunabilities of approximately 2:1 (ratio of the highest to lowest capacitance) are observed. When the BST composition is tailored to favour tunability over quality factor, tunabiliFigure 2a: Cross-Section of Actual Multities of over 4:1 have Chip Module Figure 2b: Fully Encapsulated Multi-Chip Module with been achieved, with Q The total package thickness is 60 Mils. One of I/O Pads using the Tip of a Pen as Size Reference. factors over 60 at 1GHz the layers contains BST MLC, 6 Mils in thickThinned on board capacitor dice attached on a ceramic carrier. ness. [3]. Figure 5 shows a density of these capacitors exceeds any MLCC available at present. The largest capacitance value presently available is 0201 (0.6x0.3x0.3mm) with package size of 100nF [2], translating to volumetric density of approximately 1850nF/mm3; BST capacitors have a Wafers are thinned from 22mils volumetric density from 1500 to 2500 (560microns) down to 4mils nF/mm3. Figures 2a and 2b show a (100microns). complete multi-chip module, with the A cross-section of the final stack is thinned capacitor chip attached to sevdepicted in Figure 1. eral other dice. and reactive ion etching. This is followed by the deposition and patterning of a gold or aluminum interconnect layer and deposition and patterning of a silicon nitride passivation layer.

12

PASSIVE COMPONENT INDUSTRY SEPTEMBER/OCTOBER 2004

TECHNICAL

PA P E R

Figure 3: 4" Al2O3 Ceramic Wafer with 4-Layer BST MLC Capacitors

% Capacitance vs Voltage

120% 100%

Figure 4: BST MLC Capacitor Chip The size is 3x5mm (118 x 197mils).

% Capacitance

80% 60% 40% 20% 0% -10 -5 0 5 10

DC Bias Voltage (V)

Figure 5: Tunability (0-8V) of a BST Capacitor

plot of tunability of a typical highly tunable (>4:1) BST capacitor.

Conclusions

High-density BST multi-layer capacitor technology offers distinct miniaturization advantages for various electronic modules and packages. By utilizing BST capacitors with a wide range (0.5pF to 500nF), functions like decoupling, bypassing, and varying capacitance (voltage tunable) can be realized with a single thin-film passive chip. Such miniaturized multi-functional capacitor chips can improve the performance and reduce the size of Multi-chip modules (MCM) and Systems-in-Package (SiP) [Figure 4].

References [1]

[2] [3]

M. Watt, W09800871, (1998). GRM03 capacitor from Murata Manufacturing Co., Ltd.: http://www.murata.com/catalog/k26e3.pdf I. P. Koutsaroff, T. A. Bernacki, M. Zelner, A. CervinLawry, T. Jimbo and K. Suu, Characterization of

[4]

Jpn. J. Appl. Phys. Vol. 43, No. 911, 6740, (2004). http://www.gennum.com/technology/

Thin-Film Decoupling and High-Frequency (Ba, Sr)Ti03 Capacitors on Al203 Ceramic Substrates,

PASSIVE COMPONENT INDUSTRY SEPTEMBER/OCTOBER 2004

13

Vous aimerez peut-être aussi

- CMOS Processing Technology ChapterDocument1 pageCMOS Processing Technology ChapterCarlos SaavedraPas encore d'évaluation

- Integrated Deep Trench Capacitor in Si Interposer For CoWoS Heterogeneous Integration.Document4 pagesIntegrated Deep Trench Capacitor in Si Interposer For CoWoS Heterogeneous Integration.yifan zhaoPas encore d'évaluation

- MLCC Capacitor GuideDocument2 pagesMLCC Capacitor GuideNur Fatihah SaadiqinPas encore d'évaluation

- Printed Circuit Board TechniquesDocument6 pagesPrinted Circuit Board TechniquesA. VillaPas encore d'évaluation

- Avago Layout GuideDocument8 pagesAvago Layout GuideTran Ba QuynhPas encore d'évaluation

- Bypass Capacitors IntersilDocument10 pagesBypass Capacitors IntersilBlykerPas encore d'évaluation

- UW1Document4 pagesUW1Poonam KaurPas encore d'évaluation

- 250 GHZ Sige-Bicmos Cascaded Single-Stage Distributed AmplifierDocument4 pages250 GHZ Sige-Bicmos Cascaded Single-Stage Distributed AmplifierAli HattabPas encore d'évaluation

- 158 - MWWTL - July2002 AcikelDocument3 pages158 - MWWTL - July2002 Acikel23010301042Pas encore d'évaluation

- Bias Dependent Attenuation of Coplanar Transmission Lines On SiliconDocument4 pagesBias Dependent Attenuation of Coplanar Transmission Lines On SiliconEssam KhaterPas encore d'évaluation

- A 0.35Μm Cmos 1.9Ma Vco-Core With Off-Chip Inductance On Ltcc For System-In-A-Package Solutions Of A 5-Ghz-Wlan TransceiverDocument4 pagesA 0.35Μm Cmos 1.9Ma Vco-Core With Off-Chip Inductance On Ltcc For System-In-A-Package Solutions Of A 5-Ghz-Wlan TransceiverMohamed SaidPas encore d'évaluation

- CATCTCESSEXITALYed 3 Rev 1Document38 pagesCATCTCESSEXITALYed 3 Rev 1Kailash ChandraPas encore d'évaluation

- RF Device FundamentalsDocument73 pagesRF Device FundamentalsBenjamin DoverPas encore d'évaluation

- A Wide-Band CMOS LC VCO With Linearized Coarse Tuning CharacteristicsDocument5 pagesA Wide-Band CMOS LC VCO With Linearized Coarse Tuning CharacteristicsBasavaraj S KashappanavarPas encore d'évaluation

- Designing Schottky Diodes for Pulse CompressionDocument7 pagesDesigning Schottky Diodes for Pulse CompressionJesús MartínezPas encore d'évaluation

- Challenges For The DRAM Cell Scaling To 40nmDocument4 pagesChallenges For The DRAM Cell Scaling To 40nmThomas DimecPas encore d'évaluation

- FulltextDocument7 pagesFulltextapi-3721712Pas encore d'évaluation

- Types of Distribution CablesDocument23 pagesTypes of Distribution CablesMusa'bPas encore d'évaluation

- A Fully Integrated CMOS DCS-1800 Frequency Synthesizer: Jan Craninckx,, and Michel S. J. SteyaertDocument12 pagesA Fully Integrated CMOS DCS-1800 Frequency Synthesizer: Jan Craninckx,, and Michel S. J. SteyaertgopipatPas encore d'évaluation

- High Power Bipolar Junction Transistors (BJTsDocument2 pagesHigh Power Bipolar Junction Transistors (BJTsKarteekPas encore d'évaluation

- Design of A Novel, High-Density, High-Speed 10 kVSiC MOSFET ModuleDocument8 pagesDesign of A Novel, High-Density, High-Speed 10 kVSiC MOSFET ModulegeniuspsunPas encore d'évaluation

- Design of Aperture Coupled Fed Micro-Strip Patch Antenna For Wireless CommunicationDocument3 pagesDesign of Aperture Coupled Fed Micro-Strip Patch Antenna For Wireless CommunicationALEX_125Pas encore d'évaluation

- Metal-Insulator-Metal CapacitorsDocument16 pagesMetal-Insulator-Metal Capacitorspilotvivek1087Pas encore d'évaluation

- Intel's Tri-Gate Transistor Tech.Document25 pagesIntel's Tri-Gate Transistor Tech.rvrbangPas encore d'évaluation

- Reviewing the Basics of Suspended StriplinesDocument5 pagesReviewing the Basics of Suspended Striplinesslay17Pas encore d'évaluation

- MOSFET-Only Switched-Capacitor Circuits in Digital CMOS TechnologyDocument14 pagesMOSFET-Only Switched-Capacitor Circuits in Digital CMOS Technologyfabien33Pas encore d'évaluation

- Reliable Ceramic Capacitors for Harsh Automotive EnvironmentsDocument7 pagesReliable Ceramic Capacitors for Harsh Automotive EnvironmentsSaravanan ElumalaiPas encore d'évaluation

- An Adaptive Equalizer With The Capacitance Multiplication For Displayport Main Link in 0.18-M CmosDocument5 pagesAn Adaptive Equalizer With The Capacitance Multiplication For Displayport Main Link in 0.18-M CmosRex JimPas encore d'évaluation

- Advances in Capacitor TechnologyDocument5 pagesAdvances in Capacitor TechnologyPankaj RathiPas encore d'évaluation

- Nductors and Vel Interconnect Silicon Tec: N. Mehmet Keith A. JenkinsDocument5 pagesNductors and Vel Interconnect Silicon Tec: N. Mehmet Keith A. JenkinsstevenasdasPas encore d'évaluation

- A Highly Modular LTCC Packaging Technology For Ka-Band Satellite SystemsDocument5 pagesA Highly Modular LTCC Packaging Technology For Ka-Band Satellite SystemsJeong-geun KimPas encore d'évaluation

- High-Voltage High-Frequency Transformer Design For A 7.2kV To 120V/240V 20kVA Solid State TransformerDocument6 pagesHigh-Voltage High-Frequency Transformer Design For A 7.2kV To 120V/240V 20kVA Solid State TransformerAnonymous gr5v18ItJ5Pas encore d'évaluation

- Whitepaper: Accelerated Lifetime-Test For Metallized Film CapacitorsDocument24 pagesWhitepaper: Accelerated Lifetime-Test For Metallized Film CapacitorsccuevasarenasPas encore d'évaluation

- Superchip Packaging Issues For Advanced Signal ProcessorsDocument5 pagesSuperchip Packaging Issues For Advanced Signal ProcessorsArhip CojocPas encore d'évaluation

- Lifetime Testing of Metallized Thin Film Capacitors For Inverter ApplicationsDocument3 pagesLifetime Testing of Metallized Thin Film Capacitors For Inverter ApplicationsMohammed Al gobariPas encore d'évaluation

- An Electronically Tunable Bandpass Filter Using Thin Flim BST VaractorsDocument6 pagesAn Electronically Tunable Bandpass Filter Using Thin Flim BST VaractorspramodinibidharPas encore d'évaluation

- Bypass Caps An1325Document10 pagesBypass Caps An1325Paolo RoccaratoPas encore d'évaluation

- Choosing and Using Bypass CapacitorsDocument10 pagesChoosing and Using Bypass CapacitorsDimitris LyberisPas encore d'évaluation

- 3d Floorplanning - ReviewPaperDocument6 pages3d Floorplanning - ReviewPaperMayank ChoudharyPas encore d'évaluation

- Guide to Choosing Power Electronics CapacitorsDocument38 pagesGuide to Choosing Power Electronics CapacitorsSunil GeorgePas encore d'évaluation

- The Practical Applications of Multilayer Ceramic Capacitor (MLCC)Document11 pagesThe Practical Applications of Multilayer Ceramic Capacitor (MLCC)jackPas encore d'évaluation

- Fine-Pitch Capabilities of The Flat Ultra-Thin Chip Packaging (UTCP) TechnologyDocument7 pagesFine-Pitch Capabilities of The Flat Ultra-Thin Chip Packaging (UTCP) TechnologySuresh SkvPas encore d'évaluation

- A MMW Perpendicular Coax-To-microstrip TransitionDocument4 pagesA MMW Perpendicular Coax-To-microstrip Transitionagmnm1962Pas encore d'évaluation

- Recent Trends in IGBT TechnologyDocument3 pagesRecent Trends in IGBT TechnologyRichard TsengPas encore d'évaluation

- Thick Film TechnologyDocument19 pagesThick Film TechnologyRasoul Gmdri100% (1)

- Low Phase Noise, Very Wide Band Sige Fully Integrated VcoDocument4 pagesLow Phase Noise, Very Wide Band Sige Fully Integrated VcoSAMPas encore d'évaluation

- RF-CMOS Oscillators With Switched TuningDocument4 pagesRF-CMOS Oscillators With Switched TuningQiuFengPas encore d'évaluation

- Complex Permitivity CharaterizationDocument6 pagesComplex Permitivity CharaterizationskinhugoPas encore d'évaluation

- Technicalarticles Mmwave Siw FilterDocument7 pagesTechnicalarticles Mmwave Siw FilterVikas SinglaPas encore d'évaluation

- Specification of LT Capcitor PannelDocument12 pagesSpecification of LT Capcitor PannelPrashant TrivediPas encore d'évaluation

- A High Density MIM Capacitor in A Standard CMOS Process: Christian Rye IversenDocument4 pagesA High Density MIM Capacitor in A Standard CMOS Process: Christian Rye IversenDuc DucPas encore d'évaluation

- Litz Wire - New England WireDocument18 pagesLitz Wire - New England Wireqtdragon_29Pas encore d'évaluation

- The Future of MM-Wave PackagingDocument11 pagesThe Future of MM-Wave PackagingTribu Vaquero JimenezPas encore d'évaluation

- VLSI Design PPTDocument89 pagesVLSI Design PPTPavan S 4UB18EC024Pas encore d'évaluation

- Thick Electrodes For High Energy Lithium Ion BatteDocument6 pagesThick Electrodes For High Energy Lithium Ion BattePhạm TùngPas encore d'évaluation

- On-Chip Decoupling Capacitor Optimization For Noise and Leakage ReductionDocument5 pagesOn-Chip Decoupling Capacitor Optimization For Noise and Leakage Reductioneppramod3271Pas encore d'évaluation

- 2014 MR - Metal-Layer Capacitors in The 65 NM CMOS Process and The Application For Low-Leakage Power-Rail ESD Clamp CircuitDocument7 pages2014 MR - Metal-Layer Capacitors in The 65 NM CMOS Process and The Application For Low-Leakage Power-Rail ESD Clamp CircuitspaulsPas encore d'évaluation

- Solution Manual for 100 Genesys Design Examples: Second EditionD'EverandSolution Manual for 100 Genesys Design Examples: Second EditionPas encore d'évaluation

- Mathews Paul G. Design of Experiments With MINITAB PDFDocument521 pagesMathews Paul G. Design of Experiments With MINITAB PDFFernando Chavarria100% (2)

- Dow Ecolibrium Overview Sheet v20Document1 pageDow Ecolibrium Overview Sheet v20Keng Goy PlungpongpanPas encore d'évaluation

- XRD Theory PresentationDocument47 pagesXRD Theory Presentationsimongerardgerona50% (2)

- UV Visible SpectrosDocument5 pagesUV Visible SpectrosKeng Goy PlungpongpanPas encore d'évaluation

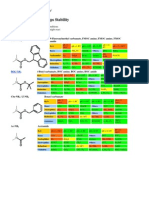

- Protecting Groups StabilityDocument7 pagesProtecting Groups StabilityKeng Goy PlungpongpanPas encore d'évaluation

- UV Visible SpectrosDocument5 pagesUV Visible SpectrosKeng Goy PlungpongpanPas encore d'évaluation

- Runt PPC HomeworkDocument13 pagesRunt PPC HomeworkKeng Goy PlungpongpanPas encore d'évaluation

- UV Visible SpectrosDocument5 pagesUV Visible SpectrosKeng Goy PlungpongpanPas encore d'évaluation

- Protecting Groups StabilityDocument7 pagesProtecting Groups StabilityKeng Goy PlungpongpanPas encore d'évaluation

- Refrigeration CyclesDocument20 pagesRefrigeration CyclesKeng Goy PlungpongpanPas encore d'évaluation

- HW Solution 4Document2 pagesHW Solution 4Keng Goy PlungpongpanPas encore d'évaluation

- RN 4.0 / C... / /o../ D: !uu - Lu-CmDocument5 pagesRN 4.0 / C... / /o../ D: !uu - Lu-CmKeng Goy PlungpongpanPas encore d'évaluation

- Liquid Crystalline PolymersDocument19 pagesLiquid Crystalline PolymersKeng Goy PlungpongpanPas encore d'évaluation

- HomeworkDocument2 pagesHomeworkKeng Goy PlungpongpanPas encore d'évaluation

- YyDocument1 pageYyKeng Goy PlungpongpanPas encore d'évaluation

- Cup - An Introduction To Polymer Physics (2002)Document465 pagesCup - An Introduction To Polymer Physics (2002)cmonasterios100% (3)

- A Review On Nanomaterial Based Humidity SensingDocument16 pagesA Review On Nanomaterial Based Humidity SensingParth GargPas encore d'évaluation

- Nanotechnology and Thin Film Deposition TechniquesDocument8 pagesNanotechnology and Thin Film Deposition TechniquesVeera Mani0% (1)

- Structure-Zone Models of Thin Films: TemperatureDocument9 pagesStructure-Zone Models of Thin Films: TemperaturechipulinoPas encore d'évaluation

- Reliability in MEMS Packaging 1Document5 pagesReliability in MEMS Packaging 1satishkumar8421Pas encore d'évaluation

- ZnSe - Structural, Morphological and Optical Studies of Zinc Selenide (ZnSe) Thin PDFDocument9 pagesZnSe - Structural, Morphological and Optical Studies of Zinc Selenide (ZnSe) Thin PDFbib123456789huPas encore d'évaluation

- Daftar PustakaDocument3 pagesDaftar PustakaMis SakqPas encore d'évaluation

- Tunneling Magnetoresistance (TMR) On Fe-Al O Nano Granular Film Growth by Helicon Plasma SputteringDocument10 pagesTunneling Magnetoresistance (TMR) On Fe-Al O Nano Granular Film Growth by Helicon Plasma SputteringRio AdiePas encore d'évaluation

- Materials For Electrical Engineering and Electronics: Unit 2Document67 pagesMaterials For Electrical Engineering and Electronics: Unit 2Jayashree MisalPas encore d'évaluation

- Electron Beam Evaporation Technique vs. SputteringDocument2 pagesElectron Beam Evaporation Technique vs. SputteringBefzzPas encore d'évaluation

- L32-Diffusion Coating ProcessesDocument10 pagesL32-Diffusion Coating ProcessesdavidblessleyPas encore d'évaluation

- Constant Phase ElementDocument7 pagesConstant Phase Elementlok171962Pas encore d'évaluation

- Stollberg Research Field Emitter DevicesDocument40 pagesStollberg Research Field Emitter DevicesSejtan TempePas encore d'évaluation

- A.N. Jannah, S.A. Halim and H. Abdullah - Superconducting Properties of BSCCO Thin Films by Pulsed Laser DepositionDocument9 pagesA.N. Jannah, S.A. Halim and H. Abdullah - Superconducting Properties of BSCCO Thin Films by Pulsed Laser DepositionKolddePas encore d'évaluation

- Questions - Surface - Engineering Mit LösungDocument9 pagesQuestions - Surface - Engineering Mit LösungParvin ShaikhPas encore d'évaluation

- 1 s2.0 S007964251730004X MainDocument20 pages1 s2.0 S007964251730004X MainMZeeshanAkramPas encore d'évaluation

- Electroluminescence of Thin Film P-I-N Diodes Based On A-Sic:H With Integrated Ge NanoparticlesDocument6 pagesElectroluminescence of Thin Film P-I-N Diodes Based On A-Sic:H With Integrated Ge Nanoparticlessper kstorPas encore d'évaluation

- MCE321 - Lubrication and LubricantsDocument9 pagesMCE321 - Lubrication and LubricantsVanina VaniniPas encore d'évaluation

- Mubashir Qayoom CVDocument6 pagesMubashir Qayoom CVMUBASHIR QAYOOMPas encore d'évaluation

- CVD 1 PDFDocument11 pagesCVD 1 PDFpichonsisimoPas encore d'évaluation

- Thin Film Reflectometry - Physics Open Lab Home PageDocument12 pagesThin Film Reflectometry - Physics Open Lab Home PageClaudio RottmanPas encore d'évaluation

- EM-Unit III NotesDocument28 pagesEM-Unit III NotesSIDDHARTH TATHAGATPas encore d'évaluation

- Mr. Bhargav S. Rajyaguru: Conferences / Symposia / Seminars / Workshops / Schools (Events) AttendedDocument14 pagesMr. Bhargav S. Rajyaguru: Conferences / Symposia / Seminars / Workshops / Schools (Events) AttendedJesse PinkmanPas encore d'évaluation

- 5007Document427 pages5007dt5632Pas encore d'évaluation

- Characterization of An Atmospheric Pressure Plasma JetDocument8 pagesCharacterization of An Atmospheric Pressure Plasma JetAjoy ChandaPas encore d'évaluation

- Quiz 2Document18 pagesQuiz 2Marquee GerbuyosPas encore d'évaluation

- Structural and Mechanical Properties of Nanostructured Tungsten Oxide Thin FilmsDocument9 pagesStructural and Mechanical Properties of Nanostructured Tungsten Oxide Thin FilmsWilma Betzabe Rojas SalinasPas encore d'évaluation

- Class6.CVD and PVDDocument30 pagesClass6.CVD and PVDSaquib HeshamPas encore d'évaluation

- Carbon Nanotubes Based Thin Films: Fabrication, Characterization and ApplicationsDocument22 pagesCarbon Nanotubes Based Thin Films: Fabrication, Characterization and ApplicationsFebri RamdaniPas encore d'évaluation

- CAMS 2018 - Advancing Materials and Manufacturing - November 27-29 - University of Wollongong, NSW, AUSTRALIADocument6 pagesCAMS 2018 - Advancing Materials and Manufacturing - November 27-29 - University of Wollongong, NSW, AUSTRALIAEngr Muhammad HussainPas encore d'évaluation

- IRJAEH0202031 - Smart Fabric Textiles Using Nanomaterials - A Contemporary Overview (2401330)Document5 pagesIRJAEH0202031 - Smart Fabric Textiles Using Nanomaterials - A Contemporary Overview (2401330)A. TonyPas encore d'évaluation